# **DSP320C10**

## **CMOS Digital Signal Processor**

## **FEATURES**

- · 122ns instruction cycle

- 144 word on-chip data RAM

- ROM-less version DSP320C10

- 1.5K word on-chip program ROM—DSP320CM10

- External memory expansion to a total of 4K words at full speed

- · 16-bit instruction/data word

- · 32-bit ALU/Accumulator

- 16 x 16-bit multiply in 122ns

- 0 to 15-bit barrel shifter

- · Eight input and eight output channels

- 16-bit bidirectional data bus with a 65Mbps transfer rate

- · Interrupt with a full context save

- · Signed two's complement fixed-point arithmetic

- CMOS technology

- · Single 5 volt supply

- · Four versions available:

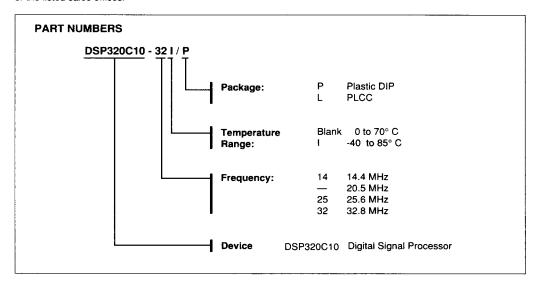

—DSP320C10-14

14.4MHz Clock

—DSP320C10

20.5MHz Clock

—DSP320C10-25

25.6MHz Clock

—DSP320C10-32

32.8MHz Clock

#### DESCRIPTION

The DSP320C10 is the first low power CMOS member of the Microchip Technology DSP320 family of digital signal processors, designed to support a wide range of high-speed or numeric-intensive applications. This device is a CMOS pin-for-pin compatible version of the industry standard DSP32010 digital signal processor.

The processor has been enhanced to make the Data RAM static with respect to the Reset. Also, the address hold time has been improved to a non-negative value.

This 16/32 bit single-chip microcomputer combines the flexibility of a high-speed controller with the numerical capability of an array processor thereby offering an inexpensive alternative to multichip bit-slice processors. The DSP320 family contains MOS microcomputers capable of executing eight million instructions per second. This high throughput is the result of the comprehensive, efficient, and easily programmed instruction set and of the highly pipelined architecture. Special instructions have been incorporated to speed the execution of digital signal processing (DSP) algorithms.

The DSP320 family's unique versatility and power give the design engineer solutions to a variety of complicated applications. In addition, these microcomputers are capable of providing the multiple functions often required for a single application. For example, the DSP320 family can enable an industrial robot to synthesize and recognize speech, sense objects with radar or optical intelligence, and perform mechanical operations through digital servo loop computations.

© 1992 Microchip Technology Inc.

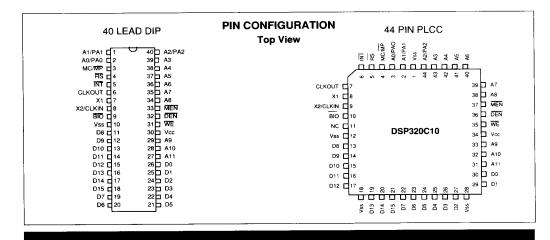

| PIN E              | DESCF | RIPTIONS                                                         |                |          |                                                                                  |

|--------------------|-------|------------------------------------------------------------------|----------------|----------|----------------------------------------------------------------------------------|

| Name               | 1/0   | Definition                                                       | Name           | I/O      | Definition                                                                       |

| A11-A0/<br>PA2-PA0 | OUT   | External address bus. I/O port address multiplexed over PA2-PA0. | MC/MP          | IN       | Memory mode select: High selects microcomputer, low selects microprocessor mode. |

| BIO                | łN    | External polling input for bit test and jump operations.         | MEN            | OUT      | Memory enable indicates that D15-D0 will accept external memory instruction      |

| CLKOUT             | OUT   | System clock output, 1/4 crystal CLKIN frequency.                | RS<br>VCC      | IN<br>IN | Reset used to initialize device. Power.                                          |

| D15-D0             | 1/0   | 16-bit data bus.                                                 |                | iN       | Ground.                                                                          |

| DEN                | OUT   | Data enable indicates the processor                              | VSS<br>WE      | OUT      | Write enable indicates valid data on D15-DO.                                     |

| INT                | IN    | accepting input data on D15-D0. Interrupt.                       | X1<br>X2/CLKIN | IN<br>IN | Crystal input. Crystal input or external clock input.                            |

DS21037B-page 2

© 1992 Microchip Technology Inc.

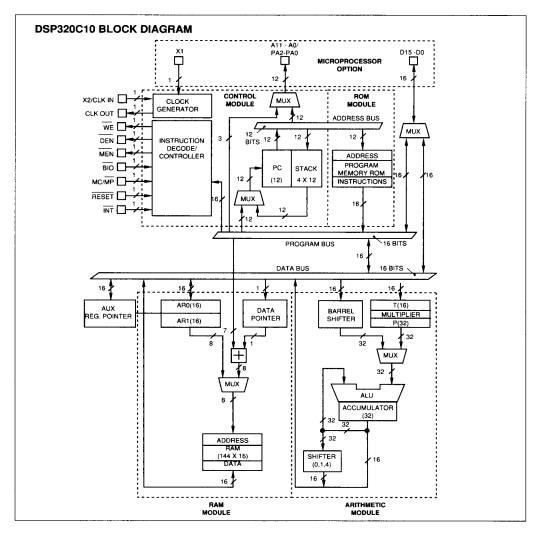

## **ARCHITECTURE**

The DSP320 family utilizes a modified Harvard architecture for speed and flexibility. In a strict Harvard architecture, program and data memory lie in two separate spaces, permitting a full overlap of the instruction fetch and execution. The DSP320 family's modification of the Harvard architecture allows transfers between program and data spaces, thereby increasing the flexibility of the device. This modification permits coefficients stored in program memory to be read into the RAM, eliminating the need for a separate coefficient ROM. It also makes available immediate instructions and subroutines based on computed values.

The DSP320C10 utilizes hardware to implement functions that other processors typically perform in software. For example, this device contains a hardware multiplier to perform a multiplication in a single 122ns cycle. There is also a hardware barrel shifter for shifting data on its way into the ALU. Finally, extra hardware has been included so that auxiliary registers, which provide indirect data RAM addresses, can be configured in an auto increment/decrement mode for single-cycle manipulation of data tables. This hardware-intensive approach gives the design engineer the type of power previously unavailable on a single chip.

#### 32-bit ALU/Accumulator

The DSP320C10 contains a 32-bit ALU and accumulator that support double-precision arithmetic. The ALU operates on 16-bit words taken from the data RAM or derived from immediate instructions. Besides the usual arithmetic instructions, the ALU can perform Boolean operations, providing the bit manipulation ability required of a high-speed controller.

## **Shifters**

A barrel shifter is available for left-shifting data 0 to 15 places before it is loaded into, subtracted from, or added to the accumulator. This shifter extends the high-order bit of the data word and zero-fills the low-order bits for two's complement arithmetic A second shifter left-shifts the upper half of the accumulator 0, 1, or 4 places while it is being stored in the data RAM. Both shifters are very useful for scaling and bit extraction.

#### 16 x 16-bit Parallel Multiplier

The DSP320C10's multiplier performs a 16 x 16-bit, two's complement multiplication in one 122ns instruction cycle. The 16-bit T Register temporarily stores the multiplicand; the P Register stores the 32-bit result. Multiplier values either come from the data memory or are derived immediately from the MPYK (multiply immediate) instruction word. The fast on-chip multiplier allows the DSP320C10 to perform such fundamental operations as convolution, correlation, and filtering at a very high rate.

#### **Program Memory Expansion**

The DSP320C10 is equipped with a 1536-word ROM which can be mask-programmed at the factory with a customer's program. It can also execute from an additional 2560 words of off-chip program memory at full speed. This memory expansion capability is especially useful for those situations where a customer has a number of different applications that share the same subroutines. In this case, the common subroutines can be stored on-chip while the application specific code is stored off-chip.

The DSP 320C10 can operate in either of the following memory modes via the MC/MP pin:

Microcomputer Mode (MC)—Instruction addresses 0-1535 fetched from on-chip ROM. Those with addresses 1536-4095 fetched from off-chip memory at full speed.

Microprocessor Mode (MP)—Full speed execution from all 4096 off-chip instruction addresses.

The ability of the DSP320C10 to execute at full speed from off-chip memory provides important benefits:

- Easier prototyping and development work than is possible with a device that can address only onchip ROM

- Purchase of a standard off-the-shelf product rather than a semi-custom mask-programmed device

- Ease of updating code

- Execution from external RAM

- Downloading of code from another microprocessor

- Use of off-chip RAM to expand data storage capability

## Input/Output

The DSP320C10's 16-bit parallel data bus can be utilized to perform I/O functions at burst rates of 65 million bits per second. Available for interfacing to peripheral devices are 128 input and 128 output bits consisting of eight 16-bit multiplexed input ports and eight 16-bit multiplexed output ports. In addition, a polling input for bit test and jump operations (BIO) and an interrupt pin (INT) have been incorporated for multi-tasking.

## Interrupts and Subroutines

The DSP320C10 contains a four-level hardware stack for saving the contents of the program counter during interrupts and subroutine calls. Instructions are available for saving the DSP320C10's complete context. The instructions, PUSH stack from accumulator, and POP stack to accumulator permit a level of nesting restricted only by the amount of available RAM. The interrupts used in the DSP320C10 are maskable.

#### INSTRUCTION SET

The DSP320C10's comprehensive instruction set supports both numeric-intensive operations, such as signal processing, and general purpose operations, such as high-speed control. The instruction set, explained in Tables 1 and 2, consists primarily of single-cycle singleword instructions, permitting execution rates of up to eight million instructions per second. Only infrequently used branch and I/O instructions are multicycle.

The DSP320C10 also contains a number of instructions that shift data as part of an arithmetic operation. These all execute in a single cycle and are very useful for scaling data in parallel with other operations.

Three main addressing modes are available with the DSP320C10 instruction set: direct, indirect, and immediate addressing.

#### **Direct Addressing**

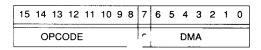

In direct addressing, seven bits of the instruction word concatenated with the data page pointer form the data memory address. This implements a paging scheme in which the first page contains 128 words and the second page contains 16 words. In a typical application, infrequently accessed variables, such as those used for servicing an interrupt, are stored on the second page. The instruction format for direct addressing is shown below.

Bit 7=0 defines direct addressing mode. The opcode is contained in bits 15 through 8. Bits 6 through 0 contain data memory address.

The seven bits of the data memory address (DMA) field can directly address up to 128 words (1 page) of data memory. Use of the data memory page pointer is required to address the full 144 words of data memory.

Direct addressing can be used with all instructions requiring data operands except for the immediate operand instructions.

## **Indirect Addressing**

Indirect addressing forms the data memory from the least significant eight bits of one of two auxiliary registers, AR0 and AR1. The auxiliary register pointer (ARP) selects the current auxiliary register. The auxiliary registers can be automatically incremented or decremented in parallel with the execution of any indirect instruction to permit single-cycle manipulation of data tables. The instruction format for indirect addressing is as follows:

| 15 14 13 12 11 10 9 | 8 | 7 | 6 | 5   | 4   | 3           | 2 | 1 | 0     |

|---------------------|---|---|---|-----|-----|-------------|---|---|-------|

| OPCODE              |   | 1 | 0 | -ZC | ОШО | N<br>A<br>R | 0 | 0 | A R P |

Bit7 = 1 defines indirect addressing mode. The opcode is contained in bits 15 through 8. Bits 7 through 0 contain indirect addressing control bits.

Bit 3 and bit 0 control the Auxiliary Register Pointer (ARP). If bit 3=0, then the content of bit 0 is loaded into the ARP. If bit 3=1, then content of ARP remain unchanged. ARP = 0 defines the contents of AR0 as memory address. ARP = 1 defines the contents of AR1 as memory address.

Bit 5 and bit 4 control the auxiliary registers. If bit 5=1, then the ARP defines which auxiliary register is to be incremented by 1. If bit 4=1, then the ARP defines which auxiliary register is to be decremented by 1. If bit 5 or bit 4 are zero, then neither auxiliary register is incremented or decremented. Bits 6, 2 and 1 are reserved and should always be programmed to zero.

Indirect addressing can be used with all instructions requiring data operands, except for the immediate operand instructions.

#### Immediate Addressing

The DSP320C10 instruction set contains special "immediate" instructions. These instructions derive data from part of the instruction word rather than from the data RAM. Some very useful immediate instructions are multiply immediate (MPYK), load accumulator immediate (LARK), and load auxiliary register immediate (LARK).

## **INSTRUCTION SET SUMMARY**

| TABLE  | 1 - INSTRUCTION SYMBOLS                           |

|--------|---------------------------------------------------|

| Symbol | Meaning                                           |

| ACC    | Accumulator                                       |

| D      | Data memory address field                         |

|        | Addressing mode bit                               |

| K      | Immediate operand field                           |

| PA     | 3-bit port address field                          |

| R      | 1-bit operand field specifying auxiliary register |

| S      | 4-bit left-shift code                             |

| Х      | 3-bit accumulator left-shift field                |

| Mne-  |                                                                 | Numi   |       |    |    |    | Op | Со          | de       | - Ins | stru              | ctio    | n R          | egis | ter |     |   |   |   |

|-------|-----------------------------------------------------------------|--------|-------|----|----|----|----|-------------|----------|-------|-------------------|---------|--------------|------|-----|-----|---|---|---|

| monic | Description                                                     | Cycles | Words | 15 | 14 | 13 | 12 | 11          | 10       | 9     | 8                 | 7       | 6            | 5    | 4   | 3   | 2 | 1 | ( |

| ABS   | Absolute value of accumulator                                   | 1      | 1     | 0  | 1  | 1  | 1  | 1           | 1        | 1     | 1                 | 1       | 0            | 0    | 0   | 1   | 0 | 0 | ( |

| ADD   | Add to accumulator with shift                                   | 1      | 1     | 0  | 0  | 0  | 0  | ←           |          | S-    | <del></del>       | -1      | <del></del>  |      |     | D - |   |   | _ |

| ADDH  | Add to high-order accumulator bit                               | ts 1   | 1     | 0  | 1  | 1  | 0  | 0           | 0        | 0     | 0                 | -1      | $\leftarrow$ |      |     | D - |   |   | _ |

| ADDS  | Add to accumulator with no sign extension                       | 1      | 1     | 0  | 1  | 1  | 0  | 0           | 0        | 0     | 1                 | ı       | <b>←</b>     |      |     | D - |   |   |   |

| AND   | AND with accumulator                                            | 1      | 1     | 0  | 1  | 1  | 1  | 1           | 0        | 0     | 1                 | -1      | $\leftarrow$ |      |     | D.  |   |   | _ |

| LAC   | Load accumulator with shift                                     | 1      | 1     | 0  | 0  | 1  | 0  | <del></del> |          | · S - | $\longrightarrow$ | -1      | ←            |      |     | D.  |   |   | _ |

| LACK  | Load accumulator immediate                                      | 1      | 1     | 0  | 1  | 1  | 1  | 1           | 1        | 1     | 0                 | <b></b> |              |      |     | K   |   |   |   |

| OR    | OR with accumulator                                             | 1      | 1     | 0  | 1  | 1  | 1  | 1           | 0        | 1     | 0                 | 1       | $\leftarrow$ |      |     | D · |   |   | _ |

| SACH  | Store high-order accumulator bits with shift                    | 1      | 1     | 0  | 1  | 0  | 1  | 1           | <b>←</b> | _X_   | <b>→</b>          | ı       | <b>←</b>     |      |     | D   | - |   |   |

| SACL  | Store low-order accumulator bits                                | 1      | 1     | 0  | 1  | 0  | 1  | 0           | 0        | 0     | 0                 | -1      | $\leftarrow$ |      |     | D.  |   |   | _ |

| SUB   | Subtract from accumulator with shift                            | 1      | 1     | 0  | 0  | 0  | 1  | <b>←</b>    |          | · S - | $\longrightarrow$ | ı       | <b>←</b>     |      |     | D   |   |   |   |

| SUBC  | Conditional subtract (for divide)                               | 1      | 1     | 0  | 1  | 1  | 0  | 0           | 1        | 0     | 0                 | 1       | ←            |      |     |     |   |   |   |

| SUBH  | Subtract from high-order                                        | 1      | 1     | 0  | 1  | 1  | 0  | 0           | 0        | 1     | 0                 | 1       | <b>←</b>     |      |     | D   |   |   |   |

| SUBS  | Subtract from accumulator with no sign extension                | 1      | 1     | 0  | 1  | 1  | 0  | 0           | 0        | 1     | 1                 | 1       | <b>←</b>     |      |     | D   |   |   | _ |

| XOR   | Exclusive OR with accumulator                                   | 1      | 1     | 0  | 1  | 1  | 1  | 1           | 0        | 0     | 0                 | - 1     | $\leftarrow$ |      |     | D   |   |   |   |

| ZAC   | Zero accumulator                                                | 1      | 1     | 0  | 1  | 1  | 1  | 1           | 1        | 1     | 1                 | 1       | 0            | 0    | 0   | 1   | 0 | 0 | • |

| ZALH  | Zero accumulator and load<br>high-order bits                    | 1      | 1     | 0  | 1  | 1  | 0  | 0           | 1        | 0     | 1                 | I       | <b>←</b>     |      |     | D   |   |   |   |

| ZALS  | Zero accumulator and load low-order bits with no sign extension | 1      | 1     | 0  | 1  | 1  | 0  | 0           | 1        | 1     | 0                 | 1       | <b>←</b>     |      |     | D   |   |   | _ |

## **INSTRUCTION SET SUMMARY (CONT.)**

| Mne-  |                                           |        | ber of |    |    |    | O  | рСс | de | - In | stru | uctio | on A     | legi | ster |   |   |   |   |

|-------|-------------------------------------------|--------|--------|----|----|----|----|-----|----|------|------|-------|----------|------|------|---|---|---|---|

| monic | Description                               | Cycles | Words  | 15 | 14 | 13 | 12 | 11  | 10 | 9    | 8    | 7     | 6        | 5    | 4    | 3 | 2 | 1 | ( |

| LAR   | Load auxiliary register                   | 1      | 1      | 0  | 0  | 1  | 1  | 1   | 0  | 0    | R    | ı     | <u> </u> |      |      | D | _ | _ |   |

| LARK  | Load auxiliary register immediate         | 1      | 1      | 0  | 1  | 1  | 1  | 0   | 0  | 0    | R    | ←     |          |      |      | K |   |   |   |

|       | Load auxiliary register pointer immediate | 1      | 1      | 0  | 1  | 1  | 0  | 1   | 0  | 0    | 0    | 1     | 0        | 0    | 0    | 0 | 0 | 0 |   |

| LDP   | Load data memory page pointer             | 1      | 1      | 0  | 1  | 1  | 0  | 1   | 1  | 1    | 1    | 1     | <b>-</b> |      |      | D | _ |   |   |

|       | Load data memory page pointer immediate   | 1      | 1      | 0  | 1  | 1  | 0  | 1   | 1  | 1    | 0    | 0     | 0        | 0    | 0    | 0 | 0 | 0 |   |

| MAR   | Modify auxiliary register and point       | ter 1  | 1      | 0  | 1  | 1  | 0  | 1   | 0  | 0    | 0    | 1     | ←        |      |      | D |   |   |   |

|       | Store auxiliary register                  | 1      | 1      | Ō  | 0  | 1  | 1  | Ó   | ō  | Ō    | Ř    | 1     | <u>`</u> |      |      | Ď | _ |   |   |

| Mne-  |                                             |        | er of |     |        |        | O      | Сс     | de | - In | stru      | ıctic    | on F     | legi:    | ster     |           |   |                |   |

|-------|---------------------------------------------|--------|-------|-----|--------|--------|--------|--------|----|------|-----------|----------|----------|----------|----------|-----------|---|----------------|---|

| monic | Description                                 | Cycles | Words | 15  | 14     | 13     | 12     | 11     | 10 | 9    | 8         | 7        | 6        | 5        | 4        | 3         | 2 | 1              | 0 |

| В     | Branch unconditionally                      | 2      | 2     | 1 0 | 1      | 1      | 1      | 1      | 0  | 0    | 1<br>- BI | 0<br>RAN | O<br>CH  | 0<br>ADD | 0<br>RES | 0<br>S    | 0 | 0              | 0 |

| BANZ  | Branch on auxiliary register not zero       | 2      | 2     | 1 0 | 1      | 1      | 1<br>0 | 0<br>← | 1  | 0    | 0<br>- BI | 0<br>RAN | O<br>CH  | 0<br>ADD | 0<br>RES | 0<br>S    | 0 | 0<br>—→        | 0 |

| BGEZ  | Branch if accumulator ≥ 0                   | 2      | 2     | 1 0 | 1<br>0 | 1      | 1<br>0 | 1<br>← | 1  | 0    | 1<br>- Bl | 0<br>RAN | 0<br>CH  | 0<br>ADD | 0<br>RES | 0<br>S—   | 0 | 0<br>→         | 0 |

| BGZ   | Branch if accumulator > 0                   | 2      | 2     | 1 0 | 1<br>0 | 1<br>0 | 1<br>0 | 1<br>← | 1  | 0    | 0<br>- BI | 0<br>RAN | 0<br>CH  | 0<br>ADD | 0<br>RES | 0<br>S—   | 0 | 0<br>—→        | 0 |

| BIOZ  | Branch on BIO = 0                           | 2      | 2     | 1 0 | 1<br>0 | 1<br>0 | 1<br>0 | 0      | 1  | 1    | 0<br>- Bl | 0<br>RAN | O<br>ICH | 0<br>ADD | 0<br>RES | 0<br>S—   | 0 | 0<br>→         | 0 |

| BLEZ  | Branch if accumulator ≤ 0                   | 2      | 2     | 1 0 | 1      | 1      | 1      | 1<br>← | 0  | 1    | 1<br>~ Bi | 0<br>RAN | 0<br>ICH | 0<br>ADD | 0<br>RES | 0<br>S—   | 0 | 0<br>—         | 0 |

| BLZ   | Branch if accumulator < 0                   | 2      | 2     | 1 0 | 1      | 1      | 1      | 1<br>← | 0  | 1    | 0<br>- Bi | 0<br>RAN | 0<br>CH  | 0<br>ADD | 0<br>RES | ิ 0<br>S— | 0 | 0              | 0 |

| BNZ   | Branch if accumulator ≠ 0                   | 2      | 2     | 1 0 | 1      | 1      | 1      | 1      | 1  | 1    | 0<br>- B  | 0<br>RAN | 0<br>ICH | 0<br>ADD | 0<br>RES | ์ 0<br>Տ— | 0 | 0              | 0 |

| BV    | Branch on overflow                          | 2      | 2     | 1 0 | 1      | 1      | 1      | 0      | 1  | 0    | 1<br>- B  | 0<br>RAN | 0<br>ICH | 0<br>ADD | 0<br>RES | ¯0<br>S—  | 0 | 0              | 0 |

| BZ    | Branch if accumulator = 0                   | 2      | 2     | 1 0 | 1      | 1      | 1      | 1 ←    | 1  | 1    | 1<br>- Bl | 0<br>RAN | 0<br>ICH | 0<br>ADD | 0<br>RES | ิ 0<br>S— | 0 | 0              | 0 |

| CALA  | Call subroutine from accumulato             | r 2    | 1     | 0   | 1      | 1      | 1      | 1      | 1  | 1    | 1         | 1        | 0        | 0        | 0        | 1         | 1 | 0              | 0 |

| CALL  | Call subroutine immediately                 | 2      | 2     | 1 0 | 1      | 1      | 1      | 1      | 0  | 0    | 0<br>- B  | 0<br>RAN | 0<br>ICH | 0<br>ADD | 0<br>RES | 0<br>S—   | 0 | 0              | 0 |

| RET   | Return from subroutine or interrupt routine | 2      | 1     | 0   | 1      | 1      | 1      | 1      | 1  | 1    | 1         | 1        | 0        | 0        | 0        | 1         | 1 | o <sup>´</sup> | 1 |

## **INSTRUCTION SET SUMMARY (CONT.)**

| Mne-  |                                                                         |        | per of |    |    |    | Ot       | Co | de | - In | stru | ıctic | n R         | egis | ster |   |   |   |               |

|-------|-------------------------------------------------------------------------|--------|--------|----|----|----|----------|----|----|------|------|-------|-------------|------|------|---|---|---|---------------|

| monic | Description                                                             | Cycles | Words  | 15 | 14 | 13 | 12       | 11 | 10 | 9    | 8    | 7     | 6           | 5    | 4    | 3 | 2 | 1 | 0             |

| APAC  | Add P register to accumulator                                           | 1      | 1      | 0  | 1  | 1  | 1        | 1  | 1  | 1    | 1    | 1     | 0           | 0    | 0    | 1 | 1 | 1 | 1             |

| LT    | Load T register                                                         | 1      | 1      | 0  | 1  | 1  | 0        | 1  | 0  | 1    | 0    | 1     | <b></b>     |      |      | D | _ |   | $\rightarrow$ |

|       | LTA combines LT and APAC into one instruction                           | 1      | 1      | 0  | 1  | 1  | 0        | 1  | 1  | 0    | 0    | ı     | <del></del> |      |      | D |   |   | <b>→</b>      |

|       | LTD combines LT, APAC, and DMOV into one instruction                    | 1      | 1      | 0  | 1  | 1  | 0        | 1  | 0  | 1    | 1    | I     | <b>←</b>    |      | _    | D | _ |   | $\rightarrow$ |

|       | Multiply with T register, store product in P register                   | 1      | 1      | 0  | 1  | 1  | 0        | 1  | 1  | 0    | 1    | I     | <del></del> | ·    |      | D |   |   | <b>→</b>      |

| MPYK  | Multiply T register with immediate operand; store product in P register |        | 1      | 1  | 0  | 0  | <b>←</b> |    |    |      |      |       | Κ -         |      |      |   |   |   | <b>-</b> →    |

|       | Load accumulator from P register                                        |        | 1      | 0  | 1  | 1  | 1        | 1  | 1  | 1    | 1    | 1     | 0           | 0    | 0    | 1 | 1 | 1 | c             |

| SPAC  | Subtract P register from accumulator                                    | 1      | 1      | 0  | 1  | 1  | 1        | 1  | 1  | 1    | 1    | 1     | 0           | 0    | 1    | 0 | 0 | 0 | Ċ             |

| Mne-  | <b>-</b>                    | Numl   |       |    |    |    | 0  | Co | ode | - In | stru | ıctic | on A         | egi | ster |   |   |   |   |

|-------|-----------------------------|--------|-------|----|----|----|----|----|-----|------|------|-------|--------------|-----|------|---|---|---|---|

| monic | Description                 | Cycles | words | 15 | 14 | 13 | 12 | 11 | 10  | 9    | 8    | 7     | 6            | 5   | 4    | 3 | 2 | 1 |   |

| DINT  | Disable interrupt           | 1      | 1     | 0  | 1  | 1  | 1  | 1  | 1   | 1    | 1    | 1     | 0            | 0   | 0    | 0 | 0 | 0 | _ |

| EINT  | Enable interrupt            | 1      | 1     | 0  | 1  | 1  | 1  | 1  | 1   | 1    | 1    | 1     | 0            | 0   | 0    | 0 | 0 | 1 |   |

| LST   | Load status register        | 1      | 1     | 0  | 1  | 1  | 1  | 1  | 0   | 1    | 1    | 1     | $\leftarrow$ |     |      | D |   |   | _ |

| NOP   | No operation                | 1      | 1     | 0  | 1  | 1  | 1  | 1  | 1   | 1    | 1    | 1     | 0            | 0   | 0    | 0 | 0 | 0 |   |

| POP   | POP stack to accumulator    | 2      | 1     | 0  | 1  | 1  | 1  | 1  | 1   | 1    | 1    | 1     | 0            | 0   | 1    | 1 | 1 | 0 |   |

| PUSH  | PUSH stack from accumulator | 2      | 1     | 0  | 1  | 1  | 1  | 1  | 1   | 1    | 1    | 1     | 0            | 0   | 1    | 1 | 1 | 0 |   |

| ROVM  | Reset overflow mode         | 1      | 1     | 0  | 1  | 1  | 1  | 1  | 1   | 1    | 1    | 1     | 0            | 0   | 0    | 1 | 0 | 1 |   |

| SOVM  | Set overflow mode           | 1      | 1     | 0  | 1  | 1  | 1  | 1  | 1   | 1    | 1    | 1     | 0            | 0   | 0    | 1 | 0 | 1 |   |

| SST   | Store status register       | 1      | 1     | 0  | 1  | 1  | 1  | 1  | 1   | 0    | 0    | - 1   | ←            |     |      | D | _ |   | _ |

| Mne-  | <b>-</b>                                             |        | per of |    |    |    | Ot | Со | de | - In | stru          | ıctic | n R         | egis | ster |   |   |   |    |

|-------|------------------------------------------------------|--------|--------|----|----|----|----|----|----|------|---------------|-------|-------------|------|------|---|---|---|----|

| monic | Description                                          | Cycles | Words  | 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8             | 7     | 6           | 5    | 4    | 3 | 2 | 1 | (  |

| DMOV  | Copy contents of data memory                         | 1      | 1      | 0  | 1  | 1  | 0  | 1  | 0  | 0    | 1             | 1     | <del></del> |      |      | D | _ |   | _  |

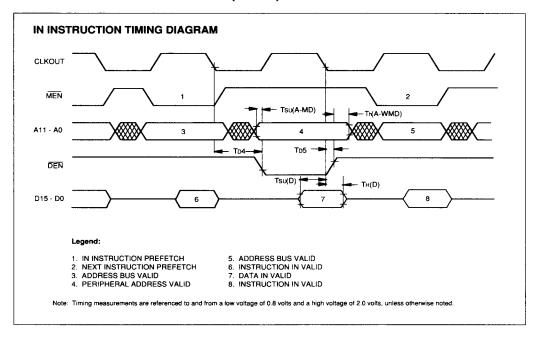

| IN    | Input data from port                                 | 2      | 1      | 0  | 1  | 0  | 0  | 0  | ←  | PΑ   | $\rightarrow$ | 1     | ←           |      |      | D |   |   | _; |

| OUT   | Output data to port                                  | 2      | 1      | 0  | 1  | 0  | 0  | 1  | ←  | PΑ   | $\rightarrow$ | 1     | ←           |      |      | D | _ |   |    |

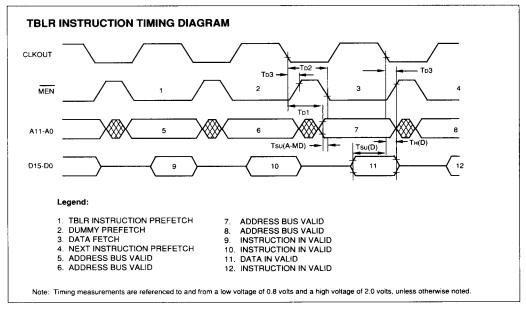

| TBLR  | Table read from program memory to data RAM           | 3      | 1      | 0  | 1  | 1  | 0  | 0  | 1  | 1    | 1             | 1     | <del></del> |      |      | D | _ |   | _  |

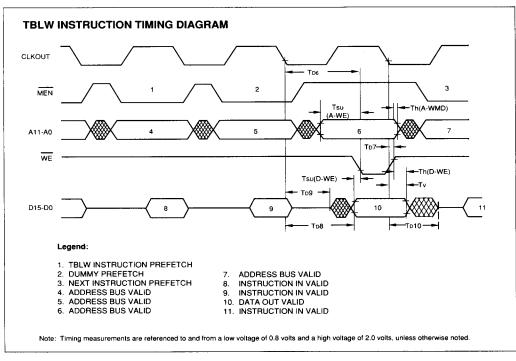

| TBLW  | Table write from data RAM to program (external only) | 3      | 1      | 0  | 1  | 1  | 1  | 1  | 1  | 0    | 1             | 1     | <b>←</b>    |      |      | D |   |   | _  |

## **ELECTRICAL CHARACTERISTICS**

## Absolute Maximum Ratings\*

\*\*Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied - operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Data labeled "typical" is presented for design guidance only and is not guaranteed.

| Observatoristics                                              | DS     | P3200    | 210       | DSP          | 320C1    | 0-14      | DSP    | 320C1    | 0-25      | DSP   | 320C1    | 0-32      | Unit                     | Conditions                     |

|---------------------------------------------------------------|--------|----------|-----------|--------------|----------|-----------|--------|----------|-----------|-------|----------|-----------|--------------------------|--------------------------------|

| Characteristics                                               | Min    | Nom*     | Max       | Min          | Nom*     | Max       | Min    | Nom*     | Max       | Min   | Nom*     | Max       | Unit                     | Conditions                     |

| Supply voltage, Vcc                                           | 4.5    | 5.0      | 5.5       | 4.5          | 5.0      | 5.5       | 4.5    | 5.0      | 5.5       | 4.5   | 5.0      | 5.5       | ٧                        |                                |

| Supply voltage, Vss                                           | _      | 0        | _         | _            | 0        |           | _      | 0        | _         | -     | 0        | ı         | ٧                        |                                |

| High-level input voltage, Vін<br>- All inputs except CLKIN    | 2.0    |          |           | 2.0          | _        |           | 2.0    | -        | _         | 2.0   |          |           | V                        |                                |

| - CLKIN                                                       | .65Vcc | -        | _         | .65Vcc       | _        |           | .65Vcc | _        | _         | .65Vc |          |           | V                        |                                |

| Low-level input voltage, VIL (all inputs)                     | -      | -        | 0.8       | -            | -        | 0.8       | _      | _        | 8.0       | _     | -        | 0.8       | V                        |                                |

| High-level output voltage Vон                                 | Vcc4   | _        | _         | Vcc4         | _        | _         | Vcc4   | _        | _         | Vcc4  | _        | _         | ٧                        | 1он = 20µА                     |

|                                                               | 2.4    | _        | _         | 2.4          | _        | _         | 2.4    | _        | _         | 2.4   | _        | _         | ٧                        | Iон = 300µA                    |

| Low-level output voltage, Vol                                 | -      | _        | 0.4       | _            | _        | 0.4       | _      | _        | 0.4       | -     | _        | 0.4       | v                        | IOL = 2mA                      |

| Off-state output current, loz                                 | _      | _        | 20<br>-20 | =            | =        | 20<br>-20 | _      | _        | 20<br>-20 | _     | _<br>_   | 20<br>-20 | μ <b>Α</b><br>μ <b>Α</b> | Vcc = 5.5V<br>Vo = Vcc4V       |

| Input current, li                                             | _      | _        | ±50       | _            | _        | ±50       | _      | _        | ±50       | _     | _        | ±50       | μА                       |                                |

| Supply current, Icc (tested w/clocks running & part in reset) | _      | _        | 50        | _            | -        | 50        | _      | _        | 55        | _     | _        | 65        | mA                       | Vcc = 5.5V                     |

| Input capacitance, Cı<br>- Data bus<br>- All others           | _<br>_ | 25<br>15 | -         | <br> -<br> - | 25<br>15 | _         | _      | 25<br>15 | _<br>_    | _<br> | 25<br>15 | _<br>_    | pF<br>pF                 | 4 4141-                        |

| Output capacitance, Co - Data bus - All others                | _      | 25<br>10 | _         | =            | 25<br>10 | _         | _      | 25<br>10 | _         | _     | 25<br>10 | _         | pF<br>pF                 | f = 1MHz,<br>all other pins 0\ |

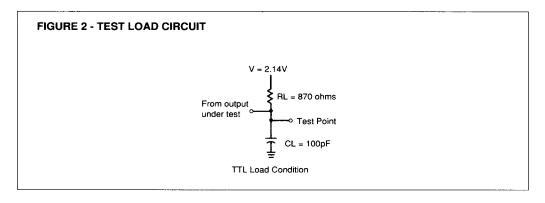

## PARAMETER MEASUREMENT INFORMATION

## **CLOCK**

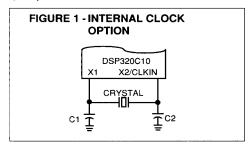

The DSP320C10 can use either its internal oscillator or an external frequency source for a clock.

## INTERNAL CLOCK OPTION

The internal oscillator is enabled by connecting a crystal across X1 and X2/CLKIN (See Figure 1). The frequency of CLKOUT is one-fourth the crystal fundamental frequency.

The crystal should be fundamental mode, and parallel resonant, with an effective series resistance of 30 ohms, a power dissipation of 1mW, and be specified at a load capacitance of 20pF.

## **EXTERNAL CLOCK OPTION**

An external frequency source can be used by injecting the frequency directly into X2/CLKIN with X1 left unconnected.

The external frequency injected must conform to the specifications listed in the table below.

| CLOCK FREQUENCIES              |     |     |     |          |      |                                 |

|--------------------------------|-----|-----|-----|----------|------|---------------------------------|

| Characteristics                | Sym | Min | Nom | Max      | Unit | Temperature<br>Range Conditions |

| DSP320C10 Crystal frequency    | fx  | 6.7 |     | 20.5     | MHz  | I, C                            |

| DSP320C10-14 Crystal frequency | fx  | 6.7 |     | 14.4     | MHz  | 1, C                            |

| DSP320C10-25 Crystal frequency | fx  | 6.7 | l — | 25.6     | MHz  | I, C                            |

| DSP320C10-32 Crystal frequency | fx  | 6.7 | l — | 32.8     | MHz  | I, C                            |

| C1,C2                          |     | _   | 10  | <u> </u> | pf   | I, C                            |

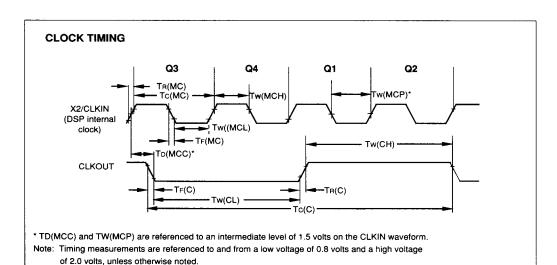

## **CLOCK (CONT.)**

#### **CLOCK AC CHARACTERISTICS**

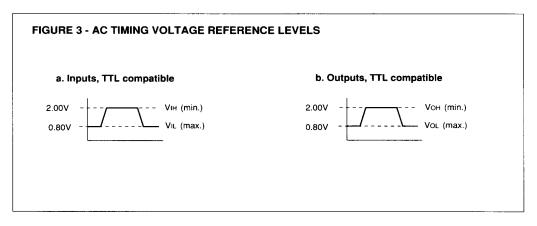

Timing requirements/Switching Characteristics over Recommended Operating Conditions

Ta (Commercial) = 0° to 70° C Ta (Industrial) = -40° to 85° C Vcc = 5V + 10%, Vss = 0V

|                         |                    | DSF       | 3200 | C10       | DSP       | 320C     | 10-14     | DSP3      | 320C | 10-25      | DSP3       | 20C | 10-32      |          |            |

|-------------------------|--------------------|-----------|------|-----------|-----------|----------|-----------|-----------|------|------------|------------|-----|------------|----------|------------|

| Characteristics         | Sym                | Min       | Nom  | Max       | Min       | Nom      | Max       | Min       | Nom  | Max        | Min        | Nom | Max        | Unit     | Conditions |

| Master clk cycle time   | Tc(MC)             | 48.78     | _    | 150       | 69.50     | -        | 150       | 39        | _    | 150        | 30.5       | _   | 150        | ns       | Note 1     |

| Rise time mast. clk in. | Tr(MC)             | _         | 5    | 10°       | _         | 5        | 10*       |           | 4    | 8*         | _          | 3   | 6*         | ns       |            |

| Fall time mast. clk in. | Tr(MC)             | _         | 5    | 10*       | _         | 5        | 10*       | _         | 4    | 8*         | _          | 3   | 6*         | ns       |            |

| Pulse dur. mast. cik    |                    |           |      |           |           |          |           |           |      |            |            |     |            |          |            |

| low, Tc(MC) = 70ns      | Tw(MCL)            | 14*       | 20   |           | 14*       | 20       | -         | 12*       | 16   | _          | 8*         | 12  | _          | ns       |            |

| Pulse dur. mast clk     |                    |           |      |           |           |          |           |           |      |            |            |     |            |          |            |

| high, Tc(MC) = 70ns     | тҗмсн)             | 14*       | 20   | _         | 14*       | 20       | _         | 12*       | 16   | _          | 8*         | 12  | -          | ns       |            |

| Pulse dur. mast clk     | Tw(MCP)            | 0.4Tc(C)* | -    | 0.6Tc(C)* | 0.4Tc(C)* | -        | 0.6Tc(C)* | 0.45Tc(C) | -    | 0.55Tc(C)* | 0.45Tc(C)* | -   | 0.55Tc(C)* | ns       |            |

| CLKOUT cycle time       | Tc(C)              | 195.12    | -    |           | 277.80    | -        | _         | 156       | -    | -          | 122        | -   |            | ns       |            |

| CLKOUT rise time        | Tr(C)              | _         | 10   | _         | -         | 10       | _         | l –       | 10   | _          | -          | 4   | -          | ns       |            |

| CLKOUT fall time        | T <sub>f</sub> (C) | _         | 8    | –         | -         | 8        | _         | -         | 8    | _          | _          | 7   | -          | ns       |            |

| Pls. dur., CLKOUT low   | Tw(CL)             | _         | 92   | _         | _         | 131      | _         | -         | 74   | _          | _          | 57  | _          | ns       | See Fig 2  |

| Pls.dur., CLKOUT high   | Tw(CH)             | _         | 90   | _         | _         | 129      | _         |           | 72   | _          | _          | 54  | _          | ns       |            |

| Delay time to CLKIN↑    |                    |           |      |           |           | <b>†</b> |           |           |      |            |            |     |            | <u> </u> |            |

| to CLKOUT↓ (Note 2)     | Td(MCC)            | 10        | -    | 60        | 10        | -        | 60        | 10        | -    | 50         | 10         | -   | 50         | ns       |            |

Note:

- (1) TC(C) is the cycle time of CLKOUT. i.e., 4\*TC(MC) (4 times CLKIN cycle time if an external oscillator is used)

- (2) \*These values were derived from characterization data and are not tested or guaranteed.

<sup>© 1992</sup> Microchip Technology Inc.

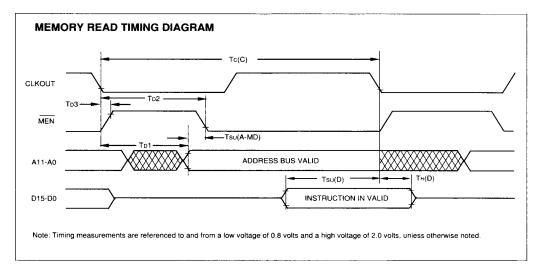

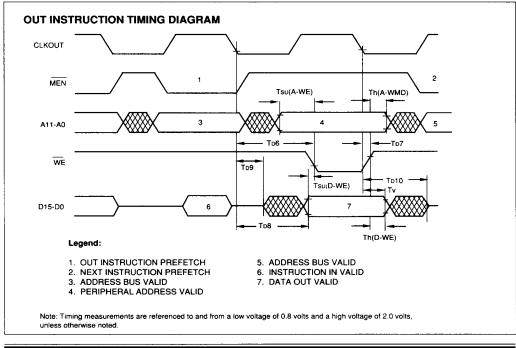

## **MEMORY AND PERIPHERAL INTERFACE TIMING**

## **MEMORY AND PERIPHERAL INTERFACE - AC CHARACTERISTICS**

Over recommended operating conditions

| Characteristics                                                                                                 | Sym        | Min           | Тур | Max            | Unit | Conditions   |

|-----------------------------------------------------------------------------------------------------------------|------------|---------------|-----|----------------|------|--------------|

| Delay time CLKOUT↓ to address bus valid (see note)                                                              | Td1        | 10*           | _   | 38             | ns   | See Figure 2 |

| Delay time CLKOUT↓ to MEN↓                                                                                      | Td2        | 1/4Tc(C) -5*  | _   | 1/4Tc(C) +12   | ns   |              |

| Delay time CLKOUT↓ to MEN↑                                                                                      | Td3        | -8*           | _   | 12             | ns   |              |

| Delay time CLKOUT↓ to DEN↓                                                                                      | Td4        | 1/4Tc(C) -5*  | -   | 1/4Tc(C) +12   | ns   |              |

| Delay time CLKOUT↓ to DEN↑                                                                                      | Td5        | -8*           | _   | 12             | ns   |              |

| Delay time CLKOUT↓ to WE↓                                                                                       | Td6        | 1/2Tc(C) -5*  | _   | 1/2Tc(C) +12   | ns   |              |

| Delay time CLKOUT↓ to WE↑                                                                                       | Td7        | -8*           | _   | 12             | ns   |              |

| Delay time CLKOUT↓ to data bus OUT valid                                                                        | Td8        | _             | _   | 1/4Tc(C) +40   | ns   |              |

| Time after CLKOUT↓ that data bus starts to be driven                                                            | Td9        | 1/4Tc(C) - 5* | _   | -              | ns   |              |

| Time after CLKOUT↓ that data bus stops being driven                                                             | Td10       | _             | _   | 1/4Tc(C) +30*  | ns   |              |

| Data bus OUT valid after CLKOUT↓                                                                                | Tv         | 1/4Tc(C) - 10 | _   | _              | ns   |              |

| Delay time DEN↑, MEN↑ and WE↑ from RS↓                                                                          | Td11       | -             | _   | Tc(C) + 50*    | ns   |              |

| Setup time data bus valid prior to CLKOUT↓                                                                      | Tsu(D)     | 38            | _   | _              | ns   |              |

| Hold time data bus held valid after CLKOUT↓                                                                     | Th(D)      | 0             | -   | _              | ns   |              |

| Address bus setup time prior to $\overline{\text{MEN}} \downarrow \text{ or } \overline{\text{DEN}} \downarrow$ | Tsu (A-MD) | 1/4Tc(C) -35  | -   | _              | ns   |              |

| Address bus hold after WE↑, MEN↑ or DEN↑                                                                        | Th(A-WMD)  | 5             | -   | _              | ns   |              |

| Address bus setup time prior to WE↓                                                                             | Tsu(A-WE)  | 1/2Tc(C) -34  | _   | _              | ns   |              |

| Data bus setup time prior to WE↓                                                                                | Tsu(D-WE)  | 1/4Tc(C) -32  | -   | _              | ns   |              |

| Data bus hold after WE↑                                                                                         | Th(D-WE)   | 1/4Tc(C) -18  | -   | _              | ns   |              |

| External memory access time                                                                                     | Tacc       | _             | -   | Tc(C) - 69     | ns   |              |

| External memory output enable time                                                                              | Toe        | _             | _   | 3/4 Tc(C) - 40 | ns   |              |

<sup>\*</sup>These values were derived from characterization data and are not tested.

Note: 1. Address bus will be valid upon  $\overline{WE}\uparrow$ ,  $\overline{DEN}\uparrow$ , or  $\overline{MEN}\uparrow$ .

<sup>2.</sup> Data may be removed from the data bus upon MEN↑ or DEN↑ preceding CLKOUT↓

## **MEMORY AND PERIPHERAL INTERFACE TIMING (CONT.)**

## **INSTRUCTION TIMING DIAGRAMS (CONT.)**

## **INSTRUCTION TIMING DIAGRAMS (CONT.)**

© 1992 Microchip Technology Inc.

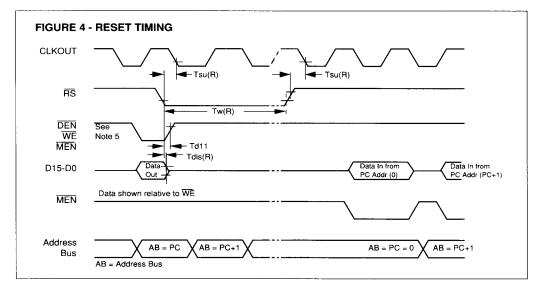

## **RESET (RS) TIMING**

#### RESET TIMING AC CHARACTERISTICS

Timing requirements over recommended operating conditions

| Characteristics                                                    | Sym     | Min    | Nom | Max             | Unit | Conditions   |

|--------------------------------------------------------------------|---------|--------|-----|-----------------|------|--------------|

| Reset (RS) setup time prior to CLKOUT. See notes 1-4. DSP320C10-32 | Tsu(R)  | 38     | _   |                 | ns   |              |

| RS pulse duration                                                  | Tw(R)   | 5Tc(C) | _   | _               | ns   |              |

| Delay time DEN↑, WE↑, and MEN↑ from RS↓                            | Td11    | _      | _   | Tc(C) + 50*     | ns   | See Figure 2 |

| Data bus disable time after RS                                     | Tdis(R) |        | _   | 3/4Tc(C) + 120* | ns   |              |

Note: RS can occur anytime during a clock cycle. Time given is minimum to ensure synchronous operation.

<sup>\*</sup>These values were derived from characterization data and are not tested.

#### Notes:

- RS forces DEN, WE, and MEN high and tristates data bus DO through D15. AB outputs (and program counter) are synchronously cleared to zero after the next complete CLK cycle from RS↓.

- 2. RS must be maintained for a minimum of five clock cycles.

- Resumption of normal program will commence after one complete CLK cycle from RS1.

- Due to the synchronizing action on RS, time to execute the function can vary dependent upon when RS↑ or RS↓ occur in the CLK cycle.

- 5. Diagram shown is for definition purpose only. DEN, WE, and MEN are mutually exclusive.

- Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

- 7. During a write cycle, RS may produce an invalid write address.

DS21037B-page 16

© 1992 Microchip Technology Inc.

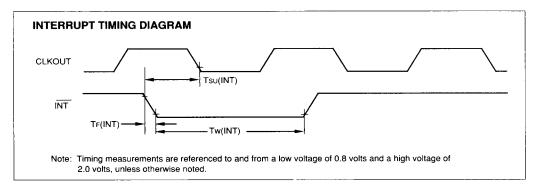

## INTERRUPT (INT) TIMING

| Timing requirements over recommended operating conditions |                      |       |     |     | * These values are not tested |            |  |

|-----------------------------------------------------------|----------------------|-------|-----|-----|-------------------------------|------------|--|

| Characteristics                                           | Sym                  | Min   | Nom | Max | Unit                          | Conditions |  |

| Fall time INT                                             | T <sub>f</sub> (INT) | _     | _   | 15* | ns                            |            |  |

| Pulse duration INT                                        | Tw(INT)              | Tc(C) | -   | _   | ns                            |            |  |

| Setup time INT↓ before CLKOUT↓                            | Tsu(INT)             | 38    | -   |     | ns                            |            |  |

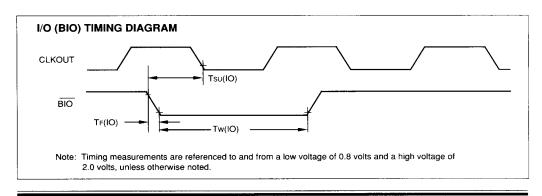

## I/O (BIO) TIMING

#### I/O (BIO) AC CHARACTERISTICS Timing requirements over recommended operating conditions \* These values are not tested Conditions Characteristics Sym Min Nom Max Unit Fall time BIO T<sub>f</sub>(IO) 15\* ns Pulse duration BIO Tw(IO) $T_c(C)$ ns Setup time BIO↓ before CLKOUT↓ Tsu(IO) 38 ns

© 1992 Microchip Technology Inc.

## **SALES AND SUPPORT**

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed sales offices.