Order this document by DSP56F827EVMUM/D Rev. 1, 07/22/2003

# 56F827 Evaluation Module Hardware User's Manual

## **Table of Contents**

|        | Preface                           |

|--------|-----------------------------------|

|        | Audience                          |

|        | Organization                      |

|        | Notation Conventions              |

|        |                                   |

|        | Chapter 1<br>Introduction         |

| 1.1    | 56F827EVM Architecture            |

| 1.2    | 56F827EVM Configuration Jumpers   |

| 1.3    | 56F827EVM Connections             |

|        | Chapter 2 Technical Summary       |

| 2.1    | 56F827                            |

| 2.2    | Program and Data Memory           |

| 2.3    | SPI EEPROM Memory                 |

| 2.4    | RS-232 Serial Communications      |

| 2.5    | Clock Source                      |

| 2.6    | Operating Mode                    |

| 2.7    | Debug LEDs                        |

| 2.8    | Debug Support                     |

| 2.8.1  | JTAG Connector                    |

| 2.8.2  | Parallel JTAG Interface Connector |

| 2.9    | External Interrupts               |

| 2.10   | Reset2-11                         |

| 2.11   | Power Supply                      |

| 2.12   | Stereo Codec                      |

| 2.12.1 | Analog Input/Output               |

| 2.12.2 | Digital Interface                 |

| 2.13   | Daughter Card Connectors                     | 2-15 |

|--------|----------------------------------------------|------|

| 2.13.1 | Memory Daughter Card Expansion Connector     | 2-15 |

| 2.13.2 | Peripheral Daughter Card Expansion Connector | 2-17 |

| 2.14   | SCI Port #2                                  | 2-19 |

| 2.15   | Test Points                                  | 2-19 |

Appendix A 56F827EVM Schematics

Appendix B 56F827EVM Bill of Material

# **List of Figures**

| 1-1  | Block Diagram of the 56F827EVM                     | 1-2  |

|------|----------------------------------------------------|------|

| 1-2  | 56F827EVM Jumper Reference                         | 1-3  |

| 1-3  | Connecting the 56F827EVM Cables                    | 1-4  |

| 2-1  | Schematic Diagram of the External Memory Interface | 2-3  |

| 2-2  | SPI EEPROM Memory Block Diagram                    | 2-4  |

| 2-3  | Schematic Diagram of the RS-232 Interface          | 2-5  |

| 2-4  | Schematic Diagram of the Clock Interface           | 2-6  |

| 2-5  | Schematic Diagram of the Debug LED Interface       | 2-7  |

| 2-6  | Block Diagram of the Parallel JTAG Interface       | 2-9  |

| 2-7  | Schematic Diagram of the User Interrupt Interface  | 2-11 |

| 2-8  | Schematic Diagram of the RESET Interface           | 2-11 |

| 2-9  | Schematic Diagram of the Power Supply              | 2-12 |

| 2-10 | Codec Analog Connections                           | 2-13 |

| 2-11 | CS4218 Stereo Audio Codec                          | 2-14 |

## **List of Tables**

| 1-1  | 56F827EVM Default Jumper Options                 | 1-3  |

|------|--------------------------------------------------|------|

| 2-1  | SPI Port Connector Description                   | 2-4  |

| 2-2  | RS-232 Serial Connector Description              | 2-5  |

| 2-3  | Operating Mode Selection                         | 2-6  |

| 2-4  | JTAG Connector Description                       | 2-8  |

| 2-5  | Parallel JTAG Interface Disable Jumper Selection | 2-8  |

| 2-6  | Parallel JTAG Interface Connector Description    | 2-9  |

| 2-7  | Codec Sample Rate Selector                       | 2-13 |

| 2-8  | Memory Daughter Card Connector Description       | 2-16 |

| 2-9  | Peripheral Daughter Card Connector Description   | 2-18 |

| 2-10 | SCI Port #2 Connector                            | 2-19 |

#### **Preface**

This reference manual describes in detail the hardware on the 56F827 Evaluation Module.

#### **Audience**

This document is intended for application developers who are creating software for devices using the Motorola 56F827 part.

#### **Organization**

This manual is organized into two chapters and two appendixes.

- Chapter 1, Introduction provides an overview of the EVM and its features.

- Chapter 2, Technical Summary describes in detail the 56F827 hardware.

- Appendix A, 56F827EVM Schematics contains the schematics of the 56F827EVM.

- Appendix B, 56F827EVM Bill of Material provides a list of the materials used on the 56F827EVM board.

#### **Suggested Reading**

More documentation on the 56F827 and the 56F827EVM kit may be found at URL:

http://www.motorola.com/semiconductors

#### **Notation Conventions**

This manual uses the following notational conventions:

| Term or Value                   | Symbol                                                            | Examples                         | Exceptions                                                                          |

|---------------------------------|-------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------|

| Active High Signals (Logic One) | No special symbol attached to the signal name                     | A0<br>CLKO                       |                                                                                     |

| Active Low Signals (Logic Zero) | Noted with an overbar in text and in most figures                 | WE<br>OE                         | In schematic drawings,<br>Active Low Signals may be<br>noted by a backslash:<br>/WE |

| Hexadecimal<br>Values           | Begin with a "\$" symbol                                          | \$0FF0<br>\$80                   |                                                                                     |

| Decimal Values                  | No special symbol attached to the number                          | 10<br>34                         |                                                                                     |

| Binary Values                   | Begin with the letter<br>"b" attached to the<br>number            | b1010<br>b0011                   |                                                                                     |

| Numbers                         | Considered positive unless specifically noted as a negative value | 5<br>-10                         | Voltage is often shown as positive: +3.3V                                           |

| Blue Text                       | Linkable on-line                                                  | refer to Figure 1-1              |                                                                                     |

| Bold                            | Reference sources, paths, emphasis                                | see:<br>http://www.motorola.com/ |                                                                                     |

#### Definitions, Acronyms, and Abbreviations

Definitions, acronyms and abbreviations for terms used in this document are defined below for reference.

Coder/DECoder; a part used to convert analog signals to digital (Coder)

and digital signals to analog (Decoder)

**EEPROM** Electrically Erasable Programmable Read Only Memory

**EVM** Evaluation Module; a hardware platform which allows a customer to

evaluate the silicon and develop their application

**GPIO** General Purpose Input and Output Port; does not share pin functionality

with any other peripheral on the chip and can only be set as an input,

output or level-sensitive interrupt input

IC Integrated Circuit

JTAG Joint Test Action Group; a bus protocol/interface used for test and debug

**LQFP** Low-profile Quad Flat Pack

MPIO Multi-Purpose Input/Output Port; shares package pins with other

peripherals on the chip and can function as a GPIO

On-Chip Emulation, a debug bus and port created by Motorola to enable

designers to create a low-cost hardware interface for a professional

quality debug environment

PCB Printed Circuit Board

PLL Phase Locked Loop

**RAM** Random Access Memory

**ROM** Read-Only Memory

SCI Serial Communications Interface Port

SPI Serial Peripheral Interface Port

SRAM Static Random Access Memory

SSI Synchronous Serial Interface Port

WS Wait State

#### References

The following sources were referenced to produce this manual:

- [1] DSP56800 Family Manual, DSP56800FM/D

- [2] DSP56F826/827 Digital Signal Processor User's Manual, DSP56F826 827UM/D

- [3] DSP56F827 Technical Data, DSP56F827/D

# Chapter 1 Introduction

The 56F827EVM is used to demonstrate the abilities of the 56F827 and to provide a hardware tool allowing the development of applications that use the 56F827.

The 56F827EVM is an evaluation module board that includes a 56F827 part, 16-bit stereo codec, external memory and a daughter card expansion interface. The daughter card expansion connectors are for signal monitoring and user feature expandability.

The 56F827EVM is designed for the following purposes:

- Allowing new users to become familiar with the features of the 56800 architecture. The tools and examples provided with the 56F827EVM facilitate evaluation of the feature set and the benefits of the family.

- Serving as a platform for real-time software development. The tool suite enables the user to develop and simulate routines, download the software to on-chip or on-board RAM, run it, and debug it using a debugger via the JTAG/OnCE™ port. The breakpoint features of the OnCE port enable the user to easily specify complex break conditions and to execute user-developed software at full-speed, until the break conditions are satisfied. The ability to examine and modify all user accessible registers, memory and peripherals through the OnCE port greatly facilitates the task of the developer.

- Serving as a platform for hardware development. The hardware platform enables the user to connect external hardware peripherals. The on-board peripherals can be disabled, providing the user with the ability to reassign any and all of the hybrid controller's peripherals. The OnCE port's unobtrusive design means that all of the memory on the board and on the hybrid controller chip are available to the user.

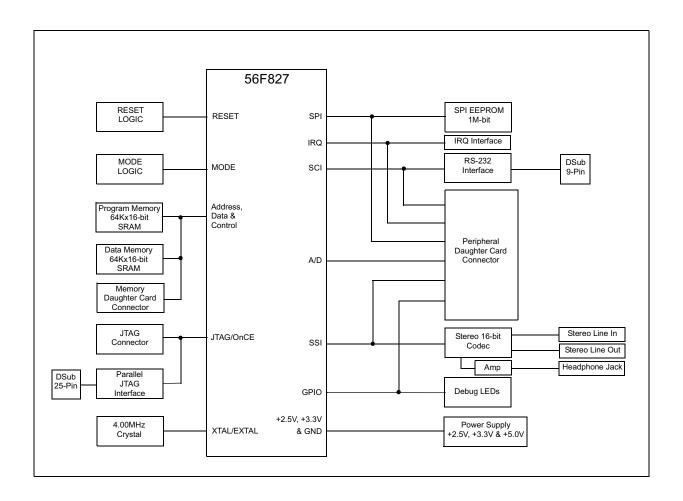

#### 1.1 56F827EVM Architecture

The 56F827EVM facilitates the evaluation of various features present in the 56F827 part. The 56F827EVM can be used to develop real-time software and hardware products based on the 56F827. The 56F827EVM provides the features necessary for a user to write and debug software, demonstrate the functionality of that software and interface with the

customer's application-specific device(s). The 56F827EVM is flexible enough to allow a user to fully exploit the 56F827's features to optimize the performance of his product, as shown in **Figure 1-1**.

Figure 1-1. Block Diagram of the 56F827EVM

#### 1.2 56F827EVM Configuration Jumpers

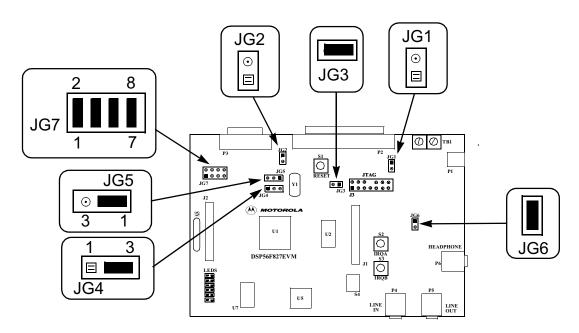

Seven jumper groups, (JG1-JG7), shown in **Figure 1-2**, are used to configure various features on the 56F827EVM board. **Table 1-1** describes the default jumper group settings.

Figure 1-2. 56F827EVM Jumper Reference

Table 1-1. 56F827EVM Default Jumper Options

| Jumper<br>Group | Comment                                                           | Jumpers<br>Connections |

|-----------------|-------------------------------------------------------------------|------------------------|

| JG1             | Enable on-board Parallel JTAG Host/Target Interface               | NC                     |

| JG2             | Enable RS-232 output                                              | NC                     |

| JG3             | Enable on-board SRAM                                              | 1–2                    |

| JG4             | Use on-board EXTAL crystal input for hybrid controller oscillator | 2–3                    |

| JG5             | Use on-board XTAL crystal input for hybrid controller oscillator  | 1–2                    |

| JG6             | Selects hybrid controller's Mode 0 operation upon exit from reset | 1-2                    |

| JG7             | Enable SPI EEPROM                                                 | 1–2, 3–4, 5–6 & 7–8    |

#### 1.3 56F827EVM Connections

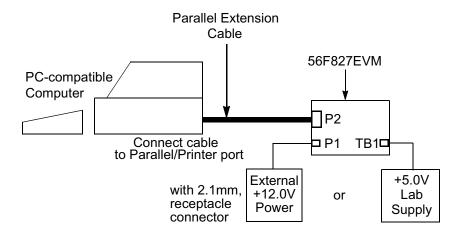

An interconnection diagram is shown in **Figure 1-3** for connecting the PC and the external +12.0V DC power supply or external +5.0V DC lab power supply to the 56F827EVM board.

Figure 1-3. Connecting the 56F827EVM Cables

Perform the following steps to connect the 56F827EVM cables:

- 1. Connect the parallel extension cable to the parallel port of the host computer.

- 2. Connect the other end of the parallel extension cable to P2, shown in **Figure 1-3**, on the 56F827EVM board. This provides the connection which allows the host computer to control the board.

- 3. Make sure that the external +12.0V DC 1.2A switching power supply or the external +5.0V DC 1.0A lab power supply is not plugged into a 120V AC power source.

- 4. Connect the 2.1mm output power plug from the external switching power supply into P1, shown in **Figure 1-3**, on the 56F827EVM board. Optionally, attach an external +5.0V DC lab power supply via the 2-pin terminal block, TB1.

- 5. Apply power to the external power supply. The green Power-On LED, LED7, will illuminate when power is correctly applied.

# Chapter 2 Technical Summary

The 56F827EVM is designed as a versatile hybrid controller development card for developing real-time software and hardware products to support a new generation of applications in digital and wireless messaging, digital answering machines, feature phones, modems, and digital cameras. The power of the 16-bit 56F827 hybrid controller, combined with the on-board 64K × 16-bit external program static RAM (SRAM), 64K × 16-bit external data SRAM, RS-232 interface, stereo 16-bit codec interface, Daughter Card Expansion interface and parallel JTAG interface, makes the 56F827EVM ideal for developing and implementing many audio and voice algorithms, as well as for learning the architecture and instruction set of the 56F827 processor.

The main features of the 56F827EVM, with board and schematic reference designators include:

- 56F827 16-bit +2.5V/+3.3V hybrid controller operating at 80MHz [U1]

- External fast static RAM (FSRAM) memory [U2], configured as:

- 64K×16 bits of program memory with 0 wait states at 70MHz

- 64K×16 bits of data memory with 0 wait states at 70MHz

- 1M-bit Serial EEPROM [U4]

- 4.00MHz crystal oscillator for hybrid controller frequency generation [Y1]

- Optional external oscillator frequency input connector [JG4 and JG5]

- Joint Test Action Group (JTAG) port interface connector for an external debug Host Target Interface [J3]

- On-board Parallel JTAG Host Target Interface, with a connector for a PC printer port cable [P2]

- RS-232 interface for easy connection to a host processor [U3 and P3]

- 16-bit stereo codec interface [U5, P4 and P5]

- Stereo headphone interface [U6 and P6]

- Codec sample rate selector [S4]

- Peripheral Daughter Card Expansion Connector, to allow the user to connect his own SCI, SSI, SPI or GPIO-compatible peripheral to the hybrid controller[J2]

- Memory Daughter Card Expansion Connector, to allow the user to connect his own memory or memory device to the hybrid controller[J1]

- On-board power regulation from an external +12V DC-supplied power input [P1]

- On-board power regulation from an optional +5V DC-supplied power input [TB1]

- Light Emitting Diode (LED) power indicator [LED7]

- Six on-board real-time user debugging LEDs [LED1-6]

- Manual RESET push-button [S1]

- Manual interrupt push-button for IRQA [S2]

- Manual interrupt push-button for IRQB [S3]

#### 2.1 56F827

The 56F827EVM uses a Motorola DSP56F827FG80 part, designated as U1 on the board and in the schematics. This part will operate at a maximum speed of 80MHz. A full description of the 56F827, including functionality and user information, is provided in these documents:

- 56F827 Technical Data, (56F827/D): Provides features list and specifications including signal descriptions, DC power requirements, AC timing requirements and available packaging.

- DSP56F826/827 16-Bit Digital Signal Processor User's Manual, (DSP56F826\_827UM/D): Provides an overview description of the hybrid controller and detailed information about the on-chip components including the memory and I/O maps, peripheral functionality, and control/status register descriptions for each subsystem.

- *DSP56800 Family Manual*, (DSP56800FM/D): Provides a detailed description of the core processor, including internal status and control registers and a detailed description of the family instruction set.

Refer to these documents for detailed information about chip functionality and operation. They can be found on this URL:

http://www.motorola.com/semiconductors

#### 2.2 Program and Data Memory

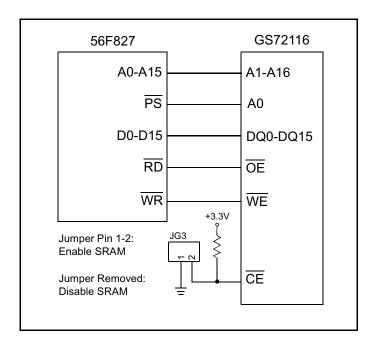

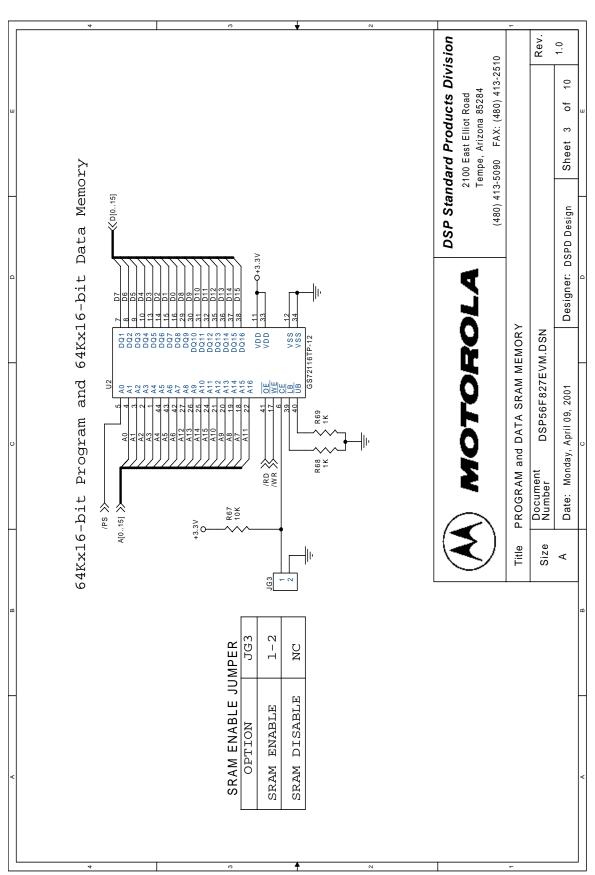

The 56F827EVM uses one bank of  $128K\times16$ -bit Fast Static RAM (GSI GS72116, labelled U2) for external memory expansion; see the FSRAM schematic diagram in **Figure 2-1**. This physical memory bank is split into two logical memory banks of 64Kx16-bits: one for program memory and the other for data memory. By using the hybrid controller's program strobe,  $\overline{PS}$ , signal line along with the memory chip's A0 signal line, half of the memory chip is selected when program memory accesses are requested and the other half of the memory chip is selected when data memory access are requested. This memory bank will operate with zero wait-state accesses while the 56F827 is running at 70MHz. However, when running at 80MHz, the memory bank operates with four wait-state accesses. This memory bank can be disabled by removing the jumper at JG3.

Figure 2-1. Schematic Diagram of the External Memory Interface

Go to: www.freescale.com

#### 2.3 SPI EEPROM Memory

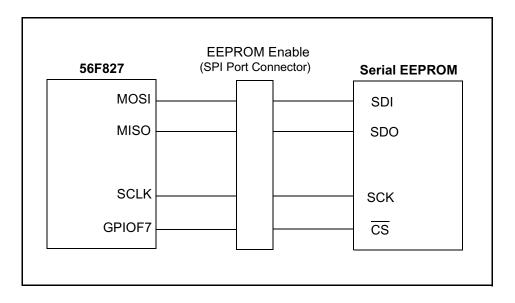

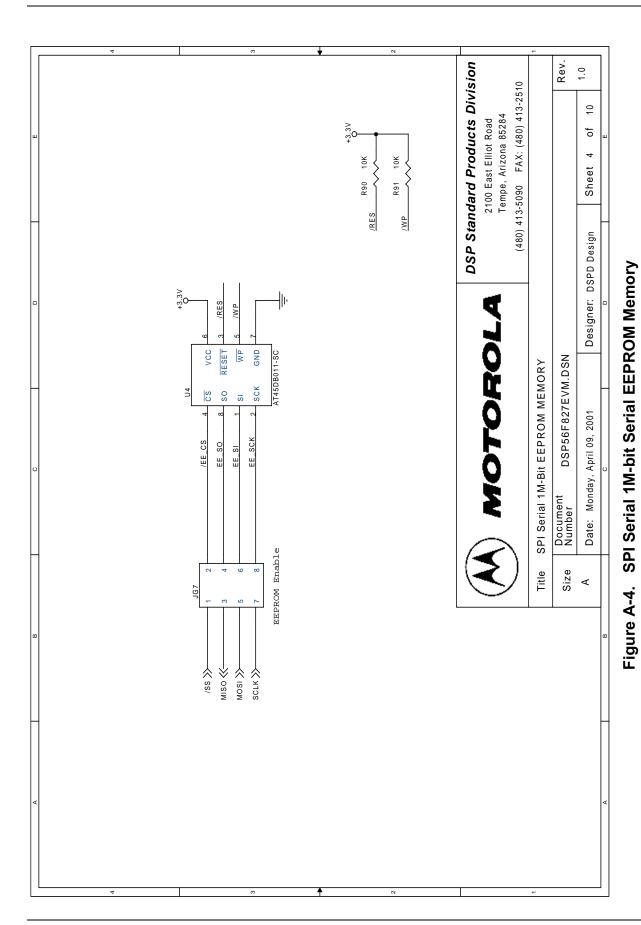

A 1M-bit +3.3V SPI serial EEPROM Memory, Atmel AT45DB011-SC, is provided on the 56F827EVM, reference **Figure 2-2**. This memory connects directly to the SPI Port through a header on the 56F827. It can be used to load program code and data into the 56F827's internal or external memory spaces. A jumper block is provided, JG7, to allow the user to disconnect the on-board SPI EEPROM from the SPI port and allow him to connect his own SPI port peripheral. The header details are shown in **Table 2-1**.

Figure 2-2. SPI EEPROM Memory Block Diagram

Table 2-1. SPI Port Connector Description

| JG7  |          |      |        |

|------|----------|------|--------|

| Pin# | Signal   | Pin# | Signal |

| 1    | SS/GPI07 | 2    | CS     |

| 3    | MISO     | 4    | SDO    |

| 5    | MOSI     | 6    | SDI    |

| 7    | SCLK     | 8    | SCK    |

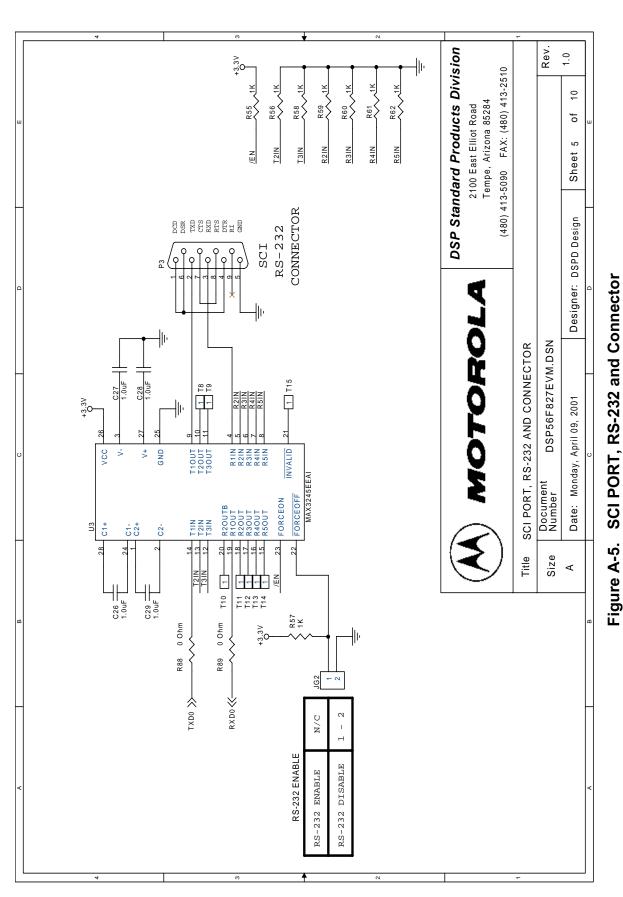

#### 2.4 RS-232 Serial Communications

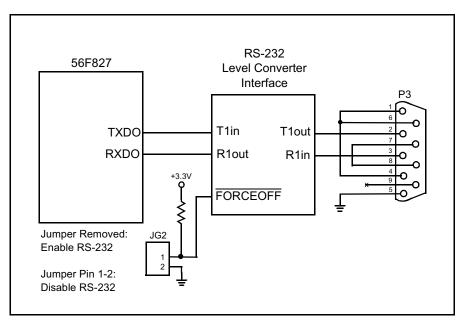

The 56F827EVM provides an RS-232 interface by the use of an RS-232 level converter, (Maxim MAX3245EEAI, designated as U3). Refer to the RS-232 schematic diagram in **Figure 2-3**. The RS-232 level converter transitions the SCI UART's +3.3V signal levels to RS-232 compatible signal levels and connects to the host's serial port via connector P3. Flow control is not provided, but could be implemented using uncommitted GPIO signals. The pinout of connector P3 is listed in **Table 2-2**. The RS-232 level converter/transceiver can be disabled by placing a jumper at JG2.

Figure 2-3. Schematic Diagram of the RS-232 Interface

| <b>Table 2-2.</b> | RS-232 Serial Connector Descript | ion |

|-------------------|----------------------------------|-----|

|                   | P3                               |     |

|      | P3              |      |                 |  |

|------|-----------------|------|-----------------|--|

| Pin# | Signal          | Pin# | Signal          |  |

| 1    | Jumper to 6 & 4 | 6    | Jumper to 1 & 4 |  |

| 2    | TXD             | 7    | Jumper to 8     |  |

| 3    | RXD             | 8    | Jumper to 7     |  |

| 4    | Jumper to 1 & 6 | 9    | N/C             |  |

| 5    | GND             |      |                 |  |

#### 2.5 Clock Source

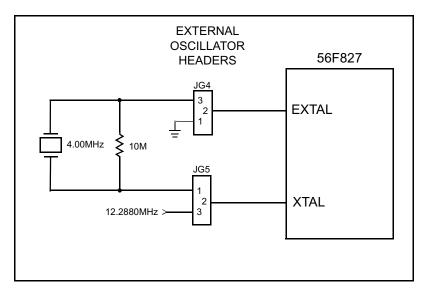

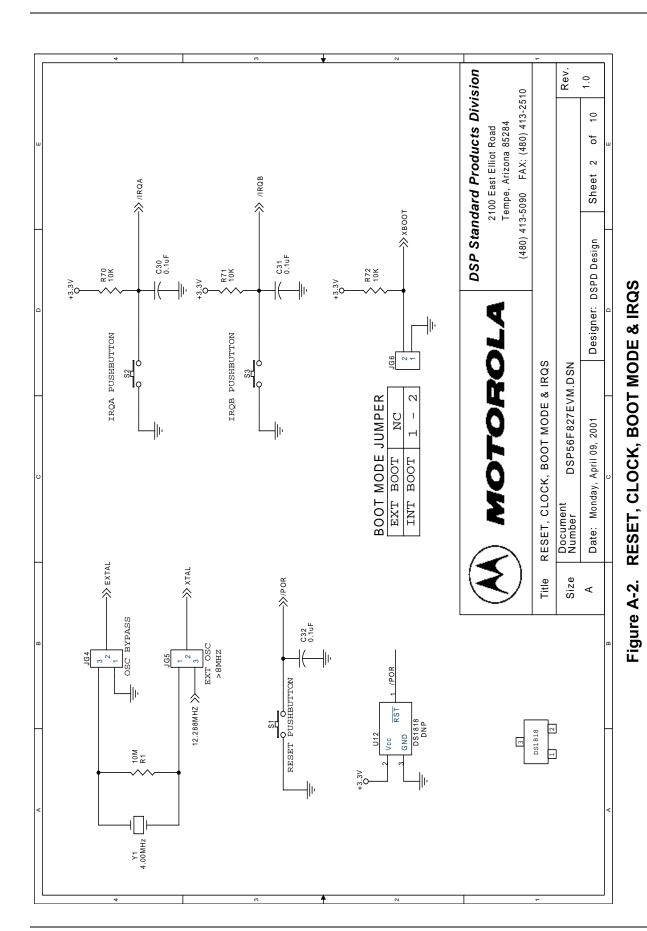

The 56F827EVM uses a 4.00MHz crystal, Y1, connected to its External Crystal Inputs, EXTAL and XTAL. The 56F827 uses its internal PLL to multiply the input frequency by 20, achieving its 80MHz maximum operating frequency. An external oscillator source can be connected to the hybrid controller by using the oscillator bypass connectors, JG4 and JG5; see Figure 2-4. If the input frequency is above 4MHz, then the EXTAL input should be jumpered to ground by adding a jumper between JG4 pins 2 and 3. The input frequency would then be injected on JG5's pin 2. If the hybrid controller needs to be synchronized to the codec's sample frequency, then the controller's input frequency should be jumpered using the 12.2280MHz codec frequency. If the input frequency is below 4MHz, then the input frequency can be injected on JG4's pin 2.

Figure 2-4. Schematic Diagram of the Clock Interface

#### 2.6 Operating Mode

The 56F827EVM provides a boot-up MODE selection jumper, JG6. This jumper is used to select the operating mode of the hybrid controller as it exits RESET. Refer to the DSP56F827 User's Manual for a complete description of the chip's operating modes. **Table 2-3** shows the two operation modes available on the 56F827.

| Operating Mode | JG6       | Comment                        |

|----------------|-----------|--------------------------------|

| 0              | 1–2       | Bootstrap from internal memory |

| 3              | No Jumper | Bootstrap from external memory |

**Table 2-3. Operating Mode Selection**

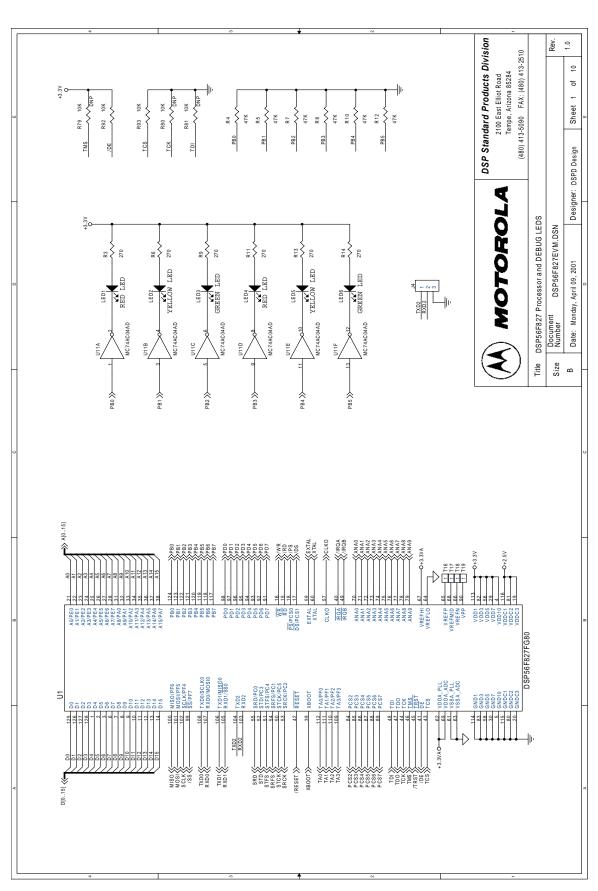

#### 2.7 Debug LEDs

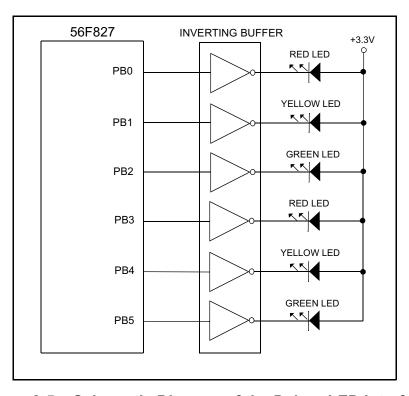

Six on-board Light-Emitting Diodes, (LEDs), are provided to allow real-time debugging for user programs. These LEDs will allow the programmer to monitor program execution without having to stop the program during debugging; refer to **Figure 2-5**. User LED1 is controlled by Port B's PB0 signal. User LED2 is controlled by PB1. User LED3 is controlled by PB2. User LED4 is controlled by PB3. User LED5 is controlled by PB4. User LED6 is controlled by PB5. Setting PB0, PB1, PB2, PB3, PB4 or PB5 to a Logic One value will turn on the associated LED.

Figure 2-5. Schematic Diagram of the Debug LED Interface

#### 2.8 Debug Support

The 56F827EVM provides an on-board Parallel JTAG Host Target Interface and a JTAG interface connector for external Target Interface support. Two interface connectors are provided to support each of these debugging approaches. These two connectors are designated the JTAG connector and the Host Parallel Interface Connector.

Go to: www.freescale.com

#### 2.8.1 JTAG Connector

The JTAG connector on the 56F827EVM allows the connection of an external Host Target Interface for downloading programs and working with the 56F827's registers. This connector is used to communicate with an external Host Target Interface which passes information and data back and forth with a host processor running a debugger program.

Table 2-4 shows the pin-out for this connector.

**Table 2-4. JTAG Connector Description**

| J3   |                           |    |      |  |  |

|------|---------------------------|----|------|--|--|

| Pin# | Pin # Signal Pin # Signal |    |      |  |  |

| 1    | TDI                       | 2  | GND  |  |  |

| 3    | TDO                       | 4  | GND  |  |  |

| 5    | TCK                       | 6  | GND  |  |  |

| 7    | NC                        | 8  | KEY  |  |  |

| 9    | RESET                     | 10 | TMS  |  |  |

| 11   | +3.3V                     | 12 | NC   |  |  |

| 13   | NC                        | 14 | TRST |  |  |

When this connector is used with an external Host Target Interface, the parallel JTAG interface should be disabled by placing a jumper in jumper block JG1. See **Table 2-5** for this jumper's selection options.

Table 2-5. Parallel JTAG Interface Disable Jumper Selection

| JG1        | Comment                                  |

|------------|------------------------------------------|

| No jumpers | On-board Parallel JTAG Interface Enabled |

| 1–2        | Disable on-board Parallel JTAG Interface |

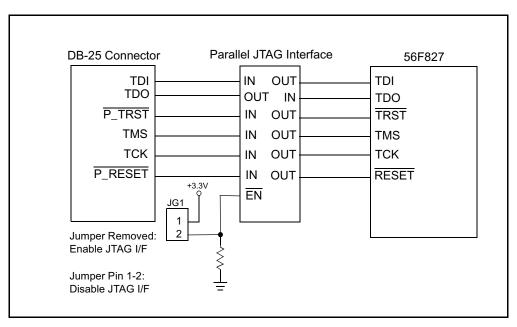

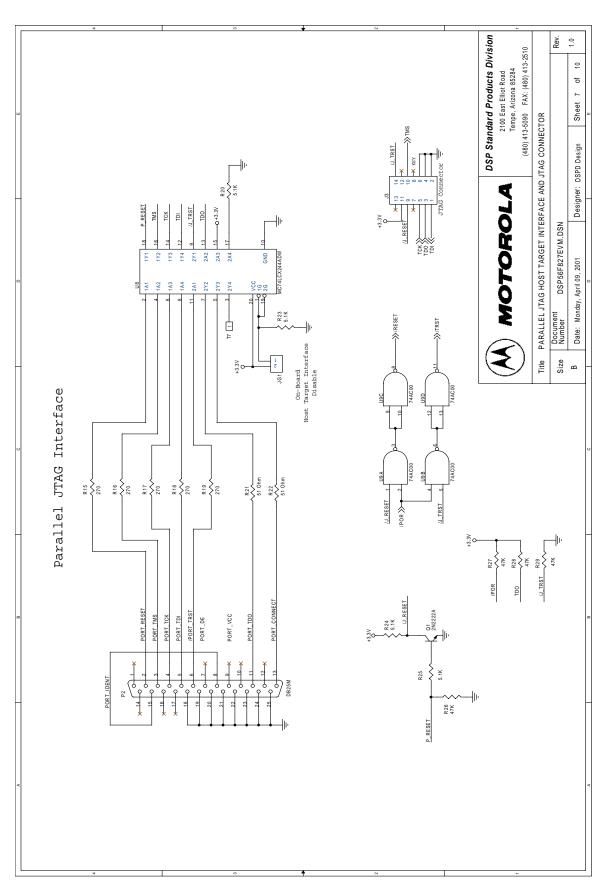

#### 2.8.2 Parallel JTAG Interface Connector

The Parallel JTAG Interface Connector, P2, allows the 56F827 to communicate with a Parallel Printer Port on a Windows PC; reference **Figure 2-6**. By using this connector, the user can download programs and work with the 56F827's registers. **Table 2-6** shows the pin-out for this connector. When using the parallel JTAG interface, the jumper at JG1 should be removed, as shown in **Table 2-5**.

Figure 2-6. Block Diagram of the Parallel JTAG Interface

Table 2-6. Parallel JTAG Interface Connector Description

| P2    |            |      |            |

|-------|------------|------|------------|

| Pin # | Signal     | Pin# | Signal     |

| 1     | NC         | 14   | NC         |

| 2     | PORT_RESET | 15   | PORT_IDENT |

| 3     | PORT_TMS   | 16   | NC         |

| 4     | PORT_TCK   | 17   | NC         |

| 5     | PORT_TDI   | 18   | GND        |

| 6     | PORT_TRST  | 19   | GND        |

| 7     | NC         | 20   | GND        |

| 8     | PORT_IDENT | 21   | GND        |

| 9     | PORT_VCC   | 22   | GND        |

**Table 2-6. Parallel JTAG Interface Connector Description**

| P2   |              |      |        |

|------|--------------|------|--------|

| Pin# | Signal       | Pin# | Signal |

| 10   | NC           | 23   | GND    |

| 11   | PORT_TDO     | 24   | GND    |

| 12   | NC           | 25   | GND    |

| 13   | PORT_CONNECT |      |        |

#### 2.9 External Interrupts

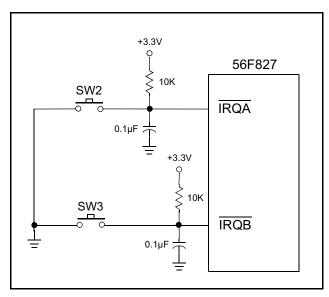

Two on-board push-button switches are provided for external interrupt generation, as shown in **Figure 2-7**. S2 allows the user to generate a hardware interrupt for signal line  $\overline{IRQA}$ . S3 allows the user to generate a hardware interrupt for signal line  $\overline{IRQB}$ . These two switches allow the user to generate interrupts for his user-specific programs.

Figure 2-7. Schematic Diagram of the User Interrupt Interface

#### 2.10 Reset

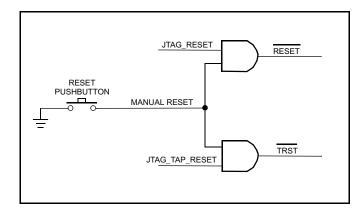

Logic is provided on the 56F827 to generate an internal Power-On RESET. Additional reset logic is provided to support the RESET signals from the JTAG connector, the Parallel JTAG Interface and the user RESET push-button; refer to **Figure 2-8**.

Figure 2-8. Schematic Diagram of the RESET Interface

Go to: www.freescale.com

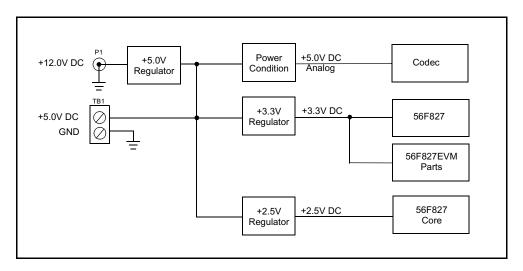

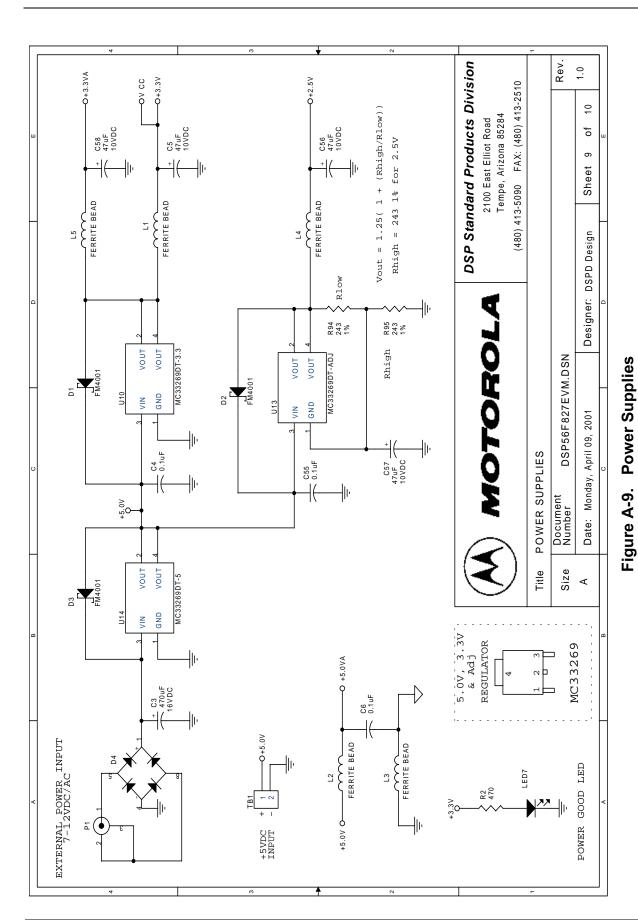

#### 2.11 Power Supply

The main power input, +12.0V DC, to the 56F827EVM is through a 2.1mm coax power jack, P1. An optional +5.0V DC power supply input is available through a 2-pin terminal block, TB1. A 1.2A power supply is provided with the 56F827EVM; however, less than 500mA is required by the EVM. The remaining current is available for user daughter card applications when connected to the daughter card interface. The power regulation on the 56F827EVM provides +5.0V DC voltage regulation for the codec's analog circuits and to the additional voltage regulation logic on the EVM. The additional voltage regulation logic provides +2.5V DC voltage regulation for the hybrid controller's core and +3.3V DC voltage regulation for the controller's I/O, memory, parallel JTAG interface and supporting logic; refer to Figure 2-9. Power applied to the 56F827EVM is indicated with a Power-On LED, referenced as LED7.

Figure 2-9. Schematic Diagram of the Power Supply

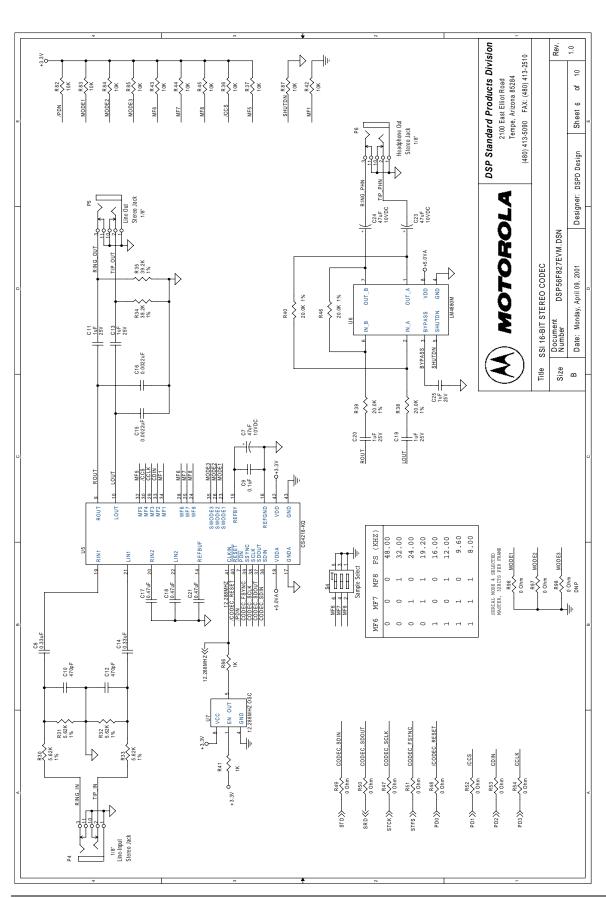

#### 2.12 Stereo Codec

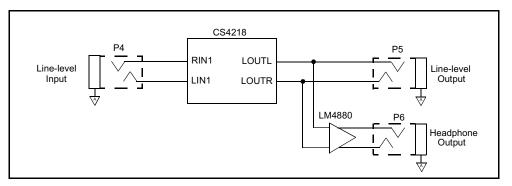

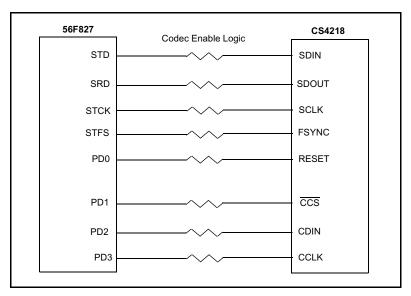

A 16-bit audio quality stereo codec, Crystal Semiconductor CS4218, is connected to the 56F827's SSI port to support audio, voice and signal analysis applications. The codec is clocked with a 12.288MHz oscillator. This allows the codec to operate between a sample frequency of 8kHz and 48kHz. The sample rate can be manually set by setting the appropriate switch positions on dip switch S4. The sample rate selections possible using this three-position dip switch are detailed in **Table 2-7**. The codec supports +3.3V digital levels, eliminating the need for voltage-level translation circuitry. Additionally, a set of zero ohm resistors are provided on the EVM to allow a user to disconnect the on-board codec from the SSI port and to connect his own codec to the SSI port; refer to **Figure 2-11**. The on-board codec has analog signal conditioning logic, allowing direct

connection to its line-level input and line-level output signals through two 1/8" stereo jacks; see Figure 2-10.

Table 2-7. Codec Sample Rate Selector

| SW 4<br>Position 3<br>(MF6) | SW 4<br>Position 2<br>(MF7) | SW 4<br>Position 1<br>(MF8) | Sample Rate |

|-----------------------------|-----------------------------|-----------------------------|-------------|

| ON                          | ON                          | ON                          | 48.00kHz    |

| ON                          | ON                          | OFF                         | 32.00kHz    |

| ON                          | OFF                         | ON                          | 24.00kHz    |

| ON                          | OFF                         | OFF                         | 19.20kHz    |

| OFF                         | ON                          | ON                          | 16.00kHz    |

| OFF                         | ON                          | OFF                         | 12.00KHz    |

| OFF                         | OFF                         | ON                          | 9.60kHz     |

| OFF                         | OFF                         | OFF                         | 8.00kHz     |

Figure 2-10. Codec Analog Connections

Go to: www.freescale.com

Figure 2-11. CS4218 Stereo Audio Codec

#### 2.12.1 Analog Input/Output

The 56F827EVM uses jacks for line-level stereo input, line-level stereo output and stereo headphone output. A National Semiconductor LM4880 is used to provide the drive required for the use of headphones. This device offers a THD, which is superior to the CS4218's on-chip headphone drive circuitry by a factor of two. The basic Analog codec connections are shown in **Figure 2-10**.

#### 2.12.2 Digital Interface

The serial interface of the codec transfers digital audio data and control data into and out of the device. The SSI port, which consists of independent transmitter and receiver sections, is used for serial communication with the codec.

On the hybrid controller side, the Serial Transmit Data pin, STD, is an output when data is being transmitted to the codec. The Serial Receive Data pin, SRD, is an input when data is being received from the codec. These two pins are connected to the codec's Serial Data Input pin, SDIN, and Serial Data Output pin, SDOUT.

The controller's Transmit Serial Clock pin, STCK, provides the serial bit rate clock for the SSI interface. It is connected to the codec's Serial Port Clock pin, SCLK. Data is transmitted on the rising edge of SCLK and is received on the falling edge of SCLK.

The device's GPIO PORT D Bit 0 pin, PD0, is programmed to control the codec's Active Low Reset signal, RESET.

The Serial Transmit Frame Sync pin, STFS, is programmed to control the codec's Frame Sync signal, FSYNC. FSYNC is sampled by SCLK, with a rising edge indicating a new frame is about to start. The FSYNC frequency is always the system's sample rate. It may be an input to the codec, or it may be an output from the codec in data mode.

The basic codec digital connections are shown in Figure 2-11.

The codec's MODE is set by the three MODE selection resistors, R96-R98. In the factory default setting of MODE 4, the codec is set to be the Master of the SPI bus with its data word set at 32 bits per frame; i.e., a 16-bit Left channel and a 16-bit Right channel. The sample rate is selected on Sample Rate Selector switch S4; reference **Table 2-7** for selection options. Codec control information is sent over a separate serial port using: PD1 as the Control Chip Select signal, CCS; PD2 as the Control Data Input signal, CDIN; and PD3 as the Control Clock signal, CCLK.

#### 2.13 Daughter Card Connectors

The EVM board contains two daughter card expansion connectors. One connector, J1, contains the hybrid controller's external memory bus signals. The other connector, J2, contains the device's peripheral port signals.

#### 2.13.1 Memory Daughter Card Expansion Connector

The hybrid controller's external memory bus signals are connected to the Memory Daughter Card Expansion connector, J1. **Table 2-8** shows the port signal to pin assignments.

**Table 2-8. Memory Daughter Card Connector Description**

| J1   |        |       |        |

|------|--------|-------|--------|

| Pin# | Signal | Pin # | Signal |

| 1    | A10    | 2     | A11    |

| 3    | A9     | 4     | DS     |

| 5    | A8     | 6     | A15    |

| 7    | A7     | 8     | A14    |

| 9    | GND    | 10    | PCS7   |

| 11   | WR     | 12    | A13    |

| 13   | D0     | 14    | A12    |

| 15   | D1     | 16    | D8     |

| 17   | D2     | 18    | D9     |

| 19   | GND    | 20    | GND    |

| 21   | D3     | 22    | D10    |

| 23   | D4     | 24    | D11    |

| 25   | D5     | 26    | D12    |

| 27   | D6     | 28    | D13    |

| 29   | PCS6   | 30    | PCS5   |

| 31   | D7     | 32    | D14    |

| 33   | PS     | 34    | D15    |

| 35   | A0     | 36    | RD     |

| 37   | A1     | 38    | A6     |

| 39   | PCS4   | 40    | GND    |

| 41   | A2     | 42    | A5     |

| 43   | A3     | 44    | A4     |

| 45   | PCS3   | 46    | PCS2   |

| 47   | +3.3V  | 48    | +3.3V  |

| 49   | GND    | 50    | GND    |

| 51   | GND    |       |        |

#### 2.13.2 Peripheral Daughter Card Expansion Connector

The hybrid controller's peripheral port signals are connected to the Peripheral Daughter Card Expansion connector, J2. **Table 2-9** shows the port signal to pin assignments.

Go to: www.freescale.com

Table 2-9. Peripheral Daughter Card Connector Description

|      |        | J2    |        |

|------|--------|-------|--------|

| Pin# | Signal | Pin # | Signal |

| 1    | PB0    | 2     | PB1    |

| 3    | CLKO   | 4     | PB2    |

| 5    | TA0    | 6     | TA1    |

| 7    | PB3    | 8     | PB4    |

| 9    | TA2    | 10    | TA3    |

| 11   | PB5    | 12    | PB6    |

| 13   | ANA0   | 14    | ANA1   |

| 15   | SRD    | 16    | PB7    |

| 17   | SRFS   | 18    | PD0    |

| 19   | SCLK   | 20    | PD1    |

| 21   | ANA2   | 22    | ANA3   |

| 23   | MOSI   | 24    | PD2    |

| 25   | MISO   | 26    | PD3    |

| 27   | ANA4   | 28    | ANA5   |

| 29   | SS     | 30    | PD4    |

| 31   | SRCK   | 32    | PD5    |

| 33   | STFS   | 34    | PD6    |

| 35   | RESET  | 36    | PD7    |

| 37   | ANA6   | 38    | ANA7   |

| 39   | STD    | 40    | RXD1   |

| 41   | STCK   | 42    | TXD1   |

| 43   | ĪRQB   | 44    | RXD0   |

| 45   | ĪRQĀ   | 46    | TXD0   |

| 47   | +3.3V  | 48    | +3.3V  |

| 49   | ANA8   | 50    | ANA9   |

| 51   | GND    |       |        |

#### 2.14 SCI Port #2

A separate connector, J4, is provided to allow the easy connection of SCI Port #2 signals along with a reference GND signal.

Table 2-10. SCI Port #2 Connector

| J4 | Signal Description |  |

|----|--------------------|--|

| 1  | TXD2               |  |

| 2  | RXD2               |  |

| 3  | GND                |  |

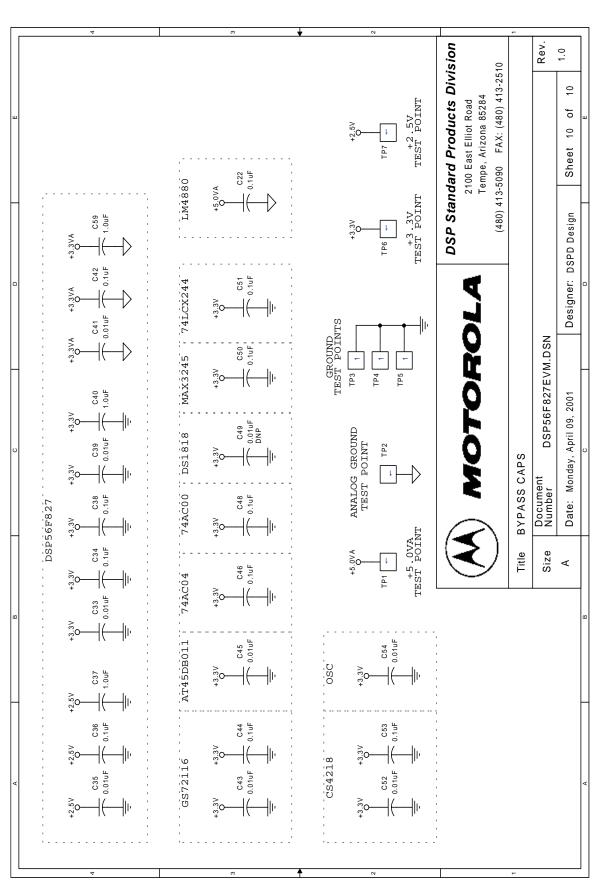

#### 2.15 Test Points

The 56F827EVM board has a total of seven test points. Three digital GND test points are located in corners of the board. The +5.0VA and AGND test points are located in the bottom right, analog corner, of the board. The +2.5V and +3.3V test points are located in the upper right, power supply section, of the board.

Go to: www.freescale.com

# **Appendix A 56F827EVM Schematics**

Figure A-1. 56F827 Processor and DEBUG LEDS

MOTOROLA

Figure A-3. PROGRAM & DATA SRAM MEMORY

MOTOROLA

MOTOROLA

Figure A-6. SSI 16-Bit Stereo Codec

Figure A-7. Parallel JTAG Host Target Interface and JTAG Connector

A-9

A-10

Figure A-10. Bypass Caps

# Appendix B 56F827EVM Bill of Material

| Qty                 | Description             | Ref. Designators                       | Vendor Part #                    |

|---------------------|-------------------------|----------------------------------------|----------------------------------|

| Integrated Circuits |                         |                                        |                                  |

| 1                   | DSP56F827FG80           | U1                                     | Motorola, DSP56F827FG80          |

| 1                   | GS72116                 | U2                                     | GSI, GS72116TP-12                |

| 1                   | MAX3245                 | U3                                     | Maxim, MAX3245EEAI               |

| 1                   | AT45DB011               | U4                                     | Atmel, AT45DB011-SC              |

| 1                   | CS4218                  | U5                                     | Crystal Semiconductor, CS4218-KQ |

| 1                   | LM4880                  | U6                                     | National Semiconductor, LM4880M  |

| 1                   | 12.288MHZ OSC           | U7                                     | Epson, SG-531P-12.288MC          |

| 1                   | 74LCX244                | U8                                     | ON Semiconductor, MC74LCX244ADW  |

| 1                   | 74AC00                  | U9                                     | Fairchild, 74AC00SC              |

| 1                   | +3.3V Voltage Regulator | U10                                    | ON Semiconductor, MC33269DT-3.3  |

| 1                   | 74AC04                  | U11                                    | ON Semiconductor, MC74AC04AD     |

| 1                   | +2.5V Voltage Regulator | U13                                    | ON Semiconductor, MC33269DT-ADJ  |

| 1                   | +5.0V Voltage Regulator | U14                                    | ON Semiconductor, MC33269DT-5    |

| Resistors           |                         |                                        |                                  |

| 1                   | 10Μ Ω                   | R1                                     | SMEC, RC73L2A10MOHMJT            |

| 1                   | 470 Ω                   | R2                                     | SMEC, RC73L2A470OHMJT            |

| 11                  | 270 Ω                   | R3, R6, R9, R11, R13 - R19             | SMEC, RC73L2A270OHMJT            |

| 10                  | 47Κ Ω                   | R4, R5, R7, R8, R10, R12,<br>R26 - R29 | SMEC, RC73L2A47KOHMJT            |

| 4                   | 5.1Κ Ω                  | R20, R23 - R25                         | SMEC, RC73L2A5.1KOHMJT           |

| 2                   | 51 Ω                    | R21, R22                               | SMEC, RC73L2A51OHMJT             |

| Qty   | Description           | Ref. Designators                                                     | Vendor Part #                |

|-------|-----------------------|----------------------------------------------------------------------|------------------------------|

| 4     | 5.62K Ω, 1%           | R30 - R33                                                            | SMEC, RC73L2A5.62KOHMFT      |

|       |                       | Resistors (Continued)                                                |                              |

| 2     | 39.2K Ω, 1%           | R34, R35                                                             | SMEC, RC73L2A39.2KOHMFT      |

| 19    | 10Κ Ω                 | R36, R37, R42 - R45, R67,<br>R70 - R72, R82 - R85, R87,<br>R90 - R93 | SMEC, RC73L2A10KOHMJT        |

| 4     | 20.0Κ Ω, 1%           | R38 - R40, R46                                                       | SMEC, RC73L20.0KOHMFT        |

| 12    | 1ΚΩ                   | R41, R55 - R62, R68, R69,<br>R86                                     | SMEC, RC73L2A1KOHMJT         |

| 12    | 0 Ω                   | R47 - R54, R88, R89, R96,<br>R97                                     | SMEC, RC73JP2A               |

| 2     | 243 Ω, 1%             | R94, R95                                                             | SMEC, RC73L243OHMFT          |

|       |                       | Inductors                                                            |                              |

| 4     | 1.0mH FERRITE BEAD    | L1, L2, L3, L4                                                       | Panasonic, EXC-ELSA35V       |

| LEDs  |                       |                                                                      |                              |

| 2     | Red LED               | LED1, LED4                                                           | Hewlett-Packard, HSMS-C650   |

| 2     | Yellow LED            | LED2, LED5                                                           | Hewlett-Packard, HSMY-C650   |

| 3     | Green LED             | LED3, LED6, LED7                                                     | Hewlett-Packard, HSMG-C650   |

| Diode |                       |                                                                      |                              |

| 2     | S2B-FM401             | D1, D2, D3                                                           | Vishay, DL4001DICT           |

| 1     | 1Amp Bridge Rectifier | D4                                                                   | General Semiconductor, DF02S |

| Qty | Description    | Ref. Designators                                                                           | Vendor Part #        |  |

|-----|----------------|--------------------------------------------------------------------------------------------|----------------------|--|

|     | Capacitors     |                                                                                            |                      |  |

| 1   | 470μF, +16V DC | C3                                                                                         | ELMA, RV-16V471MH10R |  |

| 18  | 0.1μF          | C4, C6, C9, C22, C30 - C32,<br>C34, C36, C38, C42, C44,<br>C46, C48, C50, C51, C53,<br>C55 | SMEC, MCCE104K2NR-T1 |  |

| 7   | 47μF, +16V DC  | C5, C7, C23, C24, C56, C57,<br>C58                                                         | ELMA, RV2-16V470M-R  |  |

| 2   | 0.33μF         | C8, C14                                                                                    | SMEC, MCCE334K3NR-T1 |  |

| 2   | 470pF          | C10, C12                                                                                   | SMEC, MCCE471J2NO-T1 |  |

| 12  | 1.0μF, +25V DC | C11, C13, C19, C20, C25 -<br>C29, C37, C40, C59                                            | SMEC, MCCE105K3NR-T1 |  |

| 2   | 0.0022μF       | C15, C16                                                                                   | SMEC, MCCE222K2NR-T1 |  |

| 3   | 0.47μF         | C17, C18, C21                                                                              | SMEC, MCCE474K3NR-T1 |  |

| 9   | 0.01μF         | C33, C35, C39, C41, C43,<br>C45, C49, C52, C54                                             | SMEC, MCCE103K2NR-T1 |  |

| Qty        | Description                   | Ref. Designator | Vendor Part #             |  |

|------------|-------------------------------|-----------------|---------------------------|--|

|            | Jumpers                       |                 |                           |  |

| 4          | 1 × 2, 2mm Header             | JG1 - JG3, JG6  | SAMTEC, TMM-102-03-S-S    |  |

| 2          | 3 × 1, 2mm Header             | JG4, JG5        | SAMTEC, TMM-103-03-S-S    |  |

| 1          | 4 × 2, 2mm Header             | JG7             | SAMTEC, TMM-104-03-S-D    |  |

|            | Test Points                   |                 |                           |  |

| 7          | 1 × 1, Pin                    | TP1 - TP7       | Samtec, TSW-101-06-S-S    |  |

|            |                               | Crystals        |                           |  |

| 1          | 4.00MHz Crystal               | Y1              | CTS, ATS04ASM-T           |  |

| Connectors |                               |                 |                           |  |

| 1          | 2.1mm coax<br>Power Connector | P1              | Switchcraft, RAPC-722     |  |

| 1          | DB25M Connector               | P2              | AMPHENOL, 617-C025P-AJ121 |  |

| Qty | Description          | Ref. Designator | Vendor Part #                   |

|-----|----------------------|-----------------|---------------------------------|

| 1   | DE9S Connector       | P3              | AMPHENOL, 617-C009S-AJ120       |

| 3   | 1/8" Stereo Jack     | P4 - P6         | Switchcraft, 35RAPC4BHN2        |

| 2   | 51-Pin HD Connector  | J1, J2          | FCI Framatome Conn, 91930-21151 |

| 1   | 7 x 2 Bergstick      | J3              | SAMTEC, TSW-107-07-S-D          |

| 1   | 2-Pin Terminal Block | TB1             | On-Shore Technology, ED500/2DS  |

|     |                      | Switches        |                                 |

| 3   | SPST Pushbutton      | S1 - S3         | Panasonic, EVQ-PAD05R           |

| 1   | 3-Position DIP SW    | S4              | CTS, 209-3LPST                  |

|     |                      | Transistors     |                                 |

| 1   | 2N2222A              | Q1              | ZETEX, FMMT2222ACT              |

|     |                      | Miscellaneous   | ·                               |

| 8   | 2mm Shunt            | SH1-SH8         | Samtec, 2SN-BK-T                |

| 4   | Rubber Feet          | RF1–RF4         | 3M, SJ5018BLKC                  |

## Index

| Numerics                                                                                                                                                                               | l                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 1.2A power supply 2-12 16-bit 2.5V/3.3V hybrid controller 2-1 16-bit stereo codec interface 2-1 1M-bit Serial EEPROM 2-1 4.00MHz crystal oscillator 2-1 64Kx16 bits of data memory 2-1 | IC IC viii Integrated Circuit viii  J               |

| 64Kx16 bits of program memory 2-1                                                                                                                                                      | Joint Test Action Group ix JTAG 1-1, 2-1            |

| С                                                                                                                                                                                      | connector 2-8 JTAG ix                               |

| Codec viii                                                                                                                                                                             | JTAG port interface 2-1                             |

| D                                                                                                                                                                                      | Jumper Group 1-3 JG1 1-3 JG2 1-3                    |

| Data memory 2-3 Daughter Card Expansion interface 2-1 Debugging 2-7 Development Card 2-1                                                                                               | JG2 1-3<br>JG3 1-3<br>JG4 1-3<br>JG5 1-3<br>JG6 1-3 |

| E                                                                                                                                                                                      | JG7 1-3                                             |

| EEPROM EEPROM viii Electrically Erasable Programmable Read Only Memory viii Evaluation Module viii EVM EVM viii                                                                        | L Low-profile Quad Flat Pack ix LQFP LQFP ix  M     |

| External oscillator frequency input 2-1                                                                                                                                                | MPIO                                                |

| F                                                                                                                                                                                      | MPIO ix<br>Multi-Purpose Input/Output port ix       |

| FSRAM 2-1, 2-3                                                                                                                                                                         | 0                                                   |

| G                                                                                                                                                                                      | On-board power regulation 2-2<br>OnCE 1-1           |

| General Purpose Input/Output port viii<br>GPIO 2-2<br>GPIO viii                                                                                                                        | OnCE(TM) OnCE ix On-Chip Emulation ix               |

| Н                                                                                                                                                                                      | Operating Mode 2-6                                  |

| Host Parallel Interface Connector 2-7<br>Host Target Interface 2-7                                                                                                                     | Parallel JTAG Host Target Interface 2-1             |

```

PCB

PCB ix

Phase Locked Loop ix

PLL

PLL ix

Printed Circuit Board ix

Program memory 2-3

R

RAM

RAM ix

Random Access Memory ix

Read-Only Memory ix

Real-time debugging 2-7

ROM

ROM ix

RS-232

interface 2-1, 2-5

level converter 2-5

schematic diagram 2-5

RS-232 interface 2-1

RS-232 Serial Communications 2-5

S

SCI

SCI ix

SCI-compatible peripheral 2-2

Serial Communications Interface port ix

Serial Peripheral Interface port ix

SPI 2-2

SPI ix

SRAM

external data 2-1

external program 2-1

SRAM ix

SSI 2-2

SSI ix

Static Random Access Memory ix

Stereo 16-bit codec interface 2-1

Stereo headphone interface 2-1

Synchronous Serial Interface port ix

W

Wait State ix

WS

WS ix

```

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and b are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

MOTOROLA and the Stylized M Logo are registered in the US Patent & Trademark Office. All other product or service names are the property of their respective owners. © Motorola, Inc. 2003.

How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1-303-675-2140 or 1-800-441-2447

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu. Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26668334

Technical Information Center: 1–800–521–6274

HOME PAGE: http://www.motorola.com/semiconductors/