## 64 BIT SERIAL EEPROM

### **Features**

- · 64 bit serial organisation

- Bits individually addressable

- 2 Volt operation

- 100 000 erase/write cycles

- Self timed programming cycle

- 10 nA (typ.) stand-by current

- 8 pin package

- 10 years data retention time

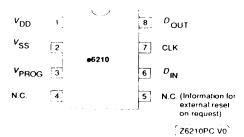

## Pad configuration

# General description

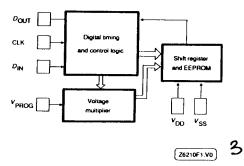

The e6210 is a 64 bit serial EEPROM, produced in low voltage CMOS Silicon Gate Technology. The addressing scheme allows bit-wise access and an arbitary number of bits can be simultaneously written (or erased). Integrated on chip is all the necessary

circuitry for operation of the EEPROM memory e.g. high voltage generation, timing logic for generation of the write/erase pulses and control logic for serial data transport.

# Absolute maximum ratings

| Supply voltage (V pp. V ss)                                                                                       |

|-------------------------------------------------------------------------------------------------------------------|

| Input voltage range, all inputs $(V_{SS}-0.3 \text{ V}) \leq (V_{DD}+0.3 \text{ V})$                              |

| Output short circuit duration indefinite                                                                          |

| Power dissipation (DIL package)                                                                                   |

| Operating ambient temperatur range                                                                                |

| Storage temperature range                                                                                         |

| Lead temperature during soldering at 2 mm distance, 10 sec                                                        |

| Absolute maximum ratings define parameter limits which, if exceeded, may permanently change or damage the device. |

All inputs and outputs on EUROSIL electronic GmbH circuits are highly protected against electrostatic discharges However, precautions to minimize build-up of electrostatic charges during handling are recommended.

The circuits are protected against supply voltage reversal for typically 5 minutes

EUROSIL electronic GmbH Erfurter Strasse 16 D-8057 Eching

Telefon: (089) 319 06-0 Telefax: (089) 319 46 21 Telex: 522 432 EUROSIL ELECTRONIC LIMITED Room 709 Chinachem Golden Plaza 77 Mody Road, Tsim Sha Tsui East Woulden Hong Kennes

Kowloon, Hong Kong Phone: 3-722 1306-9 Telefax: 3-721 48 43 Telex 33 448

<sup>\*</sup> This value applies only to the package and will not be reached under normal operating conditions

## **Functional description**

#### Memory cell

As well as the actual storage medium (FLOTOX cell), the memory cell contains a dynamic shift register for data transfer. Therefore the clock frequency for a serial data transfer must not be less than 20 kHz. After reading in the data, the dynamic shift register is configured to be a static latch, which stores the information during the write and erase cycles. Through these measures an extremely low current consumption is achieved, because current only flows during the (short) read pulse and during serial data transfer. For the rest of the time the circuit works completely statically, i.e. only leakage current flows.

#### **HV-generator**

The HV-generator produces the high voltage (-18 V) necessary for writing/erasing the EERPOM cells. The required supply voltage  $V_{\rm PROG}$  is -5 V  $\pm 10\%$ . To operate the complete circuit over a wide range of supply voltages, the supply voltage  $V_{\rm PROG}$  has a separate connection. The  $V_{\rm PROG}$  connection must only be at -5 V during programming, in normal operation it may remain unconnected. If the whole system always runs at 5 V,  $V_{\rm PROG}$  can be connected to  $V_{\rm SS}$ .

#### Control logic

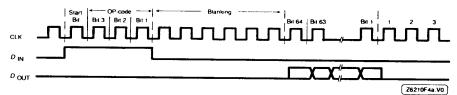

The control logic provides all the necessary timing signals for serial data transfer, write/erase pulse width definition, read pulse sequence and OP-code decoding. A start bit and a 3 bit OP-code is used for the different operating modes (write/erase etc.). The clock input signal CLK is used as a timebase. Since all times/delays are not critical (including duration of write/erase pulses), the clock frequency may vary over a relatively wide range. After power up the chip has an initialization phase which lasts a maximum of 400 µsecs. During this time the chip can accept no OP-codes.

#### OP-code

A 3 bit OP-code is used to select the required operation modes. A LO to HI transition on D in prior to the 3 OP-code bits (during CLK = LO) is recognized as start condition. The OP-code definition is as follows:

| OP-code | Bit 3 | Bit 2 | Bit 1 | Function                             |

|---------|-------|-------|-------|--------------------------------------|

| OP0     | 0     | 0     | 0     | Reserved code                        |

| OP1     | 0     | 0     | 1     | Reserved code                        |

| OP2     | 0     | 1     | 0     | Load shift register and write EEPROM |

| OP3     | 0     | 1     | 1     | Load shift register and erase EEPROM |

| OP4     | 1     | 0     | 0     | Reserved code                        |

| OP5     | 1     | 0     | 1     | Reserved code                        |

| OP6     | 1     | 1     | 0     | Reserved code                        |

| OP7     | 1     | 1     | 1     | Read and shift out                   |

Following is a detailed description of all OP-codes and how they perform:

#### OP2

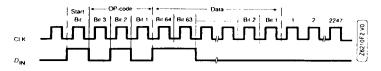

Loads the shift register via the serial interface and performs a write operation. Bits to be written into the EEPROM have to be entered as logical HI into the shift register (see Figure 2). Bits that remain at LO will not be modified, i.e. the corresponding EEPROM cell remains in its previous state (written or erased).

#### OP3

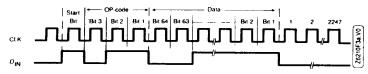

Loads the shift register via the serial interface and performs an erase operation. Bits to be erased in the EEPROM have to be entered as logical LO into the shift register (see Figure 3a and Figure 3b). Bits that remain HI will not be modified, i.e. the corresponding EEPROM cell remains in its previous state (written or erased).

#### OP7

Is the read operation (see Figure 4a and Figure 4b). The EEPROM contents are transferred to the shift register and then after a delay of 6 clocks, serially shifted out.

# **Operating characteristics**

$V_{\rm DD}=0$  V (reference potential);  $V_{\rm SS}=-5.0$  V;  $V_{\rm PROG}=-5$  V;  $T_{\rm A}=+25^{\rm o}$ C; all inputs open, unless otherwise specified

| Parameter                                                                | Symbol          | min.                                    | typ.<br>Note 1 | max.                                    | Unit       | Conditions                             |

|--------------------------------------------------------------------------|-----------------|-----------------------------------------|----------------|-----------------------------------------|------------|----------------------------------------|

| Operating voltage                                                        | V <sub>SS</sub> | -2                                      | -5             | -5.5                                    | V          |                                        |

| Operating voltage<br>HV-generator                                        | V PROG          | -4.5                                    | -5             | -5.5                                    | V          |                                        |

| Current consump-<br>tion, serial data<br>transfer                        | /ss             |                                         | 20             | 40                                      | μА         | F CLK = 50 kHz                         |

| Stand by current consumption                                             | / SS Statby     |                                         | 10             | 100                                     | nA         | DIN, CLK at                            |

| Current consump-<br>tion write/erase                                     | / PROG          |                                         | 400            | 600                                     | μА         | 55 11 1 33                             |

| D IN, CLK LO level                                                       | V DIN LO        | V <sub>SS</sub> -0.3 V                  |                | -0.9(V <sub>DD</sub> -V <sub>SS</sub> ) | V          |                                        |

| D IN, CLK HI level                                                       | V DIN +         | -0.1(V <sub>DD</sub> -V <sub>SS</sub> ) |                | V <sub>DD</sub> +0.3 V                  | V          |                                        |

| D <sub>IN</sub> , CLK<br>leakage current                                 | / Leak          |                                         |                | ±100                                    | nA         | DIN, CLK at V DD or Vss                |

| DOUT current LO                                                          | / DOUT LO       | 1.6                                     |                |                                         | mA         | V DOUT = V SS+0.4 V                    |

| DOUT current HI                                                          | / DOUT HI       | -0.5                                    |                |                                         | mA         | V DOUT = V DD-0.4 V                    |

| Clock frequency                                                          | FCLK            | 20                                      | 50             | 100                                     | kHz        |                                        |

| Write pulse length                                                       | tw              |                                         | 50             | , , , , , , , , , , , , , , , , , , ,   | msec       | internally generated;<br>FCLK = 50 kHz |

| Erase pulse length                                                       | t <sub>E</sub>  |                                         | 50             |                                         | msec       | internally generated;<br>FCLK = 50 kHz |

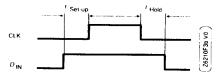

| Data set up time                                                         | f Set-up        | 1                                       |                |                                         | μsec       | under all conditions                   |

| Data hold time                                                           | t Hold          | 1                                       |                |                                         | μsec       | under all conditions                   |

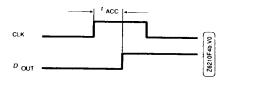

| Data access time                                                         | 1 ACC           |                                         |                | 3                                       | μsec       | under all conditions                   |

| Power on reset:<br>Power supply<br>voltage vs. power<br>supply rise time | dV ss/dt        | -5                                      |                |                                         | V/<br>msec |                                        |

Note 1:Typical parameters represent the statistical mean values

## Figure 1: Block diagram

9

Figure 2: OP2 (write) operation: Bit 63, 64 written, remaining bits unchanged

Figure 3a: OP3 (erase) operation: Bit 63, 64 erased, remaining bits unchanged

Figure 3b: Set up and hold time

Figure 4a: OP7 = serial data out

Figure 4b: Access time

Diagrams are not drawn to scale. For further technical information please contact our sales office. Information furnished by EUROSIL electronic GmbH is believed to be accurate and reiiable. However, no responsibility is assumed by EUROSIL electronic GmbH for its use, nor for any infringements of pa-

tents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of EUROSIL electronic GmbH. EUROSIL electronic GmbH reserves the right to make changes in order to improve the designs at any time.

EDS 0192.04

NAX 1 8 1393