# Video Image Processor Data Book

© Copyright 1994, 1995 Tseng Labs, Inc. 9006165 000001 590 A

# Contents

| 1.0 Introduction                                           | . 1 |

|------------------------------------------------------------|-----|

| 1.1 ET4000/V33 (VIPeR) Specifications                      | . 8 |

| 1.2 VIPeR Overview                                         |     |

| 2.0 VIPeR Functional Description                           |     |

| 2.0.1 Image Memory Access (IMA) Connector                  | 12  |

| 2.0.2 Buffered Data Bus                                    | 13  |

| 2.0.2.1 DD Bus Mode Writes                                 | 13  |

| 2.0.2.2 DD Bus Mode Reads                                  |     |

| 2.0.2.3 BDB bus mode writes                                |     |

| 2.0.2.4 BDB bus mode reads                                 |     |

| 2.0.3 Operation                                            | 14  |

| 2.0.4 VIPeR Device ID (Signature)                          | 15  |

| 2.1 Host Interface                                         |     |

| 2.2 ADC Interface                                          |     |

| 2.3 Sync Separator                                         | 25  |

| 2.4 YUV to RGB Conversion                                  |     |

| 2.4.1 Playback YUV/RGB Conversion                          | 28  |

| 2.4.2 YUV/RGB Conversion of Live Video, via ADC Input Port | 29  |

| 2.5 Horizontal/Vertical Scaling                            |     |

| 2.6 External Mask DRAM Control                             | 31  |

| 2.6.1 Split mask DRAM modes                                | 32  |

| 2.6.2 Write Sequence                                       | 33  |

| 2.6.3 Read Sequence                                        | 34  |

| 2.6.4 Special refresh considerations                       | 35  |

| 2.7 Processed Data Output                                  | 35  |

| 2.8 Audio Interface                                        | 36  |

| 2.9 Video Control Port                                     |     |

| 2.10 Image Data (W32/W32i/W32p) Interface Unit             | 38  |

| 3.0 VIPeR Pinout                                           | 39  |

| 3.1 Power On Reset Initialize (PORI)                       |     |

| 3.2 Pin Descriptions                                       | 42  |

| 3.2.1 Host Bus Interface                                   | 43  |

| 3.2.2 ADC Interface                                        |     |

| 3.2.3 Video Sync Signals                                   | 45  |

| 3.2.4 Processed Data Output                                | 46  |

|                                                            |     |

B

| 3.2.5 Audio* Input                                |    |

|---------------------------------------------------|----|

| 3.2.6 Video Control Port                          |    |

| 3.2.7 Image Data Port                             |    |

| 3.2.8 Overlay Mask Control                        |    |

| 3.2.9 System and Configuration                    |    |

| 3.2.10 Power and Ground                           | 49 |

| 3.3 VIPeR Rev. A versus Rev. B Pinout Differences | 50 |

| 3.4 Electrical Specifications                     | 52 |

| 3.4.1 Electrical Characteristics                  | 52 |

| 4.0 VIPeR I/O Timing Specification                | 53 |

| 4.1 Host Bus Signal Timing                        | 53 |

| 4.1.1 Host Write Access                           | 54 |

| 4.1.2 Host Read Access                            | 54 |

| 4.1.3 IXMADL Timing                               | 55 |

| 4.1.4 MEMWL Timing                                | 55 |

| 4.2 Image Data Port Signal Timing                 | 55 |

| 4.2.1 IXDATA<7:0>, IXMSK Timing                   | 55 |

| 4.2.1 IXCMDL Timing                               |    |

| 4.2.2 Other Output Signal Timing                  |    |

| 4.2.3 IXRDY Input Signal Timing                   |    |

| 4.2.4 Minimum Pulse Width Duration                |    |

| 4.3 ADC Interface Timing                          |    |

| 4.4 Sync Signal Timing                            |    |

| 4.5 Processed Data Output Timing                  |    |

| 4.6 Video Control Port Timing                     |    |

| 4.7 Audio Interface Timing                        |    |

| 4.8 Mask DRAM Interface Timing                    | 62 |

| 5.0 VIPeR Registers                               |    |

| 5.1 Overview                                      | 65 |

| 5.2 Register Descriptions                         | 66 |

| 5.2.1 Control Register                            | 66 |

| 5.2.1 Control Register (cont'd)                   | 67 |

| 5.2.2 Configuration Register A                    | 67 |

| 5.2.3 Configuration Register B                    | 69 |

| 5.2.3 Configuration Register B (cont'd)           | 71 |

| 5.2.4 Configuration Register C                    | 72 |

| 5.2.5 Status Register A                           | 72 |

| 5.2.6 Status Register B                           | 73 |

| 5.2.7 Status Register C                           | 73 |

|                                                   |    |

VIPeR Data Book

C

| 5.2.8 Status Register D                                             | 74 |

|---------------------------------------------------------------------|----|

| 5.2.9 Sync Separator Horizontal Sync Width Register                 | 74 |

| 5.2.10 Sync Separator Horizontal Window Closed Width Register       | 74 |

| 5.2.11 Sync Separator Horizontal Window Open Width Register         |    |

| 5.2.12 Sync Separator Vertical Sync Detector Width Register         | 76 |

| 5.2.13 Sync Separator Vertical Sync Width Register                  | 76 |

| 5.2.14 Sync Separator Vertical Window Closed Width Register         | 76 |

| 5.2.15 Sync Separator Vertical Window Open Width Register           | 77 |

| 5.2.15 Sync Separator Field Detection Window Width Register         | 77 |

| 5.2.16 Pixels Per Line Register                                     | 77 |

| 5.2.17 Lines Per Field Register                                     |    |

| 5.2.18 Framing Control Register                                     |    |

| 5.2.19 Video Bytes Per Line Register                                | 79 |

| 5.2.20 Maximum Bytes Per Line Register                              | 79 |

| 5.2.21 X delay                                                      | 79 |

| 5.2.22 Y delay                                                      | 80 |

| 5.2.23 Video Control Port Register                                  |    |

| 5.2.24 X Scaling Coefficient Register                               | 81 |

| 5.2.25 XK Scaling Coefficient Register                              | 81 |

| 5.2.26 Y Scaling Coefficient Register                               | 81 |

| 5.2.27 YK Scaling Coefficient Register                              | 81 |

| 5.2.28 Mask Control Register                                        | 82 |

| 5.2.29 Reserved Registers                                           | 82 |

| 5.2.30 Host Access Registers                                        | 83 |

| 6.0 Summary of Rev.A versus Rev.B VIPeR Differences                 |    |

| 6.1 Pin Definition Changes                                          | 84 |

| 6.2 New features: Rev.B versus Rev.A VIPeR                          | 85 |

| 6.3 VIPeR Rev. A operational discrepencies corrected in VIPeR Rev.B |    |

- - -----

# 1.0 Introduction

The Tseng Labs Video Image ProcEssoR delivers the necessary features to transform a graphics adapter into a fully functional video adapter. The VIPeR was designed to enhance both live video streams from a source such as a commercial camcorder or VCR, or digital motion video retrieved from a hardware or software compression/decompression engine (CODEC) such as Intel Indeo<sup>™</sup> or Microsoft Video for Windows<sup>™</sup>. AVI files. The VIPeR intelligently sizes and scales data to make it appear larger or smaller on screen without decreasing CPU bandwidth. The VIPeR architecture provides numerous benefits to the designer, including optimal use of the Image Memory Access (IMA)<sup>™</sup> port featured on the Tseng Labs W32 family of graphics accelerator chips.

The VIPeR allows graphics adapters based on the W32 family of accelerators from Tseng Labs to truly become video cards. By definition these video cards provide high-quality frame grabbing from any video source and apply the VIPeR's sizing and scaling to software-decompressed video, such as Microsoft's Video for Windows.

Today's CPUs are capable of 15/30 frame per second decompression of some algorithms. Typically the default resolution of CPU decompressed video is no greater than 160x120 pixels. Since many GUI users use high resolution displays, the video will need to be enlarged to occupy a significant screen area. The CPU does not have adequate bandwidth to increase resolutions. When executing both decompression and expansion, system performance deteriorates dramatically. Quality is also an issue, as CPU-based enlargement creates jagged un-lifelike images, while the VIPeR generates enlarged images smoothly without absorbing CPU bandwidth or dropping the frame rate of the motion stream. As a result the VIPeR is ideal for audio/video communication across a personal computer network, TV-in-a-window, digital authoring, video telecommunications, and other multimedia applications.

The VIPeR video processor from Tseng Labs allows users to place a high quality digital video window any where on their display. By leveraging the capabilities of the Tseng Labs W32 family of graphics accelerators, including the IMA port and CRTCB feature, the VIPeR can be programmed to display 16-bit or 24-bit full motion video at an arbitrary size on the personal computers display monitor. The VIPeR controls the digitization of video and performs digital processing on motion video data. Under an operating environment like Microsoft Windows, an application will allow the user to drag open a video window of any size from 16 by 16 to 720x480, when used with the Tseng Labs W32.

When using a decompression CODEC, like an MPEG decoder, for example, video is of a fixed output resolution and format. It can't easily be resized or moved to arbitrary locations on the display. With the VIPeR, this output decoded video stream can be resized to any arbitrary screen size desired, and placed in any screen location. Further, with the video/graphics mixing capabilities of the VIPeR/W32 graphics controller combination, the video and graphics windows can occlude and mix with each other on a pixel by pixel basis. Finally, the scaling and windowing is independent of compression/decompression algorithm used.

The VIPeR performs a number of control functions for the digitization of video. Using it's bullet-proof sync technology, it provides the clock for the external Analog to Digital converters, separates the composite sync into horizontal sync, vertical sync, and framing information. This process delivers enhanced synchronization separation, which allows for worst-case video sync input, such as fast-forward, reverse, and freeze-frame in consumer VCR's to display properly on screen.

The VIPeR uses all of the information available in each field to create a video window. In creating the digital display, the VIPeR removes various unfavorable affects of converting the interlaced video to non-interlaced VGA through digital processing. The digital processor is capable of both reduction and enlargement of the incoming video data, without recalculation from the CPU, by converting the video stream to the requested X and Y dimensions. A sample clock of approximately 15 megahertz will allow up to 20 pixels in the X dimension. With a one-line internal FIFO the VIPeR is capable of converting the incoming video lines up to 480 lines per field for NTSC; 576 for PAL.

VIPeR Data Book - 1

Furthermore, the VIPeR expands CPU bit maps or motion video as if they had entered the VIPeR through the Analog to Digital port, delivering real-time enlargement of lower resolution stored video sequences. Because the enlargement uses the VIPeR's processing power and is not the result of simple pixel replication, the quality of the image is optimal.

VIPeR performs smooth scaling, based on an area average algorithm, in both the horizontal and vertical directions. All the input data is used to create the output video stream. No pixel dropping or pixel replication is done. No line dropping or line replication is done.

The CPU communicates with the VIPeR through memory mapped bus. Using the Tseng Labs Image Memory Access (IMA) connector, register reads and writes, as well as deliverance of unscaled pixel data can be done. In ISA or MicroChannel configurations, VIPeR has a 16 bit host bus connection via a buffered data bus it shares with the W32/W32i/W32p. In PCI or VESA Local bus configurations, VIPeR's host bus connection is an 8 bit bi-directional, address/data multiplexed bus passed directly from the W32x. It is called the DD bus. All host communications to the VIPeR are memory mapped by the W32x, and repeated over the DD bus. In this way, the VIPeR does not contribute an electrical load to the host CPU bus, and PCI 2.0 compliance is maintained.

There are two main mechanisms for delivering (unscaled) video data to the VIPeR. The first is via the CPU interface bus, and is generally used when playing back data from the host computer. This is the same bus which is used to program the VIPeR registers, and is a part of the Image Memory Access (IMA) connector. The second is via the Analog to Digital Port, and is generally used when playing back live digitized data. Decompression chip outputs can feed their data to either input port, however, the Analog to Digital Port will generally be easier for the system board design.

There are two main mechanisms for outputting scaled video from the VIPeR. The first is over the Image Data Port, the other part of the Image Memory Access (IMA) connector. This is an 8 bit serial data port which feeds video data to the W32/W32i/W32p graphics controller for storage in the frame buffer. The second is over the processed digital data output bus. This is a 24 bit (red/green/blue) output which is the direct scaled video output. This video stream can be input to a compression engine for encoding scaled video streams.

The VIPeR output video data is written to the W32/W32i/W32p byte serially over the Image Data Port. When the graphics controller receives the VIPeR's video data, it immediately writes it into pre-programmed regions of its own frame buffer. Therefore, adding VIPeR video functionality does NOT require the system designer to add any additional frame buffer memory. The VIPeR/W32x system uses a single frame buffer architecture. Video memory space is allocated out of the existing graphics frame buffer. This leads to large system cost reductions.

VIPeR contains an 8 bit bi-directional Video Control (VC) Port. Data into and out of these pins is accessible by the host CPU via internal registers in VIPeR which source or read the values on the VCPort pins. This capability allows for CPU access to other devices on the video card, through the VIPeR, through W32x memory mapped access to this internal VC port register. These VC port bits can be used to control and read an IIC bus, for example.

In conjunction with the W32/W32i/W32p, VIPeR provides an alpha channel bit along with each video pixel to allow for pixel by pixel mixing of video and graphics in the display frame buffer. The video/graphics "flag" is stored in an external 256Kx4 DRAM, which the VIPeR controls. Writes to this alpha bit (mask) DRAM are done via memory mapped register access, similar to all other VIPeR register accesses. VIPeR controls reading this mask information and synchronizing it with the scaled video output stream. The W32x reads the alpha (mask) bit with each video pixel it receives from the VIPeR. The W32x is responsible for writing the appropriate video or graphics pixel in the frame buffer, and out to the display device, based on the corresponding mask bit.

A final VIPeR feature is the ability to accept digital audio data in, and synchronize it with the video. VIPeR contains an internal FIFO for storing audio (or any other relatively lower frequency, like SMPTE) data. There is a pass through

■ 9006165 0000006 072 **■**

mechanism whereby this data is written, over the Image Data Port, and stored in unused portions of the frame buffer. Although no processing on this data is done, the FIFO and IMA transfer capability potentially simplify lip sync issues of audio/video streams.

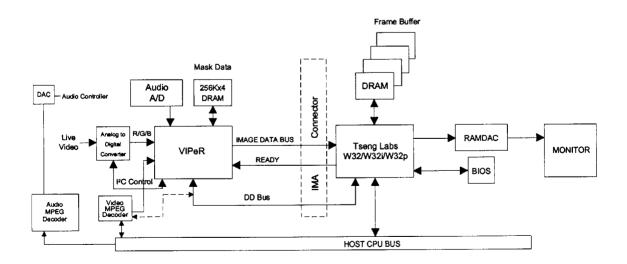

VIPeR is highly integrated for use with the Tseng Labs W32 family of graphics accelerators. The video system architect can choose any of the options desired to enhance the VIPeR/W32 video/graphics system. Following diagrams show the major elements of a VIPeR display subsystem.

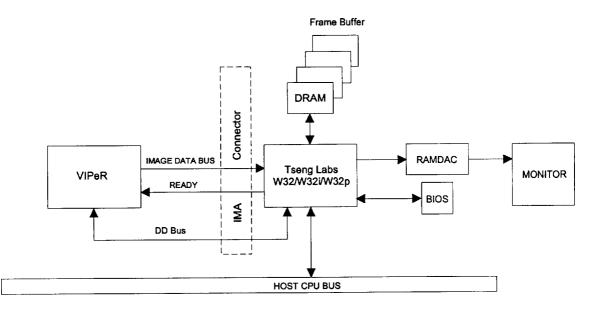

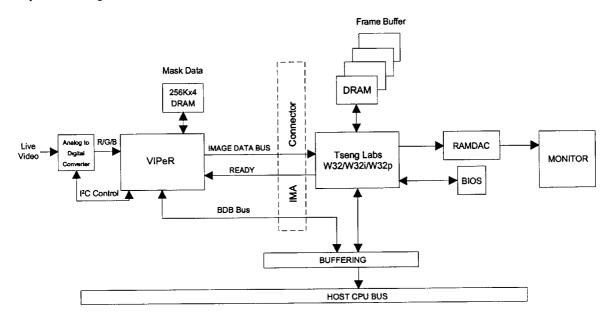

Figure 1.1 shows a bare bones configuration: W32/W32i/W32p with host bus access, DRAM frame buffer, connection to RAMDAC, and IMA connector for adding VIPeR video capabilities. VIPeR host bus connection is 8 bit DD mode, via the IMA connector to the DD bus of W32. Without a front end A/D converter to accept live video, this system will still be able to read stored data streams from the CPU bus (like Video for Windows .AVI files), scale the video, and display it over the top of the graphics windows.

Figure 1.1 DD Bus, Stored Video Playback Only

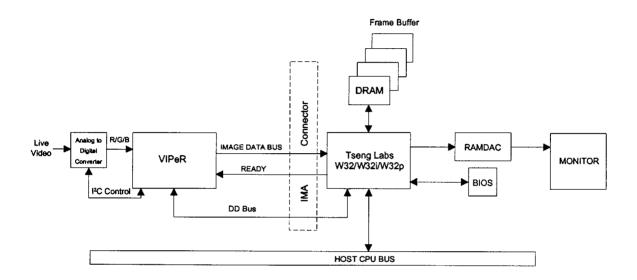

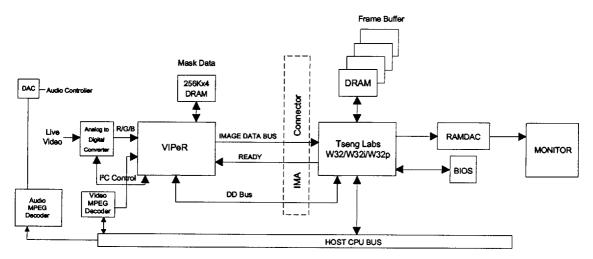

Figure 1.2 shows a system with the an added A/D front end converting incoming live video to digital format. With this additional component, and connector to live video source, this system will now be able to do what the previous did, and also scale and display live video sources as well. In addition, this system gives the ability to capture (scaled) live video and store it onto hard drive or system memory. In this system, the video window must be always on top of the graphics.

Figure 1.2 DD Bus, Live and Stored Video Playback and Capture

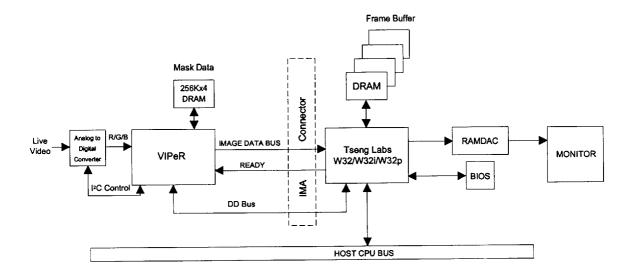

Figure 1.3 shows a system with the addition of a 256K x 4 bit DRAM. With this new component, video can now be mixed with the graphics on a pixel by pixel basis. The video can be occluded by the graphics, not only in rectangular regions (necessary for operating in a full Windows environment) but also on pixel boundaries (useful for authoring systems with text overlays on top of the video).

Figure 1.3 DD Bus: Video Playback, Capture, Store; Fully Windows Compatible

Figure 1.4 shows a system shows the above system but with VIPeR connected to the host bus in 16-bit BDB mode. This requires buffering the host bus.

Figure 1.4 BDB Bus, Video Playback, Capture, Store; Fully Windows Compatible

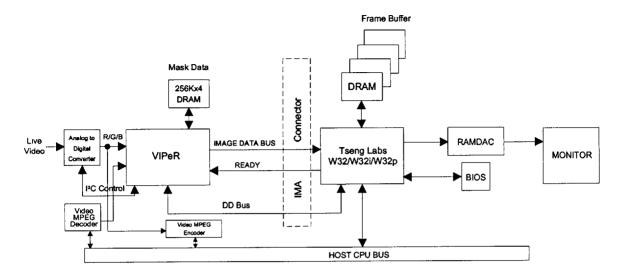

Figure 1.5 shows the DD bus mode again, but with the addition of an MPEG decoder. With this additional component, and its associated memory, the video system now supports not only live and stored video playback and capture, fully compatible with Windows, but now can accept MPEG encoded video data streams, decode, scale, and mix video with the graphics window

NOTE: MPEG decoder programming input data stream can be via DD Bus or Host CPU Bus connection

Figure 1.5 DD Bus, Video Playback, Capture, Store; MPEG Decode and Scale; Fully Windows Compatible

Figure 1.6 shows the addition of a video encoder. With this additional component, one can now encode live video streams and store them to the hard disk or system memory.

Figure 1.6 DD Bus: Video Playback, Capture, Store: MPEG Decode/Encode and Scale: Fully Windows Compatible

Figure 1.7 shows the addition of an audio receiver/digitizer. Adding this component allows for audio capture in addition to all the video features.

Figure 1.7 DD Bus: Video Playback, Capture, Store: MPEG Decode/Encode and Scale: Fully Windows Compatible, Audio Capture

VIPeR Data Book - 7

# 1.1 ET4000/V33 (VIPeR) Specifications

The following is an outline of the ET4000/V33 Video Image ProcEssoR specifications.

## 1. Input Interface

Following are the primary VIPeR input busses:

- A. Host access port, BDB or DD, bus

- 1.8 or 16-bit memory mapped I/O bus

- 2. Multiplexed address/data

- 3. 16 bits (BDB<15:0>) in ISA, MicroChannel bus modes, 8 bits (DD<7:0>) in Local bus or PCI modes

- 4. Driven by W32x in DD bus mode; driven by buffered data bus in ISA mode

- 5. Register I/O and digital video input

- Maximum 33MHz, 16.5 Mbyte/second via DD bus; maximum 33MHz, 33Mbyte/second via BDB bus

- B. ADC interface

- 1. 24-bit digital video input only

- 2. 25MHz maximum data input rate

- 3. Accepts composite or separated sync inputs

- C. Audio interface

- 1.8 bit digital data input

- 2. Data FIFO'd internally, sent out at end of video scan line

- D. Video Control Port

- 1.8 bit I/O bus

- 2. Each bit independently set to input or output

- 3. Information on pins reflected in software accessible internal VIPeR register

- 2. Output Interface

Following are the primary VIPeR output busses:

- A. Image Port Output

- 1. 8 bit data output bus: scaled video sent to W32x

- 2. Address implied: internally generated via W32x programming

- 3. Tseng IMA protocol

- 4. Maximum 50MHz, 50Mbyte/sec output

- B. Processed Data Output

- 1. 24-bit digital scaled video (tristateable) output

- 2. Video output only: result of X/Y scaling, can be sent to devices besides W32x

- 3. Maximum 50MHz, 150Mbyte/sec output

- 3. Display Formats

- A. Plane, linear byte, linear word

- B. Resolution from 16x16 to 720x480 (580 for PAL)

- C. 15/16/24 bit/pixel

- D. RGB or YUV pixel formats

8 - VIPeR Data Book

🖬 9006165 0000012 376 🖿

#### 4. Inputting Source Video to VIPeR

- A. ADC/Host access

- 1. Data accepted via either ADC or Host bus

- 2. Interlaced or non-interlaced video accepted

- B. Pixel Formats: RGB, YUV444, YUV422A, YUV422B

- 1. 15/16/24 bit RGB

- 2. YUV444

- 3. YUV422 modes: UV nibbles, or toggling UV bytes

- C. Two Sync Sources

- 1. Composite sync input

- 2. Independent horizontal/vertical/ sync, field polarity

- 5. Outputting Scaled Video from VIPeR

Video stored in shared graphics frame buffer—No need for dedicated video frame buffer or video/graphics switching logic.

15/16/24 bit RGB output formats available

A. IMA output

1. Delivered over 8 bit IMA bus, via Tseng IMA protocol, to W32x, for storage in graphics frame buffer B. Processed data output

1. 24-bit scaled RGB video output

#### 6. Video Scaling

- A. Horizontal Scaling

- 1. Smooth scaling: uses ALL incoming data, no pixel replication or pixel dropping

- 2. Scale up/Scale down: maximum input/output ratios, 1/64 or 64/1 limited by minimum video 16x16 and maximum video resolution 720x1024

- **B.** Vertical Scaling

- 1. Smooth scaling: uses ALL incoming data, no line replication or line dropping

- 2. Scale up/Scale down: maximum input/output ratios, 1/64 or 64/1 limited by minimum video 16x16 and maximum video resolution 720x1024

#### 7. YUV/RGB Conversion

- A. CCIR601 compatible YUV to RGB conversion done on fly

- B. Selectable: perform conversion or bypass conversion

## 8. Sync Separation

- A. Lock to multiple video sources

- 1. Program windows for anticipated sync pulse timing genlock to high or consumer quality sources

- 2. Composite sync or independent line/frame/field inputs

- B. Scan conversion

- 1. Converts from broadcast interlaced to high refresh rate non-interlaced

- 9. Video/Graphics Overlay Control

- A. Motion video selectable on pixel-by-pixel basis

- 1. Control logic and I/O pins for control of external 256Kx4-bit DRAM. DRAM is programmed (via VIPeR registers) with video/graphics select data

- 2. Two mask formats available: one 1024x1024, or two 1024x512 resolution video overlay windows

- 3. Pixel-by-pixel overlay control allows for graphics/video window including, non-rectangular shaped video windows, and pixel resolution graphics text overlay

#### 10. Video Control Port

- A. Read/Write external devices via program I/O port

- 1. Programmed register sets input/output functionality of each pin.

- 2. Register writes to output configured pins pass corresponding register data to output VC port pin.

- 3. Logic states on wires hooked to input configured pins are readable via corresponding register bit reads.

- B. Useful for attaching to and controlling IIC (or similar) busses

- C. Gives software accessibility to external video board hardware

### 11. Audio Input

- A. Accepts audio (or other) relatively slower digital data

- 1.8 bits data, 1 clock input loads internal 128 byte FIFO

- B. Writes data out to unused portions of frame buffer

- 1. Programmed registers set maximum number of bytes to be appended to end of video scan line.

# 1.2 VIPeR Overview

- Single 160-pin Quad Plastic Flat Pack Integrated Circuit.

- Real-time dynamic enlargement and reduction of motion data streams using a proprietary imaging algorithm. This intelligent processing eliminates jagged edges caused by pixel multiplication, or significant data loss of pixel decimation.

- Smooth scaling is performed in both X and Y directions.

- Interface to the ISA/EISA/MCA, as well as VESA VL-Bus and Intel PCI architecture.

- Directly interfaces to the Tseng Labs W32/W32i/W32p Image Memory Access port without external logic.

- Accepts input data in 15/16-bit and 24-bit RGB, as well as 4:4:4 and sub-sampled 4:2:2 YUV formats.

- Outputs 16-bit and 24-bit RGB, ideal for Microsoft Windows and other personal computer graphics environments.

- IMA/VIPeR architecture creates a single frame buffer that includes both the graphics display and the motion video.

- Accepts either live input or stored/decompressed digital data from the host bus.

- Refresh rate: selectable, 30 frames per second, 60 fields per second, or 30 fields per second.

- Digitization Resolution: up to 720 x 480 (580 for PAL) by 24-bit (dynamic).

- Screen resolution from 16x16 (icon) to 720 x 480 (580 for PAL) by 16 bits or 24 bits of color.

- High quality still frame capture.

- Bullet-proof sync separation will lock to all consumer grade and better NTSC/PAL/SVHS video sources.

- Handles scan conversion from interlaced broadcast standards to high-refresh non-interlaced

- Provides pins to control the storage of digitized audio data in unused areas of the frame buffer.

- Hardware cursor overlay for the video window when using the W32 family's CRTCB feature.

- Requires no external VRAM or DRAM for digitization. Control signals are provided for one optional external 256Kbx4 DRAM chip for overlays. The VIPeR can use this buffer to support a mask bit to display motion data on a pixel-by-pixel basis.

- Supports hardware cropping.

- Memory mapped registers are fully programmable in parallel.

- Compatible with Microsoft Windowsä and Video for Windowsä, IBM OS/2ä, and Intel Indeoä software.

# 2.0 VIPeR Functional Description

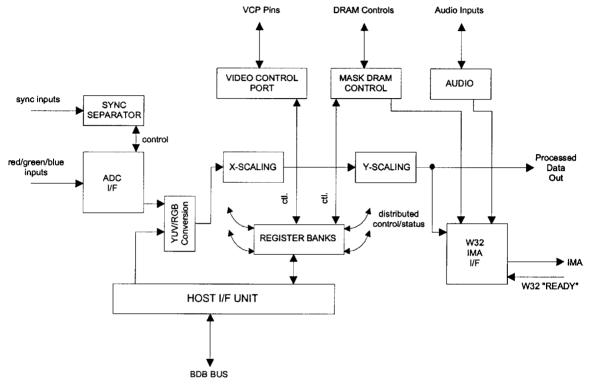

All major elements of the VIPeR are contained within a 160 pin Quad Flat Package. Figure 2.0.1 below shows the internal architecture. The following sections provide a breakdown of the major elements of the chip.

Figure 2.01 VIPeR Internal Architecture

## 2.0.1 Image Memory Access (IMA) Connector

Tseng Labs has devised a 50-pin connector which joins the video image processing functions with the graphics display functions. By using this connector, OEMs can add motion video enhancing daughter cards to either their system planer, or video adapter. The IMA connector includes 8 bits of Image Data (output from the VIPeR), control and synchronization signals, the buffered data bus, and power/ground wires. An IMA connector is not required if direct connection within a single PC board is designed, linking the VIPeR and graphics accelerator directly.

The Tseng Labs family of graphics accelerators control the resolution and color depth of the display monitor, as well as provide the memory for the motion video, within its graphics frame buffer. VIPeR video output travels over the IMA bus into the graphics accelerator, which then stores it at a CPU-definable address in the frame buffer.

The W32/W32i/W32p provides two separate and independent CRT control windows, CRTC and CRTCB, known also as the A and B windows respectively. The primary CRTC is used to display the personal computer's primary graphics session, including such things as Microsoft Windows, or DOS. The second, CRTCB, (B window), can be a hardware cursor, or it can be an independent overlay window, ideal for live video. Using the W32/W32i/W32p, the motion video window can be at different color depth than the primary window. For example, the graphics can be in 8bpp mode, while the video window is 16bpp. Other combinations are also possible. For more information, contact your Tseng Labs representative for W32 family graphics accelerator information.

9006165 0000016 T11 🔳

12 - VIPeR Data Book

## 2.0.2 Buffered Data Bus

VIPeR and W32/W32i/W32p share access to the buffered data bus. As a result, the VIPeR is accessible to the host CPU and can be configured, reprogrammed, and status monitored by the programmer. Additionally, data decompressed by the CPU or external CODEC on the bus, intended for display, can be routed to the VIPeR across this bus for real time processing. This processing relieves the CPU and CPU bus from having to scale, and YUV/RGB convert, live, full resolution motion video.

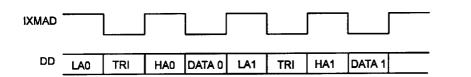

There are two main operating modes of the host buffered data bus communication with the VIPeR and W32/W32i/W32p. These are called, 16-bit buffered data bus mode, and 8-bit DD bus mode. Choice of these depends on the W32/W32i/W32p configuration. In ISA and MCA modes, 16 bits of BDB are available from the graphics accelerator, so the full 16 BDB mode can be chosen for host to VIPeR communication. In PCI and VESA local host bus modes, however, only 8 bits of host bus are available for VIPeR communication. These 8 bits are directed from the W32/W32i/W32p directly. They are the remapped address/data as seen on the host bus, when an access to the graphics accelerator external device address space is detected. In 8-bit DD bus mode, host to VIPeR accesses are still 16 bits, however, the access is done in two passes: low byte/high byte, occupyir\_four DD bus cycles as follows.

## 2.0.2.1 DD Bus Mode Writes

| <u>DD&lt;7:0&gt;</u> |

|----------------------|

| low address byte     |

| low data byte        |

| high address byte    |

| high data byte       |

|                      |

## 2.0.2.2 DD Bus Mode Reads

| DD Bus Cycle # | <u>DD&lt;7:0&gt;</u>     |

|----------------|--------------------------|

| 1              | low address byte         |

| 2              | NULL cycle               |

| 3              | high address byte        |

| 4              | VIPeR readback data byte |

|                |                          |

NOTE: A different read mechanism is available with Rev.B VIPeR only. See the PREREAD mode description in Section 5.0, Register Descriptions, Control Register, bit 3.

In 16 bit BDB bus mode, host to VIPeR accesses are 16 bit, direct, as follows.

## 2.0.2.3 BDB bus mode writes

| BDB Bus Cycle # | <u>BDB&lt;15:0&gt;</u> |

|-----------------|------------------------|

| 1               | address word           |

| 2               | data word              |

## 2.0.2.4 BDB bus mode reads

| BDB Bus Cycle # | BDB<15:0>                |

|-----------------|--------------------------|

| 1               | address word             |

| 2               | VIPeR readback data word |

NOTE: unless specified as VIPeR driven during corresponding bus cycles in read modes above, all host bus activity is driven by W32/W32i/W32p.

## 2.0.3 Operation

When the external RESET signal is activated, writable VIPeR control and configurations register bits return to zero(\*). VIPeR is now ready to be initialized.

NOTE: there are 2 exceptions to this reset to zero state. Register bits 7 and 0, CPUSYNC, and READHI, described in detail in the Register Programming Section 5.0, reset to value 1.

Initialization takes place, after RESET has returned to its inactive state, by a sequence of register writes to the VIPeR control and configuration registers. A full description of these is given in Section 5.0. The order in which these registers are written is unimportant.

VIPeR registers are accessed by the host CPU via memory (re)mapped accesses to the Tseng Labs graphics accelerator, W32/W32i/W32p. The graphics accelerator has a 4K external device address space starting at host address 0xBE000. Host accesses to this address space are remapped by the graphics accelerator to the VIPeR. The VIPeR configuration and status registers reside in the 0x00 through 0x38 address offset of the external device address space.

After initial programming, VIPeR remains in a state where it is waiting for video data. Based on programmed state, this video can come from either the ADC inputs or from continued host writes to offset 0x400 through 0x7FF addresses within the external device address space. Playback of CPU stored video will typically arrive at the VIPeR as series of host writes. Video synchronization information also arrives via register writes, in this case, to bits in the Control Register, address 0x00. For live video inputs, or other input (like from a video decompression CODEC), video can come into the VIPeR, digitally, via the ADC input. Along with the data, a clock, LLCLKIN, is provided to sample the incoming video. VIPeR accepts either 15, 16, or 24 bit/pixel video inputs in either RGB, YUV444, or YUV422 modes.

Since the video into VIPeR is digital, an analog to digital converter must be used when the source of video is live, analog video, like NTSC, PAL, or SVHS. Systems focusing on enhancing .AVI or Indeo playback may not require this analog to digital converter front end. In general, if the source of live video is from the CPU only, in a particular system, then the front end A/D component is not needed.

As input video comes into the VIPeR, horizontal and vertical direction scaling, YUV/RGB conversion (if required), formatting, and synchronization with input sync pulses and corresponding mask bit data, take place based on programmed settings. Scaled/ converted/synchronized data is FIFO'd and, based on W32/W32i/W32p ability to take the output video data (as communicated on the W32/W32i/W32p output, VIPeR input IXRDY\*), is sent, over the Image Data Port portion of the IMA connector, to the W32/W32i/W32p. 15, 16, or 24 bit output data is time multiplexed onto the 8 bit IXDATA<7:0> outputs. W32/W32i/W32p accepts this image video data, along with a mask bit, on IXMSK VIPeR output pin, and writes this video stream into preprogrammed rectangular regions of the main graphics frame buffer. In this way, the W32/W32i/W32p mix the video and graphics together. The mask bit associated with each video pixel tells the W32/W32i/W32p whether video or graphics should be displayed for that particular pixel. In this way, graphics windows can occlude arbitrary portions of the video window. Further, since the mask capability is on a pixel by pixel basis, text overlays are possible over the video window.

## 2.0.4 VIPeR Device ID (Signature)

As described in the register programming section, 5.0, VIPeR returns a device ID, or signature, when address 0x00 is read. This signature resides in the upper byte, bits <15:8> of control register, address 0x00. For VIPeR, Rev.A, the signature value is 0xBB. For VIPeR Rev.B, the signature is 0xCB. 256 values of signature is sufficient because only devices physically residing in the W32/W32i/W32p extended device address space are locatable here.

# 2.1 Host Interface

VIPeR and W32/W32i/W32p share access to the buffered data bus. As a result, the VIPeR is accessible to the host CPU and can be configured, reprogrammed, and status monitored by the programmer. Additionally, data decompressed by the CPU or external CODEC on the CPU bus, intended for display, can be routed to the VIPeR across this bus for real time processing.

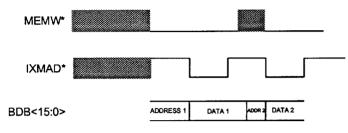

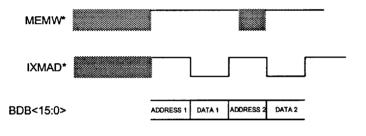

The host interface bus is a bi-directional, multiplexed address/data, 16 bit connection to the W32/W32i/W32p buffered host bus. It operates in two main modes, based on W32/W32i/W32p configuration. These are, sixteen bit buffered data bus mode (BDB mode) and 8 bit direct data (DD mode). The pin names are BDB<15:0> (the actual address and data pins), MEMW\*, the read/write indicator, and IXMAD\*, the address/data phase indicator. MEMW\* and IXMAD\* are driven by W32/W32i/W32p. BDB bus is driven by the buffered host data bus in BDB mode, during non readback data cycles. BDB bus is driven by the VIPeR during readback data cycles.

When MEMW\* is low, host accesses to the VIPeR are writes. When MEMW\* is high, VIPeR is being read, and drives the BDB lines after receipt of a valid address.

In general, IXMAD\* is driven high by W32/W32i/W32p during the address phase on BDB bus. After IXMAD\* is driven low, data is driven onto BDB bus for writes to the VIPeR, and VIPeR drives data back when IXMAD\* is low during a read access to the VIPeR (as indicated by MEMW\*). Timing of these signals can be tuned (VIPeR Rev.B silicon only) for different board design configurations, via zero ohm jumpers to ground, inserted or removed, on PRED<0> and PBLUE<0>. Details of the bus timing is provided in Section 4.1.

When the W32/W32i/W32p is in either PCI or VESA local bus mode, 8 bit DD bus mode must be chosen as the VIPeR connection to the host. This is because the VIPeR/host connection is made via the DD bus of the W32/W32i/W32p. DD bus is 8 bits when in PCI or VESA local bus mode. Since the VIPeR address decode and data access are all 16 bits, a double cycle sequence is done to access the VIPeR from the host. Low byte access is done first, followed immediately by the high byte access. BDB<7:0> is connected to the W32/W32i/W32p DD bus. BDB<15:8> are not used in this bus mode, and can be left floating.

When the W32/W32i/W32p is in either ISA or MicroChannel bus mode, 16 bit BDB bus mode must be chosen as the VIPeR/ host connection. The VIPeR 16 bit host bus, BDB<15:0>, is connected directly to the host buffered data bus, not to the W32/ W32i/W32p DD bus. Read/write and address/data signals, MEMW\*, and IXMAD\*, are still driven by the W32/W32i/ W32p. All BDB<15:0> bits are used in this bus mode.

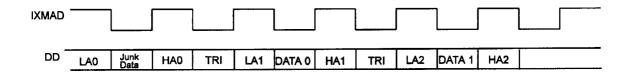

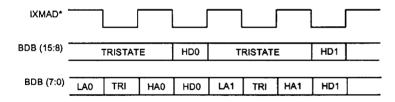

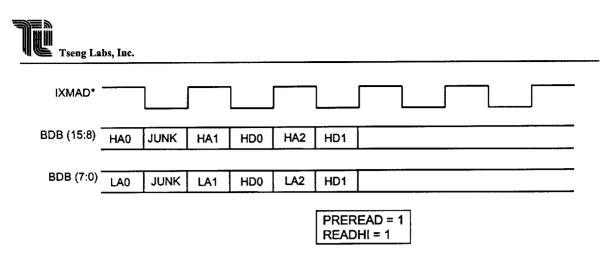

A functional timing diagram showing the register accesses is shown in figure 2.1.1 below. Included are BDB read and write operations. DD mode writes, and DD mode reads in its two read modes: preread, and not preread. These preread modes are discussed in detail in register programming section, 5.0.

## **BDB Bus Mode WRITE Access**

\* BDB always driven by host buffered data bus

### **BDB Bus Mode READ Access**

\* BDB always driven by VIPeR when DATA 1, Data2; BDB driven by host buffered data bus otherwise.

Figure 2.1.1 Register Access Functional Timing Diagram

DD Bus Mode WRITE ACCESS

Figure 2.1.1 (continued) Register Access Functional Timing Diagram

#### DD Bus Mode Read Access (not pre-read mode)

LA= Low byte address (driven by W32p) TRI= Tri-state VIPeR outputs HA=High byte address (driven by W32p \* VIPeR outputs on DD Bus also tri-stated when DATA=Low Byte of DATA if READHI=0 W32p driving high or low byte addresses High byte of DATA if READHI-1

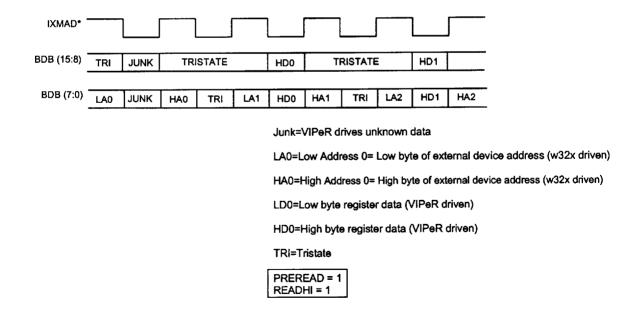

#### DD Bus Mode Pre-Read Mode

Figure 2.1.1 (continued)

| IXMAD*     |          |     |     |     |     |         |     |     |  |

|------------|----------|-----|-----|-----|-----|---------|-----|-----|--|

| BDB (15:8) | TRISTATE |     |     | HD0 | Т   | RISTATE | =   | HD1 |  |

| BDB (7:0)  | LA0      | TRI | HAO | LD0 | LA1 | TRI     | HA1 | LD1 |  |

LA0=Low Address 0= Low byte of external device address (w32x driven)

HA0=High Address 0= High byte of external device address (w32x driven)

LD0=Low byte register data (VIPeR driven)

HD0=High byte register data (VIPeR driven)

TRI=Tristate

PREREAD = 0 READHI = 0

Figure 2.1.1 (cont'd) VIPeR (DD Bus Mode) Reads

LA0=Low Address 0= Low byte of external device address (w32x driven)

HA0=High Address 0= High byte of external device address (w32x driven)

LD0=Low byte register data (VIPeR driven)

HD0=High byte register data (VIPeR driven)

TRI=Tristate

| PREREAD = 0 |

|-------------|

| READHI = 1  |

Figure 2.1.1 (cont'd) VIPeR (DD Bus Mode) Reads

VIPeR Data Book - 19

- 400PJP2 0000053 J2J 🔳

|            | ng Lai | os, Inc. |     |       |     |     |     |         |         |     |         |

|------------|--------|----------|-----|-------|-----|-----|-----|---------|---------|-----|---------|

| IXMAD*     |        | ]]       |     |       |     | L   |     |         | <b></b> | ]   | <b></b> |

| BDB (15:8) | TRI    | JUNK     | TRI | STATE |     | HD0 | Т   | RISTATE |         | HD1 |         |

| BDB (7:0)  | LA0    | JUNK     | HA0 | TRI   | LA1 | LD0 | HA1 | TRI     | LA2     | LD1 | HA2     |

\_\_\_

Junk=VIPeR drives unknown data

LA0=Low Address 0= Low byte of external device address (w32x driven)

HA0=High Address 0= High byte of external device address (w32x driven)

LD0=Low byte register data (VIPeR driven)

HD0=High byte register data (VIPeR driven)

TRI=Tristate

PREREAD = 1 READHI = 0

9006165 0000025 T24 🔳

Figure 2.1.1 (cont'd) VIPeR (16-bit) BDB Bus Mode Reads

In addition to register accesses, the optional DRAM mask is written via host accesses over the BDB interface. When mask write mode is selected, via program settings, host accesses to VIPeR addresses 0x400 through 0x7FF are translated to DRAM mask writes, via a protocol detailed in Section 2.6.

Finally, pixel data streams can be input to the VIPeR over the BDB interface. When mask write mode is disabled, and CPUSYNC mode is programmed, host accesses to VIPeR addresses 0x400 through 0x7FF are accepted by VIPeR as input pixel data. Pixel addressing is implied, based on arrival of CPULSL, and CPUFSL (register access driven line sync and frame sync), and is serial, left to right, top to bottom. That is, first input pixel data sample written to VIPeR after CPULSL is assumed to be the leftmost pixel on that scan line; next input pixel data sample written by the host is assumed to be the second pixel (moving left to right) on that scan line. Similar for lines: first line of input pixel data after CPUFSL is assumed to be the top video input line, etc.

Addressing for input pixel streams is a function of the input pixel resolution mode selected. VIPeR accepts 15, 16, or 24 bit/ pixel data streams in either RGB, YUV444, or YUV422 modes. For the 15 or 16 bit/pixel modes, (and since VIPeR is a 16 bit device) each host write contains the entire input pixel. Any address in the 0x400 through 0x7FF will be accepted by VIPeR as an input pixel. For 24 bit modes, VIPeR requires two host writes to get the whole 24 bit input pixel. These accesses are done as follows. Even addresses within the 0x400 through 0x7FF window are used to write the Green/Blue (or Y/U data in YUV444 mode) components of the pixel. Odd addresses within the 0x400 through 0x7FF window are used to write the Red (or Y in YUV444 mode) component of the pixel. Green (or V) occupies the upper data byte in even address transfers, Blue (or U) the lower data byte in even address transfers. Red (or V) occupies the lower data byte in odd address transfers. The upper data byte in odd transfers is don't care.

For 24-bit input modes, the host must deliver the data a full pixel at a time, via the two transfers; first the even address transfer, then the odd address transfer. A functional timing diagram showing the pixel writes is shown in Figure 2.1.2 below. Any other host write sequencing of delivering the pixel data will lead to unreliable operation.

# 2.2 ADC Interface

VIPeR has a primary data input bus which accepts digital video in (RED<7:0>, GREEN<7:0>, BLUE<7:0>), along with a data enable clock (LLCLKIN). Formats for this data input path can be either, RGB24, RGB16, RGB15, YUV444, or YUV422. Fuller, lower resolution ranges are also possible. For example, if 18 bits of Red/Green/Blue is available from the external A/D converter component, then VIPeR should be programmed as RGB24 input format, and the lower order Red/ Green/Blue input pins should be grounded. For YUV422 mode, the inputs are wired as follows:

| Y<7:0>  | Red<7:3>,Green<7:5>  |

|---------|----------------------|

| UV<7:0> | Green<4:2>,Blue<7:3> |

Lower order bits should be grounded.

Based on programmed state, and LLCLKIN input, a VIPeR output, ADCCLK is driven back out of the chip. A final status output pin, ADCEN, identifies the state of the ADCEN register bit written by the programmer (in Configuration Register B). Actual choice of ADC (Red<7:0>,Green<7:0>,Blue<7:0>) pixel input, or host bus (BDB<15:0>) pixel input is based on the programmed setting of CPUSYNC register bit in the Control register, address 0x00. The selection is NOT based on the ADCEN register bit setting. ADC input is selected as the input pixel stream if CPUSYNC is reset to 0. The host bus is selected as the input pixel stream is CPUSYNC is set to 1.

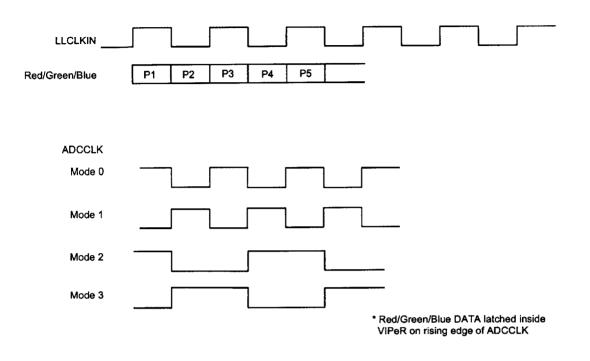

ADCCLK output can be used by the external A/D converter to sample the incoming analog video. LLCLKIN is an input to the VIPeR from the A/D component, which is a digital data clock. VIPeR latches the input digital Red/Green/Blue, based on LLCLKIN, and programmed state. Program choice states allow VIPeR to latch digital input data on either rising or falling edge of LLCLKIN, or on either edge of an internally generated LLCLKIN divided by two signal. Detailed description of programming of choices is given in the register programming section, 5.0.

The ADCCLK output signal reflects the LLCLKIN input. ADCCLK is one of four choices; based on programming of ADCCLKDIV2, and ADCCLKPOL bits in Configuration Register B, address 0x04.

|       | ADCCLKDIV2 | ADCCLKPOL | ADCCLK                           |

|-------|------------|-----------|----------------------------------|

| mode0 | 0          | 0         | inverted LLCLKIN                 |

| mode1 | 0          | 1         | LLCLKIN                          |

| mode2 | 1          | 0         | inverted LLCLKIN, divided by two |

| mode3 | 1          | 1         | LLCLKIN, divided by two          |

In all 4 modes, ADCCLK is delayed about 5 nanoseconds after the referenced LLCLKIN version.

The internal signal VIPeR used to latch the Red/Green/Blue data is effectively the ADCCLK output. It is gated internally by active display time. Active display time is determined by vertical and horizontal delay programmable parameters. These are referenced to input frame and line sync information, respectively.

Functional timing of these modes is shown in Figure 2.2.1.

Internal to VIPeR, pixel data from this ADC interface block, and pixel data from the host interface block are multiplexed together, based on programmable choice of ADC data, or CPU data (as determined by CPUSYNC program bit in Control Register, address 0x00). Result of this multiplexing goes through bit/pixel formatting, to the YUV/RGB conversion circuitry.

# 2.3 Sync Separator

When operating in ADC input data mode (by resetting CPUSYNC register bit in Control Register, address 0x00 to zero), VIPeR is supplied video synchronization information in one of two ways. The first is from the direct FSIN\*, LSIN\*, OFIN inputs. These inputs are low active video frame sync, video line sync, and odd field indicators. The second ADC input data mode synchronization source comes into VIPeR via the composite sync input, CSYNC. The following chart describes the sync source selection, based on the program register bits, CPUSYNC, and SSBYPASSL. SSBYPASSL is a register bit programmed in Configuration Register B, address 0x04.

| CPUSYNC SSBYPASSL |   | Sync Source                                  |

|-------------------|---|----------------------------------------------|

| 0                 | 0 | CSYNC input: fed into sync separator circuit |

| 0                 | 1 | FSIN*, LSIN*, OFIN, inputs: used directly    |

| 1                 | Х | CPUFSL, CPULSL register bits: used directly  |

VIPeR uses the sync source information it chooses, to generate internal vertical and horizontal sync signals, as well as a field indicator signal. These internal video synchronization signals are used to determine active video display times, and to time the processing, digital storage, and display of video information.

When the sync separator is enabled (by resetting CPUSYNC and SSBYPASSL to 0), VIPeR video sync information is gotten from the input composite sync, CSYNC, input. The Sync Separator unit takes TTL level CSYNC and separates it into horizontal and vertical sync components, detects field information, and determines whether the input signal is interlaced or non-interlaced. Using this detection circuitry, it generates internal VIPeR vertical and horizontal sync signals, as well as the field indicator signal. If the sync separator is not activated, and sync input information is coming from one of the other sources, then the internal VIPeR vertical and horizontal sync signals, and the field indicator signal, come directly from the other chosen source. These other chosen sources are FSIN\*/LSIN\*/OFIN inputs, or CPUFSL/CPULSL register bits. In addition to the video control functions discussed above, these internal sync signals are output from the VIPeR on the output pins, VSYNCL, HSYNCL, and FIELD.

When programmed to CPUSYNC=1 mode, the CSYNC, FSINL, LSINL, and OFIN inputs are don't cares for VIPeR. When ADC mode is selected, and the sync separator is enabled, CSYNC input is delivering the video sync information. FSINL, LSINL, and OFIN are don't cares. When ADC mode is selected, and the sync separator is in bypass mode, VIPeR gets its primary video sync information from the FSINL, LSINL, and OFIN inputs. However, CSYNC input is NOT a don't care in this mode. Horizontal sync information must be input to CSYNC (the LSINL input is a good choice to feed into CSYNC as well). Further, the sync separator should still be programmed for the expected video sync frequencies. Programming the sync separator is discussed below, and also in the register programming section, 5.0.

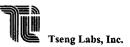

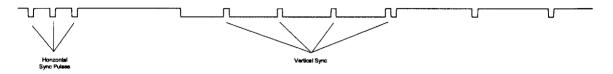

The VIPeR sync separator allows inputting of varying quality composite sync information, from studio quality through consumer grade VCRs in slow motion and fast forward modes. VIPeR can lock to not only a wide quality range of input composite sync signals, but also to a wide range of video input formats, including NTSC, PAL, and SECAM. Because it is user programmable, the sync separator allows VIPeR to lock to non standard video sources as well. The sync separator contains four basic functional sub-units: noise cancellation, horizontal sync separation, vertical sync separation, and field detection. Each of these will be described in the paragraphs below.

The noise cancellation sub-unit filters out any pulses on CSYNC input which are one SCLK time duration or less. Based on 50MHz SCLK, this translates to a filter which removes any CSYNC pulses of less than 20 nanoseconds.

The horizontal sync separator and vertical sync separator sub-units operate in almost identical fashion: one on the line sync information, the other on the frame sync information. In order to program these sync separator sub-units, the programmer must know the general parameters of the composite sync input. These are, the expected horizontal and vertical frequencies.

The sub-units contain timers which the programmer sets. These timers instruct the sync separator to look for input sync pulses in defined time windows, to block out input sync pulses during unexpected times, and reset based on expected sync pulse frequencies.

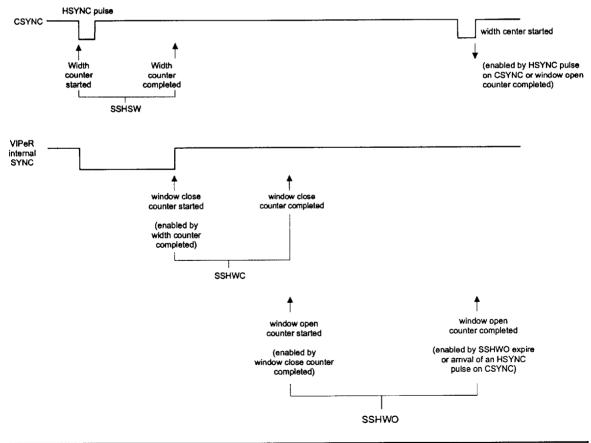

The horizontal sync separator uses three window timer settings to lock onto line sync components of the input CSYNC signal. These are user-programmed values called, Horizontal Sync Width, Horizontal Window Closed, and Horizontal Window Open register/timers. They are accessed as VIPeR registers, at addresses, 0x10, 0x12, and 0x14, respectively. These are discussed in the register programming section, 5.0. Values are programmed in units of number of SCLKs, minus 1.

The width, window closed, and window open register/timers define periods when the VIPeR sync separator is expecting to see horizontal sync pulses.

If the sync separator detects a horizontal sync signal during unexpected (Horizontal Sync Width or Horizontal Window Closed) time, it is ignored. If one is detected in the expected (Horizontal Window Open) time, it is used as the line sync information, passed on as the internal VIPeR horizontal sync signal, and output on HSYNCL. Starting when the internal horizontal sync is detected, the internal horizontal sync signal, as well as the HSYNCL output signal, are activated for a length of time equal to the value programmed in the Horizontal Sync Width register. When the horizontal sync signal is detected on CSYNC during the window open time, the timers reset themselves. If a horizontal sync signal is not detected on CSYNC during the entire horizontal window open period, then the horizontal sync separator sub-unit will create one: based on the expiring of the horizontal window open timer. If this happens, the timers all reset themselves just as if this generated horizontal sync pulse was actually derived from the input CSYNC signal. The internal VIPeR horizontal sync pulse and HSYNCL output activate for the horizontal windowing times.

26 - VIPeR Data Book

Programming the horizontal sync separator requires knowledge of the expected horizontal sync frequency. For NTSC composite video, with a horizontal frequency of 63.5 microseconds, reasonable numbers to set the window timer values (assuming 50MHz SCLK) are as follows.

| Horizontal Sync Width         | 4.7µS  | 0x00EA |

|-------------------------------|--------|--------|

| Horizontal Sync Window Closed | 57.6µS | 0x0B3F |

| Horizontal Sync Window Opened | 6.5µS  | 0x0145 |

These values control the horizontal sync separator as follows. When a horizontal sync is detected (or generated) all the counter/timers reset. The horizontal sync width timer activates first, and at the same time, the internal horizontal sync signal, and the output HSYNCL activate. They remain active for  $4.7\mu$ S (the programmed horizontal sync width value). During this  $4.7\mu$ S, the window for other horizontal sync inputs on CSYNC is closed.  $4.7\mu$ S after the first horizontal sync the horizontal sync width timer expires, and the horizontal sync window closed timer begins. For the next  $57.6\mu$ S (the programmed value), the horizontal sync separator remains closed. Any horizontal sync pulses input on CSYNC will continue to be ignored. This brings us up to  $62.5\mu$ S after the last horizontal sync ( $4.7 \mu$ s 57.6). Now, the horizontal window closed timer expires, and the horizontal sync separator is looking for a horizontal sync pulse on the CSYNC input. IF at any time within this  $6.5\mu$ S window, a horizontal sync is detected, it is used, and the horizontal window open timer immediately closes. This resets everything back to the beginning. If a horizontal sync pulse is not detected on CSYNC for the entire  $6.5\mu$ S window open time, then a horizontal sync is generated, the horizontal window open timer closes, and everything resets back to the beginning again.

The result of this is a digital band pass filter. The larger the open window time, the faster VIPeR will lock to the incoming sync. The trade-off here is that VIPeR is more likely to allow bad pulses on CSYNC to be used as valid horizontal sync pulses.

The vertical sync separator works much the same as the horizontal sync separator, with window width, window closed and window open timers. For the vertical sync separator, however, there is an additional timing parameter, minimum vertical sync pulse width. This timer works similarly to the noise cancellation sub-unit. It watches input vertical sync pulses on CSYNC input, and allows only pulses whose duration are longer than the programmed minimum pulse width to be passed.

The user programmable vertical sync separator window register/timers are Vertical Sync Width, Vertical Window Closed, Vertical Window Open, and Vertical Sync Detector Width (the minimum vertical sync pulse width). They are accessed as VIPeR registers at addresses, 0x18, 0x1A, 0x1C, and 0x16 respectively. Values for the first three registers programmed in units of horizontal syncs pulses, minus 1. Values of the Vertical Sync Detector Width are programmed in system clocks, SCLK, minus 1. For NTSC video inputs, a reasonable value of Vertical Sync Detector Width is 10µS, or about 0x200 for 50MHz SCLK.

The final sub-unit is the field detector. It is controlled by the Field Detection Window Width register, programmable in horizontal sync pulses, minus 1, at VIPeR register address 0x1E. After a vertical sync pulse is received, the field unit counts the programmable number of horizontal syncs, and determines, via the monitored level of the CSYNC input, whether the field is even or odd. Result of this measurement is broadcast to the VIPeR internally, to effect video processing functions, and is output on the FIELD output signal pin.

# 2.4 YUV to RGB Conversion

The VIPER YUV/RGB conversion is done to CCIR601 specification. RGB values range from 0 to 255. YUV values between 0 and 255 are converted, although the specification is from 16 < Y < 235, and 16 < U, V < 240. Resultant RGB values less than 0 are truncated to 0. Resultant RGB values greater than 255 are saturated to 255. Nine bits of precision are maintained throughout the conversion. It is done in real time, as a pipeline delay structure between the input video stream formatting, and the video scaling units. Mathematics of the YUV to RGB conversion are as follows:

Green = Y - (0.698) V - (0.338) U + 132.56 Red = Y + (1.371) V - 175.45 Blue = Y + (1.732) U - 221.75

VIPeR converts YUV data input either from the ADC input port or from the host bus, BDB<15:0> bus. This gives VIPeR the capability of working with either front end A/D converters which deliver digitized live data in YUV format, or playback, scale and convert YUV based stored video.

Three types of YUV formats are accepted, and converted to 24-bit RGB. These are YUV444, and two types of YUV422, YUV422a, and YUV422b where the formats of each are as follows. The YUV422 are inherently 16 bit/pixel modes. YUV444 is 24 bits, 8 each of Y, U, and V.

YUV422a:

| input pixel 1<15:0> = | Y0<7:0>,U0,1<7:0> |

|-----------------------|-------------------|

| input pixel 2<15:0> = | Y1<7:0>,V0,1<7:0> |

| input pixel 3<15:0> = | Y2<7:0>,U2,3<7:0> |

| input pixel 4<15:0> = | Y3<7:0>,V2,3<7:0> |

| etc                   | ,,,,              |

YUV422b:

| input pixel $1 < 15:0 > =$ | Y0<7:0>,U0,1<7:4>,V0,1<7:4> |

|----------------------------|-----------------------------|

| input pixel 2<15:0> =      | Y1<7:0>,U0,1<3:0>,V0,1<3:0> |

| input pixel $3 < 15:0 > =$ | Y2<7:0>,U2,3<7:4>,V2,3<7:4> |

| input pixel 4<15:0> =      | Y3<7:0>,U2,3<3:0>,V2,3<3:0> |

| etc                        |                             |

The YUV422 are inherently 16 bit/pixel modes. YUV444 is 24 bits, 8 each of Y, U, and V.

Further, the byte lanes of the Y versus UV data can be switched via setting program bit YLSBIN, bit 10 in Configuration Register B, address 0x04. This feature, however, is available in Rev.B silicon only.

## 2.4.1 Playback YUV/RGB Conversion

For playback of stored video in YUV mode, YUV422a is by far the most popular format, so we will detail that mode here. The host CPU delivers YUV422a mode pixels to VIPeR over the BDB<15:0> lines. In general, Y<7:0> is input on the most significant byte of the input pixel, and UV<7:0> is input over the least significant byte. U,V is time multiplexed, so that pixels alternate YU, or YV samples. VIPeR then does a linear interpolation of the 2:1 subsampled U and V values to bring the YUV up to 24 bits per pixel. This 24-bit YUV is then input to the actual conversion block to create the 24 bit RGB output. This 24-bit RGB output, This 24-bit RGB output then goes on to the video scaling units (described in Section 2.5). Programmer has option of switching the VIPeR interpretation of data to be Y in the LSB and UV in the MSB, by setting YINLSB. In this case, CPU must deliver the Y data in the LSB, etc.

28 - VIPeR Data Book

# 2.4.2 YUV/RGB Conversion of Live Video, via ADC Input Port

VIPeR accepts YUV formatted video input to its ADC (Red<7:0>, Green<7:0>, and Blue<7:0>) input pins as well. Again, more popular front end A/D conversion components output YUV422, so we detail that mode here. Just as with the host input, VIPeR accepts the YUV422 input data on ADC, and multiplexing it with the host bus, feeds it to the YUV422 interpolator, and then on to the YUV to RGB conversion. 2:1 subsampled UV data is brought up to full resolution by the linear interpolator, to take input YUV422 to YUV444, 24 bit/pixel. Then, this 24-bit YUV is changed to 24-bit RGB and fed into the video scaling units.

Inputting YUV422 video to the ADC pins must follow this convention:

| Input Data | ADC Pin Input |

|------------|---------------|

| Y<7>       | RED<7>        |

| Y<6>       | RED<6>        |

| Y<5>       | RED<5>        |

| Y<4>       | RED<4>        |

| Y<3>       | RED<3>        |

| Y<2>       | GREEN<7>      |

| Y<1>       | GREEN<6>      |

| Y<0>       | GREEN<5>      |

| UV<7>      | GREEN<4>      |

| UV<6>      | GREEN<3>      |

| UV<5>      | GREEN<2>      |

| UV<4>      | BLUE<7>       |

| UV<3>      | BLUE<6>       |

| UV<2>      | BLUE<5>       |

| UV<1>      | BLUE<4>       |

| UV<0>      | BLUE<3>       |

RED<2:0>, GREEN<1:0>, and BLUE<2:0> input pins should be grounded.

# 2.5 Horizontal/Vertical Scaling

The VIPeR scaler can be used to convert either live video or stored video to arbitrary sizes in both the horizontal and vertical dimensions. It calculates visually correct images at up to one pixel per clock cycle. By smoothly scaling via an area average algorithm, VIPeR uses all of the incoming video to create the resulting scaled output video. In scaling down, no pixels are dropped, and no lines are dropped. Rather, all the incoming pixels and lines are used: every bit of the incoming data has a contribution to generating the output video stream. In scaling video up, no pixel replication or line replication is done. Similarly, all the incoming video is weighted and used to generate the output video stream. By using this sophisticated area averaging algorithm, very high quality video scaling is done: visible artifacts in the scaling are minimized.

In order to program the VIPeR horizontal and vertical scaling units, the CPU passes the input and desired output horizontal and vertical video resolutions. The VIPeR software driver then calculates the program register loads required to scale from the input video resolutions to the output video resolutions. Programmed registers that control the scaling are:

| X Scaling Coefficient  | register address 0x30 |

|------------------------|-----------------------|

| XK Scaling Coefficient | register address 0x32 |

| Y Scaling Coefficient  | register address 0x34 |

| YK Scaling Coefficient | register address 0x36 |

Since the video scaling algorithm is Tseng Labs confidential, the programming of these registers is undocumented. VIPeR driver software calculates the register values based on the horizontal and vertical input and output scaling resolutions.

VIPeR can scale video from 1024x1024 input resolution to 16x16 output resolution in one extreme, and from 16x16 input resolution to \*720x1024 output resolution in the other extreme. All other input to output scaling factors within this range are possible.

\*720x1024 for VIPeR Rev.B. 640x1024 for VIPeR Rev.A.

When scaling live video, as input from the ADC input port (Red<7:0>, Green<7:0>, Blue<7:0), the maximum frequency which the input pixel stream can come into the VIPeR is 1/2 SCLK frequency. Based on SCLK frequency, this could potentially limit the maximum video input resolution. A constraint on the scaling is imposed for video coming into the VIPeR over the ADC port. Since VIPeR must generate lines of video when scaling up in the vertical dimension, data overruns can occur based on VIPeR processing, W32/W32i/W32p ability to accept the VIPeR output video stream, and the horizontal video resolutions. In general, no data overruns leading to visible artifacts will occur if the video vertical output resolution is no greater than the video vertical input resolution. Care must be taken in scaling up ADC input video by ratios of between 1 and 2. Scaling up video to factors greater than 2:1 in the vertical dimension is not recommended for ADC input video streams, unless provision can be made to "stall" the input video stream based on instantaneous VIPeR video processing status. This video processing status information is discussed below.

When scaling stored video, as input from the host bus (BDB<15:0>), the full range of video scaling ratios are possible. Maximum video input rate over the host bus is determined by host bus clock frequency, as determined by the W32/W32i/ W32p, and by the host bus configuration: either BDB mode or DD mode. See Section 2.1 for a description of these host bus modes. As an example, while operating in DD host bus mode, at 33MHz, W32/W32i/W32p writes a new pixel to VIPeR at about a 5-6 Mpixel/sec rate. At 16bpp, this is about 10-12 Mbytes per second. These rates are more than sufficient to write typical format, typical resolution stored video streams, such as Microsoft Video for Windows, .AVI files, Indeo format, Cinepak format, and MPEG1 video streams. Care must be taken when vertically scaling up input video from the host bus. As was mentioned for the ADC port live video input, when VIPeR is generating lines for vertically scaled up video, care must be taken to throttle the input video stream so as to not create data overruns in the IMA (W32 interface) FIFO. This throttling is more easily done when input video comes over the host bus, since the CPU controls the data flow rate directly. Throttling can be accomplished by software monitoring, via periodic register reads, of the IMA FIFO empty flag. This flag is the EMPTY register status bit in Status Register B, address 0x0A. When the FIFO is empty, the CPU can safely send the next line of input video, which triggers VIPeR to deliver not only that output scaled video line, but potentially other generated video lines of output data when scaling up in the vertical direction.

The VIPeR scaling algorithm, and data input stream sources supported, make VIPeR ideal for live video scale and show, for video capture (when used in conjunction with W32/W32i/W32p), and for scaled video playback of stored video.

# 2.6 External Mask DRAM Control

## Overview

VIPeR has a 256Kx4 DRAM controller which it uses to access alpha bit (mask overlay) information from an external 256Kx4 DRAM. VIPeR passes one bit per pixel, over the IXMSK output to the W32x, as an alpha bit paired with each video pixel. The W32x then uses this alpha (or mask) bit to determine whether video or graphics data should be written into the frame buffer at that pixel location. In this way, video/graphics overlaying, and pixel by pixel mixing of video and graphics is done.

The external (optional) DRAM overlay mask is controlled by the VIPeR's preset operating modes, and it's programming. The mask DRAM can be written at any time via sequences of register accesses to the mask control register, address 0x38, and to the VIPeR data address space, 0x400-0x7FF. However, it is strongly recommended that writes happen only during non-active video display times. A CAS before RAS refresh cycle, in addition to the accessed row refresh, occurs whenever a mask DRAM write is done.

The mask DRAM is *not* directly readable through the VIPeR. Contents of the DRAM can be indirectly inferred by loading various video, graphics, and mask patterns, running video into the graphics frame buffer, and downloading the contents of the frame buffer through the W32x. Contents of the mask DRAM are read out, and paired up with corresponding video pixels, during active video display times. Addressing is done automatically based on the VIPeR's current internal line and pixel numbers. Two refresh cycles are done every video scan line: one read access refresh to the row corresponding to that particular video line, and one CAS before RAS refresh cycle, triggered by the horizontal sync pulse.

## **Data Organization**

The mask DRAM is organized logically into 512 rows and 512 columns, each of 4 bits. The mask DRAM is programmed, and VIPeR interprets the data, as one bit of mask for each video pixel. Each mask bit is paired up (by the VIPeR) with the corresponding video pixel it is generating, and sent over the IMA port to the W32x. The W32x uses this mask bit to mix the video and graphics in the single frame buffer. The optional masking capability is enabled by setting IXMSKEN, bit 14 in VIPeR register 0x02. The polarity of the read out mask bit can be inverted by setting IXMSKPOL, bit 15 in VIPeR register 0x02.

When reading data out of the mask DRAM during active video display time, the VIPeR associates it's current line number with a row address in the mask DRAM. Rows addresses are accessed in descending order: video display line number 0 corresponds to mask DRAM row address 511, video display line number 1 corresponds to mask DRAM row address 510, and so forth. The final video display line number N corresponds to mask DRAM address (511-N). Horizontally, the mask DRAM data within each row address (within each video display line) corresponds directly to video display pixel number. The first video display pixel, pixel 0, corresponds to column address 0. Since the data in the mask DRAM is 4 bits per location, however, there are 4 mask bits read by the VIPeR every access. The VIPeR stores 4 bits of mask for each access and pairs them up as the following. For video display pixels 0-3, column address 0 is used, and the data is taken from bits 0-3 for pixels 0-3. Therefore upon writing the mask DRAM pattern, the programmer can think of the mask data pattern as looking physically like the video screen, with inverted row addresses (inverted line numbers).

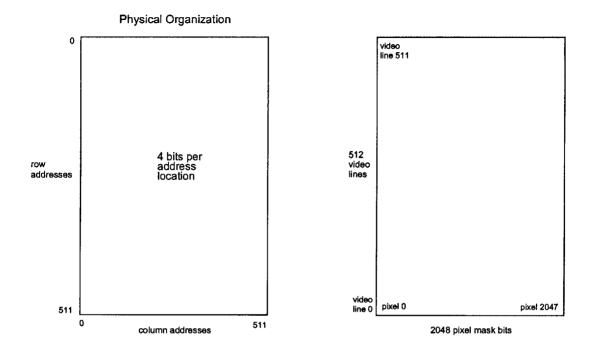

The organization of the mask data, in this case, is 512 video lines vertically, by 2048 video pixels horizontally. This is the default organization mode: when MSKCOL8, bit 10 in register 0x38 is reset to zero. An alternate organization, one useful for video display formats with greater than 512 scan lines (like PAL) is discussed below. See figure 2.6.1, Default Mask DRAM Organization

Figure 2.6.1, Default Mask DRAM Organization

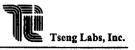

## 2.6.1 Split mask DRAM modes

Setting MSKCOL8, bit 10 in register 0x38, forces the column address to range from 256-511 when reading mask data during active video display. In this mode, the active display column address equals the current pixel number (divided by 4, for 4 mask bits per column address) plus the offset column address in the most significant bit. In this mode, the mask data can be thought of as two different mask patterns, each of 512 rows by 256 columns, or 512 lines by 1024 pixels. An additional mode, enabled by setting G512LINES, bit 6 in address 0x02, enables wrap over of the two mask patterns. When video line number is less than 511, the lower half column addresses are accessed: when the video line number, N, becomes greater than 511 (like for the bottom of a PAL screen) the row addresses go to N-511, and the column addresses go to (pixelnumber/4 + 256) See split mask dram organization, Figure 2.6.2.

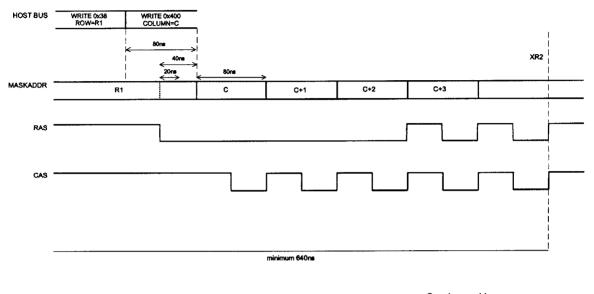

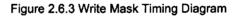

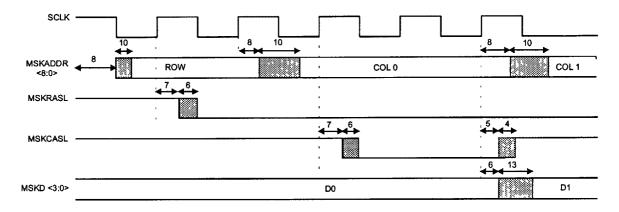

#### 2.6.2 Write Sequence

The mask DRAM is written by first programming the desired row address in mask control register, address 0x38. In addition, CPUMSKWRL, bit 11 must also be reset. The MSKCOL8 bit is also set to the desired value based on whether split mask DRAM mode is being used or not. This register access loads the desired row address to be written, tells the host bus interface logic to interpret subsequent accesses to addresses 0x400-0x7FF as mask DRAM write data, as well as enabling the mask DRAM write state machine in the VIPeR.

After this is done, a write is done to an address in the 0x400-0x7FF range. The lower 7 bits of this register address define the upper 7 (of 9) column address to bits to be written to. The lower 2 bits of the column address are provided by sequencing of an internal VIPeR state machine during the actual mask DRAM write sequence. Sixteen bits of data associated with this register access are then loaded by the VIPeR and written in 4 CAS write cycles, to 4 consecutive column addresses to the mask DRAM.

After the 4 CAS write cycles (writing 16 bits of data) are completed, a CAS before RAS refresh cycle is completed. Timing of the write cycling is NOT programmable, however, it is done slowly enough so that 80 ns DRAMs can be used.

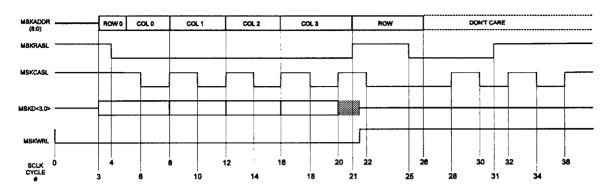

To ensure proper execution of the write cycles the programmer must wait a minimum of 640 nanoseconds between subsequent mask DRAM writes. The 640 nanoseconds is measured from one access to 0x400-0x7FF to the next 0x400-0x7FF access. See write mask timing diagram, Figure 2.6.3

C=column address R1=row address

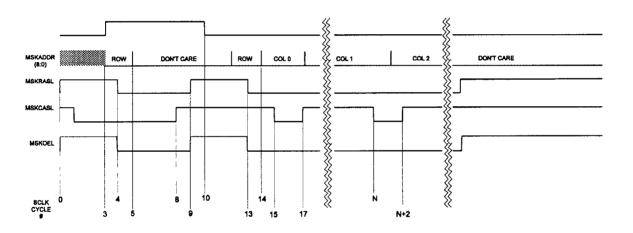

#### 2.6.3 Read Sequence

The mask DRAM is read by the VIPeR during active video display times. Addressing is done automatically by internal vertical line and horizontal pixel number counters. The row address, and a RAS cycle is done at the beginning of every video scan line (as initiated by horizontal sync). The row address is equal to the inverted video scan line, or the video scan line minus 511, if G512LINES is set to 1, and the current pixel line number is greater than 511.

CAS cycles are initiated by the VIPeR for every fourth video pixel. Timing of the access is controlled by internal VIPeR state machines. Column address is equal to the video pixel number, divided by four.

At the end of every scan line, a CAS before RAS refresh is executed.

#### 2.6.4 Special refresh considerations

While displaying video, refreshes to the mask DRAM occur at effectively twice the video line rate. While writting data to the mask DRAM, refreshes occur once for the specific row being written, and one CBR refresh. When CPUMSKWRL is left active (reset to 0), CBR refreshes happen automatically, one every 1.28 usec. Care must be taken when leaving CPUMSKWRL set to 1, and with no mask writes, or with no active video data moving through the VIPeR. In this case, refreshes to the mask DRAM do NOT occur, and data loss may result. If VIPeR is left in CPUMSKWRL=1 mode, with no video input, and no mask DRAM writes, for greater than the mask DRAM refresh time requirements, the mask DRAM data will need to be reloaded before video can be enabled.

## 2.7 Processed Data Output

VIPeR has a 25 pin processed data output bus. It consists of a strobe signal, PSTBL, and 24 data outputs, PRED<7:0>, PGREEN<7:0>, PBLUE<7:0>. The data signals are the direct output of the horizontal and vertical scaling units.

PSTBL is the data valid strobe associated with the output data. It is driven low for 1 SCLK duration whenever a new pixel is output on PRED, PGREEN, PBLUE. PSTB is driven 5 ( $\pm$ 3) nanoseconds after the <u>falling</u> edge of SCLK. Pixel data output on PRED, PGREEN, PBLUE is driven 5 ( $\pm$ 3) nanoseconds after the <u>rising</u> edge of SCLK. PSTB lags the pixel data outputs by ½ SCLK.

Pixel data on PRED<7:0>, PGREEN<7:0>, and PBLUE<7:>, hereafter referred to as PRGB, reflects the input programmed pixel resolution. 24 bits of PRGB are always output, however, lower bits of PRGB are padded with zeros if the input pixel resolution is less than 24 bits/pixel. For example, if the input pixel source is 16 bit, RGB565, then PRED<2:0>, PGREEN<1:0>, PBLUE<2:0>, will appear always as logic value 0. In YUV422 mode, although the input pixel resolution source is really 16 bit/pixel, VIPeR is internally interpolating (thereby expanding) the data up to 24 bit/pixel. PRGB outputs are the full 24 bits for YUV422 modes.

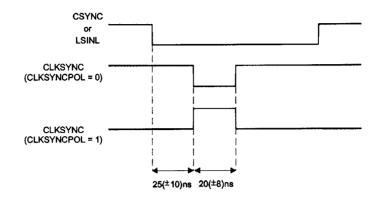

This PRGB output pixel data is the result of input processing, YUV/RGB conversion (if selected) and the horizontal and vertical scaling. It is the pixel data stream as it is input to the W32 interface Image Data Port unit. There it is FIFO'd, converted to the programmed output pixel resolution, and delayed (stored in the FIFO) until the W32/W32i/W32p is able to take the data. In general, the PRGB pixel output is earlier than the pixel output stream on the Image Data Port. Also, since it is delivered 24 bit/pixel, and the Image Data Port is time multiplexed down to 8 bit per clock cycle output, the PRGB data can come out at higher frequency.