## 3.3 Electrical Specifications

## 3.3.1 Maximum Ratings

| Storage temperature                                 | -40 to +125° C       |

|-----------------------------------------------------|----------------------|

| Operating free-air temperature range                | 0 to +70° C          |

| Supply voltage applied to ground potential          | -0.5 to +7.0 V       |

| DC voltage applied to outputs for high output state | -0.5 to Vdd max.     |

| DC input voltage                                    | +4.75V to +5.25 V    |

| Supply current                                      | 200mA typ / 300 max. |

| Analog output current                               | 45mA                 |

| Reference current                                   | -15mA                |

### 3.3.2 Electrical Characteristics

The following condition applies unless otherwise specified:  $T(A) = 0 + 70^{\circ} \text{ Vdd} = 5.0 \text{ V} \pm 5\%$

| DC Characteristics Over Operating Temperature |                                       |                                  |                       |              |      |      |          |

|-----------------------------------------------|---------------------------------------|----------------------------------|-----------------------|--------------|------|------|----------|

| Symbol                                        | Parameter                             | I/O Cell                         | Condition             | Min.         | Тур. | Max. | Unit     |

|                                               |                                       | ΠL                               |                       | 2.0          |      |      |          |

| V <sub>H</sub>                                | High Level Input Voltage              | CMOS                             |                       | 3.5          |      |      | l v      |

|                                               |                                       | CMOS Schmidt trigger             |                       | 4.0          |      |      | 1        |

|                                               |                                       | TTL                              |                       |              |      | 0.8  |          |

| V <sub>IL</sub>                               | Low Level Input Voltage               | CMOS                             |                       |              |      | 1.5  | V        |

|                                               |                                       | CMOS Schmidt trigger             |                       |              |      | 1.0  | 1        |

| I <sub>H</sub>                                | High Level Output Current             | Input buffer                     | V <sub>IN</sub> =VCC  | -10          | 1    | 10   | uA       |

|                                               |                                       | Input buffer with pull-<br>down  |                       | 10           |      | 200  |          |

| 1 <sub>L</sub>                                | Low Level Output Current              | Input buffer                     | V <sub>IN</sub> =GND  | -10          |      | 10   | uA       |

|                                               |                                       | Input buffer with pull-<br>up    |                       | -200         |      | -10  |          |

|                                               |                                       | BT2, BD2 TTL                     | I <sub>OH</sub> =-2mA |              |      | 1    | ·        |

|                                               |                                       | BT4, BT4 TTL                     | I <sub>OH</sub> =-4mA | 2.4          | 1    |      | l        |

| V <sub>OH</sub>                               | High Level Output Voltage             | BT8, BD8 TTL                     | I <sub>OH</sub> =-8mA | 1            |      |      | V        |

|                                               |                                       | BTPCI, BDPCI TTL                 | I <sub>OH</sub> =-2mA | 2.4          | 1    |      | 1        |

|                                               |                                       | ALL TTL                          | I <sub>OH</sub> =-1uA | VCC-<br>0.05 |      |      |          |

|                                               |                                       | BT4, BD4 CMOS                    | I <sub>OH</sub> =-4mA | 3.5          |      |      | 1        |

|                                               |                                       | BT2, BD2 TTL                     | I <sub>OL</sub> =2mA  |              |      |      | <u> </u> |

|                                               |                                       | BT4, BT4 TTL                     | I <sub>OL</sub> =4mA  | 1            |      | 0.5  |          |

| Vol                                           | Low Level Output Voltage              | BT8, BD8 TTL                     | I <sub>OL</sub> =8mA  | 1            |      | ĺ    | V        |

|                                               |                                       | BTPCI, BDPCI TTL                 | I <sub>OL</sub> =6mA  |              |      | 0.55 | 1        |

|                                               |                                       | ALL TTL                          | I <sub>OL</sub> =1uA  |              | 1    | 0.05 | 1        |

|                                               |                                       | BT4, BD4 CMOS                    | I <sub>OL</sub> =4mA  |              | 1    | 1.5  | 1        |

|                                               |                                       | Output buffer                    |                       | -10          |      | 10   |          |

| loz                                           | High Impedance Leakage current        | Output buffer with pull-         | Vout=VCC or           | -200         |      | -10  | uA       |

|                                               |                                       | up                               | GND                   |              |      |      |          |

|                                               |                                       | Output buffer with pull-<br>down |                       | 10           |      | 200  |          |

| Vн                                            | Schmidt Trigger<br>Hysteresis Voltage |                                  |                       |              | 0.6  |      | V        |

NOTE: The MDRAM outputs (see pins below) are specifically designed to work into  $220\Omega$  loads, to VDD and ground, with reduced swing and a 50 percent duty cycle to achieve the high data exchange rate. Different loads may affect performance.

| MDRAM Outputs        |                |  |  |  |

|----------------------|----------------|--|--|--|

| Pins Function        |                |  |  |  |

| MD1<15:0>, MD0<15:0> | input/output   |  |  |  |

| MM1<1:0>, MM0<1:0>   | input to MDRAM |  |  |  |

| CLK1, CLK0           | input to MDRAM |  |  |  |

### 3.3.3 DAC Characteristics

| Symbol               | Parameter                        | Conditions         | Min. | Max. | Units |

|----------------------|----------------------------------|--------------------|------|------|-------|

| V <sub>REF</sub>     | Reference voltage                |                    | 1.10 | 1.35 | V     |

| Vo (max)             | Maximum output voltage           | lo≤ 10mA           |      | 1.5  | V     |

| I <sub>O</sub> (max) | Maximum output current           | V <sub>o</sub> ≤1V |      | 21   | mA    |

|                      | Full scale error                 | note A, B          |      | ±5   | %     |

|                      | DAC to DAC correlation           | note B             |      | ±2   | %     |

|                      | Integral linearity, 6-bit        | note B             |      | ±0.5 | LSB   |

|                      | Integral linearity, 8-bit        | note B             |      | ±1   | LSB   |

|                      | Full-scale settling time*, 6-bit | note C             |      | 28   | ns    |

|                      | Full-scale settling time*, 8-bit | note C             |      | 20   | ns    |

|                      | Rise time (10% to 90%)*          | note C             |      | 6    | ns    |

|                      | Glitch energy*                   | note C             |      | 200  | pVsec |

<sup>\*</sup> Characterized values only

#### 3.3.4 PLL Characteristics

| Symbol           | Parameter                                                     | Conditions                        | Min.   | Max.  | Units |

|------------------|---------------------------------------------------------------|-----------------------------------|--------|-------|-------|

| F <sub>D</sub>   | Frequency change of CLK0 and CLK1 over supply and temperature | With respect to typical frequency |        | 0.05  | %     |

| fo               | CLOCK0 operating range*                                       |                                   | 25     | 135   | MHz   |

| f <sub>1</sub>   | CLOCK1 operating range*                                       |                                   | 25     | 135   | MHz   |

| dt               | Duty cycle*                                                   |                                   | 40/60  | 60/40 | %     |

| j <sub>1s</sub>  | Jitter, one sigma*                                            |                                   |        | 130ps | ps    |

| jabs             | Jitter, absolute*                                             |                                   | -300ps | 300ps | ps    |

| f <sub>ref</sub> | Input reference frequency                                     | typically 14.318MHz               | 5      | 25    | MHz   |

#### NOTES:

A. Full scale error is derived from design equation

$${[(F.S.I_{out})R_L - 2.1 (I_{REF})R_L]/[2.1(I_{REF})R_L]} 100\%$$

V<sub>BLACK LEVEL</sub> = 0V F.S.I<sub>OUT</sub> = Actual full scale measured output

B. R = 37.5

$$\Omega$$

, I<sub>REF</sub> = -8.88mA, J<sub>REF</sub> = V<sub>REF</sub>/R<sub>SET</sub>

C.

$$Z_1 = 37.5\Omega + 30pF$$

,  $I_{REF} = -8.88mA$

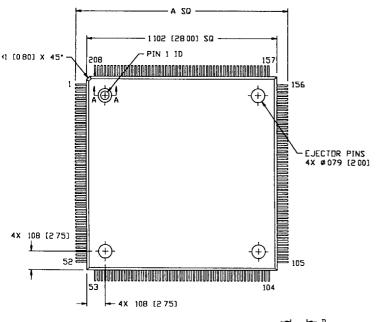

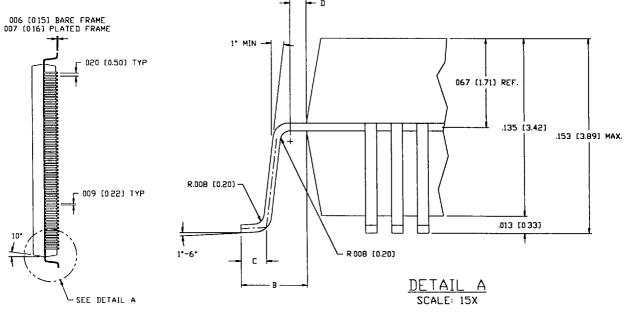

# **Appendix C. Mechanical Specification**

#### ET6000 208-pin Plastic Quad Flat Package