## F9450 High-Performance 16-Bit Bipolar Microprocessor

#### **General Description**

The National F9450 microprocessor is the nucleus of a family of high-performance devices intended for commercial and military applications requiring sophisticated, high-speed, real-time processing. It has, on-chip, all of the functions necessary to perform floating-point operations without the use of a coprocessor. Other on-chip capabilities allow addressing of up to 2M words of memory and, with the addition of the optional F9451 Memory Management Unit (MMU), up to 16M words of memory.

Real-time processing is achieved through advanced architecture that incorporates two programmable timers, user-accessible general-purpose registers, a complete 16-level interrupt processor, and a comprehensive fault handler on the chip. Multiprocessing is supported by a flexible bus arbitration scheme, as well as process synchronization (test and set) instructions.

The F9450 instruction set is optimized for complex real-time applications. It implements the complete MIL-STD-1750A instruction set architecture (ISA) and its floating-point standard on a single chip.

The F9450 family of support circuits and systems provides additional capabilities, including memory-mapped expansion with the F9451 MMU.

Comprehensive software support for the F9450, including assemblers, loaders, simulators, and compilers, is provided by National and other sources. Software development for the F9450 can be performed using the VAX-11/7XXTM computers using the VMSTM operating system.

For complete information on available support circuits and software, contact your local National Sales Office or the Microcontroller Division.

#### **Features**

- Single-chip 16-bit microprocessor with 32- and 48-bit floating-point arithmetic on-chip

- Real-time processing: Two programmable timers, 16 levels of vectored interrupt

- Address space of up to 2M words, expandable to 16M words with optional F9451

- Instruction set optimized for real-time applications (MIL-STD-1750A ISA)

- Built-in self-test, fault handling, and abort

- Twenty-four user-accessible registers

- Built-in multiprocessor capabilitiesSingle- and double-precision integer arithmetic

- Built-in console operations

- Complete high-level language and design development support available

- Static operation with single clock: 0 MHz-20 MHz

- TTL inputs and outputs with 8 mA drive capability

- Small size 64-pin DIP or surface-mount packages

Full performance over −55°C to +125°C operating temperature range

- Bipolar I3L® technology

TRI-STATE\* and I<sup>9</sup>L\* are registered trademarks of National Semiconductor Corporation VAX\*M and VMS\*M are trademarks of Digital Equipment Corporation.

### **Table of Contents**

#### DESCRIPTION

Features

#### **F9450 SYSTEM ARCHITECTURE**

Data Types Register Set

SW Register

SCR Register Timer A and Timer B

Instruction Set

MIL-STD-1750A Description

Addressing Modes Instruction Execution Times

Interrupts

Fault and Error Handling

Instruction Abort Fault Register (FT)

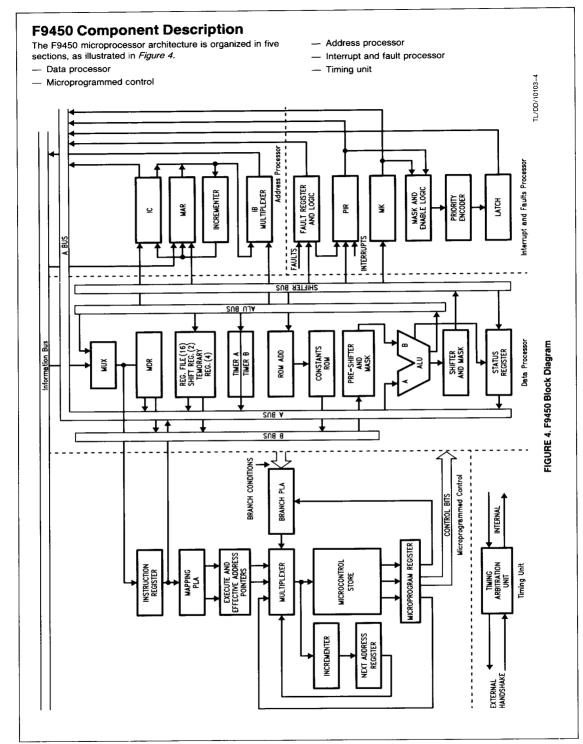

#### **F9450 COMPONENT DESCRIPTION**

Data Processor Microprogrammed Control

Address Processor

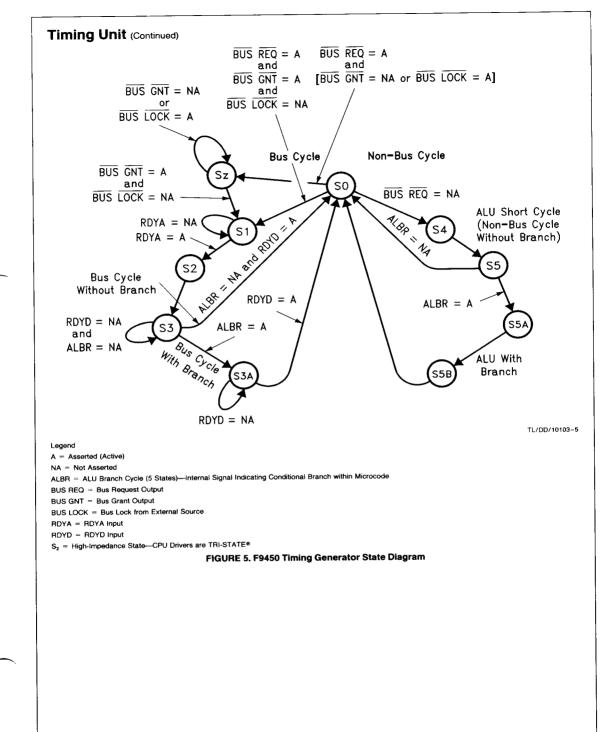

Interrupt and Fault Processor Timing Unit

Self-Test and Initialization

#### CONSOLE OPERATIONS

**Entering Console Mode**

Use of Console Mode

Exiting Console Mode

#### SIGNAL DESCRIPTIONS

DEVICE OPERATION

**Bus Transactions**

**TIMING CHARACTERISTICS**

ABSOLUTE MINIMUM/MAXIMUM RATINGS

RECOMMENDED OPERATING RANGES

DC CHARACTERISTICS

#### SYSTEM IMPLEMENTATION

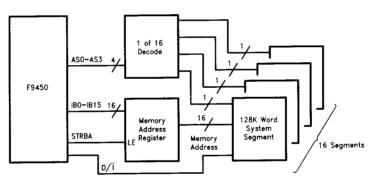

F9450 Address Space Implementation

Memory Expansion

Memory Expansion without an MMU

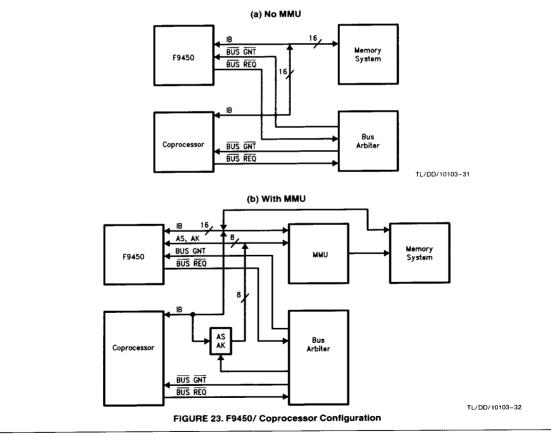

**Built-In Function Implementation** with an External Coprocessor

ORDERING INFORMATION

PACKAGE INFORMATION

### List of Illustrations

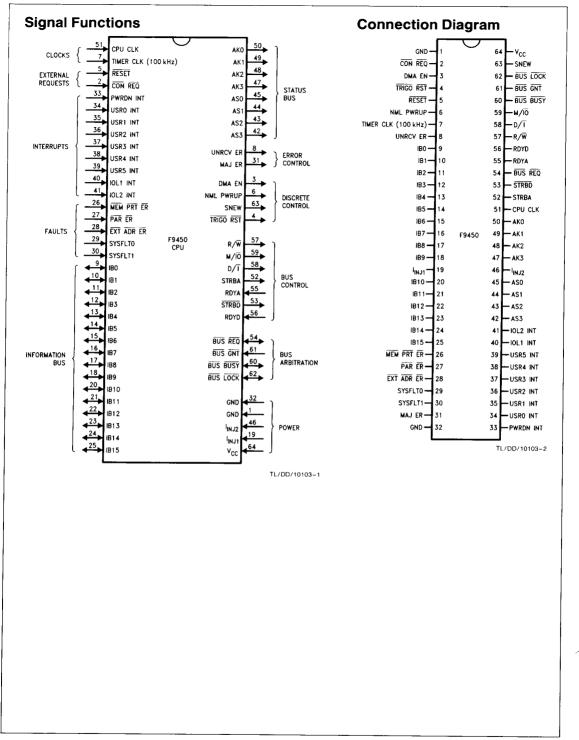

| Signal Functions Diagram                               | 4  |

|--------------------------------------------------------|----|

| Connection Diogram                                     |    |

| FOASO Slooting Point Formats                           |    |

| FOAFO Programmor's Register Model                      |    |

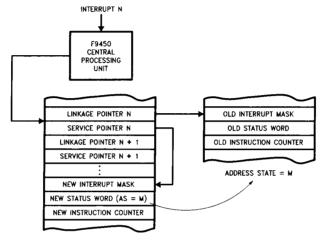

| Intermed Voctors                                       |    |

| FOASO Block Dingram                                    |    |

| FOAFO Timing Congretor State Diagram                   | 20 |

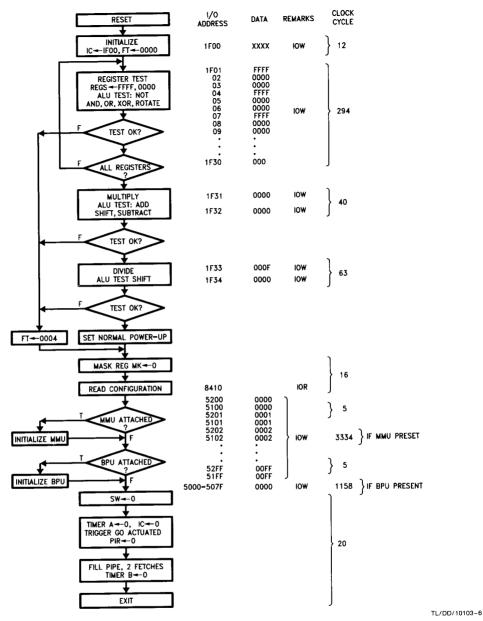

| Colf Toot and Initiatization Sequence                  |    |

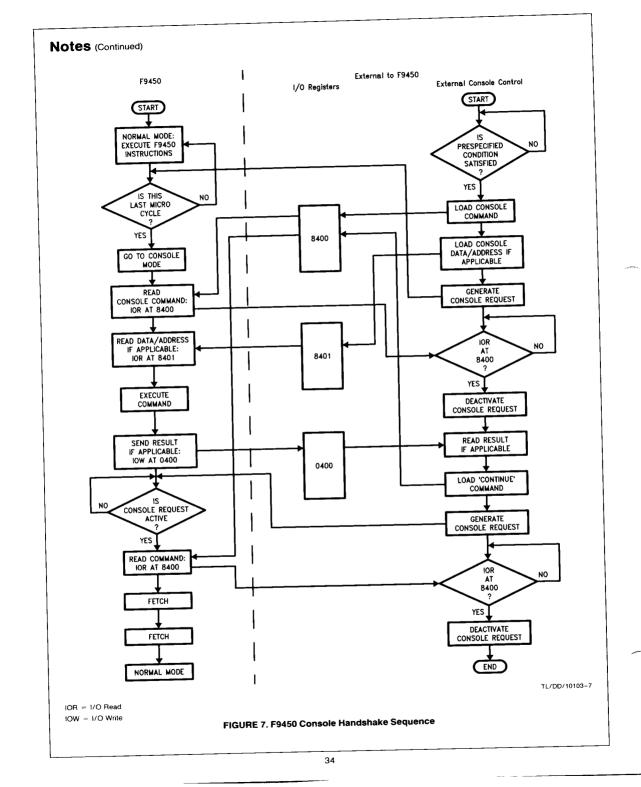

| F0450 Concolo Handshake Seguence                       |    |

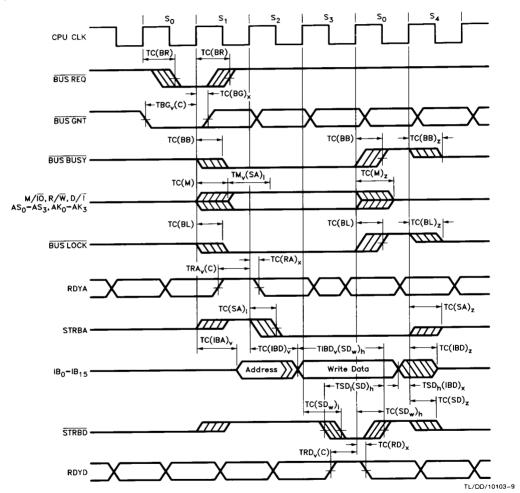

| Our Appear Cignal Paguirements                         |    |

| Minimum Write Bue Cycle Timing Diagram                 |    |

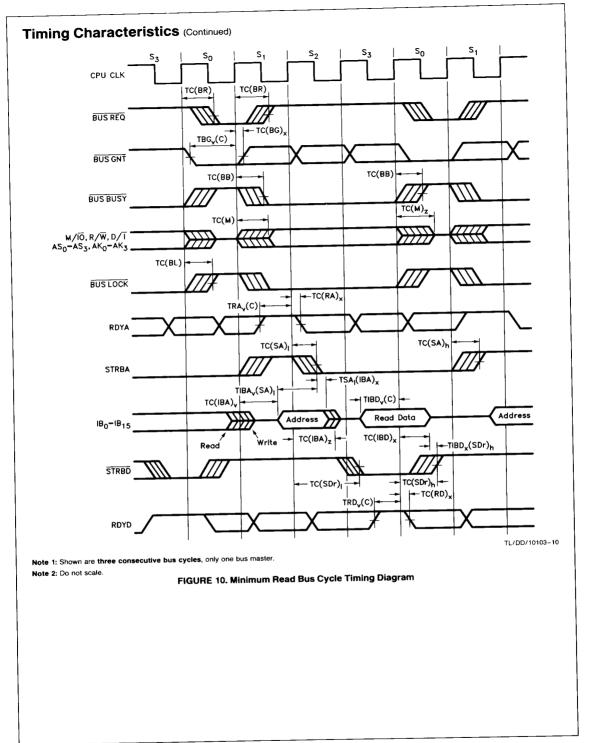

| Minimum Bood Rus Cycle Timing Diagram                  |    |

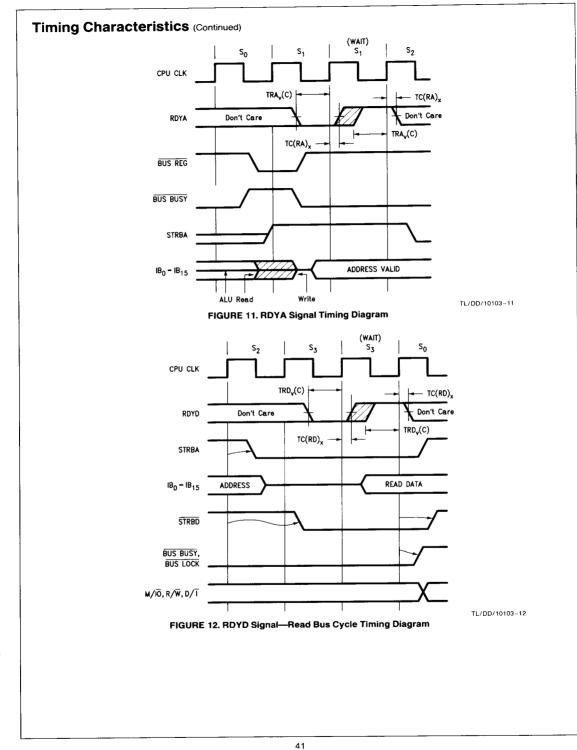

| DDVA Cignal Timing Diagram                             |    |

| DDVD Signal - Boad Bus Cycle Timing Diagram            |    |

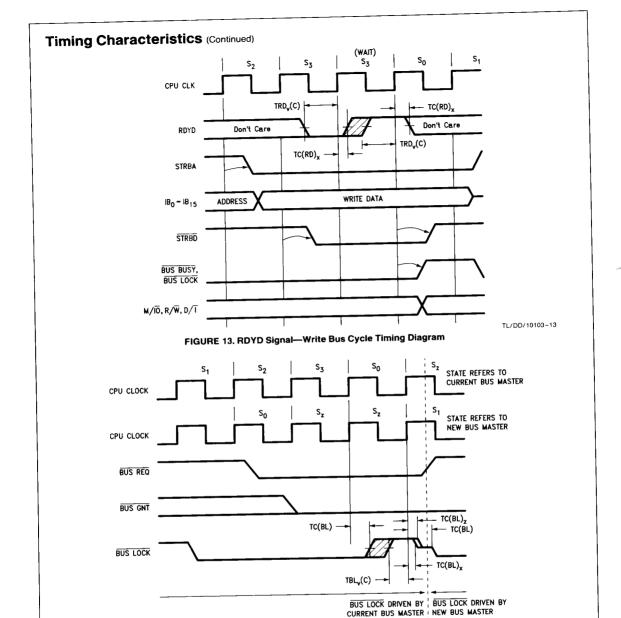

| DDVD Signal - Write Rus Ovele Timing Diagram           |    |

| Cional Requirements for Accessing Rus                  |    |

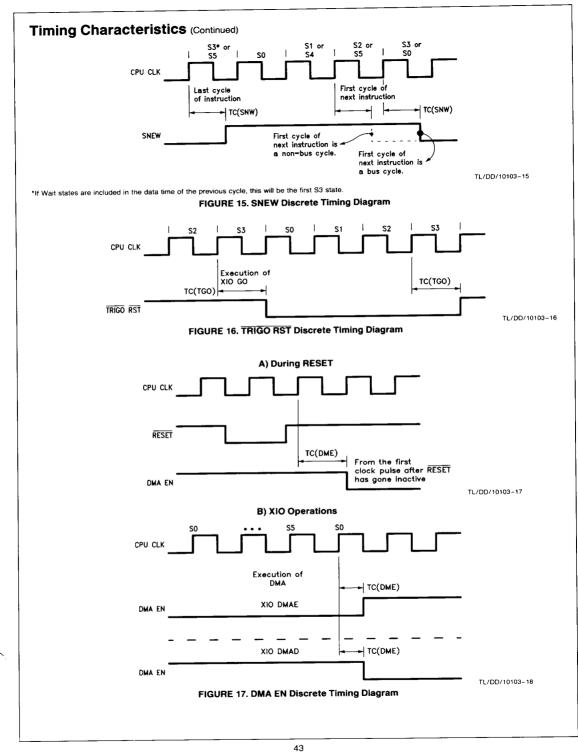

| SNEW Discrete Timing Diagram                           |    |

| TRICO RST Discrete Timing Diagram                      |    |

| DMA EN Dicercto Timing Dicercam                        | 43 |

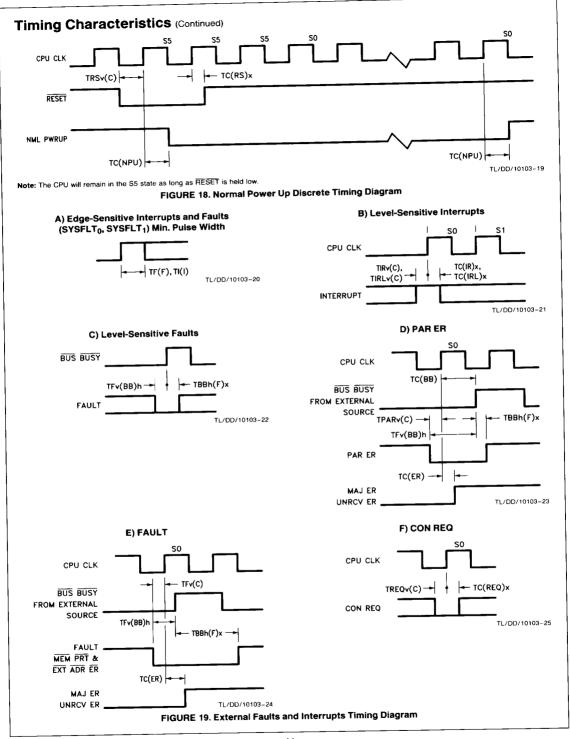

| Normal Power Lto Discrete Timing Diagram               |    |

| External Faults and Interrunts Timing Diagram          |    |

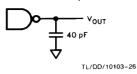

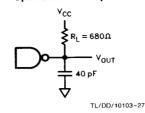

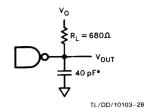

| Switching Time Test Circuits                           | 45 |

| Typical Memory Subsystem Minimum Configuration         |    |

| Typical Segmented 2M Word Memory System                | 52 |

| F9450/Coprocessor Configurations                       | 55 |

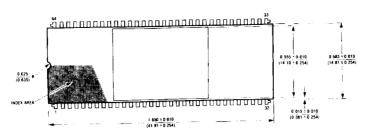

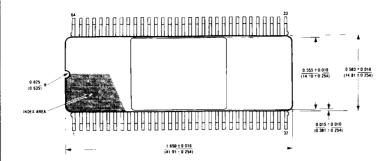

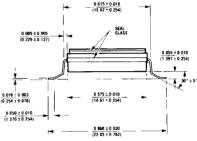

| 64-Pin Ceramic Dual-In-Line Package                    | 56 |

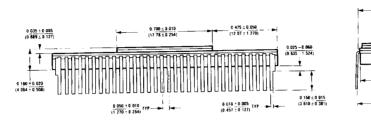

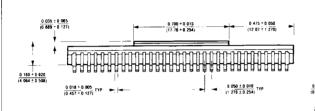

| 64-Pin Ceramic Gull-Wing Dual-In-Line Package          |    |

| List of Tables                                         |    |

|                                                        | ρ  |

| F9450 Addressing Modes and Instruction Formats         | 9  |

| F9450 Instruction Execution Times                      | 20 |

| MIL-STD-1750A Defined I/O Commands                     | 21 |

| F9450 Dedicated I/O Addresses.                         | 22 |

| F9450 Instruction Execution Times in µs, 20 MHz Device | 23 |

| F9450 Instruction Execution Times in µs, 15 MHz Device | 24 |

| Interrupt Priorities                                   | 26 |

| Fault Register Bit Assignments                         | 30 |

| F9450 System Initialization                            | 33 |

| Console Command Formats                                | 35 |

| F9450 Signal Descriptions                              | 38 |

| Typical Memory Subsystem Access Time Requirements      | 45 |

| F9450 CPU Timing Characteristics                       | 48 |

|                                                        | 48 |

| DC Characteristics                                     |    |

### F9450 System Architecture

The F9450 instruction set has been designed for demanding real-time applications. Such operations as single- and double-precision integer arithmetic, including multiply and divide, floating-point arithmetic, bit operations, fault and error handling, interrupt processing, and direct memory access (DMA) are available. Memory management and protection can be accomplished using the F9451 MMU peripheral. Console commands permit direct interaction with the user.

### **Data Types**

The F9450 processes six data types:

- Bits

- Bytes (8 bits)

- Words (16 bits)

- Double words (32 bits)

- Single-precision floating-point numbers (32 bits)

- Extended-precision floating-point numbers (48 bits)

The floating-point numbers are represented by a fractional-twos-complement mantissa (24 bits for single-precision and 40 bits for extended-precision) and an 8-bit twos-complement exponent, as shown in *Figure 1*. These floating-point data formats are specified by MIL-STD-1750A.

#### Single Precision

| 0 | 23       | 24       | 31 |

|---|----------|----------|----|

| Г | MANTISSA | EXPONENT |    |

#### Double Precision

| 0 | 23       | 24     | 31 3 | 32       | 4 |

|---|----------|--------|------|----------|---|

| Γ | MANTISSA | EXPONE | NT   | MANTISSA |   |

FIGURE 1. F9450 Floating-Point Formats

### **Register Set**

The F9450 contains 24 user-accessible registers. A model of these registers is shown in *Figure 2*. There are 16 program-accessible general-purpose registers (R0 to R15), a Pending Interrupt Register (PIR), Mask Register (MK), Fault Register (FT), Instruction Counter (IC), Status Word Register (SW), System Configuration Register (SCR), and two Timers (A and B). The PIR, MK and FT are described in the "Interrupts" section. The 16-bit IC contains the address of the instruction currently being executed.

The F9450 register set also includes six temporary registers, A1, A2, DO1, DO2, O1, and Q2, that are internal to the operation of the F9450 and accessible only from the console. These, therefore, are not included in the programmer's model.

| R0  |  |

|-----|--|

| R1  |  |

| R2  |  |

| R3  |  |

| R4  |  |

| R5  |  |

| R6  |  |

| R7  |  |

| R8  |  |

| R9  |  |

| R10 |  |

| R11 |  |

| R12 |  |

| R13 |  |

| R14 |  |

| R15 |  |

|     |  |

| PENDING INTERRUPT REGI | ISTER (PIR) |

|------------------------|-------------|

| MASK REGISTER (M       | MK)         |

| FAULT REGISTER (FT) |  |

|---------------------|--|

|                     |  |

| <br>                     |

|--------------------------|

| INSTRUCTION COUNTER (IC) |

SYSTEM CONFIGURATION REGISTER (SCR)\*

| <br>        |  |

|-------------|--|

| <br>TIMER A |  |

| TIMER B     |  |

|             |  |

<sup>\*</sup>The SCR is 5 bits only, and is not available to the programmer.

FIGURE 2. F9450 Programmer's Register Model

### Status Word Register (SW)

The Status Word Register is 16 bits wide, defined as:

| _0 | )                |    |   | 3                                       | 4                                                                                                                     | 7                                        | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11                                                              | 12                                                     | 15                                                           |  |

|----|------------------|----|---|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|--|

| C  | )                | Р  | Z | Ν                                       | RESERV                                                                                                                | ED                                       | AK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (PS)                                                            | A                                                      | s                                                            |  |

|    | C<br>P<br>Z<br>N |    |   | Zer<br>Neg                              | sitive<br>o<br>gative                                                                                                 |                                          | Results of the most recent arithmetic operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                 |                                                        |                                                              |  |

|    | ser              |    |   |                                         | ese bits will                                                                                                         |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                                        |                                                              |  |

| AF | (PS              | 5) |   | two                                     | cess Key/logical functions:                                                                                           |                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                 |                                                        |                                                              |  |

|    |                  |    |   | F<br>S<br>S<br>S<br>E<br>6<br>2. U<br>S | Determine privileged in struction is An attempt struction witeror, sets and causes Define the systems with sess Lock. | exector to eth Pt bit 10 an ir           | ctions uted execu S ≠ 0 in t nstructes K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . A p with F te a p 0 cau he Fa tion a                          | riviledg PS = 0 privileg uses a ault Re ubort at is us | ed in-<br>) only.<br>ed in-<br>Major<br>gister,<br>sed in    |  |

| AS | •                |    |   | gro<br>out<br>era<br>for<br>AS<br>con   | dress State up in the M an MMU, a ted (bit 11 any operati field to a r idition is als sing (i.e., rd with AS          | MU. in Ad in th ions a nonze so tes an i | For coloress temperous values of the colorest co | onfigu<br>State<br>ult Re<br>pting<br>lue. N<br>uring<br>upt se | urations a fault is gister i to modi lote the interrup | s with-<br>s gen-<br>s set)<br>ify the<br>at this<br>of pro- |  |

All usable bits of the status word can be modified under program control or from the console (for details, refer to the F9451 MMU datasheet).

# System Configuration Register (SCR)

The SCR defines to the F9450 control circuitry the configuration of the external system connected to the CPU.

The 5-bit wide SCR is defined as:

|   | 0                                                                                                                                                                                                        | 1 | 2 | 3 | 4 | 5 | 15      |  |  |  |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---------|--|--|--|

|   | М                                                                                                                                                                                                        | В | С | Р |   |   | Not Use |  |  |  |

| М | MMU Present = 1 if an MMU is connected in the system. This must be set if the application ever requires AS $\neq$ 0.                                                                                     |   |   |   |   |   |         |  |  |  |

| В | BPU Present == 1 if a BPU is connected in the system.                                                                                                                                                    |   |   |   |   |   |         |  |  |  |

| С | Console Present = 1 if a console is connected in the system.                                                                                                                                             |   |   |   |   |   |         |  |  |  |

| P | Coprocessor = 1 if a coprocessor is connected in the system. If this bit is not set, the BIF instruction (see the "Built-In Function Implementation" section) will be considered an illegal instruction. |   |   |   |   |   |         |  |  |  |

Interrupt Mode = Selects the interrupt mode for the PWRDN INT and USR<sub>0</sub> INT-USR<sub>5</sub> INT signals: 1 is level-sensitive, 0 is edge-sensitive (low to high).

To load the SCR, external hardware is required to respond to an I/O Read request at I/O address 8410 (Hex). The internal SCR is not program-accessible, but is automatically loaded from the external hardware via the I/O Read from 8410, which is initiated by the F9450 during either the Reset initialization or the execution of the breakpoint instruction (BPT).

#### Timer A and Timer B

ı

The two 16-bit-wide timers are started, halted, loaded, and read under software control. Timer A is controlled by the timer clock (100 kHz) and Timer B is controlled by the timer clock divided by 10.

When Timer A and Timer B reach their terminal counts, they set the corresponding bits in the PIR. Both are halted when the CPU is in the console mode and continue on the resumption of program execution.

#### Instruction Set

The instruction set of the F9450 is optimized for real-time applications in accordance with the MIL-STD-1750A ISA. Table I shows addressing modes and related instruction word formats, Derived Address (DA), and Derived Operand (DO). Not all instructions use all the addressing modes; therefore, acceptable addressing modes should be confirmed for each instruction. Table II provides the instruction set with applicable addressing modes and Table III gives the dedicated I/O addresses.

### MIL-STD-1750A Description

For a complete description of the instruction set, refer to MIL-STD-1750A ISA. The military standard is available from the Department of the Navy, Naval Publications and Forms Center, 5801 Tabor Ave., Philadelphia, PA 19120, telephone (603) 121-3202.

### **Addressing Modes**

There are ten addressing modes. The smallest addressable memory word is 16 bits. Therefore, the 16-bit address field allows direct addressing of 64k words. There is no restriction on the location of double-word operands in memory.

- Register Direct (R): The instruction-specified register contains the required operand, With the exception of this mode, the Derived Address (DA) denotes a memory address.

- 2. **Memory Direct (D):** In this mode, the instruction contains the memory address of the operand.

- Memory Direct—Indexed (DX): The memory address of the required operand is specified by the sum of the contents of an index register and the instruction address field. Registers R1 through R15 may be specified for indexing.

- Memory Indirect (I): The instruction-specified memory address contains the address of the required operand.

### Addressing Modes (Continued)

- 5. Memory Indirect with Pre-Indexing (IX): The sum of the contents of a specified index register and the instruction address field specify the address of a memory location containing the address of the required operand. Registers R1 through R15 may be specified for pre-indexing.

- 6. Immediate Long (IM): One method of Immediate Long addressing allows indexing and one does not. The indexable form of immediate addressing is shown in Table III. If the specified index register, RX, is ≠ 0, the contents of RX is added to the immediate field to form the required operand; otherwise, the immediate field contains the required operand.

- 7. Immediate Short(IS): The required 4-bit operand is contained within the 16-bit instruction. One method of Immediate Short addressing interprets the contents of the immediate field as positive data and another method interprets the contents of the immediate field as negative data.

- a. Immediate Short Positive (ISP): The immediate operand is treated as a positive integer between 1 and

- b. Immediate Short Negative (ISN): The immediate operand is treated as a negative integer between 1 and 16. Its internal form is a twos-complement, signextended 16-bit number.

- Instruction Counter Relative (ICR): This mode is used for 16-bit branch instructions. The contents of the instruction counter minus one (i.e., the address of the cur-

- rent instruction) are added to the sign-extended 8-bit displacement field of the instruction. The sum points to the memory address to which control may be transferred if a branch is executed. This mode allows adversing within a memory region of -128 to +127 words, relative to the address of the current instruction.

- 9. Base Relative (B): The contents of an instruction-specified base register are added to the 8-bit displacement field of the 16-bit instruction. The displacement field is taken to be a positive number between 0 and 255. The sum points to the memory address of the required operand. This mode allows addressing within a memory region of 256 words, beginning at the address pointed to by the base register.

- 10. Base Relative-Indexed (BX): The sum of the contents of a specified index register and a specified base register is the address of the required operand. Registers R1 through R15 may be specified for indexing.

Table II shows execution time as a function of clock cycles for the instruction set of the F9450. This information is based on the microprogram of the F9450 and is subject to change for future design iterations.

Note that many instructions, including all floating-point operations, are data-dependent. This information is given as a guide to the user and includes a great number of these data dependencies. Such error conditions as overflows or underflows are not included in this table. Care should be taken to verify these times on a device with actual data for time-critical applications.

| Mode                                    | Format                               | IAOLE          | . F343U    | Auuressing I       |                       | struction Formats<br>I Operand (DO)                 | Derived           | Derived Address (DA)                              |  |  |

|-----------------------------------------|--------------------------------------|----------------|------------|--------------------|-----------------------|-----------------------------------------------------|-------------------|---------------------------------------------------|--|--|

|                                         |                                      |                |            |                    | Single-<br>Precision  | Floating-Point and Double Precision                 |                   | Floating-Point and Double Precision               |  |  |

| 1. Register Direct                      | 0 7 8                                | 11 1           |            | 5<br>              |                       |                                                     |                   |                                                   |  |  |

| "R"                                     | 0.0.                                 | RA             | RB         |                    | (RB)                  | (RB, RB + 1)                                        | RB                | RB, RB + 1                                        |  |  |

|                                         | 0 78                                 | 44.4           | 0 40       | - 10 01            | '                     | ,,,                                                 |                   | ,                                                 |  |  |

| 2. Memory Direct                        | O.C.                                 | 11 1:<br>RA    | RX         | 5 16 31<br>A       | 1                     |                                                     |                   |                                                   |  |  |

| "D"                                     | RX = 0 (Non-I                        |                | - na       |                    | [A]                   | [A, A + 1]                                          | A                 | A, A + 1                                          |  |  |

| "DX"                                    | RX ≠ 0 (Index                        |                |            |                    | [A + (RX)]            | [A + (RX),<br>A + 1 + (RX)]                         | A + (RX)          | A + (RX),<br>A + 1 + (RX)                         |  |  |

|                                         | 0 78                                 | 11 1:          | 2 15       | 5 16 31            |                       |                                                     |                   |                                                   |  |  |

| I. Memory Indirect                      | O.C.                                 | RA             | RX         | À                  |                       |                                                     |                   |                                                   |  |  |

| "I"<br>"IX"                             | RX = 0 (Non-l<br>$RX \neq 0$ (Indexe |                |            |                    | [ A ]<br>[ A + (RX) ] | [ A ,  A  + 1]<br> [ A + (RX) ,<br>  A + (RX)  + 1] | [A]<br>[A + (RX)] | [A], [A] + 1<br>[A + (RX)],<br>[A + (RX)] + 1     |  |  |

| . Immediate Long                        |                                      |                |            |                    |                       |                                                     |                   |                                                   |  |  |

| - 11-41-4                               | 0 78                                 | 11 12          |            | 16 31              |                       |                                                     |                   |                                                   |  |  |

| a. Not Indexable<br>"IM"                | O.C.                                 | RA             | OCX        | الا                |                       |                                                     |                   |                                                   |  |  |

| 1141                                    | 0 78                                 | 11 12          | 2 15       | 5 16 31            | '                     |                                                     |                   |                                                   |  |  |

| b. Indexable                            | O.C.                                 | RA             | RX         |                    |                       |                                                     |                   |                                                   |  |  |

| "IM"<br>"łMX"                           | RX = 0 (Non-In                       |                |            |                    | <br>  + (RX)          |                                                     |                   |                                                   |  |  |

| . Immediate Short                       |                                      |                |            |                    |                       |                                                     |                   |                                                   |  |  |

| <b>_</b>                                | 0 78                                 | 11 12          | 15         | ,<br>1             |                       |                                                     |                   |                                                   |  |  |

| a. Positive "ISP"                       | O.C.                                 | RA             | ı          | J                  |                       |                                                     |                   |                                                   |  |  |

| ISP                                     | 0 78                                 | 11 12          | 15         |                    | + (I + 1)             |                                                     |                   |                                                   |  |  |

| b. Negative                             | O.C.                                 | RA             | I          | ]                  |                       |                                                     |                   |                                                   |  |  |

| "ISN"                                   |                                      |                |            |                    | - (i + 1)             |                                                     |                   |                                                   |  |  |

|                                         | 0 78                                 |                | 15         | _                  |                       |                                                     |                   |                                                   |  |  |

| . IC Relative<br>(Note 1)               | O.C.                                 |                | DU         |                    |                       |                                                     |                   |                                                   |  |  |

| "ICR"                                   |                                      |                |            |                    |                       |                                                     | DU + (IC - 1)     |                                                   |  |  |

| Baran Balani                            |                                      |                |            |                    |                       |                                                     | ,                 |                                                   |  |  |

| . Base Relative<br>(Note 2)             | 0 56                                 | 7 8            | 15         |                    |                       |                                                     |                   |                                                   |  |  |

| a. Not Indexable                        | O.C.                                 | BR             | DU         |                    |                       |                                                     |                   |                                                   |  |  |

| (Note 3)<br>'B''                        | BR = BR + 12                         |                |            | ,                  | [DU + (BR)]           | (DIT + (DD)                                         | DU L (DD)         | DII ( (DD)                                        |  |  |

|                                         | DIT DIT 12                           |                |            |                    | [DO + (BN)]           | [DU + (BR),<br>DU + 1 + (BR)]                       | DU + (BR)         | DU + (BR),<br>DU + 1 + (BR)                       |  |  |

|                                         | 0 50                                 | 7.0            |            |                    |                       |                                                     |                   | DO 1 1 (BH)                                       |  |  |

| b. Indexable                            | 0 5 6<br>O.C.                        | 7 8<br>BR      | OCX 11     | 12 15<br>RX        |                       |                                                     |                   |                                                   |  |  |

| "B"                                     | RX = 0 (Non-In                       |                | JUX        | ^                  | [(BR)]                | [(BR), (RR) + 1]                                    | (BR)              | (BB) (BD) ± 1                                     |  |  |

|                                         | RX ≠ 0 (Indexe                       |                |            |                    | [(BR) + (RX)]         |                                                     | (BR) + (RX)       | (BR), (BR) + 1<br>(BR) + (RX),<br>(BR) + 1 + (RX) |  |  |

| Note 1: -128 < DU                       | ≤ 127.                               |                |            | į                  |                       |                                                     |                   |                                                   |  |  |

| Note 2: Base register                   |                                      | . R14 and R    | 15.        |                    |                       |                                                     |                   |                                                   |  |  |

| Note 3: 0 ≤ DU ≤ 2 Note 4: Extended-pre |                                      | t instructions | require or | ddressing of the   | e operando los-1-     | ed at DA, DA + 1 and D                              | <b>A</b>          |                                                   |  |  |

| Extended-pre                            | on noaming-pon                       | . man detions  | require at | acressing or tille | o operands locate     | dalua, DA + 1 and D                                 | + + 2.            |                                                   |  |  |

|                                         |                                      |                |            |                    |                       |                                                     |                   |                                                   |  |  |

### **Instruction Execution Times**

TABLE II. F9450 Instruction Execution Times

|                                        |             |        |     |    | Al - | Notes                     |

|----------------------------------------|-------------|--------|-----|----|------|---------------------------|

| Group                                  | Instruction | Mode   | Nf  | No | Nc   | Notes                     |

| TEGER ARITHMETIC/LOGIC                 |             |        |     |    |      |                           |

| Single-Precision Add                   | Α           | R      | 1   | 0  | 5    | Nf/N6                     |

| - 3                                    | Α           | В      | 1   | 1  | 12   | Nf/N6                     |

|                                        | Α           | BX     | 1   | 1  | 12   | Nf/N6                     |

|                                        | Α           | ISP    | 1   | 0  | 8    | Nf/N6                     |

|                                        | A           | D      | 2   | 1  | 13   | Nf/N6                     |

|                                        | Α           | DX     | 2   | 1  | 13   | Nf/N6                     |

|                                        | Α           | IM     | 2   | 0  | 12   | Nf/N6                     |

| Double-Precision Add                   | DA          | R      | 1   | 0  | 18   |                           |

| Double-r recision Add                  | DA          | D      | 2   | 2  | 24   |                           |

|                                        | DA          | DX     | 2   | 2  | 24   |                           |

| la a a a a a a a a a a a a a a a a a a | INCM        | D      | 2   | 2  | 17   | Nf/N6 Bus Lock            |

| Increment Memory by                    | INCM        | DX     | 2   | 2  | 17   | Nf/N6 Bus Lock            |

| Positive Integer                       | ABS         | R      | 1   | 0  | 5    | Nf/N6, Pos. #             |

| Single-Precision                       | 1           | R      | '1  | 0  | 10   | Nf/N6, Neg. #             |

| Absolute Value                         | ABS         | R      | 1   | 0  | 13   | Pos. #                    |

| Double-Precision                       | DABS        |        |     | 0  | 21   | Neg. #                    |

| Absolute Value                         | DABS        | R      | 1   | 0  | 5    | Nf/N6                     |

| Single-Precision Subtract              | S           | R      | 1   |    | 12   | Nf/N6                     |

|                                        | S           | В      | 1   | 1  |      | Nf/N6                     |

|                                        | s           | BX     | 1   | 1  | 12   |                           |

|                                        | S           | ISP    | 1   | 0  | 8    | Nf/N6                     |

|                                        | S           | D      | 2   | 1  | 13   | Nf/N6                     |

|                                        | S           | DX     | 2   | 1  | 13   | Nf/N6                     |

|                                        | S           | IM     | 2   | 0  | 12   | Nf/N6                     |

| Double-Precision Subtract              | DS          | R      | 1   | 0  | 18   |                           |

|                                        | DS          | D      | 2   | 2  | 24   |                           |

|                                        | DS          | DX     | 2   | 2  | 24   |                           |

| Decrement Memory by                    | DECM        | D      | 2   | 2  | 17   | Nf/N6 Bus Lock            |

| Positive Integer                       | DECM        | DX     | 2   | 2  | 17   | Nf/N6 Bus Lock            |

| Single-Precision Negate                | NEG         | R      | 1   | 0  | 5    | Nf/N6                     |

| Double-Precision Negate                | DNEG        | R      | 1   | 0  | 18   |                           |

| Single-Precision Multiply              | MS          | R      | 1   | 0  | 44   |                           |

| 16-Bit Product                         | MS          | ISP    | 1   | 0  | 47   |                           |

| 16-Bit Floduct                         | MS          | ISN    | 1   | 0  | 47   |                           |

|                                        | MS          | D      | 2   | 1  | 52   |                           |

|                                        | MS          | DX     | 2   | 1  | 52   | İ                         |

|                                        | MS          | IM     | 2   | Ö  | 51   |                           |

|                                        | I MIS       | 1101   | 0   | 0  | (30) | + Zero Multiplicand       |

|                                        | l           |        | 1 1 | 0  | 42   | 2010 Maniphotano          |

| Single-Precision Multiply              | M           | R<br>B | 1 1 | 1  | 42   |                           |

| 32-Bit Product                         | M           |        | 1   |    | 49   |                           |

|                                        | M           | BX     | 1   | 1  |      |                           |

|                                        | М           | D      | 2   | 1  | 50   |                           |

|                                        | M           | DX     | 2   | 1  | 50   |                           |

|                                        | M           | IM     | 2   | 0  | 49   | 7 14014 -414-19-1         |

|                                        | 1           |        | 0   | 0  | 5    | + Zero MSW of Multiplican |

|                                        |             |        | 0   | 0  | (25) | + Zero Multiplicand       |

| Double-Precision Multiply              | DM          | R      | 1   | 0  | 130  |                           |

| • •                                    | DM          | D      | 2   | 2  | 136  |                           |

|                                        | DM          | DX     | 2   | 2  | 136  | 1                         |

| Single-Precision Divide                | DV          | R      | 1   | 0  | 100  | Nf/N6                     |

| 16-Bit Dividend                        | DV          | ISP    | 1   | 0  | 100  | Nf/N6                     |

| 10-Dit Dividorio                       | DV          | ISN    | 1   | 0  | 100  | Nf/N6                     |

| Group                    | Instruction   | Mode  | Nf  | No     | Nc  | Notes                              |

|--------------------------|---------------|-------|-----|--------|-----|------------------------------------|

| NTEGER ARITHMETIC/LOGI   | C (Continued) |       |     |        | 1   |                                    |

|                          | DV            | D     | 2   | 1      | 105 | Nf/N6                              |

|                          | DV            | DX    | 2   | 1      | 105 | Nf/N6                              |

|                          | DV            | IM    | 2   | 0      | 104 | Nf/N6                              |

|                          |               |       | lo  | 0      | 5   | Add for Dividend = 8000(H)         |

|                          |               |       | 0   | 0      | 6   | Add for Negative Dividend          |

|                          |               |       | 0   | 0      | 3   | Add for Negative Divisor           |

|                          |               | -     | 0   | 0      | 3   | Add for Remainder Correction       |

| Single-Precision Divide  | D             | l R   | 1   | o      | 101 | Nf/N6                              |

| 32-Bit Dividend          | D             | В     | 1   | 1      | 105 | Nf/N6                              |

|                          | D             | вх    | 1 1 | 1      | 105 | Nf/N6                              |

|                          | D             | D     | 2   | 1      | 106 | Nf/N6                              |

|                          | D             | DX    | 2   | 1      | 106 | Nf/N6                              |

|                          | D             | IM    | 2   | 0      | 105 | Nf/N6                              |

|                          |               |       | 0   | 0      | 6   | Add for RA ≥ Divisor               |

|                          |               |       | 0   | 0      | 9   | Add for Negative Dividend          |

|                          |               |       | 0   | o      | 5   | Add for Negative Divisor           |

|                          |               | İ     | 0   | 0      | 3   | Add for Remainder Correction       |

| Double-Precision Divide  | DD            | R     | 1   | 0      | 241 |                                    |

|                          | DD            | D     | 2   | 2      | 247 |                                    |

|                          | DD            | DX    | 2   | 2      | 247 |                                    |

|                          |               |       | 0   | 0      | 6   | Add for Negative Dividend          |

|                          |               | ļ     | 0   | 0      | 6   | Add for Negative Divisor           |

|                          |               |       | 0   | 0      | 7   | Add for Negative Result            |

|                          |               |       | 0   | 0      | 5   | Add for MSW of Dividend = 8000(H)  |

|                          |               | ] .   | 0   | 0      | 5   | Add for Dividend = 8000 0000(H)    |

|                          |               |       | 0   | 0      | 5   | Add Above + LSW of Dividend = $-1$ |

| Single-Precision Compare | С             | R     | 1   | 0      | 8   | Nf/N6                              |

|                          | C             | В     | 1 1 | 1      | 15  | Nf/N6                              |

|                          | С             | BX    | 1   | 1      | 15  | Nf/N6                              |

|                          | С             | ISP   | 1   | 0      | 11  | Nf/N6                              |

|                          | С             | ISN   | 1   | 0      | 11  | Nf/N6                              |

|                          | С             | D     | 2   | 1      | 16  | Nf/N6                              |

|                          | C             | DX    | 2   | 1      | 16  | Nf/N6                              |

|                          | С             | l im  | 2   | 0      | 15  | Nf/N6                              |

| Compare Between Limits   | CBL           | l o l | 2   | 2      | 30  | Nf/N6 (RA < DO1)                   |

| ·                        |               | i - I | 2   | 2      | 43  | $Nf/N6$ (DO1 $\leq$ RA $\leq$ DO2) |

|                          |               |       | 2   | 2      | 40  | Nf/N6 (RA > DO2)                   |

|                          | CBL           | DX    | 2   | 2      | 30  | Nf/N6 (RA < DO1)                   |

|                          |               |       | 2   | 2      | 43  | Nf/N6 (DO1 ≤ RA ≤ DO2)             |

|                          |               |       | 2   | 2      | 40  | Nf/N6 (RA > DO2)                   |

| Double-Precision Compare | DC            | R     | 1   | -<br>0 | 21  | 7.11.113 (1.11.1 BOZ)              |

|                          | DC            | D     | 2   | 2      | 27  |                                    |

|                          | DC            | DX    | 2   | 2      | 27  |                                    |

| Inclusive-OR             | OR            | R     | 1   | 0      | 4   |                                    |

|                          | OR            | В     | 1   | 1      | 11  |                                    |

|                          | OR            | вх    | 1   | 1      | 11  |                                    |

|                          | OR            | D     | 2   | 1      | 12  |                                    |

|                          | OR            | DX    | 2   | 1      | 12  |                                    |

|                          | OR            | IM    | 2   | o l    | 11  |                                    |

| AND                      | AND           | R     | 1   | ő      | 4   |                                    |

|                          | AND           | В     | i   | 1      | 11  |                                    |

|                          | AND           | вх    | 1   | 1      | 11  |                                    |

| Group                | Instruction     | Mode | Nf          | No  | Nc   | Notes                         |

|----------------------|-----------------|------|-------------|-----|------|-------------------------------|

| NTEGER ARITHMETIC/LO | GIC (Continued) | - I  |             |     |      |                               |

|                      | AND             | D    | 2           | 1   | 12   |                               |

|                      | AND             | DX   | 2           | 1   | 12   |                               |

|                      | AND             | IM   | 2           | 0   | 11   |                               |

| Exclusive-OR         | XOR             | R    | 1           | 0   | 4    |                               |

| Exclusive-OH         | XOR             | D    | 2           | 1   | 12   |                               |

|                      | XOR             | DX   | 2           | 1   | 12   |                               |

|                      | I               | IM   | 2           | o   | 11   |                               |

|                      | XOR<br>NAND     | R    | 1           | ő   | 9    |                               |

| NAND                 |                 | D    | 2           | 1   | 17   |                               |

|                      | NAND            | DX   | 2           |     | 17   |                               |

|                      | NAND<br>NAND    | IM   | 2           | o   | 16   |                               |

| LOATING POINT        | 10.00           |      | <del></del> |     | L    |                               |

| Floating-Point Add   | FA              | R    | 1           | 0   | 91   | (Note 3) No Shifts in         |

| Floating-Folht Add   |                 | ''   | 1           | o   | 70   | (Note 2) Exponent Adjust      |

|                      | FA              | В    | ;           | 2   | 96   | (Note 3) And in               |

|                      | "               |      | 1           | 2   | 75   | (Note 2) Normalization        |

|                      | FA              | вх   |             | 2   | 96   | (Note 3)                      |

|                      | FA              | 5^   | '1          | 2   | 75   | (Note 2)                      |

|                      | FA              | D    | 2           | 2   | 97   | (Note 3)                      |

|                      | FA              |      | 2           | 2   | 76   | (Note 2)                      |

|                      | F.4             | DX   | 2           | 2   | 97   | (Note 3)                      |

|                      | FA              | 0^   | 2           | 2   | 76   | (Note 2)                      |

|                      | 1               |      | 0           | 0   | (15) | + RA = 0                      |

|                      | FA              | ALL  | 0           | 0   | (67) | (Note 3) + D0 = 0             |

|                      |                 |      |             | 0   | 1 1  | (Note 3) 1 D0 = 0<br>(Note 2) |

|                      |                 |      | 0           | 1   | (46) | + Addition Overflow           |

|                      |                 |      | 0           | 0   | 14   | + Scale RA                    |

|                      |                 | 1    | 0           | 0   | 8    |                               |

|                      |                 |      | 0           | 0   | 6    | Incremental                   |

|                      |                 |      | 0           | 0   | 6    | + Scale D0                    |

|                      |                 |      | 0           | 0   | 6    | Incremental                   |

|                      |                 |      | 0           | 0   | 5    | + Normalize                   |

|                      |                 |      | 0           | 0   | 13   | Incremental                   |

|                      |                 |      | 0           | 0   | 5    | Unnormalized Mantissa =       |

|                      |                 |      | 0           | 0   | 10   | Result = 0                    |

| Extended-Precision   | EFA             | R    | 1           | 0   | 106  | (Note 3)                      |

| Floating-Point Add   |                 |      | 1           | 0   | 85   | (Note 2)                      |

|                      | EFA             | D    | 2           | 3   | 113  | (Note 3)                      |

|                      |                 |      | 2           | 3   | 92   | (Note 2)                      |

|                      | EFA             | DX   | 2           | 3   | 113  | (Note 3)                      |

|                      |                 |      | 2           | 3   | 92   | (Note 2)                      |

|                      | EFA             | ALL  | 0           | 0   | (15) | + RA = 0                      |

|                      |                 |      | 0           | 0   | (76) | (Note 3) + D0 = 0             |

|                      |                 |      | 0           | 0   | (55) | (Note 2)                      |

|                      |                 |      | 0           | 0   | 17   | + Addition Overflow           |

|                      |                 |      | 0           | 0   | 8    | + Scale RA                    |

|                      |                 |      | 0           | 0   | 9    | Incremental                   |

|                      |                 |      | 0           | 0   | 6    | + Scale D0                    |

|                      |                 |      | 0           | 0   | 9    | Incremental                   |

|                      |                 |      | 0           | 0   | 8    | + Normalize                   |

|                      |                 |      | 0           | 0   | 16   | Incremental                   |

|                      | 1               |      | 0           | l 0 | 2    | MSH of Mantissa = 0           |

| Group                     | Instruction | Mode | Nf  | No  | Nc   | Notes                       |

|---------------------------|-------------|------|-----|-----|------|-----------------------------|

| LOATING POINT (Continued) |             |      | 1   |     | 1    |                             |

|                           |             |      | 0   | 0   | 7    | Unormalized Mantissa = 0    |

|                           |             |      | 0   | 0   | 20   | Result = 0                  |

| Floating-Point            | FABS        | R    | 1   | 0   | 16   | Pos. #                      |

| Absolute Value            | FABS        | R    | 1   | 0   | 71   | Neg. #                      |

| Floating-Point Subtract   | FS          | R    | 1   | 0   | 91   | (Note 3)                    |

|                           |             |      | 1   | 0   | 70   | (Note 2)                    |

|                           | FS          | В    | 1   | 2   | 96   | (Note 3)                    |

|                           |             |      | 1   | 2   | 75   | (Note 2)                    |

|                           | FS          | BX   | 1   | 2   | 96   | (Note 3)                    |

|                           |             |      | 1   | 2   | 75   | (Note 2)                    |

|                           | FS          | D    | 2   | 2   | 97   | (Note 3)                    |

|                           |             |      | 2   | 2   | 76   | (Note 2)                    |

|                           | FS          | DX   | 2   | 2   | 97   | (Note 3)                    |

|                           |             |      | 2   | 2   | 76   | (Note 2)                    |

|                           | FS          | ALL  | 0   | 0   | (15) | + RA = 0                    |

|                           |             |      | 0   | 0   | (67) | + D0 = 0 (Note 3)           |

|                           |             |      | 0   | 0   | (46) | (Note 2)                    |

|                           |             |      | 0   | 0   | 14   | + Addition Overflow (Note 3 |

|                           |             |      | О   | 0   | 17   | (Note 2)                    |

|                           |             |      | 0   | 0   | 8    | + Scale RA                  |

|                           |             |      | 0   | 0   | 6    | Incremental                 |

|                           |             |      | 0   | 0   | 6    | + Scale D0                  |

|                           |             |      | 0   | o   | 6    | Incremental                 |

|                           |             |      | 0   | 0   | 5    | + Normalize                 |

|                           |             | ļ    | 0   | 0   | 13   | Incremental                 |

|                           |             |      | 0   | o I | 5    | Unnormalized Mantissa = 0   |

|                           |             |      | 0   | 0   | 10   | Result = 0                  |

| Extended-Precision        | EFS         | R    | 1   | 0   | 106  | (Note 3)                    |

| Floating-Point Subtract   |             |      | 1   | o   | 85   | (Note 2)                    |

| -                         | EFS         | D    | 2   | 3   | 113  | (Note 3)                    |

|                           |             | i    | 2   | 3   | 92   | (Note 2)                    |

|                           | EFS         | DX   | 2   | 3   | 113  | (Note 3)                    |

|                           | i           |      | 2   | 3   | 92   | (Note 2)                    |

|                           | EFS         | ALL  | 0   | 0   | (15) | +RA=0                       |

|                           |             |      | 0   | ō   | (76) | + D0 = 0 (Note 3)           |

|                           |             |      | 0   | o   | 5    | (Note 2)                    |

|                           |             |      | 0   | o l | 17   | + Addition Overflow         |

|                           |             |      | 0   | 0   | 8    | + Scale RA                  |

| i                         |             |      | 0   | 0   | 9    | Incremental                 |

|                           |             |      | ō   | ō   | 6    | + Scale D0                  |

|                           |             |      | 0   | ō   | 9    | Incremental                 |

|                           |             | 1    | 0   | 0   | 8    | + Normalize                 |

|                           | ]           | İ    | ō   | o   | 16   | Incremental                 |

| ,                         |             | ]    | o   | ō   | 2    | MSH of Mantissa = 0         |

|                           |             | 1    | o l | ŏ   | 7    | Unnormalized Mantissa = 0   |

|                           |             |      | o l | o l | 20   | Result = 0                  |

| Floating-Point Negate     | FNEG        | R    | 1   | 0   | 61   | POS #                       |

| , ,                       |             |      | i   | 0   | 65   | NEG #                       |

| Floating-Point Multiply   | FM          | R    | i   | o l | 120  |                             |

|                           | FM          | В    | i [ | 2   | 125  |                             |

|                           | FM          | вх   | i   | 2   | 125  |                             |

|                           | FM          | D    | 2   | 2   | 126  |                             |

| Croun                                   | Instruction   | Mode | Nf | No | Nc    | Notes                             |

|-----------------------------------------|---------------|------|----|----|-------|-----------------------------------|

| Group  Group  Group                     | Illistraction | Wode |    |    |       |                                   |

| FLOATING POINT (Continued)              |               | DX   | 2  | 2  | 126   |                                   |

|                                         | FM            | l ox | 0  | 0  | 18    | + Normalize                       |

|                                         |               |      | 0  | 0  | 6     | + 8000 00XX * 8000 00XX           |

|                                         | CC14          | R    | 1  | ő  | 243   | 7 0000 00701 0000 00101           |

| Extended-Precision                      | EFM           | D    | 2  | 3  | 250   |                                   |

| Floating-Point Multiply                 | EFM           | DX   | 2  | 3  | 250   |                                   |

|                                         | EFM           | 0^   | 0  | 0  | 24    | + Normalize                       |

|                                         |               |      | 0  | ő  | 6     | + 8000 00XX 0000 * 8000 00XX 0000 |

| Election Point Divido                   | FD            | R    | 1  | o  | 222   |                                   |

| Floating-Point Divide                   | FD            | В    | 1  | 2  | 227   |                                   |

|                                         | FD            | BX   | 1  | 2  | 227   |                                   |

|                                         | FD            | D    | 2  | 2  | 228   |                                   |

|                                         | FD            | DX   | 2  | 2  | 228   |                                   |

|                                         | FD            | ALL  | 0  | 0  | 18    | + Normalize                       |

|                                         | 10            | /122 | o  | o  | 14    | + MAN(RA) > MAN(DO)               |

|                                         |               |      | o  | ō  | 9     | + MAN(RA) = MAN(DO)               |

|                                         |               |      | o  | 0  | (181) | + Divisor = 0                     |

|                                         |               |      | 0  | 0  | (195) | + Dividend = 0                    |

|                                         |               |      | 0  | o  | 6     | + Correction Required             |

| Extended-Precision                      | EFD           | R    | 1  | 0  | 462   |                                   |

| Floating-Point Divide                   | EFD           | D    | 2  | 3  | 469   |                                   |

| riodang rome situas                     | EFD           | DX   | 2  | 3  | 469   |                                   |

|                                         | _, _          |      | 0  | 0  | 24    | + Normalize                       |

|                                         |               |      | 0  | 0  | 17    | + MAN(RA) > MAN(DO)               |

|                                         |               |      | 0  | 0  | 12    | + MAN(RA) = MAN(DO)               |

|                                         |               |      | 0  | 0  | (412) | + Divisor = 0                     |

|                                         |               |      | 0  | 0  | (435) | + Dividend = 0                    |

|                                         |               |      | 0  | 0  | 3     | + Correction Required             |

| Floating-Point Compare                  | FC            | R    | 1  | 0  | 52    | Nf/N6; RA < DO; RA > DO, A1 < >0  |

| , , , , , , , , , , , , , , , , , , , , | FC            | В    | 1  | 2  | 57    | Nf/N6; RA < DO; RA > DO, A1 < >0  |

|                                         | FC            | вх   | 1  | 2  | 57    | Nf/N6; RA < DO; RA > DO, A1 < >0  |

|                                         | FC            | D    | 2  | 2  | 58    | Nf/N6; RA < DO; RA > DO, A1 < >0  |

|                                         | FC            | DX   | 2  | 2  | 58    | Nf/N6; RA < DO; RA > DO, A1 < >0  |

|                                         |               | 1    | 0  | 0  | (15)  | + RA = 0                          |

|                                         |               |      | 0  | 0  | (28)  | + DO = 0                          |

|                                         |               |      | 0  | 0  | 14    | + Addition Overflow               |

|                                         |               | i    | 0  | 0  | 8     | + Scale RA                        |

|                                         |               |      | 0  | 0  | 6     | Incremental                       |

|                                         |               |      | 0  | 0  | 3     | + Scale DO                        |

|                                         |               |      | 0  | 0  | 6     | Incremental                       |

|                                         |               |      | 0  | 0  | 10    | + RA = DO; RA > DO, A1 = 0, A2 >  |

|                                         |               | -    | 0  | 0  | 13    | + RA > DO, A1 = 0, A2 < 0         |

| Extended-Precision                      | EFC           | R    | 1  | 0  | 55    | Nf/N6; RA < DO; RA > DO, A1 < > 0 |

| Floating-Point Compare                  | EFC           | D    | 2  | 3  | 68    | Nf/N6; RA < DO; RA > DO, A1 < > 0 |

| •                                       | EFC           | DX   | 2  | 3  | 68    | Nf/N6; RA < DO; RA > DO, A1 < > 0 |

|                                         | EFC           | ALL  | 0  | 0  | (15)  | + RA = 0                          |