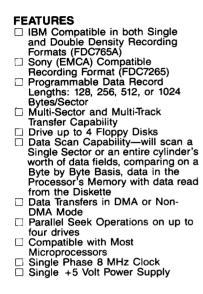

## FDC765A/765A-2 FDC 7265/7265-2

# Single/Double Density Floppy Disk Controller

### **GENERAL DESCRIPTION**

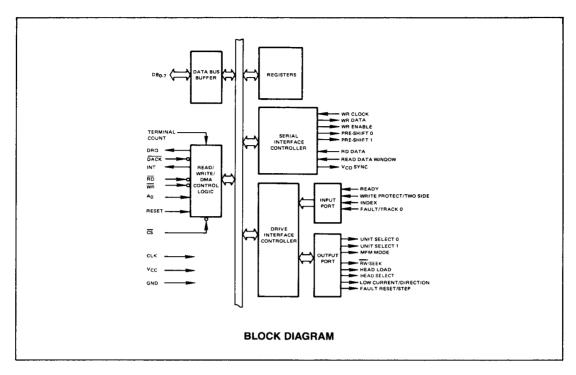

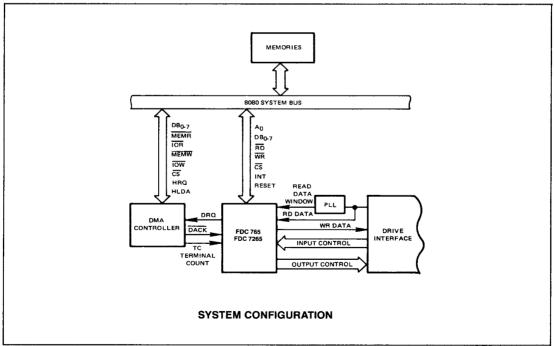

The FDC765A is an LSI floppy disk controller (FDC) chip, which contains the circuitry and control functions for interfacing a processor to 4 floppy disk drives. It is capable of either IBM 3740 single density format (FM), or IBM System 34 double density format (MFM) including double-sided recording. The FDC765A provides control signals which simplify the design of an external phase-locked loop and write precompensation circuitry. The FDC simplifies and handles most of the burdens associated with implementing a floppy disk interface.

The FDC7265 is an addition to the FDC family that has been designed specifically for the Sony Micro Floppydisk® drive. The FDC7265 is pin-compatible and electrically equivalent to the 765A but utilizes the Sony recording format. The FDC7265 can read a diskette that has been formatted by the FDC765A.

Each of these devices is also available in a -2 version. The -2 versions represent a reduction from 4-micron to 3-micron design rule. Functionally is the same. Minor differences between the two versions are detailed in the AC Characteristics table. The -2 versions are only available in the plastic package at this time.

Hand-shaking signals are provided in the FDC765A/FDC7265 which make DMA operation easy to incorporate with the aid of an external DMA controller chip. The FDC will operate in either the DMA or non-DMA mode. In the non-DMA mode the FDC generates interrupts to the processor

every time a data byte to be transferred. In the DMA mode, the processor need only load the command into the FDC and all data transfers occur under control of the FDC and DMA controllers.

There are 15 commands which the FDC765A/FDC7265 will execute. Each of these commands requires multiple 8-bit bytes to fully specify the operation which the processor wishes the FDC to perform. The following commands are available:

Read Data

Read ID

Specify

Read Track

Scan Equal

Scan High or Equal

Read Deleted Data

Write Data

Format Track

Write Deleted Data

Seek

Recalibrate

Scan Low or Equal Sense Interrupt Status Sense Drive Status

Address mark detection circuitry is internal to the FDC which simplifies the phase-locked loop and read electronics. The track stepping rate, head load time, and head unload time are user-programmable. The FDC765A/FDC7265 offers additional features such as multi-track and multi-side read and write commands and single and double density capabilities.

## **DESCRIPTION OF PIN FUNCTIONS**

| NC.          | PIN                               | NAME                        | INPUT/<br>OUTPUT   | CONNECTION      | FUNCTION                                                                                                                                                                                                                                                             |

|--------------|-----------------------------------|-----------------------------|--------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>NO.</b> 1 | RST                               | Reset                       | Input              | Processor       | Places FDC in idle state. Resets output lines to FDD to "0" (low). Does not effect SRT, HUT or HLT in Specify command. If RDY pin is held high during Reset, FDC will generate interrupt 1.024 ms later. To clear this interrupt use Sense Interrupt Status command. |

| 2            | RD                                | Read                        | Input <sup>®</sup> | Processor       | Control signal for transfer of data from FDC to Data Bus, when "0" (low).                                                                                                                                                                                            |

| 3            | WR                                | Write                       | Input <sup>®</sup> | Processor       | Control signal for transfer of data to FDC via Data Bus, when "0" (low).                                                                                                                                                                                             |

| 4            | CS                                | Chip Select                 | Input              | Processor       | IC selected when "0" (low),<br>allowing RD and WR to be<br>enabled.                                                                                                                                                                                                  |

| 5            | A <sub>o</sub>                    | Data/Status Reg<br>Select   | Input <sup>®</sup> | Processor       | Selects Data Reg ( $A_o = 1$ ) or<br>Status Reg ( $A_o = 0$ ) contents of<br>the FDC to be sent to Data Bus.                                                                                                                                                         |

| 6-13         | DB <sub>0</sub> -DB <sub>7</sub>  | Data Bus                    | Input①<br>Output   | Processor       | Bi-Directional 8-Bit Data Bus.                                                                                                                                                                                                                                       |

| 14           | DRQ                               | Data DMA<br>Request         | Output             | DMA             | DMA Request is being made by FDC when DRW = "1".                                                                                                                                                                                                                     |

| 15           | DACK                              | DMA<br>Acknowledge          | Input              | DMA             | DMA cycle is active when "0" (low) and Controller is performing DMA transfer.                                                                                                                                                                                        |

| 16           | TC                                | Terminal Count              | Input              | DMA             | Indicates the termination of a DMA transfer when "1" (high). It terminates data transfer during Read/Write/Scan command in DMA or interrupt mode.                                                                                                                    |

| 17           | IDX                               | Index                       | Input              | FDD             | Indicates the beginning of a disk track.                                                                                                                                                                                                                             |

| 18           | INT                               | Interrupt                   | Output             | Processor       | Interrupt Request Generated by FDC.                                                                                                                                                                                                                                  |

| 19           | CLK                               | Clock                       | Input              |                 | Single Phase 8 MHz Squarewave Clock.                                                                                                                                                                                                                                 |

| 20           | GND                               | Ground                      |                    |                 | D.C. Power Return.                                                                                                                                                                                                                                                   |

| 21           | WCK                               | Write Clock                 | Input              |                 | Write data rate to FDD. FM = 500 kHz, MFM = 1 MHz, with a pulse width of 250 ns for both FM and MFM.                                                                                                                                                                 |

| 22           | RDW                               | Read Data<br>Window         | Input              | Phase Lock Loop | Generated by PLL, and used to sample data from FDD.                                                                                                                                                                                                                  |

| 23           | RDD                               | Read Data                   | Input              | FDD             | Read data from FDD, containing clock and data bits.                                                                                                                                                                                                                  |

| 24           | vco                               | VCO Sync                    | Output             | Phase Lock Loop | Inhibits VCO in PLL when "0" (low), enables VCO when "1."                                                                                                                                                                                                            |

| 25           | WE                                | Write Enable                | Output             | FDD             | Enables write data into FDD.                                                                                                                                                                                                                                         |

| 26           | MFM                               | MFM Mode                    | Output             | Phase Lock Loop | MFM mode when "1," FM mode when "0."                                                                                                                                                                                                                                 |

| 27           | HD                                | Head Select                 | Output             | FDD             | Head 1 selected when "1" (high).<br>Head 2 selected when "0" (low).                                                                                                                                                                                                  |

| 28, 29       | US,, US <sub>o</sub>              | Unit Select                 | Output             | FDD             | FDD Unit Selected.                                                                                                                                                                                                                                                   |

| 30           | WDA                               | Write Data                  | Output             | FDD             | Serial clock and data bits to FDD.                                                                                                                                                                                                                                   |

| 31, 32       | PS <sub>1</sub> , PS <sub>0</sub> | Precompensation (pre-shift) | Output             | FDD             | Write precompensation status<br>during MFM mode. Determines<br>early, late, and normal times.                                                                                                                                                                        |

| 33           | FLT/TR <sub>o</sub>               | Fault/Track 0               | Input              | FDD             | Senses FDD fault condition, in Read/Write mode; and Track 0 condition in Seek mode.                                                                                                                                                                                  |

| 34           | WP/TS                             | Write Protect/<br>Two-Side  | Input              | FDD             | Senses Write Protect status in<br>Read/Write mode; and Two Side<br>Media in Seek mode.                                                                                                                                                                               |

## **DESCRIPTION OF PIN FUNCTIONS**

|     | PIN             |                           | INPUT/ | CONNECTION |                                                                                                                                                                                                                                               |

|-----|-----------------|---------------------------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | SYMBOL          | NAME                      | OUTPUT | TO         | FUNCTION                                                                                                                                                                                                                                      |

| 35  | RDY             | Ready                     | Input. | FDD        | Indicates FDD is ready to send or receive data.                                                                                                                                                                                               |

| 36  | HDL             | Head Load                 | Output | FDD        | Command which causes read/<br>write head in FDD to contact<br>diskette.                                                                                                                                                                       |

| 37  | FR/STP          | Fit Reset/Step            | Output | FDD        | Resets fault F.F. in FDD in Read/<br>Write mode, contains stop pulses<br>to move head to another cylinder in<br>Seek mode.                                                                                                                    |

| 38  | LCT/DIR         | Low Current/<br>Direction | Output | FDD        | Lowers Write current on inner tracks ≥ 42 in Read/Write mode, determines direction head will stop in Seek mode. A fault reset pulse is issued at the beginning of each Read or Write command prior to the occurrence of the Head Load signal. |

| 39  | RW/SEEK         | Read Write/SEEK           | Output | FDD        | When "1" (high) Seek mode<br>selected and when "0" (low) Read/<br>Write mode selected.                                                                                                                                                        |

| 40  | V <sub>cc</sub> | + 5V                      |        |            | DC Power.                                                                                                                                                                                                                                     |

Note: ① Disabled when CS = 1.

## **DESCRIPTION OF INTERNAL REGISTERS**

The FDC765A/7265 contains two registers which may be accessed by the main system processor; a Status Register and a Data Register. The 8-bit Main Status Register contains the status information of the FDC, and may be accessed at any time. The 8-bit Data Register (actually consists of several registers in a stack with only one register presented to the data bus at a time), which stores data, commands, parameters, and FDD status information. Data bytes are read out of, or written into, the Data Register in order to program or obtain the results after a particular command. The Status Register may only be read and used to

facilitate the transfer of data between the processor and FDC.

The relationship between the Status/Data registers and the signals  $\overline{RD}$ ,  $\overline{WR}$ , and  $A_o$  is shown below.

| Αo | RD | WR | FUNCTION                  |

|----|----|----|---------------------------|

| 0  | 0  | 1  | Read Main Status Register |

| 0  | 1  | 0  | Illegal                   |

| 0  | 0  | 0  | Illegal                   |

| 1  | 0  | 0  | Illegal                   |

| 1  | 0  | 1  | Read from Data Register   |

| 1  | 1  | 0  | Write into Data Register  |

The bits in the Main Status Register are defined as follows:

| BIT NUMBER      | NAME                              | SYMBOL | DESCRIPTION                                                                                                                                                                                                |

|-----------------|-----------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB <sub>o</sub> | FDD 0 Busy                        | D₀B    | FDD number 0 is in the Seek mode. If any of the bits is set FDC will not accept read or write command.                                                                                                     |

| DB,             | FDD 1 Busy                        | D,B    | FDD number 1 is in the Seek mode. If any of the bits is set FDC will not accept read or write command.                                                                                                     |

| DB <sub>2</sub> | FDD 2 Busy                        | D₂B    | FDD number 2 is in the Seek mode. If any of the bits is set FDC will not accept read or write command.                                                                                                     |

| DB <sub>3</sub> | FDD 3 Busy                        | D₃B    | FDD number 3 is in the Seek mode. If any of the bits is set FDC will not accept read or write command.                                                                                                     |

| DB₄             | FDC Busy                          | СВ     | A read or write command is in process. FDC will not accept any other command.                                                                                                                              |

| DB₅             | Execution Mode                    | EXM    | This bit is set only during execution phase in non-DMA mode. When DB, goes low, execution phase has ended, and result phase was started. It operates only during NON-DMA mode of operation.                |

| DB₀             | DB <sub>6</sub> Data Input/Output |        | Indicates direction of data transfer between FDC and Data Register. If DIO = "1" then transfer is from Data Register to the Processor. If DIO = "0", then transfer is from the Processor to Data Register. |

| DB,             | Request for Master                | RQM    | Indicates Data Register is ready to send or receive data to or from the Processor. Both bits DIO and RQM should be used to perform the hand-shaking functions of "ready" and "direction" to the processor. |

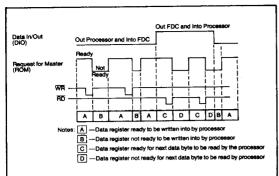

The DIO and RQM bits in the Status Register indicate when Data is ready and in which direction data will be transferred on the Data Bus. The max time between the last RD or WR during command or result phase and DIO and RQM getting set or reset is  $12 \mu s$ . For this reason every time Main Status Register is read the CPU should wait  $12 \mu s$ . The max time from the trailing edge of the last RD in the result phase to when DB, (FDC Busy) goes low is  $12 \mu s$ .

## **COMMAND SEQUENCE**

The FDC is capable of performing 15 different commands. Each command is initiated by a multi-byte transfer from the processor, and the result after execution of the command may also be a multi-byte transfer back to the processor. Because of this multi-byte interchange of information between the FDC and the processor, it is convenient to consider each command as consisting of three phases:

Command Phase:

The FDC receives all information required to perform a particular operation from the processor. The FDC performs the operation

Execution Phase:

Result Phase:

it was instructed to do.

After completion of the operation, status and other housekeeping information are made available to the processor.

#### \_\_\_\_

### COMMAND SYMBOL DESCRIPTION

| SYMBOL                         | NAME                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>o</sub>                 | Address Line 0                               | $A_o$ controls selection of Main Status Register ( $A_o = 0$ ) or Data Register ( $A_o = 1$ ).                                                                                                                                                                                                                                                                                                                        |

| С                              | Cylinder Number                              | C stands for the current/selected Cylinder (track) number 0 through 76 of the medium.                                                                                                                                                                                                                                                                                                                                 |

| D                              | Data                                         | D stands for the data pattern which is going to be written into a Sector.                                                                                                                                                                                                                                                                                                                                             |

| D <sub>7</sub> -D <sub>0</sub> | Data Bus                                     | 8-bit Data Bus, where $D_7$ stands for a most significant bit, and $D_0$ stands for a least significant bit.                                                                                                                                                                                                                                                                                                          |

| DTĻ                            | Data Length                                  | When N is defined as 00, DTL stands for the data length which users are going to read out or write into the Sector.                                                                                                                                                                                                                                                                                                   |

| EOT                            | End of Track                                 | EOT stands for the final Sector number on a Cylinder. During Read or Write operation FDC will stop data transfer after a sector # equal to EOT.                                                                                                                                                                                                                                                                       |

| GPL                            | Gap Length                                   | GPL stands for the length of Gap 3. During Read/Write commands this value determines the number of bytes that VCOs will stay low after two CRC bytes. During Format command it determines the size of Gap 3.                                                                                                                                                                                                          |

| Н                              | Head Address                                 | H stands for head number 0 or 1, as specified in ID field.                                                                                                                                                                                                                                                                                                                                                            |

| HD                             | Head                                         | HD stands for a selected head number 0 or 1 and controls the polarity of pin 27. (H = HD in all command words.)                                                                                                                                                                                                                                                                                                       |

| HLT                            | Head Load Time                               | HLT stands for the head load time in the FDD (2 to 254 ms in 2 ms increments).                                                                                                                                                                                                                                                                                                                                        |

| HUT                            | Head Unload Time                             | HUT stands for the head unload time after a read or write operation has occurred (16 to 240 ms in 16 ms increments).                                                                                                                                                                                                                                                                                                  |

| MF                             | FM or MFM Mode                               | If MF is low, FM mode is selected, and if it is high, MFM mode is selected.                                                                                                                                                                                                                                                                                                                                           |

| MT                             | Multi-Track                                  | If MT is high, a multi-track operation is to be performed. If MT = 1 after finishing Read/Write operation on side 0 FDC will automatically start searching for sector 1 on side 1.                                                                                                                                                                                                                                    |

| N                              | Number                                       | N stands for the number of data bytes written in a Sector.                                                                                                                                                                                                                                                                                                                                                            |

| NCN                            | New Cylinder Number                          | NCN stands for a new Cylinder number, which is going to be reached as a result of the Seek operation. Desired position of Head.                                                                                                                                                                                                                                                                                       |

| ND                             | Non-DMA Mode                                 | ND stands for operation in the Non-DMA Mode.                                                                                                                                                                                                                                                                                                                                                                          |

| PCN                            | Present Cylinder<br>Number                   | PCN stands for the Cylinder number at the completion of SENSE INTERRUPT STATUS Command. Position of Head at present time.                                                                                                                                                                                                                                                                                             |

| R                              | Record                                       | R stands for the Sector number, which will be read or written.                                                                                                                                                                                                                                                                                                                                                        |

| R/W                            | Read/Write                                   | R/W stands for either Read (R) or Write (W) signal.                                                                                                                                                                                                                                                                                                                                                                   |

| SC                             | Sector                                       | SC indicates the number of Sectors per Cylinder.                                                                                                                                                                                                                                                                                                                                                                      |

| SK                             | Skip                                         | SK stands for Skip Deleted Data Address Mark.                                                                                                                                                                                                                                                                                                                                                                         |

| SRT                            | Step Rate Time                               | SRT stands for the Stepping Rate for the FDD. (1 to 16 ms in 1 ms increments.) Stepping Rate applies to all drives, (F = 1 ms, E = 2 ms, etc.).                                                                                                                                                                                                                                                                       |

| ST 0<br>ST 1<br>ST 2<br>ST 3   | Status 0<br>Status 1<br>Status 2<br>Status 3 | ST 0-3 stand for one of four registers which store the status information after a command has been executed. This information is available during the result phase after command execution. These registers should not be confused with the main status register (selected by $A_{\circ}=0$ ). ST 0-3 may be read only after a command has been executed and contain information relevant to that particular command. |

| STP                            |                                              | During a Scan operation, if STP = 1, the data in continguous sectors is compared byte by byte with data sent from the processor (or DMA); and if STP = 2, then alternate sectors are read and compared.                                                                                                                                                                                                               |

| US0, US1                       | Unit Select                                  | US stands for a selected drive number 0 or 1.                                                                                                                                                                                                                                                                                                                                                                         |

## **INSTRUCTION SET 1) 2**

|                                                  | T                | i -                               | γ                                                       | T           | _        | · · · · · · · · · · · · · · · · · · ·  |                                                  |

|--------------------------------------------------|------------------|-----------------------------------|---------------------------------------------------------|-------------|----------|----------------------------------------|--------------------------------------------------|

| PHASE                                            | l <sub>R/W</sub> | DATA BUS  D7 D6 D5 D4 D3 D2 D1 D0 |                                                         | 1           | l        | DATA BUS                               | 4                                                |

| THASE                                            | 1 "/"            |                                   | REMARKS                                                 | PHASE       | R/W      | · · · · · · · · · · · · · · · · · · ·  | REMARKS                                          |

| Command                                          | T                | READ DATA                         | T                                                       | <del></del> | _        | READ A TRACK                           | ·                                                |

| Command                                          | w                | MT MF SK 0 0 1 1 0                | Command Codes                                           | Command     | w        | 0 MF SK 0 0 0 1 0                      | Command Codes                                    |

|                                                  |                  | X X X X HD U\$1 US0               |                                                         | 1           | l w      | X X X X X HD US1 US0                   |                                                  |

| 1                                                | w                | c                                 | Sector ID information prior                             |             | l w      | c                                      | Sector ID information prior                      |

|                                                  | l w              |                                   | to Command execution. The 4 bytes are commanded against |             | W        | H                                      | to Command execution                             |

| i                                                | w                |                                   | header on Floppy Disk.                                  | 1           | W        |                                        |                                                  |

|                                                  | w                | EOT                               | 1                                                       |             | w        | EOT                                    |                                                  |

| 1                                                | w                | GPL                               |                                                         | ł           | w        |                                        | 1                                                |

|                                                  | w                | DTL                               | i                                                       | 1           | w        | DTL                                    | 1                                                |

| Execution                                        | 1                |                                   | Data-transfer between the                               | Execution   | ŀ        | İ                                      | Data-transfer between the                        |

| 1                                                |                  |                                   | FDD and main-system                                     |             |          |                                        | FDD and main-system, FDC                         |

| Result                                           | R                |                                   | Status information after                                | 1           | ì        |                                        | reads all data fields                            |

|                                                  | R                | ST 1                              | Command execution                                       |             |          | 1                                      | from index hole to EOT.                          |

|                                                  | R                | ST 2                              | 1                                                       | Result      | R        | ST 0-                                  | Status information after                         |

|                                                  | R                | с                                 | Sector ID information after                             |             | R        | ST 1                                   | Command execution                                |

|                                                  | R                | H                                 | Command execution                                       | ł           | R        | St 2                                   |                                                  |

|                                                  | R                | N                                 | l                                                       | <b>!</b>    | B        | c                                      | Sector ID information after                      |

|                                                  | <del></del>      | <u> </u>                          | <u> </u>                                                | ł           | R        |                                        | Command execution                                |

| <u> </u>                                         | T                | MEAD DELETED DATA                 | <del>,</del>                                            | 4           | l e      | N                                      |                                                  |

| Command                                          | ₩                | MT MF SK 0 1 1 0 0                | Command Codes                                           |             | <u> </u> | READID                                 | <u> </u>                                         |

| 1                                                | w                | X X X X HD US1 US0                |                                                         | Command     | Τw       | ,                                      | T                                                |

|                                                  | w                | c                                 | Sector ID information prior                             | Command     | W        | 0 MF 0 0 1 0 1 0                       | Commands                                         |

| 1                                                | w                | H                                 | to Command execution, The                               | 1           | , w      | X X X X X HD US1 US0                   | i                                                |

|                                                  | w                | N                                 | 4 bytes are commanded against<br>header on Floppy Disk. | Execution   | ł        |                                        | The first correct ID information                 |

|                                                  | w                | ЕОТ                               | l land and apply Disk.                                  | 1           |          |                                        | on the Cylinder is stored in                     |

|                                                  | w                |                                   |                                                         | 1           |          |                                        | Data Register                                    |

| 1 '                                              | w                |                                   |                                                         | Result      | R        | st 0                                   | Status information after                         |

| Execution                                        |                  |                                   | Data-transfer between the                               | l .         | R        | ST 1                                   | Command execution                                |

|                                                  | i 1              |                                   | FDD and main-system                                     |             | R        | ST 2                                   |                                                  |

| Result                                           | R                |                                   |                                                         |             | R        | c                                      | Sector ID information read                       |

| result                                           | R                | ST 0                              | Status information after<br>Command execution           |             | l 🖁      | H — —                                  | during Execution Phase from<br>Floppy Disk       |

|                                                  | R                | ST 2                              | Command execution                                       | i           | B        |                                        | Ріорру Шівк                                      |

| 1                                                | R                | с                                 | Sector ID information after                             |             | •        | FORMAT A TRACK                         |                                                  |

|                                                  | R                | н                                 | Command execution                                       | Command     | w        |                                        | 0                                                |

|                                                  | R                |                                   |                                                         | Command     | l w      |                                        | Command Codes                                    |

|                                                  | :                | N                                 |                                                         | 1           |          |                                        |                                                  |

|                                                  |                  | WRITE DATA                        |                                                         |             | w        |                                        | Bytes/Sector                                     |

| Command                                          | w                | MT MF 0 0 0 1 0 1                 | - Command Codes                                         |             | w        | GPL                                    | Sectors/Track<br>Gap 3                           |

| !!!                                              | w                | X X X X X HD US1 US0              |                                                         |             | w        | D                                      | Filler Byte                                      |

| i I                                              | w                | c                                 | Sector ID information prior                             | Execution   | i l      |                                        |                                                  |

|                                                  | w                |                                   | to Command execution, The                               | Execution   |          |                                        | FDC formats an entire track                      |

|                                                  | w                | K                                 | 4 bytes are commanded against                           | Result      | R        | st 0                                   | Status information after                         |

| i 1                                              | w                | EOT                               | header on Floppy Disk,                                  |             | R        | ST 1                                   | Command execution                                |

| i 1                                              | w                |                                   | Ī                                                       |             | R        | ST 2                                   | In this case, the ID information                 |

|                                                  | w                |                                   |                                                         |             | R        | H                                      | has no meaning                                   |

| Executión                                        |                  |                                   | Data-transfer between the                               |             | R        | R                                      | The tree tree tree tree tree tree tree tr        |

|                                                  |                  |                                   | main-system and FDD                                     |             | R        | N                                      |                                                  |

| Result                                           | R                | ST 0                              |                                                         |             |          | SCAN EQUAL                             |                                                  |

| - esuit                                          | R                | ST 0                              | Status information after<br>Command execution           | Command     | W        | MT MF SK 1 0 0 0 1                     | Command Codes                                    |

|                                                  | R                | ST 2                              |                                                         | İ           | w        | X X X X X HD US1 US0                   |                                                  |

|                                                  | R                | c                                 | Sector ID information after                             |             | w        | с                                      | Sector ID information prior                      |

|                                                  | R                |                                   | Command execution                                       |             | w        | — н                                    | to Command execution                             |

|                                                  | R                |                                   |                                                         |             | w        | R                                      | ſ                                                |

| <del>                                     </del> | ···              | WRITE DELETED DATA                |                                                         |             | w        | N                                      | ŀ                                                |

| Commercial                                       | 147              |                                   |                                                         |             | w        | —————————————————————————————————————— | l                                                |

| Command                                          | w                | MT MF 0 0 1 0 0 1                 | Command Codes                                           | !           | w        | STP                                    |                                                  |

|                                                  | w                | X X X X HD US1 US0                |                                                         | Euga:       |          |                                        |                                                  |

|                                                  | w                |                                   | Sector ID information prior                             | Execution   | l l      |                                        | Data-compared between the<br>FDD and main-system |

|                                                  | w                |                                   | to Command execution. The                               |             |          |                                        | . OO and manipystem                              |

|                                                  | ₩                |                                   | 4 bytes are commanded against<br>header on Floppy Disk. | Result      | P        | ST 0                                   | Status information after                         |

|                                                  | w                | EOT                               | повоен он гворру DISK.                                  | i           | R        | ST 1                                   | Command execution                                |

|                                                  | w                | GPL                               | i                                                       |             | R        |                                        | Sector ID information after                      |

|                                                  | w                | DTL                               |                                                         | j           | A        | H                                      | Command execution                                |

| Execution                                        | - 1              |                                   | Data-transfer between the                               |             | R        |                                        |                                                  |

|                                                  | ļ                |                                   | FDD and main-system                                     | ļ           | R        | N                                      |                                                  |

| L . I                                            | _                |                                   | i i                                                     | i           | 1        |                                        | j                                                |

| Result                                           | R                | ST 0                              | Status information after                                |             |          |                                        | J                                                |

|                                                  | R                | ST 2                              | Command execution                                       | l           |          |                                        | i                                                |

|                                                  | R                | c                                 | Sector ID information after                             |             | 1        |                                        | İ                                                |

|                                                  | R                | —— H ———                          | Command execution                                       |             |          |                                        | 1                                                |

|                                                  | R                | R                                 | I                                                       | 1           |          |                                        |                                                  |

|                                                  | R                | N                                 | i                                                       | - 1         | - 1      |                                        | 1                                                |

|                                                  |                  |                                   |                                                         |             |          | <del></del>                            |                                                  |

Note: ① Symbols used in this table are described at the end of this section.

Ag should equal binary 1 for all operations.

<sup>3</sup> X = Don't care, usually made to equal binary 0.

## **INSTRUCTION SET (CONT.)**

|           |                   |          |    |             | DA | TA 8  | ı ıs           |                |             |                                                  |            |     | Γ        |    |     | DAT    | A B   | US             |                |          |                                                |

|-----------|-------------------|----------|----|-------------|----|-------|----------------|----------------|-------------|--------------------------------------------------|------------|-----|----------|----|-----|--------|-------|----------------|----------------|----------|------------------------------------------------|

| PHASE     | R/W               | 07       | De | Dε          | _  | _     | D <sub>2</sub> | D <sub>1</sub> | ъ           | REMARKS                                          | PHASE      | R/W | 07       | De | DS  | D4     | D3    | D <sub>2</sub> | D <sub>1</sub> | DQ       | REMARKS                                        |

|           | SCAN LOW OR EQUAL |          |    | RECALIBRATE |    |       |                |                |             |                                                  |            |     |          |    |     |        |       |                |                |          |                                                |

| Command   | w                 | мт       | MF | SK          | 1  | 1     | 0              | 0              | 1           | Command Codes                                    | 'Command   | w   | 0        | 0  | 0   | 0      | 0     | 1              |                | 1        | Command Codes                                  |

|           | w                 | ×        | ×  | ×           | x  | ×     | HĐ             | US1            | US0         |                                                  |            | w   | ×        | ×  | ×   | X      | х     | е              | ŲS1            | US0      | Į                                              |

|           | w                 | l        |    |             |    |       |                |                |             | Sector ID information prior                      | Execution  |     |          |    |     |        |       |                |                |          | Head retracted to Track 0                      |

|           | w                 | =        |    |             |    |       |                |                |             | Command execution                                |            |     |          |    | SEN | ISE I  | NTE   | RRUF           | T ST           | ATUS     |                                                |

|           | w                 | l —      |    |             |    |       |                |                |             |                                                  | Command    | w   | 0        | 0  | 0   | 0      | 1     | 0              | 0              | 0        | Command Codes                                  |

|           | w                 |          |    | _           |    | EOT-  |                |                | _           |                                                  | Result     | R   | l        |    |     | s      | то-   |                |                |          | Status information at the end                  |

|           | w                 | =        |    |             |    |       |                |                |             |                                                  | , New York | R   | <u> </u> |    |     |        |       |                |                |          | of seek-operation about the FDC                |

| Execution |                   |          |    |             |    |       |                |                |             | Date-compared between the                        |            |     |          |    |     |        | SP    | ECIFY          | _              |          |                                                |

| Execution |                   |          |    |             |    |       |                |                |             |                                                  | Command    | w   | 0        | 0  | 0   | 0      | 0     | 0              | 1              | 1        | Command Codes                                  |

| Result    | R                 | l        |    |             |    | ST O- |                |                |             | Status information after                         |            | W   |          |    |     |        |       |                | - HU           |          |                                                |

| 1100011   | R                 | _        |    |             |    | ST 1- |                |                |             | Commend execution                                | $\vdash$   | w   |          |    | _   |        |       | _              | TATL           |          | <u> </u>                                       |

|           | R                 | =        | _  |             |    | ST 2  |                |                |             | Sector ID information after                      | Command    | w   | 0        | _  | 0   |        |       | 1              | IAIL           | <u> </u> | Command Codes                                  |

| 1         | R                 | l —      |    |             |    | -H    |                |                |             | Command execution                                | Command    | w   | 1        | -  | -   | -      | -     |                |                | USO      | Command Codes                                  |

|           | R                 | l —      |    |             |    | R —   | _              |                | _           |                                                  |            | **  | 1 ^      |    |     |        |       |                |                | 030      |                                                |

|           | н                 |          |    |             |    |       | _              | EQU            | <del></del> | L                                                | Result     | R   | L=       | _  |     | s      |       |                |                |          | Status information about FDD                   |

| Command   | w                 | 1 447    | ME | _           |    |       | 1              |                | 1           | Command Codes                                    | Ь          |     |          |    |     |        |       | EEK            |                |          |                                                |

| Command   | w                 |          |    |             |    |       |                |                | USO         | Command Codes                                    | Command    | w   | 0        | -  | 0   | -      |       |                | 1              | 1        | Command Codes                                  |

|           | w                 | <u> </u> |    |             |    |       |                |                |             | Sector ID information prior                      |            | w   | ×        | x  | ×   |        |       |                | USI            | USO      |                                                |

|           | w                 | l —      |    |             |    |       |                |                |             | Command execution                                | Execution  | w   | _        |    |     | —r     | NCIN- |                |                |          |                                                |

|           | w                 | =        |    |             |    |       |                |                |             |                                                  | EXECUSION  |     |          |    |     |        |       |                |                |          | Head is positioned over<br>proper Cylinder on  |

|           | w                 | ۱ –      |    |             |    | EOT.  |                |                |             |                                                  |            |     |          |    |     |        |       |                |                |          | Diskerte                                       |

|           | w                 | =        |    |             |    |       |                |                |             |                                                  |            |     |          |    |     |        |       |                |                |          | <u> </u>                                       |

|           | - "               |          |    |             |    | 311   |                |                |             |                                                  |            |     |          |    |     |        | IN    | VALI           | D .            |          |                                                |

| Execution |                   |          |    |             |    |       |                |                |             | Data-compared between the<br>FDD and main-system | Command    | W   | _        |    |     | nvelic | d Cod | ies —          |                |          | Invalid Command Codes<br>(NoOp - FDC goes into |

| Result    | R                 | l —      |    |             |    |       |                |                |             | Status information after                         |            |     |          |    |     |        |       |                |                |          | Standby State)                                 |

|           | R                 | =        |    |             |    |       | _              |                | _           | Command execution                                | Result     | Я   | —        |    |     | —-s    | т 0-  |                |                |          | ST 0 = 80<br>(16)                              |

|           | Ř                 | =        |    |             |    | - c-  |                |                |             | Sector 1D information after                      |            |     |          |    |     |        |       |                |                |          | 1                                              |

|           | R                 | -        |    |             | _  | н-    |                |                |             | Command execution                                | 1          |     | ļ        |    |     |        |       |                |                |          |                                                |

|           | R                 | _        |    |             |    |       |                |                |             |                                                  |            |     | l        |    |     |        |       |                |                |          |                                                |

# FUNCTIONAL DESCRIPTION OF COMMANDS Read Data

A set of nine (9) byte words are required to place the FDC into the Read Data Mode. After the Read Data command has been issued the FDC loads the head (if it is in the unloaded state), waits the specified head settling time (defined in the Specify Command), and begins reading ID Address Marks and ID fields. When the current sector number ("R") stored in the ID Register (IDR) compares with the sector number read off the diskette, then the FDC outputs data (from the data field) byte-to-byte to the main system via the data bus.

After completion of the read operation from the current sector, the Sector Number is incremented by one, and the data

from the next sector is read and output on the data bus. This continuous read function is called a "Multi-Sector Read Operation." The Read Data Command may be terminated by the receipt of a Terminal Count signal. TC should be issued at the same time that the DACK for the last byte of data is sent. Upon receipt of this signal, the FDC stops outputting data to the processor, but will continue to read data from the current sector, check CRC (Cyclic Redundancy Count) bytes, and then at the end of the sector terminate the Read Data Command.

The amount of data which can be handled with a single command to the FDC depends upon MT (multi-track), MF (MFM/FM), and N (Number of Bytes/Sector). Table 1 below shows the Transfer Capacity.

| Multi-Track<br>MT | MFM/FM<br>MF | Bytes/Sector<br>N | Maximum Transfer Capacity<br>(Bytes/Sector) (Number of<br>Sectors) | Final Sector<br>Read<br>from Diskette |

|-------------------|--------------|-------------------|--------------------------------------------------------------------|---------------------------------------|

| 0                 | 0            | 00<br>01          | (128) (26) = 3,328<br>(256) (26) = 6,656                           | 26 at Side 0<br>or 26 at Side 1       |

| 1                 | 0            | 00<br>01          | (128) (52) = 6,656<br>(256) (52) = 13,312                          | 26 at Side 1                          |

| 0                 | 0            | 01<br>02          | (256) (15) = 3,840<br>(512) (15) = 7,680                           | 15 at Side 0<br>or 15 at Side 1       |

| 1                 | 0            | 01<br>02          | (256) (30) = 7,680<br>(512) (30) = 15,360                          | 15 at Side 1                          |

| 0                 | 0            | 02<br>03          | (512) (8) = 4,096<br>(1024) (8) = 8,192                            | 8 at Side 0<br>or 8 at Side 1         |

| 1                 | 0            | 02<br>03          | (512) (16) = 8,192<br>(1024) (16) = 16,384                         | 8 at Side 1                           |

**Table 1. Transfer Capacity**

The "multi-track" function (MT) allows the FDC to read data from both sides of the diskette. For a particular cylinder, data will be transferred starting at Sector 1, Side 0 and completing at Sector L, Side 1 (Sector L = last sector on the side). Note, this function pertains to only one cylinder (the same track) on each side of the diskette.

When N = 0, the DTL defines the data length which the FDC must treat as a sector. If DTL is smaller than the actual data length in a Sector, the data beyond DTL in the Sector, is not sent to the Data Bus. The FDC reads (internally) the complete Sector performing the CRC check, and depending upon the manner of command termination, may perform a Multi-Sector Read Operation. When N is non-zero, then DTL has no meaning and should be set to FF Hexidecimal.

At the completion of the Read Data command, the head is not unloaded until after Head Unload Time Interval (specified in the Specify Command) has elapsed. If the processor issues another command before the head unloads then the head settling time may be saved between subsequent reads. This time out is particularly valuable when a diskette is copied from one drive to another.

If the FDC detects the Index Hole twice without finding the right sector, (indicated in "R"), then the FDC sets the ND (No Data) flag in Status Register 1 to a 1 (high), and terminates the Read Data Command. (Status Register 0 also has bits 7 and 6 set to 0 and 1 respectively.)

After reading the ID and Data Fields in each sector, the FDC checks the CRC bytes. If a read error is detected (incorrect CRC in ID field), the FDC sets the DE (Data Error) flag in Status Register 1 to a 1 (high), and if a CRC error occurs in the Data Field the FDC also sets the DD (Data Error in Data Field) flag in Status Register 2 to a 1 (high), and terminates the Read Data Command. (Status Register 0 also has bits 7 and 6 set to 0 and 1 respectively.)

If the FDC reads a Deleted Data Address Mark off the diskette, and the SK bit (bit D5 in the first Command Word) is not set (SK = 0), then the FDC sets the CM (Control Mark) flag in Status Register 2 to a 1 (high), and terminates the Read Data Command, after reading all the data in the Sector. If SK = 1, the FDC skips the sector with the Deleted Data Address Mark and reads the next sector. The CRC bits in the deleted data field are not checked when SK = 1.

During disk data transfers between the FDC and the processor, via the data bus, the FDC must be serviced by the processor every 27  $\mu$ s in the FM Mode, and every 13  $\mu$ s in the MFM Mode, or the FDC sets the OR (Over Run) flag in Status Register 1 to a 1 (high), and terminates the Read Data Command.

If the processor terminates a read (or write) operation in the FDC, then the ID Information in the Result Phase is dependent upon the state of the MT bit and EOT byte. Table 2 shows the value for C, H, R, and N, when the processor terminates the Command.

|    |    | Final Sector<br>Transferred to | ID Information at Result<br>Phase |     |        |    |  |  |  |

|----|----|--------------------------------|-----------------------------------|-----|--------|----|--|--|--|

| MT | HD | Processor                      | С                                 | Н   | R      | N  |  |  |  |

|    | 0  | Less than EOT                  | NC                                | NC  | R + 1  | NC |  |  |  |

|    | 0  | Equal to EOT                   | C + 1                             | NC  | R = 01 | NC |  |  |  |

| 0  | 1  | Less than EOT                  | NC                                | NC  | R + 1  | NC |  |  |  |

|    | 1  | Equal to EOT                   | C + 1                             | NC  | R = 01 | NC |  |  |  |

|    | 0  | Less than EOT                  | NC                                | NC  | R + 1  | NC |  |  |  |

|    | 0  | Equal to EOT                   | NC                                | LSB | R = 01 | NC |  |  |  |

| 0  | 1  | Less than EOT                  | NC                                | NC  | R + 1  | NC |  |  |  |

|    | 1  | Equal to EOT                   | C + 1                             | LSB | R = 01 | NC |  |  |  |

Notes: 1. NC (No Change): The same value as the one at the beginning of command execution.

2. LSB (Least Significant Bit): The least significant bit of

H is complemented.

#### **Write Data**

A set of nine (9) bytes are required to set the FDC into the Write Data mode. After the Write Data command has been issued the FDC loads the head (if it is in the unloaded state), waits the specified Head Settling Time (defined in the Specify Command), and begins reading ID Fields. When all four bytes loaded during the command (C, H, R, N) match the four bytes of the ID field from the diskette, the FDC takes data from the processor byte-by-byte via the data bus, and outputs it to the FDD.

After writing data into the current sector, the Sector Number stored in "R" is incremented by one, and the next data field is written into. The FDC continues this "Multi-Sector Write Operation" until the issuance of a Terminal Count signal. If a Terminal Count signal is sent to the FDC it continues writing into the current sector to complete the data field. If the Terminal Count signal is received while a data field is being written then the remainder of the data field is filled with 00

The FDC reads the ID field of each sector and checks the CRC bytes. If the FDC detects a read error (incorrect CRC) in one of the ID Fields, it sets the DE (Data Error) flag of Status Register 1 to a 1 (high), and terminates the Write Data Command. (Status Register 0 also has bits 7 and 6 set to 0 and 1 respectively.)

The Write Command operates in much the same manner as the Read Command. The following items are the same, and one should refer to the Read Data Command for details:

- Transfer Capacity

- EN (End of Cylinder) Flag

- ND (No Data) Flag

- Head Unload Time Interval

- ID Information when the processor terminates command (see Table 2)

- Definition of DTL when N = 0 and when  $N \neq 0$

In the Write Data mode, data transfers between the processor and FDC, via the Data Bus, must occur every 27  $\mu s$  in the FM mode, and every 13 us in the MFM mode. If the time interval between data transfers is longer than this then the FDC sets the OR (Over Run) flag in Status Register 1 to a 1 (high), and terminates the Write Data Command. (Status Register 0 also has bit 7 and 6 set to 0 and 1 respectively.)

#### Write Deleted Data

This command is the same as the Write Data Command except a Deleted Data Address Mark is written at the beginning of the Data Field instead of the normal Data Address Mark.

#### Read Deleted Data

This command is the same as the Read Data Command except that when the FDC detects a Data Address Mark at the beginning of a Data Field and SK = 0 (low), it will read all the data in the sector and set the CM flag in Status Register 2 to a 1 (high), and then terminate the command. If SK = 1, then the FDC skips the sector with the Data Address Mark and reads the next sector.

## Read A Track

This command is similar to READ DATA Command except that this is a continuous READ operation where the entire

| Format    | Sector Size      | N      |       | GPL <sub>①</sub> | GPL@3 |

|-----------|------------------|--------|-------|------------------|-------|

|           | 8" Standar       | d Flo  | рру   |                  |       |

|           | 128 bytes/sector | 00     | 1A    | 07_              | 1B    |

| ·         | 256              | 01     | 0F    | 0E               | 2A    |

| FN4 N4ada | 512              | 02     | 08    | 1B               | 3A    |

| FM Mode   | 1024             | 03     | 04    | 47               | 8A    |

| ·         | 2048             | 04     | 02    | C8               | FF    |

|           | 4096             | 05     | 01    | C8               | FF    |

|           | 256              | 01     | 1A    | OΕ               | 36    |

|           | 512              | 02     | 0F    | 1B               | 54    |

| МЕМ       | 1024             | 03     | 08    | 35               | 74    |

| Mode 4    | 2048             | 04     | 04    | 99               | FF    |

|           | 4096             | 05     | 02    | C8               | FF    |