# **FDC 9229T FDC 9229BT**

### FLOPPY DISK INTERFACE CIRCUIT

#### **FEATURES**

- ☐ Digital Data Separator

Performs complete data separation

function for floppy disk drives

Separates FM and MFM encoded data

No critical adjustments necessary

51/4" and 8" compatible

- ☐ Variable Write Precompensation

- ☐ Internal Crystal Oscillator Circuit

☐ Track-Selectable Write Precompensation

- Retriggerable Head-Load Timer

- ☐ Compatible with the FDC 179X, 765, and other standard Floppy Disk Controllers

- ☐ COPLAMOS® n-channel MOS Technology

- ☐ Single + 5 Volt Supply

- ☐ TTL Compatible

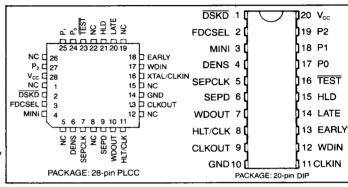

#### **PIN CONFIGURATION**

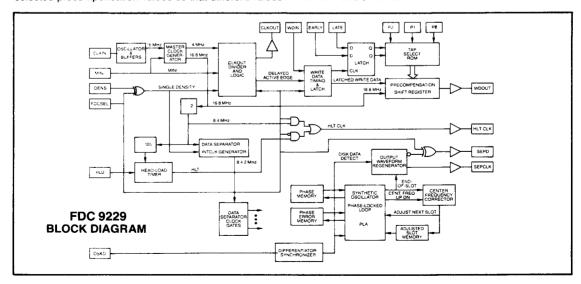

#### **FUNCTIONAL DESCRIPTION**

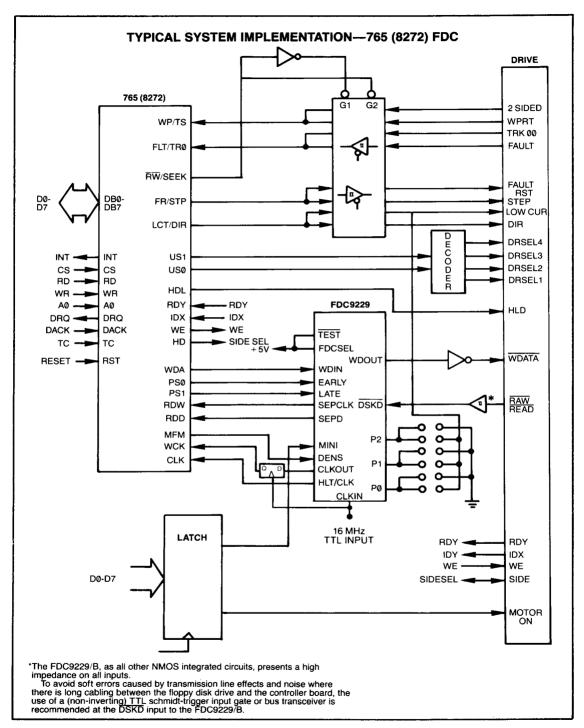

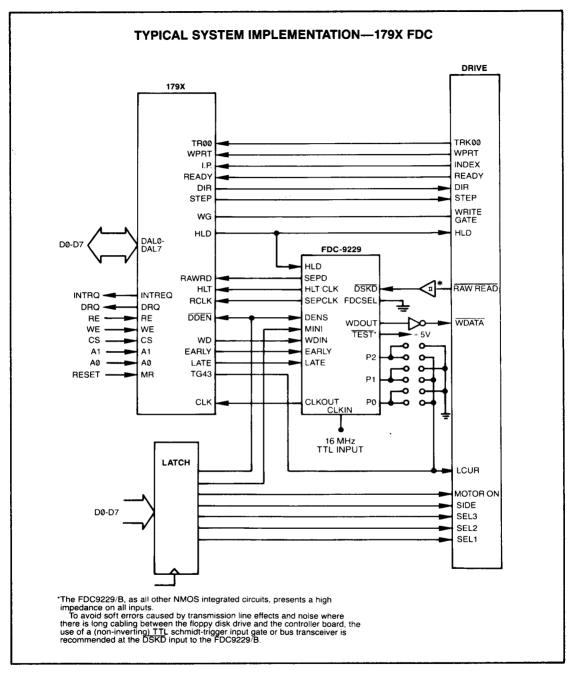

The FDC 9229 is an MOS integrated circuit designed to complement either the 179X or 765 (8272) type of floppy disk controller chip. It incorporates a digital data separator, write precompensation logic, and a head-load timer in one 0.3-inch wide 20-pin package. A single pin will configure the chip to work with either the 179X or 765 type of controller. The FDC 9229 provides a number of different dynamically selected precompensation values so that different values

may be used when writing to the inner and outer tracks of the floppy disk drive. The FDC 9229 operates from a + 5V supply and simply requires that a TTL-level clock be connected to the CLKIN pin. All inputs and outputs are TTL compatible.

The FDC 9229 is available in two versions: The FDC 9229/T are intended for 51/4" drives and the FDC 9229B/T for 51/4" and 8" drives

#### **DESCRIPTION OF PIN FUNCTIONS**

| PIN NO. | SYMBOL          | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DSKD            | 1   | This input is the raw read data received from the drive. (This input is active low.)                                                                                                                                                                                                                                                                                                                                            |

| 2       | FDCSEL          | 1   | This input signal, when low, programs the FDC 9229 for a 179X type of LSI controller. When FDCSEL is high, the FDC 9229 is programmed for a 765 (8272) type of controller. (See fig. 4.)                                                                                                                                                                                                                                        |

| 3       | MINI            | 1   | The state of this input determines whether the FDC 9229 is configured to support 8" or 51/4" floppy disk drive interfaces. It is used in conjunction with the DENS input to prescale the clock for the data separator. The state of this input also alters the CLKOUT frequency, the precompensation value, the head load delay time (when in 179X mode) and the HLT/CLK frequency (when in 765 mode). (See figs. 2, 3, and 4.) |

| 4       | DENS            | ı   | The state of this input determines whether the FDC 9229 is configured to support single density (FM) or double density (MFM) floppy disk drive interfaces. It is used in conjunction with the MINI input to prescale the clock for the data separator. The state of this input also alters the CLKOUT frequency when in the 765 mode. (See figs. 2, 3, and 4.)                                                                  |

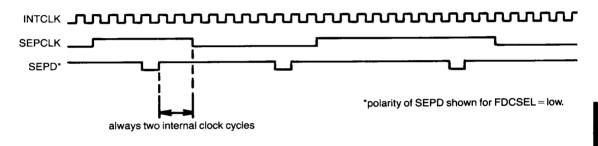

| 5       | SEPCLK          | 0   | A square-wave window clock signal output derived from the DSKD input.                                                                                                                                                                                                                                                                                                                                                           |

| 6       | SEPD            | 0   | This output is the regenerated data pulse derived from the raw data input (DSKD). This signal may be either active low or active high as determined by FDCSEL (pin 2).                                                                                                                                                                                                                                                          |

| 7       | WDOUT           | 0   | The precompensated WRITE DATA stream to the drive.                                                                                                                                                                                                                                                                                                                                                                              |

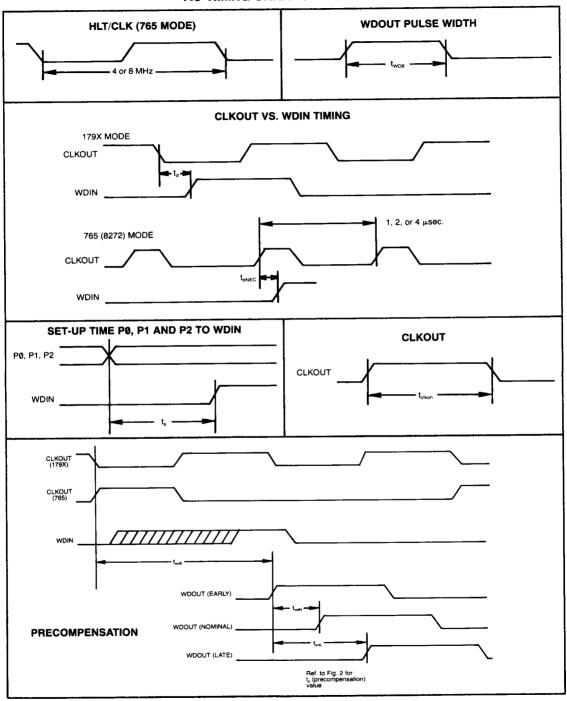

| 8       | HLT/CLK         | 0   | When in the 765 mode (FDCSEL high), this output is the master clock to the floppy disk controller. When in the 179X mode, this signal goes high after the head load delay has occurred following the HLD input going high. This output is retriggerable. (See fig. 3.)                                                                                                                                                          |

| 9       | CLKOUT          | 0   | This signal is the write clock to the floppy disk controller. Its frequency is determined by the state of the MINI, DENS, and FDCSEL input pins. (See fig. 3.)                                                                                                                                                                                                                                                                  |

| 10      | GND             |     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11      | CLKIN           | 1   | This input is for direct connection to a 16 MHz or 8 MHz single-phase TTL-level clock.                                                                                                                                                                                                                                                                                                                                          |

| 12      | WDIN            | I   | The write data stream from the floppy disk controller.                                                                                                                                                                                                                                                                                                                                                                          |

| 13      | EARLY           | 1   | When this input is high, the current WRITE DATA pulse will be written early to the disk.                                                                                                                                                                                                                                                                                                                                        |

| 14      | LATE            | 1   | When this input is high, the current WRITE DATA pulse will be written late to the disk.  When both EARLY and LATE are low, the current WRITE DATA pulse will be written at the nominal position.                                                                                                                                                                                                                                |

| 15      | HLD             | I   | This input is only used in 179X mode. A high level at this input causes a high level on the HLT/CLK output after the specified head-load time delay has elapsed. The delay is selected by the state of the MINI output. (See fig. 3.) In 765 mode, this pin should be left floating or grounded.                                                                                                                                |

| 16      | TEST            | ı   | This input (when low) decreases the head-load time delay and initializes the data separator. This pin is for test purposes only. This input has an internal pull-up resistor and should be tied high or disconnected for normal operation.                                                                                                                                                                                      |

| 17      | P0              | ı   | DO DO selectible amount of processes and indicate the proite data                                                                                                                                                                                                                                                                                                                                                               |

| 18      | P1              |     | P2-P0 select the amount of precompensation applied to the write data.  (See fig. 2.)                                                                                                                                                                                                                                                                                                                                            |

| 19      | P2              | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 20      | V <sub>cc</sub> |     | +5 VOLT SUPPLY                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### **OPERATION**

**Data Separator**

The CLKIN input clock is internally divided by the FDC 9229 to provide an internal clock. The division ratio is selected by the FDCSEL, MINI and DENS inputs depending on the type of drive used. (See fig. 1.)

The FDC 9229 detects the leading (negative) edges of the disk data pulses and adjusts the phase of the internal clock to provide the SEPCLK output.

Separate short- and long-term timing correctors assure accurate clock separation.

The SEPCLK frequency is nominally ½6 the internal clock frequency. Depending on the internal timing correction, the duration of any SEPCLK half-cycle may vary from a nominal of 8 to a minimum of 6 and a maximum of 11 internal clock cycles.

|                  | NPUTS |         | DI (100D                      |

|------------------|-------|---------|-------------------------------|

| FDCSEL DENS MINI |       |         | DIVISOR<br>f(CLKIN)/f(INTCLK) |

| FDUSEL           | DENS  | MILLIAI | (CERTIA)/I(IIATOERS)          |

| 0                | 0     | 0       | 2                             |

| 0                | 0     | 1       | 4                             |

| 0                | 1     | 0       | 4                             |

| 0                | 1     | 1       | 8                             |

| 1                | 0     | 0       | 4                             |

| 1                | 0     | 1       | 8                             |

| 1                | 1     | 0       | 2                             |

| 1                | 1     | 1       | 4                             |

FIG. 1

Precompensation

The desired precompensation delay is determined by the state of the P0, P1 and P2 inputs of the FDC 9229 as per fig. 2. Logic levels present on these pins may be changed dynamically as long as the inputs are stable during the time the floppy disk controller is writing to the drive and the inputs meet the minimum setup time with respect to the write data from the floppy disk controller.

| MINI | P2 | P1 | P0 | PRECOMP VALUE |

|------|----|----|----|---------------|

| 0    | 0  | 0  | 0  | 0 ns          |

| 0    | 0  | 0  | 1  | 62.5 ns       |

| 0    | 0  | 1  | 0  | 125 ns        |

| 0    | 0  | 1  | 1  | 187.5 ns      |

| 0    | 1  | 0  | 0  | 250 ns        |

| 0    | 1  | 0  | 1  | 250 ns        |

| 0    | 1  | 1  | 0  | 312.5 ns      |

| 0    | 1  | 1  | 1  | 312.5 ns      |

| MINI | P2 | P1 | P0 | PRECOMP VALUE |

|------|----|----|----|---------------|

| 1    | 0  | 0  | 0  | 0 ns          |

| 1    | 0  | 0  | 1  | 125 ns        |

| 1    | Ô  | 1  | 0  | 250 ns        |

| 1    | Ō  | 1  | 1  | 375 ns        |

| 1    | 1  | 0  | 0  | 500 ns        |

| 1    | 1  | Ō  | 1  | 500 ns        |

| 1    | 1  | 1  | Ó  | 625 ns        |

| 1    | 1  | 1  | 1  | 625 ns        |

|      |    |    |    |               |

NOTE: All values shown are obtained with a 16 MHz reference clock. Multiply pre-comp values by two for 8 MHz operation.

FIG. 2 WRITE PRECOMPENSATION VALUE SELECTION

#### **OPERATION (CONT'D)**

#### **Head Load Timer**

The head load time delay is either 40 ms or 80 ms, depending on the state of MINI. (See fig. 3.) The purpose of this delay is to ensure that the head has enough time to engage properly. The head load timer is only used in the 179X mode; it is non-functional in the 765 mode.

The FDC 179X initiates the loading of the floppy disk drive head by setting HLD high. The controller then waits the programmed amount of time until the HLT signal from the FDC 9229 goes high before starting a read or write operation.

|        | INPUTS | OUTPUTS |         |         |  |

|--------|--------|---------|---------|---------|--|

| FDCSEL | DENS   | MINI    | CLKOUT  | HLT/CLK |  |

| 0      | 0      | 0       | 2 MHz   | 40 ms*  |  |

| 0      | 0      | 1       | 1 MHz   | 80 ms*  |  |

| 0      | 1      | 0       | 2 MHz   | 40 ms*  |  |

| 0      | 1      | 1       | 1 MHz   | 80 ms*  |  |

|        |        |         |         |         |  |

| 1      | 0      | 0       | 500 KHz | 8 MHz   |  |

| 1      | 0      | 1       | 250 KHz | 4 MHz   |  |

| 1      | 1      | 0       | 1 MHz   | 8 MHz   |  |

| 1      | 1      | 1       | 500 KHz | 4 MHz   |  |

NOTE: All values shown are obtained with a 16 MHz reference clock. Divide all frequencies and multiply all periods by two for 8 MHz operation.

## FIG. 3 CLOCK AND HEAD LOAD TIME DELAY SELECTION

| FDCSEL           | INPUTS<br>DENS   | MINI             | FLOPPY DISK<br>DRIVE TYPE                          | FLOPPY DISK<br>DRIVE DENSITY         | FLOPPY DISK<br>CONTROLLER TYPE                       |

|------------------|------------------|------------------|----------------------------------------------------|--------------------------------------|------------------------------------------------------|

| 0<br>0<br>0<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 8" DRIVE<br>51/4" DRIVE<br>8" DRIVE<br>51/4" DRIVE | DOUBLE<br>DOUBLE<br>SINGLE<br>SINGLE | 179X<br>179X<br>179X<br>179X                         |

| 1<br>1<br>1      | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 8" DRIVE<br>51/4" DRIVE<br>8" DRIVE<br>51/4" DRIVE | SINGLE<br>SINGLE<br>DOUBLE<br>DOUBLE | 765 (8272)<br>765 (8272)<br>765 (8272)<br>765 (8272) |

FIG. 4 FLOPPY DISK DRIVE AND CONTROLLER SELECTION

<sup>\*</sup>May be mask programmed at factory to any value from 1 to 512 ms in 15.625 µs increments (MINI low) or 1 to 1024 ms in 31.25 µs increments (MINI high).

#### **MAXIMUM GUARANTEED RATINGS\***

| Operating Temperature Range0°C                          | to +70°C  |

|---------------------------------------------------------|-----------|

| Storage Temperature Range                               | o + 150°C |

| Lead Temperature (soldering, 10 sec.)                   | . +300°C  |

| Positive Voltage on any I/O Pin, with respect to ground | +8.0V     |

| Negative Voltage on any I/O Pin, with respect to ground | 0.3V      |

| Power Dissipation                                       |           |

<sup>\*</sup>Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

NOTE: When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes or "glitches" on their outputs when the AC power is switched on and off. In addition, voltage transients on the AC power line may appear on the DC output.

#### **ELECTRICAL CHARACTERISTICS** ( $T_A = 0^{\circ}\text{C}$ to $70^{\circ}\text{C}$ , $V_{CC} = 5\text{V} \pm 5\%$ )

| PARAMETER                  | MIN   | TYP | MAX                | UNIT | CONDITIONS                                 |

|----------------------------|-------|-----|--------------------|------|--------------------------------------------|

| DC CHARACTERISTICS         |       |     |                    |      |                                            |

| INPUT VOLTAGE              |       |     |                    |      |                                            |

| Low Level V <sub>IL</sub>  | - 0.3 |     | 0.8                | v    | Except CLKIN                               |

| High Level V₁ӊ             | 2.0   |     | (V <sub>cc</sub> ) | V    |                                            |

| CLKIN INPUT VOLTAGE        |       |     |                    |      |                                            |

| Low Level                  | -0.3  |     | 0.8                | V    | 1                                          |

| High Level                 | 2.4   |     | (V <sub>cc</sub> ) | V    |                                            |

| OUTPUT VOLTAGE             |       |     |                    |      |                                            |

| Low Level Vot              |       |     | 0.4                | V    | I <sub>OI</sub> = 1.6 mA except HLT/CLK    |

| <del></del>                |       |     |                    |      | I <sub>OL</sub> = 0.4 mA, HLT/CLK only     |

| High Level V <sub>он</sub> | 2.4   |     | 1                  | V    | $I_{OH} = -100 \mu\text{A}$ except HLT/CLI |

|                            |       |     |                    |      | $I_{OH} = -400 \mu\text{A}$ , HLT/CLK only |

| POWER SUPPLY CURRENT       |       |     |                    |      |                                            |

| I <sub>cc</sub>            |       |     | 100                | mA   |                                            |

| INPUT LEAKAGE CURRENT      |       |     |                    |      |                                            |

| l <sub>iL</sub>            |       |     | 10                 | μΑ   | $V_{IN} = 0 \text{ to } V_{CC}$            |

| INPUT CAPACITANCE          |       |     | 10                 | pF   | Except CLKIN                               |

| Cin                        |       |     | 25                 | pF   | CLKIN only                                 |

#### **ELECTRICAL CHARACTERISTICS** ( $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{cc} = 5V \pm 5\%$

| PARAMETER                        | MIN                                                         | TYP      | MAX         | UNIT       | CONDITIONS                   |  |

|----------------------------------|-------------------------------------------------------------|----------|-------------|------------|------------------------------|--|

| AC ELECTRICAL<br>CHARACTERISTICS | All times assume CLKIN = 16 MHz unless otherwise specified) |          |             |            |                              |  |

| CLKIN frequency                  | 3.95<br>3.95                                                | 16<br>8  | 16.2<br>8.1 | MHz<br>MHz | FDC 9229B<br>FDC 9229        |  |

| CLKIN DUTY CYCLE                 | 25                                                          |          | 75          | %          |                              |  |

| ckah                             | 465                                                         | 500      | 515         | ns         | FDCSEL = low; MINI = high.   |  |

|                                  | 215                                                         | 250      | 265         | ns         | FDCSEL = low; MINI = low.    |  |

|                                  | 90                                                          | 125      | 140         | ns         | FDCSEL = high.               |  |

| wdo                              | 280                                                         | 312.5    | 350         | ns         | Time Doubles with MINI = 1   |  |

| t <sub>a</sub>                   | 50                                                          |          | 400         | ns         |                              |  |

| dNEC                             | 0                                                           |          | 400         | ns         | 1                            |  |

| wdE                              | 500                                                         | 562.5    | 625         | ns         | 9 clock times ± 1 clock time |  |

| -wdN                             |                                                             | precom   |             |            | See fig. 2                   |  |

| wdL.                             |                                                             | 2x preco | mp value    |            | See fig. 2                   |  |

| ĺ <sub>s</sub>                   | 1.0                                                         | 1        |             | μs         |                              |  |

#### **AC TIMING CHARACTERISTICS**

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications; consequently complete information sufficient for construction purposes is not necessarily given. The information has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of SMC or others. SMC reserves the right to make changes at any time in order to improve design and supply the best product possible.