T-41-91

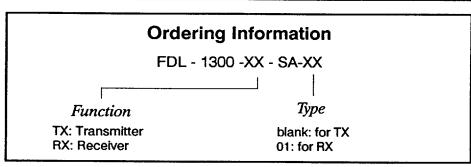

# FDL-1300-SA SPECIAL

#### **Data Link Modules for FDDI**

| reat | ures                                                        |

|------|-------------------------------------------------------------|

|      | Full FDDI Compliance                                        |

|      | Integral ST™ Optical Connector                              |

|      | Single Supply Voltage<br>( +5 V or -5.2 V)                  |

|      | Standard 16 Pin Footprint                                   |

|      | Model FDL-1300-SA is Pinout<br>Compatible with AT&T ODL-125 |

|      | Dual-in-Line Conductive Plastic<br>Package                  |

|      | 0°C to +70°C Operating<br>Temperature Range                 |

|      |                                                             |

## Description

The FDL-1300 Fiber Optic Transmitter and Receiver Data Link Set is designed to meet or exceed all the requirements of the Physical Layer Medium Dependent (PMD) specification for the Fiber Distributed Data Interface (FDDI). Highly reliable 1300 nm surface-emitting LEDs selected for proper rise/fall time, center wavelength and spectral width are utilized in the transmitters. The receivers incorporate an InGaAs/InP PIN photodiode and a high speed transimpedance amplifier to meet the sensitivity and dynamic range requirements of FDDI. The receiver post-amplifier

features the specified Signal Detect function and differential emitter coupled logic (ECL) outputs. The FDL-1300-SA transmitters and receivers are housed in a cost-effective 16-pin dual-in-line conductive plastic package with integral ST™ connector and operate on standard +5·volt or -5.2 volt power supply.

The FDL-1300-SA transmitter and receiver are pin compatible with the ODL-125 Data Link Modules from AT&T. The receiver, SA-01, is optimized for both 125 Mbaud (FDDI) and 50 Mbaud operation.

# **Optical Communication Products, Inc.**

ST is a trademark of AT&T

21737-0102 Rev. B 02/09/93

#### **Absolute Maximum Ratings**

| Parameter             | Minimum | Maximum        | Units |

|-----------------------|---------|----------------|-------|

| Storage Temperature   | - 55    | +100           | ~C    |

| Operating Temperature | - 40    | + 85           | °C    |

| Supply Voltage        | 0       | +6.0           | V     |

| Input Voltage         | 0       | +6.0           | V     |

| Lead Soldering        | -       | 240 °C, 10 sec | -     |

#### **Transmitter Electrical Interface**

| Parameter                                     |                                  | Symbol           | Minimum    | Typical                | Maximum                | Units |

|-----------------------------------------------|----------------------------------|------------------|------------|------------------------|------------------------|-------|

| Supply Voltage                                | +5 V                             | Vcc              | 4.75       | 5.0                    | 5.25                   | ٧     |

| Supply Voltage                                | - 5.2 V                          | VEE              | - 5.25     | - 5.2                  | - 4.75                 | ٧     |

| Supply Current                                |                                  | 1                | -          | 110                    | 135                    | mA    |

| Power Dissipation                             |                                  | Р                | -          | 550                    | 700                    | mW    |

| Input HIGH Voltage (Data/Data)                |                                  | ViHS             | Vcc - 1.15 | -                      | V <sub>CC</sub> - 0.73 | ٧     |

| Input LOW Voltage (Dat                        | a/Data)                          | Vils             | Vcc - 1.87 | -                      | V <sub>CC</sub> - 1.45 | V     |

| Differential Input Voltage                    |                                  | V <sub>DIF</sub> | 0.3        | -                      | 1.1                    | V     |

| Input Common Mode Voltage <sup>1</sup>        |                                  | VICM             | -          | -                      | 1.0                    | V     |

| Reference Voltage                             |                                  | V <sub>BB</sub>  | Vcc - 1.39 | V <sub>CC</sub> - 1.29 | Vcc - 1.17             | ٧     |

| <sup>1</sup> Permissible ± V <sub>ICM</sub> w | ith respect to V <sub>BB</sub> . |                  |            | <del></del>            |                        |       |

#### **Receiver Electrical Interface**

| Parameter           |         | Symbol | Minimum     | Typical | Maximum                | Units |

|---------------------|---------|--------|-------------|---------|------------------------|-------|

| Supply Voltage      | +5 V    | Vcc    | 4.75        | 5.0     | 5.25                   | ٧     |

|                     | - 5.2 V | VEE    | - 5.25      | - 5.2   | - 4.75                 | ٧     |

| Supply Current      |         | 1      | -           | 55      | 65                     | mA    |

| Power Dissipation   |         | Р      | -           | 275     | 350                    | mW    |

| Output HIGH Voltage |         | Voн    | Vcc - 1.035 | •       | V <sub>CC</sub> - 0.88 | V     |

| Output LOW Voltage  |         | Vol    | Vcc - 1.83  | •       | Vcc - 1.62             | ٧     |

## **Transmitter and Receiver Operation**

The transmitter behaves logically as a differential input gate which controls a 1300 nm LED. When the DATA input voltage is greater than the DATA input voltage, the LED is ON, and vice versa. In single-ended applications, the unused input pin should be connected to reference voltage VBB or biased to VCC - 1.29 volts.

The receiver converts the incident optical power to a photocurrent via a high performance PIN photodiode. The photocurrent is converted to a voltage signal by a transimpedance amplifier. This signal is then amplified by additional gain stages and processed through a shaping filter and a comparator to generate the differential ECL outputs.

Both outputs (DATA and DATA) are open emitters requiring termination to V<sub>CC</sub> - 2 volts with 50 ohms or to V<sub>EE</sub> with 510 ohms. For optimum performance both outputs should be terminated identically, even if only one output is used.

The Signal Detect circuit monitors the level of incoming optical signal and generates a logic LOW signal when insufficient photocurrent is produced to ensure proper operation. The Signal Detect can be used to control an external squelch circuit to gate off spurious outputs generated by the receiver when no optical input is available. The outputs are open emitter ECL requiring termination (510 ohms to VEE is recommended).

21737-0102 Rev. B 02/09/93

## Transmitter Performance (Over Operating Temperature Range 0°C to +70°C)

| Parameter                             | Symbol | Minimūm | Typical | Maximum | Units |

|---------------------------------------|--------|---------|---------|---------|-------|

| Data Rate                             | В      | DC      | 125     | 130     | Mb/s  |

| Optical Output Power                  | Po     | - 19.0  | - 16.0  | - 14.0  | dBm   |

| Center Wavelength <sup>1</sup>        | λο     | 1270    | 1320    | 1380    | nm    |

| Rise Time (10% to 90%) <sup>1</sup>   | tr     | 0.6     | -       | 3.0     | ns    |

| Fall Time (90% to 10%) <sup>1</sup>   | tf     | 0.6     | -       | 3.0     | ns    |

| Random Jitter (p-p)                   | RJ     | 0       | -       | 0.70    | ns    |

| Duty Cycle Distortion (p-p)           | DCD    | 0       | -       | 0.6     | ns    |

| Data Dependent Jitter (p-p)           | DDJ    | 0       | -       | 0.6     | ns    |

| Extinction Ratio<br>(Poff/Pon) x 100% | -      | _       | -       | 10      | %     |

| Transmit OFF Power                    | Poff   | -       | -       | - 45.0  | dBm   |

| Spectral Width <sup>1</sup>           | Δλ     | -       | 150     | -       | nm    |

# Receiver Performance (Over Operating Temperature Range 0°C to +70°C)

| Parameter                          |                          | Symbol          | Minimum | Typical | Maximum | Units |

|------------------------------------|--------------------------|-----------------|---------|---------|---------|-------|

| Data Rate                          |                          | В               | 1       | 125     | 130     | Mb/s  |

| Optical Input Power                | FDDI Test <sup>1</sup>   | P <sub>in</sub> | - 32.0  | - 33    | - 14.0  | dBm   |

| (BER = $2.5 \times 10^{-10}$ )     | Sensitivity <sup>2</sup> |                 | - 35.5  | - 37.0  |         |       |

| Signal Detect Thresholds           | Assertion                | P <sub>sd</sub> | -       | -       | - 35.0  | dBm   |

|                                    | Deassertion              |                 | - 45.0  | _       | -       |       |

| Signal Detect Hysteresis           |                          |                 | 1.5     | -       | -       | dB    |

| Signal Detect Timing               | Assertion                | T <sub>sd</sub> | -       | _       | 100     | μs    |

| olgilai Detect Tilling             | Deassertion              |                 | -       | -       | 350     |       |

| Wavelength of Operation            |                          | λ               | 1100    | 1320    | 1600    | nm    |

| Output Duty Cycle Distortion (p-p) |                          | DCD             |         | -       | 0.4     | ns    |

<sup>&</sup>lt;sup>1</sup> FDDI Test Conditions.

## **Application Notes**

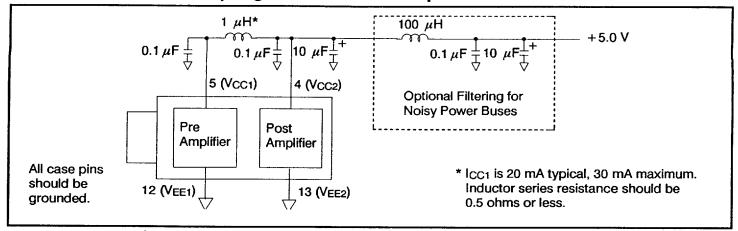

The transmitter and receiver power supply leads should be bypassed with RF quality capacitors (0.1microfarad) close to the package. A solid ground plane and low impedance power supply traces are highly recommended. The transmitter differential inputs and the receiver differential outputs are high speed ECL signals. Printed circuit board interconnections should be configured in accordance with ECL design rules. The MECL System Design Handbook from Motorola, Inc. is

an excellent reference. Board layouts created by CAD autorouting techniques should be reviewed carefully.

Special care should be taken with the receiver, since it is a very sensitive analog device. If the receiver outputs drive long traces or multiple loads, the use of an ECL buffer gate to isolate the receiver from transmission line reflections is recommended. Normal handling precautions for electrostatic-sensitive devices should be observed.

21737-0102 Rev. B 02/09/93

<sup>&</sup>lt;sup>2</sup> When tested with 2<sup>7</sup>-1 PRBS with 50% duty cycle, optical rise/fall time of 2.5 nsec, and optimum sampling point at 50 Mbaud.

### Recommended De-Coupling Circuit for +5 V Operation

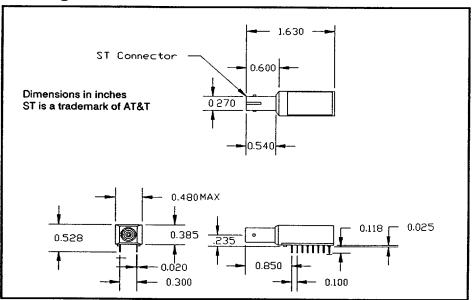

#### **Package Outline**

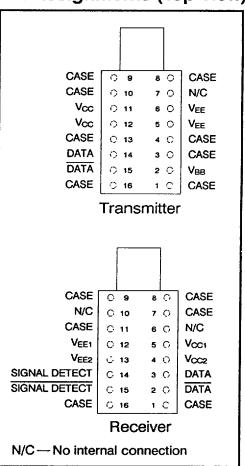

### Pin Assignments (Top View)

# Optical Communication Products, Inc.

9736 Eton Avenue, Chatsworth, CA 91311 Phone: 818-701-0164, FAX: 818-701-1468

Optical Communication Products, Inc. reserves the right to make changes in equipment design or specifications without notice. Information supplied by Optical Communication Products, Inc. is believed to be accurate and reliable. However, no responsibility is assumed by Optical Communication Products, Inc. for its use nor for any infringements of third parties which may result from its use. No license is granted by implication or otherwise under any patent right of Optical Communication Products, Inc.

21737-0102 Rev. B 02/09/93

4