# MX·COM, INC.

# MX419 MX519

# 1200 BAUD MINIMUM SHIFT KEY MODEM

#### **FEATURES:**

- Full Duplex 1200 Baud MSK

- On-Chip R<sub>x</sub>/T<sub>x</sub> Bandpass Filters

- R<sub>x</sub>/T<sub>x</sub> Synchronization Clocks

- Carrier Detect O/P

- Narrow Band Frequency Shift

- Few External Components Required

- Read/Write Sync Control

- Easy Microprocessor Interface

#### **APPLICATIONS:**

- Nordic Mobile Telephone 450/900 Cellular

- German ZVEI

- French Radiocomm 2000

- UK Band III

- · Japanese Personal Radio trunked SMR systems

- Packet Radio

- · Radio Telemetry

#### **DESCRIPTION:**

The MX419/519 is a single chip CMOS LSI Modern employing Minimum Shift Key signaling at 1200 baud, compatible with the data transmission standards of numerous operating systems worldwide. In addition to the applications listed above, the American Association of Railroads uses 1200 baud MSK on board trains in a radio telemetry application that replaced the caboose.

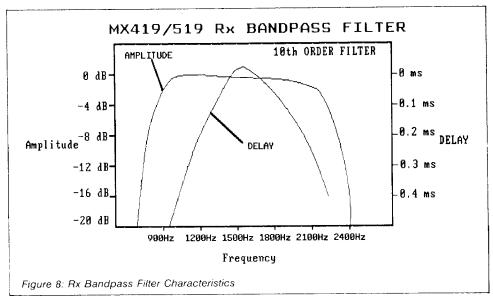

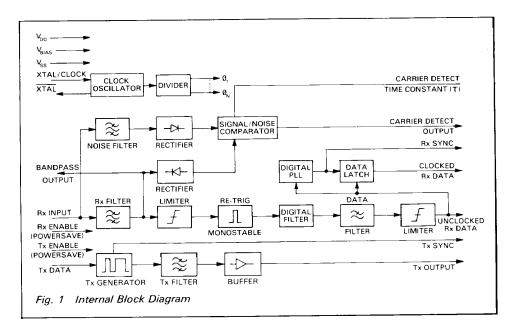

MSK (also known as FFSK) operation at 1200 baud employs phase continuous 1200/1800 Hz mark and space frequencies in which data transitions occur only at the signal zero crossing point. This provides identical mark/space period timing and an occupied band of only 1200 Hz. The MX419/519 derives its carriers, switched capacitor filter clocks, and  $R_x$  and  $T_x$  synchronization from an external 1.008 MHz crystal. A carrier detect O/P is provided as well as a recovered  $R_x$  clock.

The MX419 succeeds the MX409 in a functionally equivalent package, while adding an output from the  $R_x$  bandpass filter. The MX519 employs the same die in a smaller, more economical 16 pin DIP package.

#### **MX419/519 PIN FUNCTION TABLE**

|                 | PIN             |                 | FUNCTION/DESCRIPTION                                                                                                                                                                                                                                                                                                             |

|-----------------|-----------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP<br>MX419J,P | PLCC<br>MX419LH | DIP<br>MX519J,P |                                                                                                                                                                                                                                                                                                                                  |

| 1               | 1               | 16              | <b>Xtal/Clock:</b> The input to an on-chip inverter for use with a 1.008MHz xtal. Alternatively, a 1.008MHz clock may be used.                                                                                                                                                                                                   |

| 2               | 2               | 1               | Xtal: Output of on-chip inverter.                                                                                                                                                                                                                                                                                                |

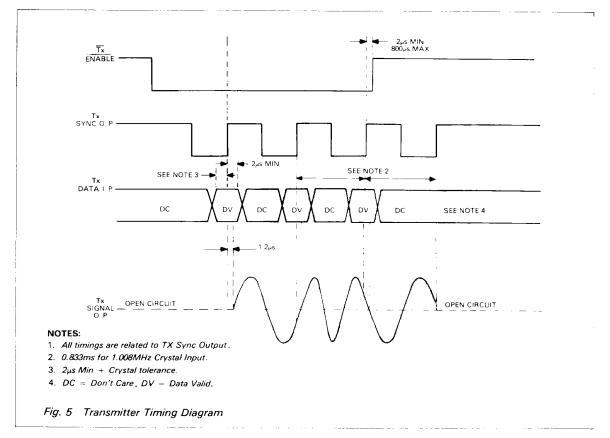

| 3               | 3               | 2               | Tx Sync O/P: A 1200Hz squarewave used to synchronize the input of logic data and transmission of the MSK signal (See Fig. 5).                                                                                                                                                                                                    |

| 4               | 4               |                 | No Connection: Leave open circuit.                                                                                                                                                                                                                                                                                               |

| 5               | 5               | 3               | Tx Signal O/P: With transmitter disabled, this pin is set to a high impedance state. When transmitter is enabled, this pin outputs the 1200/1800Hz (140 step pseudo-sinewave) MSK signal (See Fig. 5).                                                                                                                           |

| 6               | 7               | 4               | Tx Data I/P: Serial logic data to be transmitted, is input to this pin and synchronized by the "Tx Sync O/P" (See Fig. 5).                                                                                                                                                                                                       |

| 7               | 8               | 5               | Tx Enable: A logic '1' applied to this input will put the transmitter into powersave while forcing "Tx Sync O/P" to logic '1' and "Tx Signal O/P" to a high impedance state. A logic '0' will enable the transmitter (See Fig. 5). This pin is internally pulled to V <sub>DD</sub> .                                            |

| 8               | 9               |                 | <b>Bandpass O/P:</b> This is the output of the Rx 900-2100Hz bandpass filter. The output impedance of this pin is typically 10k $\Omega$ and may require buffering prior to use.                                                                                                                                                 |

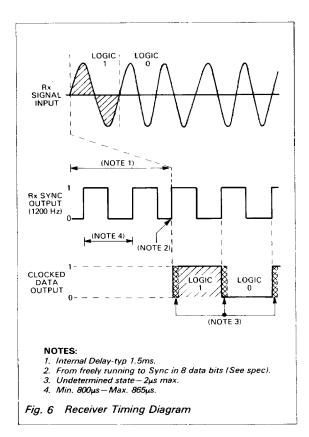

| 9               | 10              | 6               | <b>Rx Enable:</b> A logic '0' applied to this input will put the receiver into powersave while forcing "Clocked Data O/P" and "Carrier Detect" to logic '0.' A logic '1' will enable the receiver (See Figures 2 and 6). "Rx Sync Out" may be logic '1' or '0' during powersave. This pin is internally pulled to $V_{\rm DD}$ . |

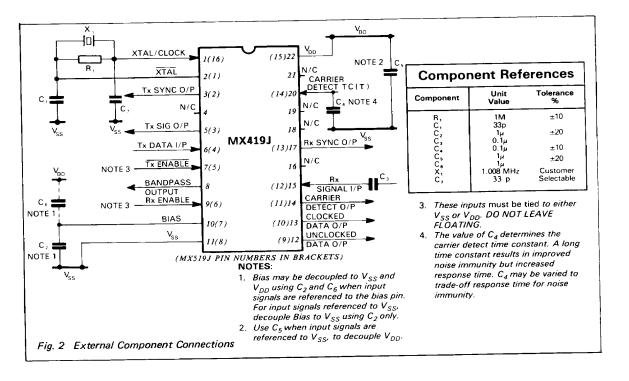

| 10              | 11              | 7               | <b>Bias:</b> Provides bias internally and should be decoupled externally to $V_{SS}$ by a capacitor (See Fig. 2).                                                                                                                                                                                                                |

| 11              | 12              | 8               | V <sub>ss</sub> : Negative supply.                                                                                                                                                                                                                                                                                               |

| 12              | 13              | 9               | <b>Unclocked Data O/P:</b> This pin outputs recovered asynchronous serial data from the receiver.                                                                                                                                                                                                                                |

| 13              | 14              | 10              | Clocked Data O/P: This pin outputs recovered synchronous serial data from the receiver and is internally latched out by a recovered clock appearing on the "Rx Sync O/P" pin (See Figures 2 and 6).                                                                                                                              |

# **MX419/519 PIN FUNCTION TABLE**

|                 | PIN             |                 | FUNCTION/DESCRIPTION                                                                                                                                                                                                                              |  |  |

|-----------------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DIP<br>MX419J,P | PLCC<br>MX419LH | DIP<br>MX519J,P |                                                                                                                                                                                                                                                   |  |  |

| 14              | 15              | 11              | <b>Carrier Detect:</b> This pin will output a logic '1' when an MSK signal is being received.                                                                                                                                                     |  |  |

| 15              | 16              | 12              | $\mbox{\bf RxSignalI/P:}$ This is the MSK signal input pin for the receiver and should be decoupled via a capacitor $\mbox{\bf C}_3.$                                                                                                             |  |  |

| 16              | 17              |                 | No Connection: Leave open circuit.                                                                                                                                                                                                                |  |  |

| <b>17</b>       | 18              | 13              | Rx Sync O/P: This is a flywheel 1200Hz squarewave output which, upon presentation of MSK data signal, is synchronized internally to the incoming data (See Figures 2 and 6).                                                                      |  |  |

| 18,19           | 19, 20, 21      |                 | No Connection: Leave open circuit.                                                                                                                                                                                                                |  |  |

| 20              | 22              | 14              | Carrier Detect Time Constant $(\tau)$ : This input forms part of the carrier detect integration function. The value of $C_4$ connected to this pin will affect the carrier detect response time and hence noise performance (See Fig. 2, Note 4). |  |  |

| 21              | 23              |                 | No Connection: Leave open circuit.                                                                                                                                                                                                                |  |  |

| 22              | 24              | 15              | V <sub>DD</sub> : Positive supply.                                                                                                                                                                                                                |  |  |

#### Note: Output Loading.

Large capacitive loads could cause the output pins of this device to oscillate. If capacitive loads in excess of 200pF are unavoidable, a resistor of typically  $<100\Omega$  put in series with the load should minimize this effect.

# **MX419/519 ELECTRICAL SPECIFICATIONS**

### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

| implied.                                            |                                        |                              |

|-----------------------------------------------------|----------------------------------------|------------------------------|

| Supply voltage                                      |                                        | -0.3V to 7.0V                |

| Input voltage at any pin (ref V <sub>SS</sub> = OV) |                                        | $-0.3V$ to $(V_{DD} + 0.3V)$ |

| Output sink/source current (total)                  |                                        | 20mA                         |

| Operating temperature range:                        | MX419J/MX519J                          | -30°C to +85°C               |

| Speraming to the second second                      | MX419P,LH/MX519P                       | -30°C to +70°C               |

| Storage temperature range:                          | MX419J/MX519J                          | -55°C to +125°C              |

| Glorago tomporataro rango.                          | MX419P.LH/MX519P                       | -40°C to +85°C               |

| Maximum device dissipation:                         | ······································ | All versions 100mW           |

## Operating Limits

$V_{DD} = +5V$ ,  $T_{amb} = 25^{\circ}C$ ,  $\emptyset = 1.008MHz$  (Xtal),  $\Delta f\emptyset = 0$

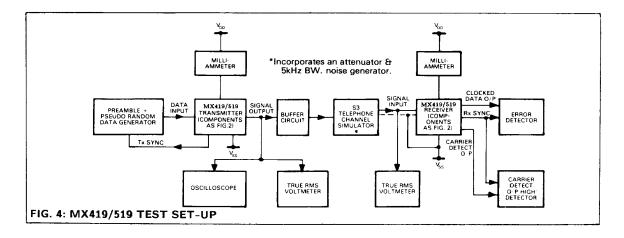

All characteristics measured using the standard test circuit (figure 4) with the following test parameters which is valid for all tests unless otherwise stated:

0dB reference

300mV rms

Noise

(band limited 5kHz gaussian white noise)

SNR ratio measured in bit rate bandwidth (1200Hz)

| Characteristics                            | See Note           | Min                 | Тур   | Max                | Unit             |

|--------------------------------------------|--------------------|---------------------|-------|--------------------|------------------|

| Static Characteristics                     |                    |                     |       |                    |                  |

| Supply volts                               |                    | 4.5                 | 5.0   | 5.5                | V                |

| Supply current: Rx (Enabled) Tx (Disabled) |                    | _                   | 3.6   |                    | mA               |

| Rx (Enabled) Tx (Enable                    | _                  | 4.5                 | _     | mA                 |                  |

| Rx (Disabled) Tx (Disable                  | _                  | 650                 | _     | μА                 |                  |

| Logic '1' level                            | 80%V <sub>DD</sub> |                     | _     | V                  |                  |

| Logic '0' level                            |                    | _                   | _     | 20%V <sub>DD</sub> | v                |

| Digital O/P Impedance                      |                    | _                   | 4     | _                  | kΩ               |

| Analog and Digital input impedance         |                    | 100                 | _     |                    | kΩ               |

| Tx O/P impedance                           |                    | _                   | 10    |                    | kΩ               |

| On-chip crystal oscillator:                |                    |                     | . •   |                    | 1142             |

| R <sub>in</sub>                            |                    | 10                  |       | _                  | MΩ               |

| R <sub>out</sub>                           |                    | 5                   | _     | 15                 | kΩ               |

| Inverter gain                              |                    | 10                  | _     | 20                 | dB               |

| Gain Bandwidth Product                     |                    | 3 × 10 <sup>6</sup> | _     | _                  | u.b              |

| Crystal frequency                          | 1                  | _                   | 1.008 |                    | MHz              |

| Dynamic Characteristics                    | •                  |                     | 1.000 |                    | 1411 12          |

| Receiver:                                  |                    |                     |       |                    |                  |

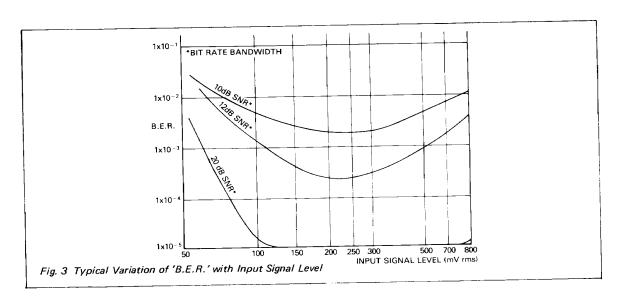

| Signal Input: Dynamic range (50dB SNR)     | 2,3                | 100                 | 230   | 1000               | mV rms           |

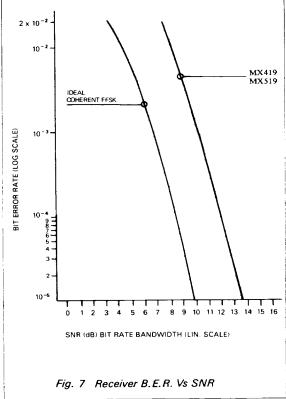

| Bit Error Rate: 12dB SNR                   | 3                  | _                   | 7.0   | _                  | 10-4             |

| 20dB SNR                                   | 3                  | _                   | 1.0   | _                  | 10 <sup>-8</sup> |

| Receiver Synchronization 12dB SNR:         | 6                  |                     |       |                    | 10               |

| Probability of bit 8 being correct         | -                  |                     | 0.99  |                    |                  |

| Probability of bit 16 being correct        |                    |                     | 0.995 |                    |                  |

| Carrier Detect                             | 6                  |                     | 0.000 |                    |                  |

| Probability of Carrier Detect being high:  |                    |                     |       |                    |                  |

| 12dB SNR after bit 8                       | 4                  |                     | 0.99  | 0.98               |                  |

| 12dB SNR after bit 16                      | 4                  |                     | 0.999 | 0.995              |                  |

| 0dB noise                                  | •                  |                     | 0.000 | 0.01               |                  |

| Transmitter O/P                            |                    |                     |       | 0.01               |                  |

| Tx O/P level                               |                    |                     | 775   | _                  | mV rms           |

| Output level variation 1200/1800Hz         |                    | 0                   |       | ± 1.00             | dB               |

| O/P distortion                             |                    | _                   | 3     | ± 1.00<br>5        | %                |

| 3rd harmonic distortion                    |                    | _                   | 2     | 3                  | %                |

| Logic '1' carrier frequency                | 5                  | _                   | 1200  | _                  | /o<br>Hz         |

| Logic '0' carrier frequency                | 5                  | _                   | 1800  | _                  | Hz               |

| Isochronous distortion                     | -                  |                     | .000  |                    | . 12             |

| 1200Hz-1800Hz                              |                    |                     | 25    | 40                 | μS               |

| 1800Hz-1200Hz                              |                    | _                   | 20    | 40                 | •                |

| . 3001 IZ 12001 IZ                         |                    | _                   | 20    | 40                 | μS               |

Notes: 1. Crystal tolerance depends on system requirements.

<sup>2.</sup> See Fig. 3.

<sup>3.</sup> SNR (Bit Rate Bandwidth).

<sup>4.</sup> Signal In = 0db (300 mV rms), SNR ≥ 20dB

<sup>5.</sup> Depending on crystal tolerance.

<sup>6. 101010</sup> Pattern.