# Index of /ds/FS/

|             | Name             | Last modif | ied   | Size | Description |

|-------------|------------------|------------|-------|------|-------------|

|             | Parent Directory |            |       |      |             |

|             | FSB560.pdf       | 22-Dec-99  | 00:08 | 208K |             |

|             | FSB560A.pdf      | 22-Dec-99  | 00:08 | 208K |             |

|             | FSB619.pdf       | 22-Dec-99  | 00:08 | 27K  |             |

|             | FSB660.pdf       | 22-Dec-99  | 00:08 | 209K |             |

|             | FSB660A.pdf      | 22-Dec-99  | 00:08 | 209K |             |

|             | FSB6726.pdf      | 22-Dec-99  | 00:08 | 23K  |             |

|             | FSBCW30.pdf      | 22-Dec-99  | 00:08 | 43K  |             |

| <u>L</u>    | FST16209.pdf     | 31-Dec-99  | 00:00 | 134K |             |

|             | FST16210.pdf     | 31-Dec-99  | 00:00 | 110K |             |

| <u>[</u> ]_ | FST16211.pdf     | 31-Dec-99  | 00:00 | 213K |             |

|             | FST16212.pdf     | 31-Dec-99  | 00:00 | 155K |             |

|             | FST16213.pdf     | 31-Dec-99  | 00:00 | 153K |             |

|             | FST16232.pdf     | 31-Dec-99  | 00:00 | 98K  |             |

|             | FST16233.pdf     | 31-Dec-99  | 00:00 | 97K  |             |

| <u> </u>    | FST162861.pdf    | 09-Jan-00  | 00:00 | 163K |             |

|             | FST16292.pdf     | 31-Dec-99  | 00:00 | 95K  |             |

|             | FST16861.pdf     | 09-Jan-00  | 00:00 | 88K  |             |

|             | FST3125.pdf      | 31-Dec-99  | 00:00 | 123K |             |

|             | FST3126.pdf      | 31-Dec-99  | 00:00 | 121K |             |

|             | FST3244.pdf      | 31-Dec-99  | 00:00 | 103K |             |

|             | FST3245.pdf      | 31-Dec-99  | 00:00 | 110K |             |

|             | FST3253.pdf      | 31-Dec-99  | 00:00 | 138K |             |

|             | FST3257.pdf      | 31-Dec-99  | 00:00 | 96K  |             |

|        | FST3345.pdf    | 31-Dec-99 | 00:00 | 119K |

|--------|----------------|-----------|-------|------|

|        | FST3383.pdf    | 22-Dec-99 | 00:08 | 50K  |

|        | FST3384.pdf    | 31-Dec-99 | 00:00 | 99K  |

|        | FST3384A.pdf   | 22-Dec-99 | 00:08 | 90K  |

|        | FST6800.pdf    | 31-Dec-99 | 00:00 | 121K |

|        | FSTD16211.pdf  | 21-Dec-99 | 00:00 | 227K |

|        | FSTU32160.pdf  | 22-Dec-99 | 00:08 | 108K |

|        | FSTU32160A.pdf | 22-Dec-99 |       | 108K |

| <br>Fì | FSTU3257.pdf   | 21-Dec-99 |       | 81K  |

| Fì     | _              |           |       |      |

| <br>   | FSTU3384.pdf   | 31-Dec-99 |       | 99K  |

|        | FSTU6800.pdf   | 31-Dec-99 |       | 181K |

|        | FSTU6800A.pdf  | 31-Dec-99 | 00:00 | 182K |

**July 1998**

# **FSB560 / FSB560A**

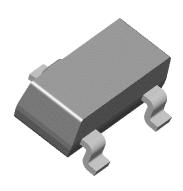

SuperSOT<sup>™</sup>-3 (SOT-23)

## **NPN Low Saturation Transistor**

These devices are designed with high current gain and low saturation voltage with collector currents up to 2A continuous.

Absolute Maximum Ratings\* T<sub>A = 25°C unless otherwise noted</sub>

| Symbol                           | Parameter                                        | FSB560/FSB560A | Units |

|----------------------------------|--------------------------------------------------|----------------|-------|

| V <sub>CEO</sub>                 | Collector-Emitter Voltage                        | 60             | V     |

| V <sub>CBO</sub>                 | Collector-Base Voltage                           | 80             | V     |

| V <sub>EBO</sub>                 | Emitter-Base Voltage                             | 5              | V     |

| Ic                               | Collector Current - Continuous                   | 2              | А     |

| T <sub>J,</sub> T <sub>stg</sub> | Operating and Storage Junction Temperature Range | -55 to +150    | °C    |

<sup>\*</sup>These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.

#### NOTES:

- 1) These ratings are based on a maximum junction temperature of 150  $^{\circ}\text{C}.$

- 2) These are steady state limits. The factory should be consulted on applications involving pulsed or low duty cycle operations.

# Thermal Characteristics T<sub>A = 25°C unless otherwise noted</sub>

| Symbol            | Characteristic                          | Max            | Units |

|-------------------|-----------------------------------------|----------------|-------|

|                   |                                         | FSB560/FSB560A |       |

| P <sub>D</sub>    | Total Device Dissipation                | 500            | mW    |

| R <sub>θ</sub> JA | Thermal Resistance, Junction to Ambient | 250            | °C/W  |

| NPN | Low | Saturation | <b>Transistor</b> |

|-----|-----|------------|-------------------|

|     |     |            |                   |

(continued)

## **Electrical Characteristics**

T<sub>A = 25°C</sub> unless otherwise noted

| Symbol               | Parameter                            | Test Conditions                                            | Min | Max  | Units |

|----------------------|--------------------------------------|------------------------------------------------------------|-----|------|-------|

| OFF CHAI             | RACTERISTICS                         |                                                            |     |      |       |

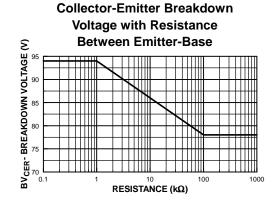

| BV <sub>CEO</sub>    | Collector-Emitter Breakdown Voltage  | I <sub>C</sub> = 10 mA                                     | 60  |      | V     |

| BV <sub>CBO</sub>    | Collector-Base Breakdown Voltage     | I <sub>C</sub> = 100 μA                                    | 80  |      | V     |

| BV <sub>EBO</sub>    | Emitter-Base Breakdown Voltage       | I <sub>E</sub> = 100 μA                                    | 5   |      | V     |

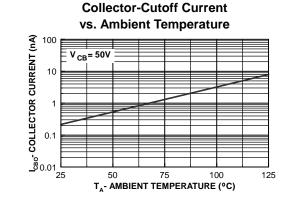

| I <sub>CBO</sub>     | Collector Cutoff Current             | V <sub>CB</sub> = 30 V                                     |     | 100  | nA    |

|                      |                                      | V <sub>CB</sub> = 30 V, T <sub>A</sub> =100°C              |     | 10   | uA    |

| I <sub>EBO</sub>     | Emitter Cutoff Current               | V <sub>EB</sub> = 4V                                       |     | 100  | nA    |

| ON CHAR              | ACTERISTICS*                         |                                                            |     | ı    |       |

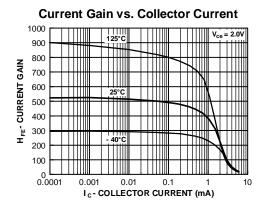

| h <sub>FE</sub>      | DC Current Gain                      | I <sub>C</sub> = 100 mA, V <sub>CE</sub> = 2 V             | 70  |      | -     |

|                      |                                      | I <sub>C</sub> =500mA, V <sub>CE</sub> =2V <b>FSB560</b>   | 100 | 300  |       |

|                      |                                      | FSB560A                                                    | 250 | 550  |       |

|                      |                                      | I <sub>C</sub> = 1 A, V <sub>CE</sub> = 2 V                | 80  |      |       |

|                      |                                      | I <sub>C</sub> = 2 A, V <sub>CE</sub> = 2 V                | 40  |      |       |

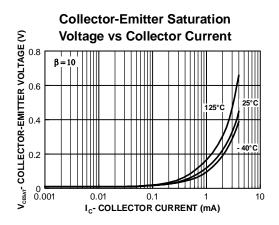

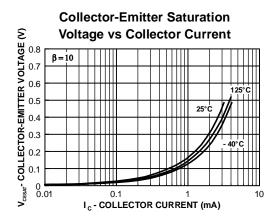

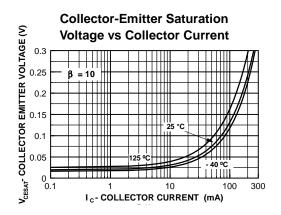

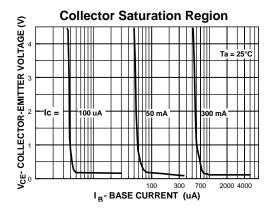

| V <sub>CE(sat)</sub> | Collector-Emitter Saturation Voltage | I <sub>C</sub> = 1 A, I <sub>B</sub> = 100 mA              |     | 300  | mV    |

| ,                    |                                      | I <sub>C</sub> = 2 A, I <sub>B</sub> =200 mA <b>FSB560</b> |     | 350  |       |

|                      |                                      | FSB560A                                                    |     | 300  |       |

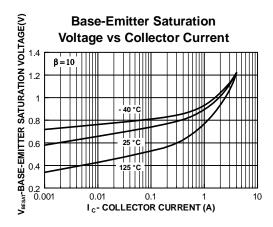

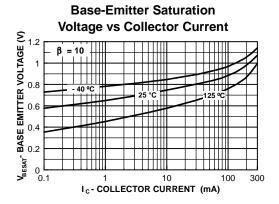

| V <sub>BE(sat)</sub> | Base-Emitter Saturation Voltage      | I <sub>C</sub> = 1 A, I <sub>B</sub> = 100 mA              |     | 1.25 | V     |

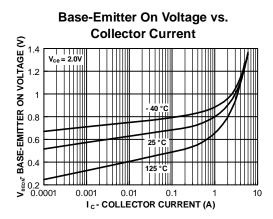

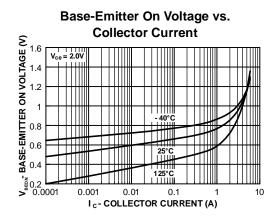

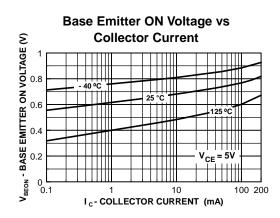

| V <sub>BE(on)</sub>  | Base-Emitter On Voltage              | I <sub>C</sub> = 1 A, V <sub>CE</sub> = 2 V                |     | 1    | V     |

| SMALL SI             | GNAL CHARACTERISTICS                 |                                                            |     |      |       |

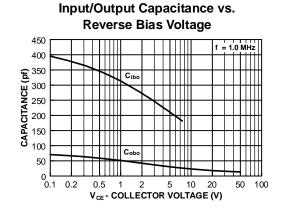

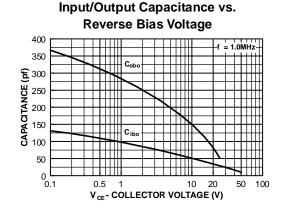

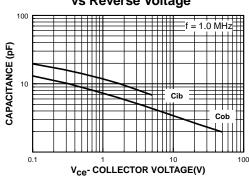

| C <sub>obo</sub>     | Output Capacitance                   | V <sub>CB</sub> = 10 V, I <sub>E</sub> = 0, f = 1MHz       |     | 30   | pF    |

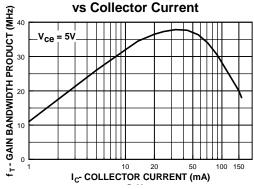

| f <sub>T</sub>       | Transition Frequency                 | I <sub>C</sub> = 100 mA,V <sub>CE</sub> = 5 V, f=100MHz    | 75  |      | -     |

\*Pulse Test: Pulse Width  $\leq 300~\mu s,~Duty~Cycle \leq 2.0\%$

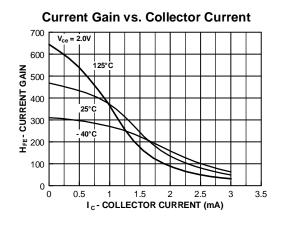

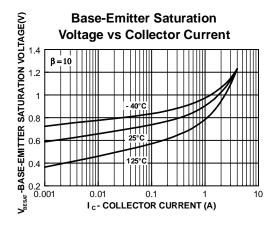

# **Typical Characteristics**

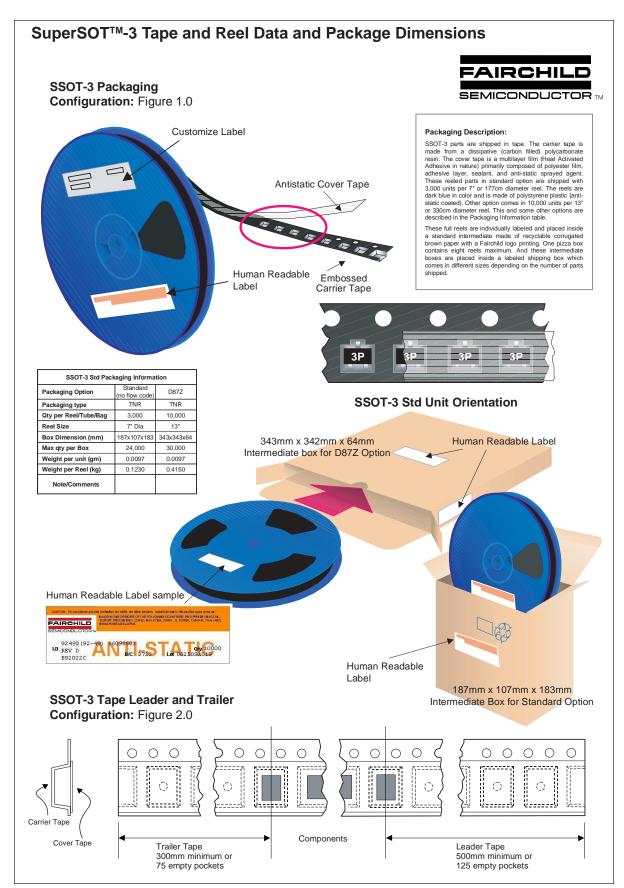

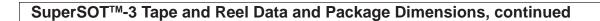

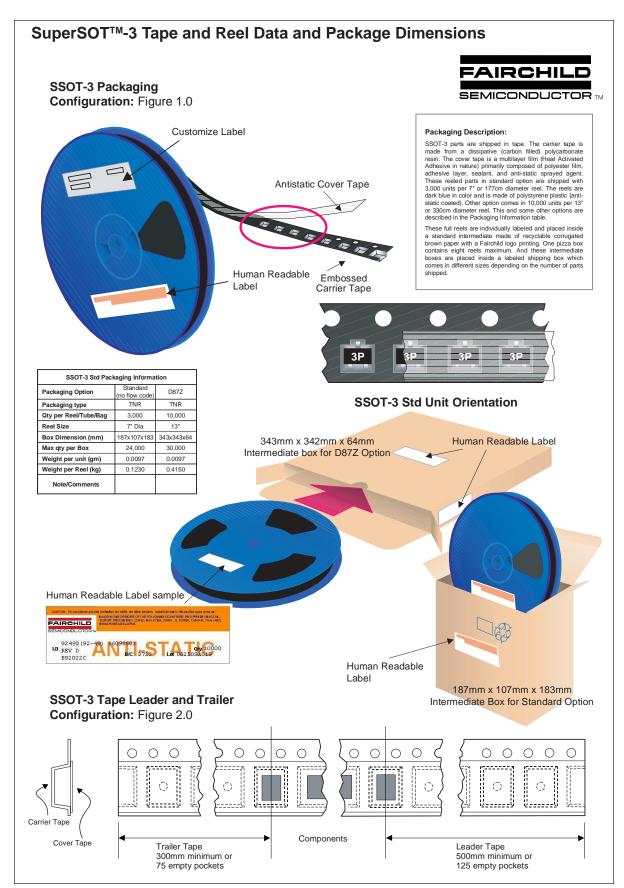

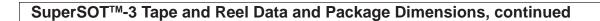

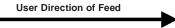

# **SSOT-3 Embossed Carrier Tape**

Configuration: Figure 3.0

| Dimensions are in millimeter                                                                                                                         |                 |                 |               |                 |                   |                 |             |                 |               |               |                 |                   |               |               |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|---------------|-----------------|-------------------|-----------------|-------------|-----------------|---------------|---------------|-----------------|-------------------|---------------|---------------|

| Pkg type         A0         B0         W         D0         D1         E1         E2         F         P1         P0         K0         T         Wc |                 |                 |               |                 |                   |                 | Тс          |                 |               |               |                 |                   |               |               |

| SSOT-3<br>(8mm)                                                                                                                                      | 3.15<br>+/-0.10 | 2.77<br>+/-0.10 | 8.0<br>+/-0.3 | 1.55<br>+/-0.05 | 1.125<br>+/-0.125 | 1.75<br>+/-0.10 | 6.25<br>min | 3.50<br>+/-0.05 | 4.0<br>+/-0.1 | 4.0<br>+/-0.1 | 1.30<br>+/-0.10 | 0.228<br>+/-0.013 | 5.2<br>+/-0.3 | 0.06<br>+/-02 |

Notes: A0, B0, and K0 dimensions are determined with respect to the EIA/Jedec RS-481 rotational and lateral movement requirements (see sketches A, B, and C).

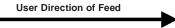

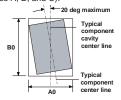

Sketch A (Side or Front Sectional View)

Component Rotation

Sketch B (Top View)

Component Rotation

Sketch C (Top View)

Component lateral movement

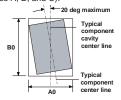

DETAIL AA

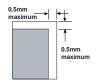

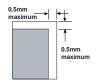

## SSOT-3 Reel Configuration: Figure 4.0

| Dimensions are in inches and millimeters |                |               |              |                                   |               |             |                                   |               |                             |

|------------------------------------------|----------------|---------------|--------------|-----------------------------------|---------------|-------------|-----------------------------------|---------------|-----------------------------|

| Tape Size                                | Reel<br>Option | Dim A         | Dim B        | Dim C                             | Dim D         | Dim N       | Dim W1                            | Dim W2        | Dim W3 (LSL-USL)            |

| 8mm                                      | 7" Dia         | 7.00<br>177.8 | 0.059<br>1.5 | 512 +0.020/-0.008<br>13 +0.5/-0.2 | 0.795<br>20.2 | 2.165<br>55 | 0.331 +0.059/-0.000<br>8.4 +1.5/0 | 0.567<br>14.4 | 0.311 - 0.429<br>7.9 - 10.9 |

| 8mm                                      | 13" Dia        | 13.00<br>330  | 0.059<br>1.5 | 512 +0.020/-0.008<br>13 +0.5/-0.2 | 0.795<br>20.2 | 4.00<br>100 | 0.331 +0.059/-0.000<br>8.4 +1.5/0 | 0.567<br>14.4 | 0.311 - 0.429<br>7.9 - 10.9 |

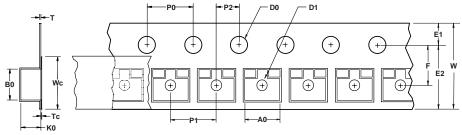

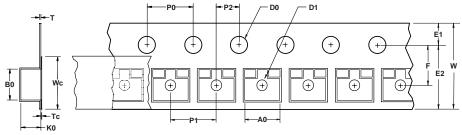

# SuperSOT™-3 Tape and Reel Data and Package Dimensions, continued

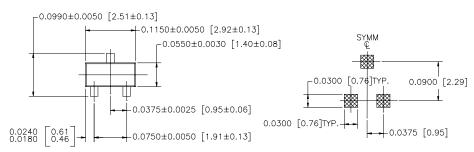

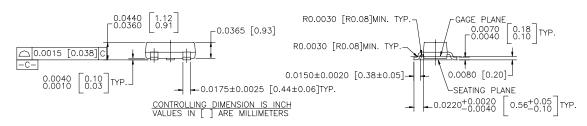

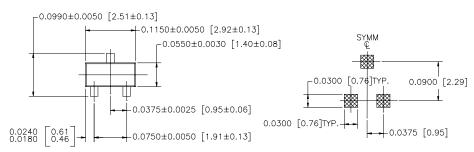

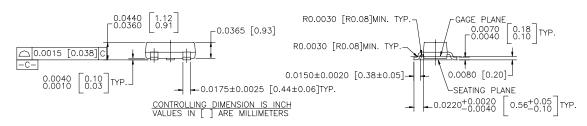

# SuperSOT™-3 (FS PKG Code 32)

Scale 1:1 on letter size paper

Dimensions shown below are in:

inches [millimeters]

Part Weight per unit (gram): 0.0097

LAND PATTERN RECOMMENDATION

NOTES: UNLESS OTHERWISE SPECIFIED

SUPER SOT , 3 LEADS

- 1. STANDARD LEAD FINISH TO BE 150 MICROINCHES / 3.81 MICROMETERS MINIMUM TIN/LEAD (SOLDER) ON COPPER.

- 2. NO JEDEC REGISTRATION AS OF DEC. 1995.

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

CROSSVOLT<sup>TM</sup> POP<sup>TM</sup>

E<sup>2</sup>CMOS<sup>™</sup> PowerTrench<sup>™</sup>

FACT<sup>TM</sup> QS<sup>TM</sup>

FACT Quiet Series TM Quiet Series TM SuperSOT TM-3 SuperSOT TM-6 GTO TM SuperSOT TM-8 TinyLogic TM TinyLogic TM

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |

# Discrete Power & Signal Technologies

**July 1998**

# **FSB619**

SuperSOT<sup>™</sup>-3 (SOT-23)

## **NPN Low Saturation Transistor**

These devices are designed with high current gain and low saturation voltage with collector currents up to 3A continuous.

# Absolute Maximum Ratings\* TA = 25°C unless otherwise noted

| Symbol                           | Parameter                                        | FSB619      | Units |

|----------------------------------|--------------------------------------------------|-------------|-------|

| V <sub>CEO</sub>                 | Collector-Emitter Voltage                        | 50          | V     |

| V <sub>CBO</sub>                 | Collector-Base Voltage                           | 50          | V     |

| V <sub>EBO</sub>                 | Emitter-Base Voltage                             | 5           | V     |

| Ic                               | Collector Current - Continuous                   | 2           | А     |

| T <sub>J,</sub> T <sub>stg</sub> | Operating and Storage Junction Temperature Range | -55 to +150 | °C    |

<sup>\*</sup>These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.

#### **NOTES**

- 1) These ratings are based on a maximum junction temperature of 150°C.

- 2) These are steady state limits. The factory should be consulted on applications involving pulsed or low duty cycle operations.

## Thermal Characteristics T<sub>A = 25°C unless otherwise noted</sub>

| Symbol            | Characteristic                              | Max      | Units       |

|-------------------|---------------------------------------------|----------|-------------|

|                   |                                             | FSB619   |             |

| P <sub>D</sub>    | Total Device Dissipation* Derate above 25°C | 500<br>4 | mW<br>mW/°C |

| R <sub>θ</sub> JA | Thermal Resistance, Junction to Ambient     | 250      | °C/W        |

\*Device mounted on FR-4 PCB 4.5" X 5"; mounting pad 0.02 in² of 2oz copper.

# **NPN Low Saturation Transistor**

(continued)

| Ele | ctr | ica | I Characteristics | T <sub>A = 25°C unless otherwise note</sub> |

|-----|-----|-----|-------------------|---------------------------------------------|

| _   |     |     |                   |                                             |

| Symbol               | Parameter                            | Test Conditions                                         | Min | Max | Units |

|----------------------|--------------------------------------|---------------------------------------------------------|-----|-----|-------|

| OFF CHAF             | RACTERISTICS                         |                                                         |     |     |       |

| BV <sub>CEO</sub>    | Collector-Emitter Breakdown Voltage  | I <sub>C</sub> = 10 mA                                  | 50  |     | V     |

| BV <sub>CBO</sub>    | Collector-Base Breakdown Voltage     | I <sub>C</sub> = 100 μA                                 | 50  |     | V     |

| BV <sub>EBO</sub>    | Emitter-Base Breakdown Voltage       | I <sub>E</sub> = 100 μA                                 | 5   |     | V     |

| I <sub>CBO</sub>     | Collector Cutoff Current             | V <sub>CB</sub> = 40 V                                  |     | 100 | nA    |

| I <sub>EBO</sub>     | Emitter Cutoff Current               | V <sub>EB</sub> = 4V                                    |     | 100 | nA    |

| I <sub>CES</sub>     | Collector Emitter Cutoff Current     | V <sub>CES</sub> = 40 V                                 |     | 100 | nA    |

| ON CHAR              | ACTERISTICS*                         |                                                         |     |     |       |

| h <sub>FE</sub>      | DC Current Gain                      | I <sub>C</sub> = 10 mA, V <sub>CE</sub> = 2V            | 200 |     | -     |

|                      |                                      | $I_C = 200 \text{ mA}, V_{CE} = 2V$                     | 300 |     |       |

|                      |                                      | $I_C = 1A$ , $V_{CE} = 2V$                              | 200 |     |       |

|                      |                                      | $I_C = 2A$ , $V_{CE} = 2V$                              | 100 |     |       |

| V <sub>CE(sat)</sub> | Collector-Emitter Saturation Voltage | $I_C = 100 \text{ mA}, I_B = 10 \text{ mA}$             |     | 20  | mV    |

| , ,                  |                                      | $I_C = 1 \text{ A}, I_B = 10 \text{ mA}$                |     | 235 |       |

|                      |                                      | $I_C = 2 \text{ A}, I_B = 50 \text{ mA}$                |     | 320 |       |

| V <sub>BE(sat)</sub> | Base-Emitter Saturation Voltage      | I <sub>C</sub> = 2 A, I <sub>B</sub> = 50 mA            |     | 1   | V     |

| V <sub>BE(on)</sub>  | Base-Emitter On Voltage              | I <sub>C</sub> = 2 A, V <sub>CE</sub> = 2 V             |     | 1   | V     |

| SMALL SI             | GNAL CHARACTERISTICS                 |                                                         |     |     |       |

| Cobo                 | Output Capacitance                   | V <sub>CB</sub> = 10 V, I <sub>E</sub> = 0, f = 1MHz    |     | 30  | pF    |

| f <sub>T</sub>       | Transition Frequency                 | I <sub>C</sub> = 50 mA,V <sub>CE</sub> = 10 V, f=100MHz | 100 |     | -     |

\*Pulse Test: Pulse Width  $\leq 300~\mu s,~Duty~Cycle \leq 2.0\%$

**July 1998**

# **FSB660 / FSB660A**

SuperSOT<sup>™</sup>-3 (SOT-23)

# **PNP Low Saturation Transistor**

These devices are designed with high current gain and low saturation voltage with collector currents up to 2A continuous.

# **Absolute Maximum Ratings\*** $T_{A=25^{\circ}\text{C unless otherwise noted}}$

| Symbol                            | Parameter                                        | FSB660/FSB660A | Units |

|-----------------------------------|--------------------------------------------------|----------------|-------|

| V <sub>CEO</sub>                  | Collector-Emitter Voltage                        | 60             | V     |

| V <sub>CBO</sub>                  | Collector-Base Voltage                           | 80             | V     |

| V <sub>EBO</sub>                  | Emitter-Base Voltage                             | 5              | V     |

| Ic                                | Collector Current - Continuous                   | 2              | Α     |

| T <sub>J</sub> , T <sub>stg</sub> | Operating and Storage Junction Temperature Range | -55 to +150    | °C    |

<sup>\*</sup>These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.

#### NOTES:

- 1) These ratings are based on a maximum junction temperature of 150°C.

- 2) These are steady state limits. The factory should be consulted on applications involving pulsed or low duty cycle operations.

# Thermal Characteristics T<sub>A = 25°C unless otherwise noted</sub>

| Symbol          | Characteristic                          | Max            | Units |

|-----------------|-----------------------------------------|----------------|-------|

|                 |                                         | FSB660/FSB660A |       |

| P <sub>D</sub>  | Total Device Dissipation                | 500            | mW    |

| $R_{\theta JA}$ | Thermal Resistance, Junction to Ambient | 250            | °C/W  |

| PNP Lov (continued)  | w Saturation Transistor                            |                                                            |     |      |       |

|----------------------|----------------------------------------------------|------------------------------------------------------------|-----|------|-------|

| Electrica            | al Characteristics T <sub>A = 25°C unless ot</sub> | herwise noted                                              |     |      |       |

| Symbol               | Parameter                                          | Test Conditions                                            | Min | Max  | Units |

| OFF CHAI             | RACTERISTICS                                       |                                                            |     |      |       |

| BV <sub>CEO</sub>    | Collector-Emitter Breakdown Voltage                | I <sub>C</sub> = 10 mA                                     | 60  |      | V     |

| BV <sub>CBO</sub>    | Collector-Base Breakdown Voltage                   | I <sub>C</sub> = 100 μA                                    | 80  |      | V     |

| BV <sub>EBO</sub>    | Emitter-Base Breakdown Voltage                     | I <sub>E</sub> = 100 μA                                    | 5   |      | V     |

| I <sub>CBO</sub>     | Collector Cutoff Current                           | V <sub>CB</sub> = 30 V                                     |     | 100  | nA    |

|                      |                                                    | V <sub>CB</sub> = 30 V, T <sub>A</sub> =100°C              |     | 10   | uA    |

| I <sub>EBO</sub>     | Emitter Cutoff Current                             | V <sub>EB</sub> = 4V                                       |     | 100  | nA    |

| ON CHAR              | ACTERISTICS*                                       |                                                            |     |      |       |

| h <sub>FE</sub>      | DC Current Gain                                    | I <sub>C</sub> = 100 mA, V <sub>CE</sub> = 2 V             | 70  |      | -     |

|                      |                                                    | I <sub>C</sub> =500mA, V <sub>CE</sub> =2V <b>FSB660</b>   | 100 | 300  |       |

|                      |                                                    | FSB660A                                                    | 250 | 550  |       |

|                      |                                                    | I <sub>C</sub> = 1 A, V <sub>CE</sub> = 2 V                | 80  |      |       |

|                      |                                                    | $I_C = 2 A, V_{CE} = 2 V$                                  | 40  |      |       |

| V <sub>CE(sat)</sub> | Collector-Emitter Saturation Voltage               | I <sub>C</sub> = 1 A, I <sub>B</sub> = 100 mA              |     | 300  | mV    |

| , ,                  |                                                    | I <sub>C</sub> = 2 A, I <sub>B</sub> =200 mA <b>FSB660</b> |     | 350  |       |

|                      |                                                    | FSB660A                                                    |     | 300  |       |

| V <sub>BE(sat)</sub> | Base-Emitter Saturation Voltage                    | I <sub>C</sub> = 1 A, I <sub>B</sub> = 100 mA              |     | 1.25 | V     |

| V <sub>BE(on)</sub>  | Base-Emitter On Voltage                            | I <sub>C</sub> = 1 A, V <sub>CE</sub> = 2 V                |     | 1    | V     |

## **SMALL SIGNAL CHARACTERISTICS**

| C <sub>obo</sub> | Output Capacitance   | V <sub>CB</sub> = 10 V, I <sub>E</sub> = 0, f = 1MHz    |    | 30 | pF |

|------------------|----------------------|---------------------------------------------------------|----|----|----|

| f <sub>T</sub>   | Transition Frequency | I <sub>C</sub> = 100 mA,V <sub>CE</sub> = 5 V, f=100MHz | 75 |    | -  |

\*Pulse Test: Pulse Width  $\leq 300~\mu s,~Duty~Cycle \leq 2.0\%$

# **Typical Characteristics**

# **SSOT-3 Embossed Carrier Tape**

Configuration: Figure 3.0

|                 | Dimensions are in millimeter |                 |               |                 |                   |                 |             |                 |               |               |                 |                   |               |               |

|-----------------|------------------------------|-----------------|---------------|-----------------|-------------------|-----------------|-------------|-----------------|---------------|---------------|-----------------|-------------------|---------------|---------------|

| Pkg type        | A0                           | В0              | w             | D0              | D1                | E1              | E2          | F               | P1            | P0            | K0              | т                 | Wc            | Тс            |

| SSOT-3<br>(8mm) | 3.15<br>+/-0.10              | 2.77<br>+/-0.10 | 8.0<br>+/-0.3 | 1.55<br>+/-0.05 | 1.125<br>+/-0.125 | 1.75<br>+/-0.10 | 6.25<br>min | 3.50<br>+/-0.05 | 4.0<br>+/-0.1 | 4.0<br>+/-0.1 | 1.30<br>+/-0.10 | 0.228<br>+/-0.013 | 5.2<br>+/-0.3 | 0.06<br>+/-02 |

Notes: A0, B0, and K0 dimensions are determined with respect to the EIA/Jedec RS-481 rotational and lateral movement requirements (see sketches A, B, and C).

Sketch A (Side or Front Sectional View)

Component Rotation

Sketch B (Top View)

Component Rotation

Sketch C (Top View)

Component lateral movement

DETAIL AA

## SSOT-3 Reel Configuration: Figure 4.0

|           | Dimensions are in inches and millimeters |               |              |                                   |               |             |                                   |               |                             |

|-----------|------------------------------------------|---------------|--------------|-----------------------------------|---------------|-------------|-----------------------------------|---------------|-----------------------------|

| Tape Size | Reel<br>Option                           | Dim A         | Dim B        | Dim C                             | Dim D         | Dim N       | Dim W1                            | Dim W2        | Dim W3 (LSL-USL)            |

| 8mm       | 7" Dia                                   | 7.00<br>177.8 | 0.059<br>1.5 | 512 +0.020/-0.008<br>13 +0.5/-0.2 | 0.795<br>20.2 | 2.165<br>55 | 0.331 +0.059/-0.000<br>8.4 +1.5/0 | 0.567<br>14.4 | 0.311 - 0.429<br>7.9 - 10.9 |

| 8mm       | 13" Dia                                  | 13.00<br>330  | 0.059<br>1.5 | 512 +0.020/-0.008<br>13 +0.5/-0.2 | 0.795<br>20.2 | 4.00<br>100 | 0.331 +0.059/-0.000<br>8.4 +1.5/0 | 0.567<br>14.4 | 0.311 - 0.429<br>7.9 - 10.9 |

# SuperSOT™-3 Tape and Reel Data and Package Dimensions, continued

# SuperSOT™-3 (FS PKG Code 32)

Scale 1:1 on letter size paper

Dimensions shown below are in:

inches [millimeters]

Part Weight per unit (gram): 0.0097

LAND PATTERN RECOMMENDATION

NOTES: UNLESS OTHERWISE SPECIFIED

SUPER SOT , 3 LEADS

- 1. STANDARD LEAD FINISH TO BE 150 MICROINCHES / 3.81 MICROMETERS MINIMUM TIN/LEAD (SOLDER) ON COPPER.

- 2. NO JEDEC REGISTRATION AS OF DEC. 1995.

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

CROSSVOLT<sup>TM</sup> POP<sup>TM</sup>

E<sup>2</sup>CMOS<sup>™</sup> PowerTrench<sup>™</sup>

FACT<sup>TM</sup> QS<sup>TM</sup>

FACT Quiet Series TM Quiet Series TM SuperSOT TM-3 SuperSOT TM-6 GTO TM SuperSOT TM-8 TinyLogic TM TinyLogic TM

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |

# **FSB6726**

$\textbf{SuperSOT}^{\text{TM}}\textbf{-3}$

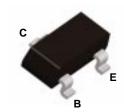

# **PNP General Purpose Amplifier**

This device is designed for general purpose medium power amplifiers and switches requiring collector currents to 1.0 A. Sourced from Process 77.

# **Absolute Maximum Ratings\*** $T_{A=25^{\circ}\text{C unless otherwise noted}}$

| Symbol                            | Parameter                                        | FSB660/FSB660A | Units |

|-----------------------------------|--------------------------------------------------|----------------|-------|

| V <sub>CEO</sub>                  | Collector-Emitter Voltage                        | 30             | V     |

| V <sub>CBO</sub>                  | Collector-Base Voltage                           | 40             | V     |

| V <sub>EBO</sub>                  | Emitter-Base Voltage                             | 5              | V     |

| Ic                                | Collector Current - Continuous                   | 1.5            | А     |

| T <sub>J</sub> , T <sub>stg</sub> | Operating and Storage Junction Temperature Range | -55 to +150    | °C    |

<sup>\*</sup>These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.

#### NOTES:

- 1) These ratings are based on a maximum junction temperature of 150°C.

- 2) These are steady state limits. The factory should be consulted on applications involving pulsed or low duty cycle operations.

# Thermal Characteristics $T_{A=25^{\circ}\text{C unless otherwise noted}}$

| Symbol           | Characteristic                          | Max     | Units |

|------------------|-----------------------------------------|---------|-------|

|                  |                                         | FSB6726 |       |

| P <sub>D</sub>   | Total Device Dissipation                | 500     | mW    |

| R <sub>θJA</sub> | Thermal Resistance, Junction to Ambient | 250     | °C/W  |

# **PNP General Purpose Amplifier**

(continued)

# **Electrical Characteristics**

$T_{\text{A}\,=\,25^{\circ}\text{C}\,\text{unless otherwise noted}}$

| Symbol               | Parameter                            | Test Conditions                                       | Min | Max | Units |

|----------------------|--------------------------------------|-------------------------------------------------------|-----|-----|-------|

| OFF CHA              | RACTERISTICS                         |                                                       |     | •   |       |

| BV <sub>CEO</sub>    | Collector-Emitter Breakdown Voltage  | I <sub>C</sub> = 10 mA                                | 30  |     | V     |

| BV <sub>CBO</sub>    | Collector-Base Breakdown Voltage     | Ι <sub>C</sub> = 100 μΑ                               | 40  |     | V     |

| BV <sub>EBO</sub>    | Emitter-Base Breakdown Voltage       | I <sub>E</sub> = 100 μA                               | 5   |     | V     |

| I <sub>CBO</sub>     | Collector Cutoff Current             | V <sub>CB</sub> = 40 V                                |     | 100 | nA    |

| I <sub>EBO</sub>     | Emitter Cutoff Current               | V <sub>EB</sub> = 5V                                  |     | 100 | nA    |

| ON CHAR              | ACTERISTICS*                         |                                                       | •   |     |       |

| h <sub>FE</sub>      | DC Current Gain                      | I <sub>C</sub> = 100 mA, V <sub>CE</sub> = 1 V        | 60  |     | -     |

|                      |                                      | $I_C = 1 A$ , $V_{CE} = 1V$                           | 50  | 250 | -     |

| V <sub>CE(sat)</sub> | Collector-Emitter Saturation Voltage | I <sub>C</sub> = 1 A, I <sub>B</sub> = 100 mA         |     | 500 | mV    |

| V <sub>BE(on)</sub>  | Base-Emitter On Voltage              | I <sub>C</sub> = 1 A, V <sub>CE</sub> = 1 V           |     | 1.2 | V     |

| SMALL S              | IGNAL CHARACTERISTICS                |                                                       |     |     |       |

| C <sub>cb</sub>      | Collector-Base Capacitance           | V <sub>CB</sub> = 10 V, f = 1MHz                      |     | 30  | pF    |

| hfe                  | Small Signal Current Gain            | I <sub>C</sub> = 50 mA,V <sub>CE</sub> = 10V, f=20MHz | 2.5 | 25  | -     |

\*Pulse Test: Pulse Width  $\leq$  300  $\mu$ s, Duty Cycle  $\leq$  2.0%

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

CROSSVOLT<sup>TM</sup> POP<sup>TM</sup>

E<sup>2</sup>CMOS<sup>™</sup> PowerTrench<sup>™</sup>

FACT<sup>TM</sup> QS<sup>TM</sup>

FACT Quiet Series TM Quiet Series TM SuperSOT TM-3 SuperSOT TM-6 GTO TM SuperSOT TM-8 TinyLogic TM TinyLogic TM

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |

## Discrete POWER & Signal **Technologies**

# FSBCW30

SuperSOT™-3

# **PNP General Purpose Amplifier**

This device is designed for general purpose medium power amplifiers and switches requiring collector currents to 300 mA. Sourced from Process 68. See BC857A for characteristics.

# **Absolute Maximum Ratings\***

TA = 25°C unless otherwise noted

| Symbol                            | Parameter                                        | Value       | Units |

|-----------------------------------|--------------------------------------------------|-------------|-------|

| $V_{CEO}$                         | Collector-Emitter Voltage                        | 32          | V     |

| V <sub>CBO</sub>                  | Collector-Base Voltage                           | 32          | V     |

| V <sub>EBO</sub>                  | Emitter-Base Voltage                             | 5.0         | V     |

| I <sub>C</sub>                    | Collector Current - Continuous                   | 500         | mA    |

| T <sub>J</sub> , T <sub>stg</sub> | Operating and Storage Junction Temperature Range | -55 to +150 | °C    |

<sup>\*</sup>These ratings are limiting values above which the serviceability of any semiconductor device may be impaired.

#### **Thermal Characteristics** TA = 25°C unless otherwise noted

| Symbol          | Characteristic                          | Max     | Units |

|-----------------|-----------------------------------------|---------|-------|

|                 |                                         | FSBCW30 |       |

| P <sub>D</sub>  | Total Device Dissipation                | 500     | mW    |

|                 | Derate above 25°C                       | 4       | mW/°C |

| $R_{\theta JA}$ | Thermal Resistance, Junction to Ambient | 250     | °C/W  |

<sup>\*</sup>Device mounted on FR-4 PCB 4.5" x 5"; mounting pad  $0.02\,\mathrm{in^2}$  of  $2\mathrm{oz}$  copper.

These ratings are based on a maximum junction temperature of 150 degrees C.

These are steady state limits. The factory should be consulted on applications involving pulsed or low duty cycle operations.

# PNP General Purpose Amplifier (continued)

| Symbol            | Parameter                              | Test Conditions                                                                                                       | Min         | Max       | Units    |

|-------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------|-----------|----------|

| OFF CHA           | RACTERISTICS                           |                                                                                                                       |             |           |          |

| BV <sub>CEO</sub> | Collector-Emitter Breakdown<br>Voltage | $I_C = 2.0 \text{ mA}, I_B = 0$                                                                                       | 32          |           | V        |

| BV <sub>CBO</sub> | Collector-Base Breakdown Voltage       | $I_C = 10  \mu A, I_E = 0$                                                                                            | 32          |           | V        |

| BV <sub>CES</sub> | Collector-Emitter Breakdown<br>Voltage | $I_C = 10 \mu A, I_E = 0$                                                                                             | 32          |           | V        |

| BV <sub>EBO</sub> | Emitter-Base Breakdown Voltage         | I <sub>E</sub> = 10 μA, I <sub>C</sub> = 0                                                                            | 5.0         |           | V        |

| Ісво              | Collector-Cutoff Current               | V <sub>CB</sub> = 32 V, I <sub>E</sub> = 0<br>V <sub>CB</sub> = 32 V, I <sub>E</sub> = 0, T <sub>A</sub> = +100<br>°C |             | 100<br>10 | nA<br>μA |

|                   | •                                      |                                                                                                                       | •           |           | •        |

| ON CHAR           | ACTERISTICS                            |                                                                                                                       |             |           |          |

| ON CHAR           | ACTERISTICS DC Current Gain            | V <sub>CE</sub> = 5.0 V, I <sub>C</sub> = 2.0 mA                                                                      | 215         | 500       |          |

| h <sub>FE</sub>   |                                        | $V_{CE} = 5.0 \text{ V}, I_{C} = 2.0 \text{ mA}$ $I_{C} = 10 \text{ mA}, I_{B} = 0.5 \text{ mA}$                      | 215         | 500       | V        |

|                   | DC Current Gain                        | , ,                                                                                                                   | 215<br>0.60 |           | V        |

## **PNP General Purpose Amplifier**

(continued)

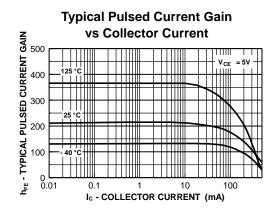

## **Typical Characteristics**

# **PNP General Purpose Amplifier**

(continued)

# Typical Characteristics (continued)

# Input and Output Capacitance vs Reverse Voltage

Gain Bandwidth Product

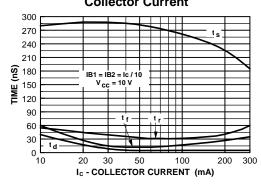

Switching Times vs Collector Current

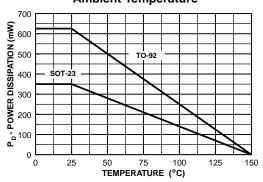

Power Dissipation vs Ambient Temperature

#### **TRADEMARKS**

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEX<sup>TM</sup> ISOPLANAR<sup>TM</sup> COOIFET<sup>TM</sup> MICROWIRE<sup>TM</sup>

CROSSVOLT<sup>TM</sup> POP<sup>TM</sup>

E<sup>2</sup>CMOS<sup>™</sup> PowerTrench<sup>™</sup>

FACT<sup>TM</sup> QS<sup>TM</sup>

$\begin{array}{lll} \text{FACT Quiet Series}^{\text{TM}} & \text{Quiet Series}^{\text{TM}} \\ \text{FAST}^{\text{®}} & \text{SuperSOT}^{\text{TM}}\text{-3} \\ \text{FASTr}^{\text{TM}} & \text{SuperSOT}^{\text{TM}}\text{-6} \\ \text{GTO}^{\text{TM}} & \text{SuperSOT}^{\text{TM}}\text{-8} \\ \text{HiSeC}^{\text{TM}} & \text{TinyLogic}^{\text{TM}} \\ \end{array}$

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **PRODUCT STATUS DEFINITIONS**

#### **Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                            |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                                    |

| Preliminary              | First Production          | This datasheet contains preliminary data, and supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.                                                       |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor. The datasheet is printed for reference information only.                                                   |

September 1997 Revised December 1999

# FST16209 18-Bit Bus Exchange Switch

## **General Description**

The Fairchild Switch FST16209 provides 18-bits of highspeed CMOS TTL-compatible bus switching or exchanging. The low on resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise.

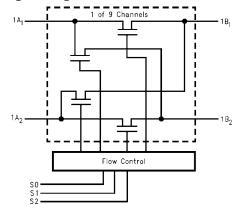

The device operates as a 18-bit bus switch or a 9-bit bus exchanger, which allows data exchange between the four signal ports via the data-select terminals.

#### **Features**

- $\blacksquare$  4 $\Omega$  switch connection between two ports.

- Minimal propagation delay through the switch.

- Low I<sub>CC</sub>.

- Zero bounce in flow-through mode.

- Control inputs compatible with TTL level.

## **Ordering Code:**

| ľ | Order Number | Package Number | Package Description                                                         |

|---|--------------|----------------|-----------------------------------------------------------------------------|

| - | FST16209MEA  | MS48A          | 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300 Wide       |

| - | FST16209MTD  | MTD48          | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

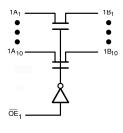

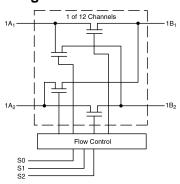

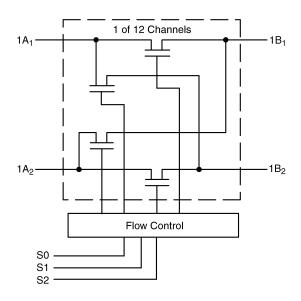

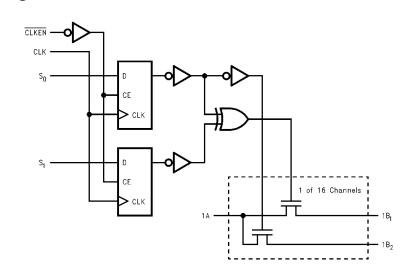

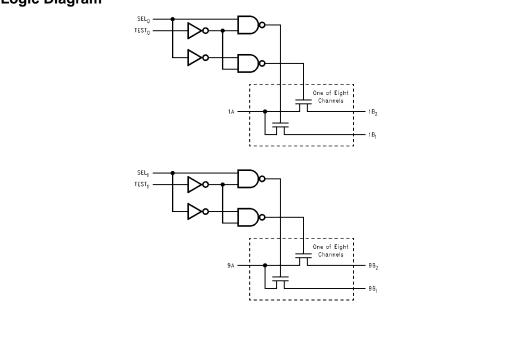

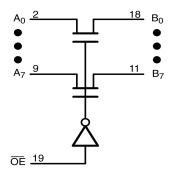

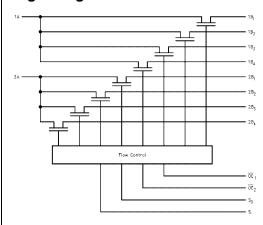

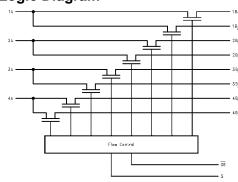

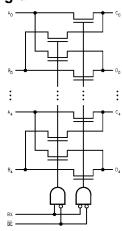

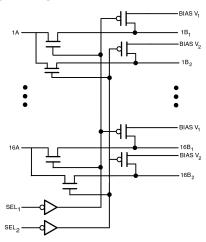

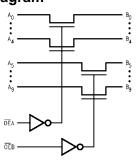

## **Logic Diagram**

### **Truth Table**

| S2 | S1 | S0 | A <sub>1</sub> | A <sub>2</sub> | Function               |

|----|----|----|----------------|----------------|------------------------|

| L  | L  | L  | Z              | Z              | Disconnect             |

| L  | L  | Н  | B <sub>1</sub> | Z              | $A_1 = B_1$            |

| L  | Н  | L  | B <sub>2</sub> | Z              | $A_1 = B_2$            |

| L  | Н  | Н  | Z              | $B_1$          | $A_2 = B_1$            |

| Н  | L  | L  | Z              | $B_2$          | $A_2 = B_2$            |

| Н  | L  | Н  | Z              | Z              | Disconnect             |

| Н  | Н  | L  | B <sub>1</sub> | $B_2$          | $A_1 = B_1, A_2 = B_2$ |

| Н  | Н  | Н  | B <sub>2</sub> | $B_1$          | $A_1 = B_2, A_2 = B_1$ |

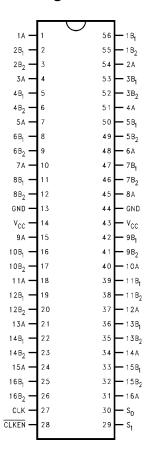

# **Connection Diagram**

## **Pin Descriptions**

| Pin Name                        | Description        |

|---------------------------------|--------------------|

| S2, S1, S0                      | Data-select inputs |

| A <sub>1</sub> , A <sub>2</sub> | Bus A              |

| B <sub>1</sub> , B <sub>2</sub> | Bus B              |

## Absolute Maximum Ratings(Note 1)

| Supply Voltage (V <sub>CC</sub> )                                    | -0.5V to +7.0V   |

|----------------------------------------------------------------------|------------------|

| DC Switch Voltage (V <sub>S</sub> )                                  | -0.5V to $+7.0V$ |

| DC Input Voltage (V <sub>IN</sub> )(Note 2)                          | -0.5V to $+7.0V$ |

| DC Input Diode Current (I <sub>IK</sub> ) V <sub>IN</sub> <0V        | -50mA            |

| DC Output (I <sub>OUT</sub> ) Sink Current                           | 128mA            |

| DC V <sub>CC</sub> /GND Current (I <sub>CC</sub> /I <sub>GND</sub> ) | +/- 100mA        |

| Storage Temperature Range (T <sub>STG</sub> )                        | -65°C to +150 °C |

# Recommended Operating Conditions (Note 3)

$\begin{array}{ll} \mbox{Power Supply Operating ($V_{CC}$)} & 4.0 \mbox{V to } 5.5 \mbox{V} \\ \mbox{Input Voltage ($V_{IN}$)} & 0 \mbox{V to } 5.5 \mbox{V} \\ \mbox{Output Voltage ($V_{OUT}$)} & 0 \mbox{V to } 5.5 \mbox{V} \\ \end{array}$

Input Rise and Fall Time (t<sub>r</sub>, t<sub>f</sub>)

Switch Control Input 0nS/V to 5nS/V Switch I/O 0nS/V to DC Free Air Operating Temperature ( $T_A$ ) -40 °C to +85 °C

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

**Note 2:** The input and output negative voltage ratings may be exceeded if the input and output diode current ratings are observed.

Note 3: Unused control inputs must be held HIGH or LOW. They may not float.

#### **DC Electrical Characteristics**

|                   |                                       | $V_{CC}$ $T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C}$ |     |                 |      |       |                                         |

|-------------------|---------------------------------------|----------------------------------------------------------------|-----|-----------------|------|-------|-----------------------------------------|

| Symbol            | Parameter                             | (V)                                                            | Min | Typ<br>(Note 4) | Max  | Units | Conditions                              |

| V <sub>IK</sub>   | Clamp Diode Voltage                   | 4.5                                                            |     |                 | -1.2 | V     | $I_{IN} = -18mA$                        |

| V <sub>IH</sub>   | HIGH Level Input Voltage              | 4.0-5.5                                                        | 2.0 |                 |      | V     |                                         |

| V <sub>IL</sub>   | LOW Level Input Voltage               | 4.0-5.5                                                        |     |                 | 0.8  | V     |                                         |

| I <sub>I</sub>    | Input Leakage Current                 | 5.5                                                            |     |                 | ±1.0 | μΑ    | $0 \le V_{IN} \le 5.5V$                 |

|                   |                                       | 0                                                              |     |                 | 10   | μΑ    | $V_{IN} = 5.5V$                         |

| I <sub>OFF</sub>  | OFF-STATE Leakage Current             | 5.5                                                            |     |                 | ±1.0 | μΑ    | $0 \le A, B \le V_{CC}$                 |

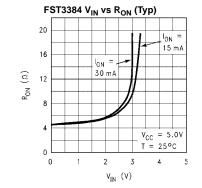

| R <sub>ON</sub>   | Switch On Resistance                  | 4.5                                                            |     | 4               | 7    | Ω     | $V_{IN} = 0V$ , $I_{IN} = 64mA$         |

|                   | (Note 5)                              | 4.5                                                            |     | 4               | 7    | Ω     | $V_{IN} = 0V, I_{IN} = 30mA$            |

|                   |                                       | 4.5                                                            |     | 8               | 12   | Ω     | $V_{IN} = 2.4V, I_{IN} = 15mA$          |

|                   |                                       | 4.0                                                            |     | 14              | 20   | Ω     | $V_{IN} = 2.4V, I_{IN} = 15mA$          |

| I <sub>CC</sub>   | Quiescent Supply Current              | 5.5                                                            |     |                 | 3    | μА    | $V_{IN} = V_{CC}$ or GND, $I_{OUT} = 0$ |

| Δ I <sub>CC</sub> | Increase in I <sub>CC</sub> per Input | 5.5                                                            |     |                 | 2.5  | mA    | One input at 3.4V                       |

|                   |                                       |                                                                |     |                 |      |       | Other inputs at V <sub>CC</sub> or GND  |

Note 4: Typical values are at  $V_{CC} = 5.0V$  and  $T_A = +25^{\circ}C$

Note 5: Measured by the voltage drop between A and B pins at the indicated current through the switch. On resistance is determined by the lower of the voltages on the two (A or B) pins.

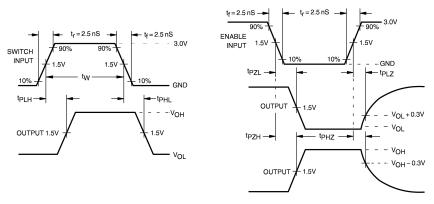

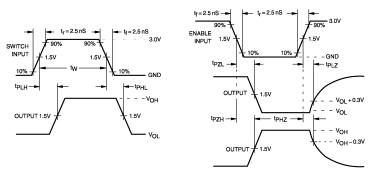

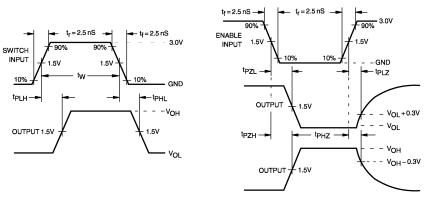

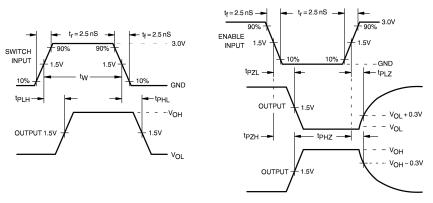

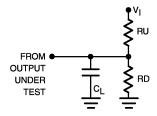

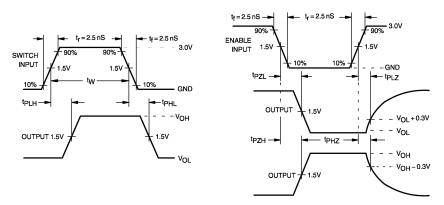

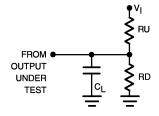

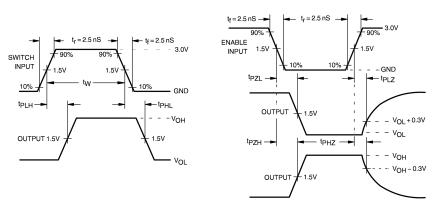

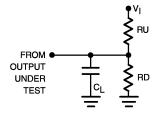

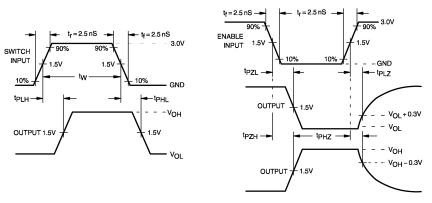

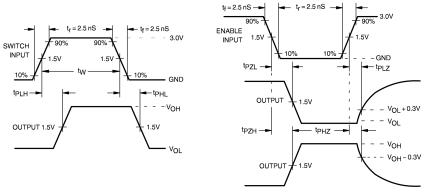

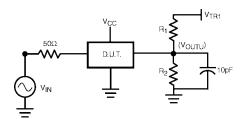

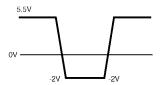

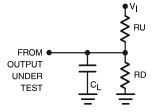

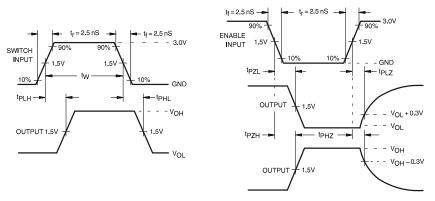

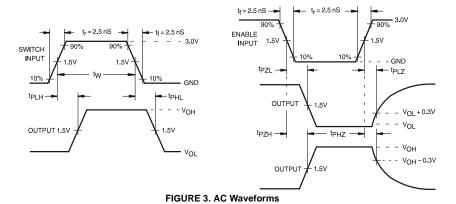

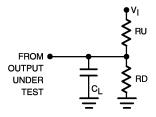

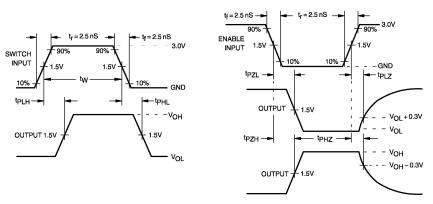

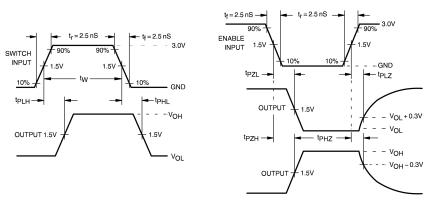

## **AC Electrical Characteristics**

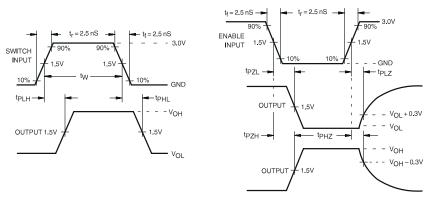

| Symbol                              | Parameter                       |                      | T <sub>A</sub> = -40 °C<br>_ = 50pF, R <sub>L</sub> |                   |        | Units | Conditions                                             | Figure No.           |

|-------------------------------------|---------------------------------|----------------------|-----------------------------------------------------|-------------------|--------|-------|--------------------------------------------------------|----------------------|

| Symbol                              | Faranietei                      | V <sub>CC</sub> = 4. | .5 – 5.5V                                           | V <sub>CC</sub> = | = 4.0V | Units | Conditions                                             | rigure No.           |

|                                     |                                 | Min                  | Max                                                 | Min               | Max    |       |                                                        |                      |

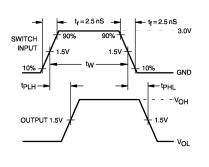

| t <sub>PHL</sub> , t <sub>PLH</sub> | Prop Delay Bus to Bus (Note 6)  |                      | 0.25                                                |                   | 0.25   | ns    | V <sub>I</sub> = OPEN                                  | Figure 1<br>Figure 2 |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Prop Delay S to Bus             | 1.5                  | 7.0                                                 |                   | 7.0    | ns    | V <sub>I</sub> = OPEN                                  | Figure 1<br>Figure 2 |

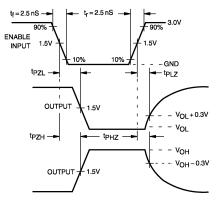

| t <sub>PZH</sub> , t <sub>PZL</sub> | Output Enable Time, S to A or B | 1.5                  | 7.5                                                 |                   | 8.0    | ns    | $V_I = 7V$ for $t_{PZL}$<br>$V_I = OPEN$ for $t_{PZH}$ | Figure 1<br>Figure 2 |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Output Disable Time S to A or B | 1.0                  | 8.5                                                 |                   | 9.0    | ns    | $V_I = 7V$ for $t_{PLZ}$<br>$V_I = OPEN$ for $t_{PHZ}$ | Figure 1<br>Figure 2 |

Note 6: This parameter is guaranteed by design but is not tested. The bus switch contributes no propagation delay other than the RC delay of the typical On resistance of the switch and the 50pF load capacitance, when driven by an ideal voltage source (zero output impedance).

## Capacitance (Note 7)

| Symbol           | Parameter                     | Тур | Max | Units | Conditions              |

|------------------|-------------------------------|-----|-----|-------|-------------------------|

| C <sub>IN</sub>  | Control pin Input Capacitance | 3   |     | pF    | V <sub>CC</sub> = 5.0V  |

| C <sub>I/O</sub> | Input/Output Capacitance      | 10  |     | pF    | V <sub>CC</sub> = 5.0V, |

|                  |                               |     |     |       | S0, S1, and S2 = GND    |

Note 7: T<sub>A</sub> = +25°C, f = 1 MHz, Capacitance is characterized but not tested.

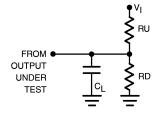

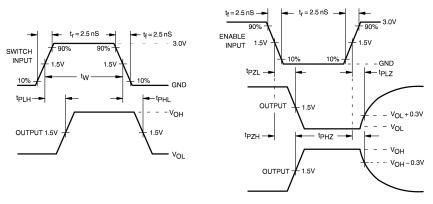

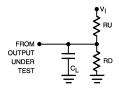

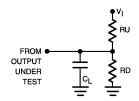

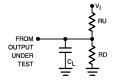

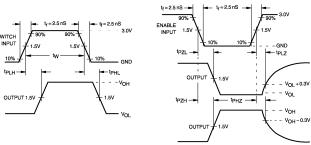

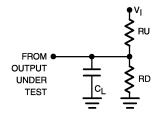

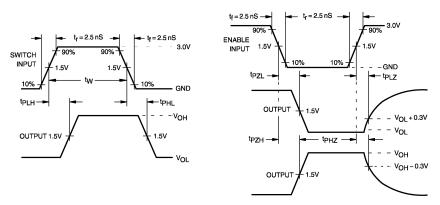

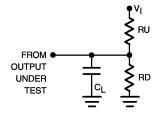

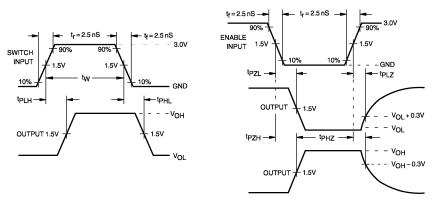

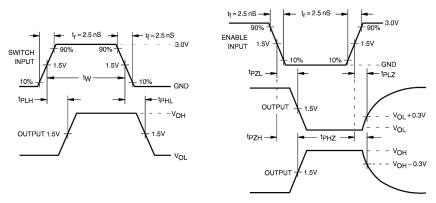

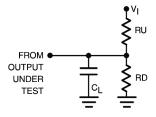

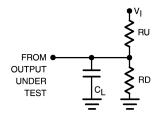

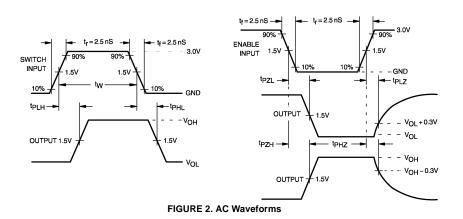

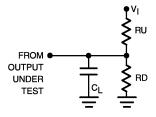

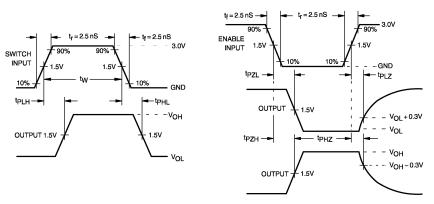

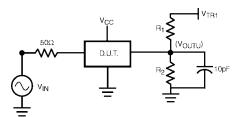

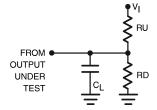

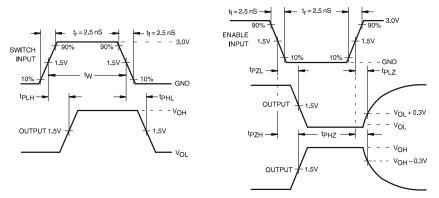

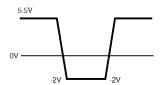

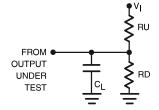

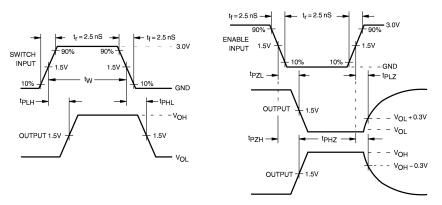

# **AC Loading and Waveforms**

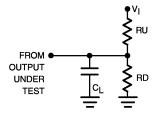

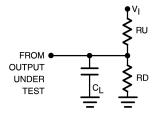

Note: Input driven by 50  $\Omega$  source terminated in 50  $\Omega$  Note: C\_L includes load and stray capacitance

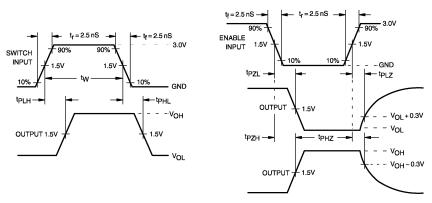

Note: Input PRR = 1.0 MHz,  $t_W$  = 500 ns

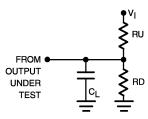

### FIGURE 1. AC Test Circuit

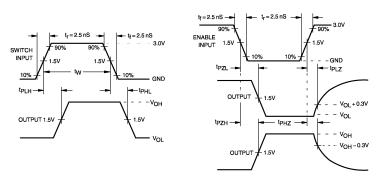

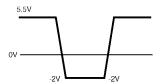

FIGURE 2. AC Waveforms

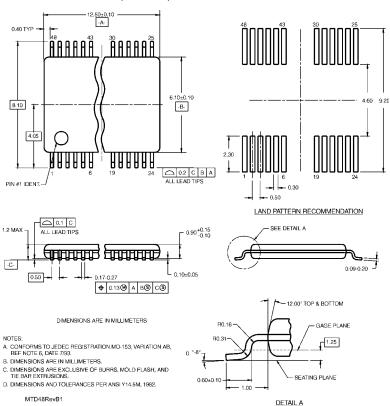

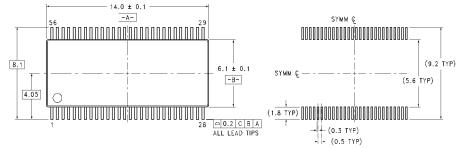

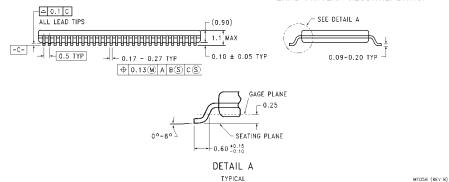

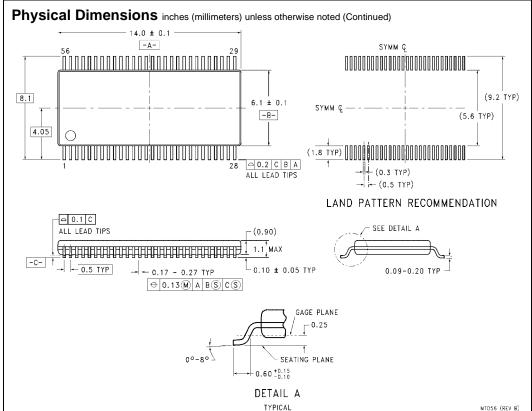

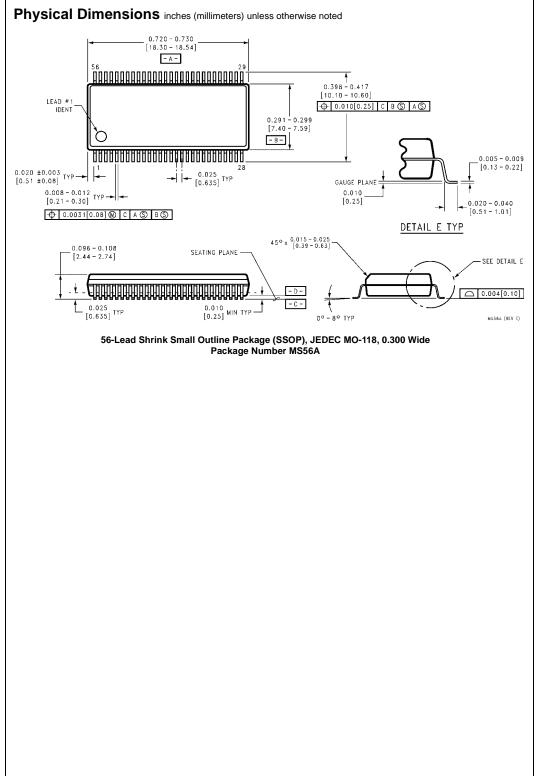

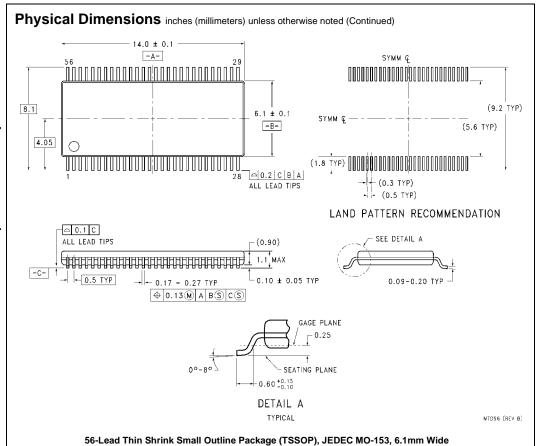

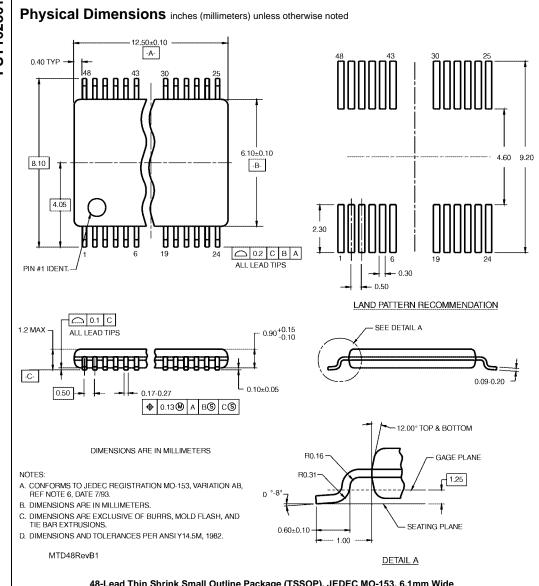

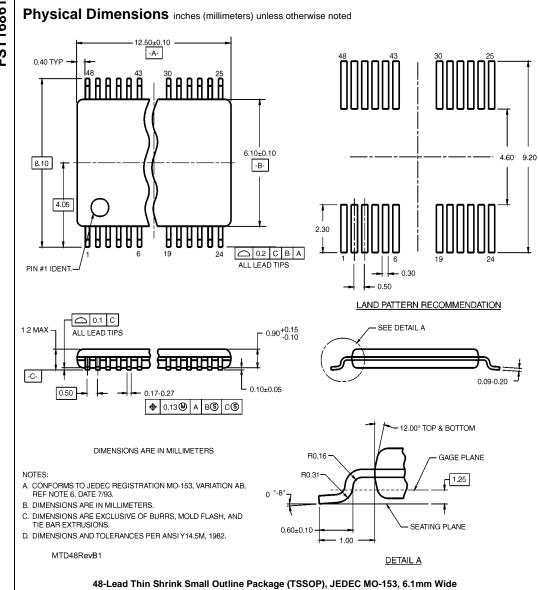

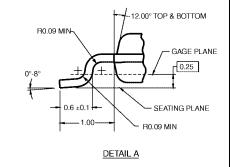

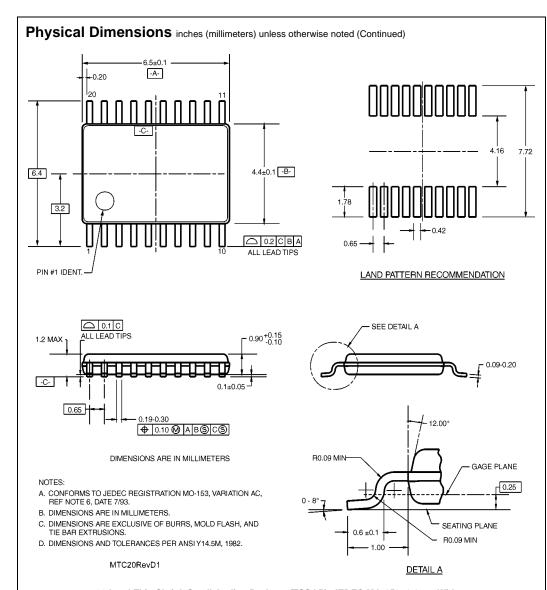

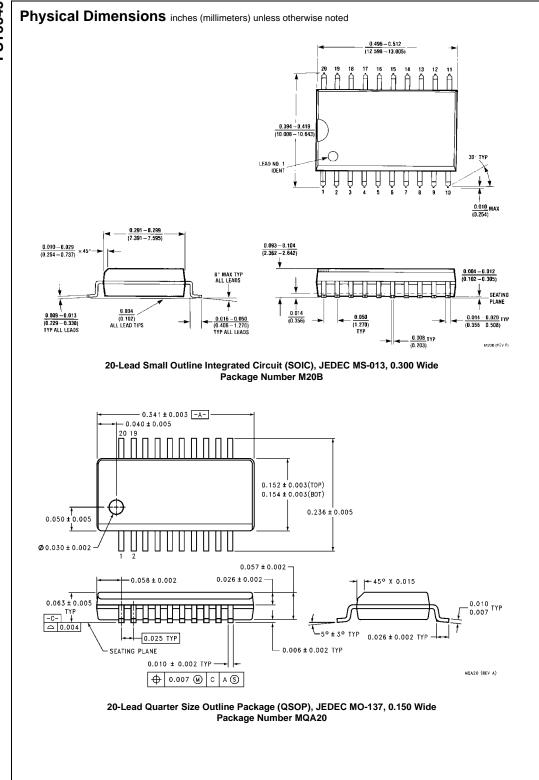

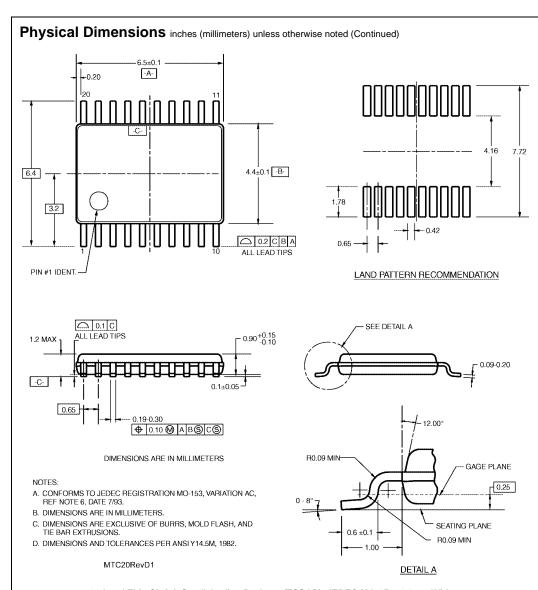

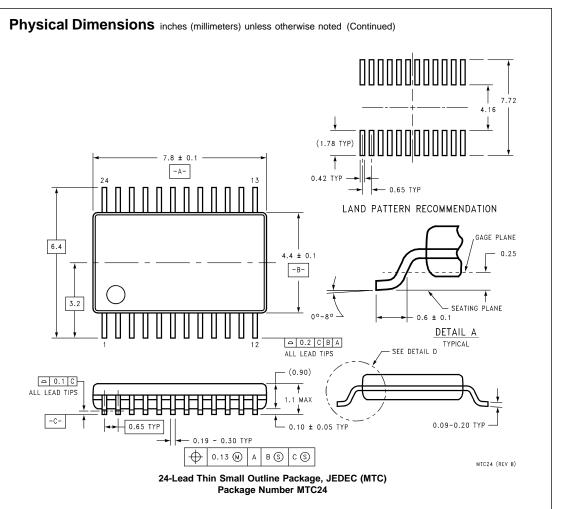

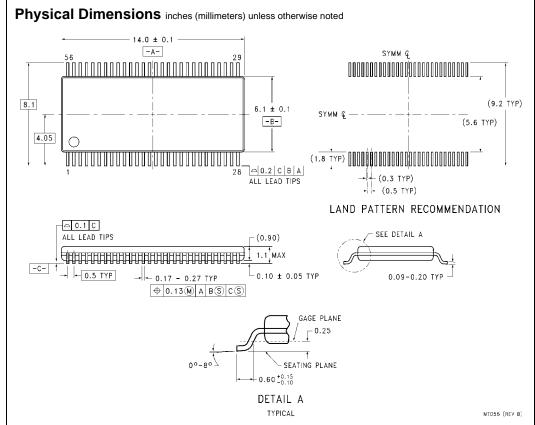

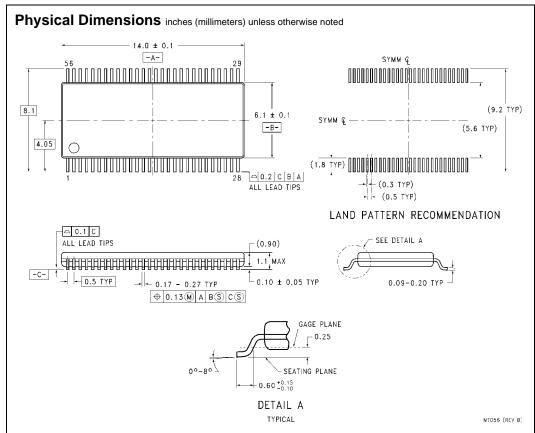

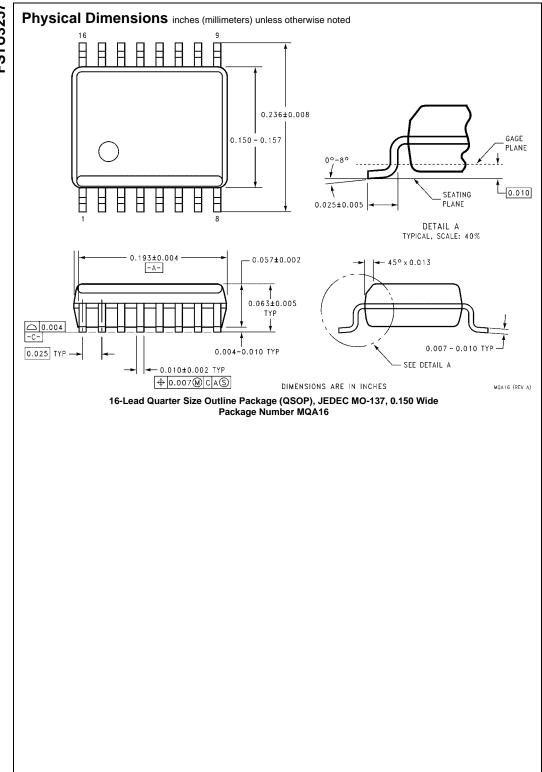

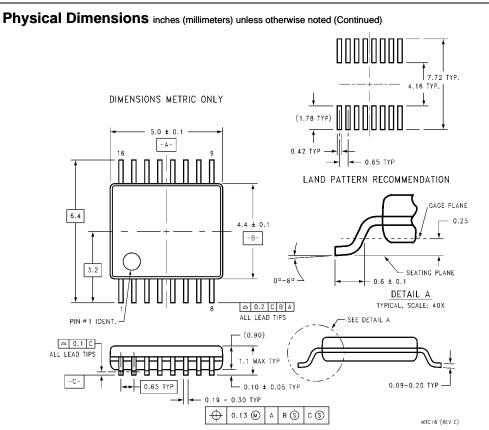

## Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 0.40 TYP ĤAAAAĤ 9.20 8.10 -В-0.2 C B A PIN #1 IDENT - 0.30 0.50 LAND PATTERN RECOMMENDATION 0.1 C SEE DETAIL A 0.90+0.15 0.09-0.20 0.50 Ф 0.13 W A BS CS - 12.00° TOP & BOTTOM DIMENSIONS ARE IN MILLIMETERS R0.16 NOTES: NOTES: A CONFORMS TO JEDEC REGISTRATION MO-153, VARIATION AB, REF NOTE 6, DATE 7/93. B. DIMENSIONS ARE IN MILLIMETERS. C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS. SEATING PLANE

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide Package Number MTD48

0.60±0.10

### **Technology Description**

MTD48RevB1

D. DIMENSIONS AND TOLERANCES PER ANSI Y14.5M, 1982.

The Fairchild Switch family derives from and embodies Fairchild's proven switch technology used for several years in its 74LVX3L384 (FST3384) bus switch product.

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

November 1998 Revised December 1999

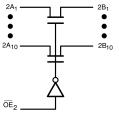

# FST16210 20-Bit Bus Switch

## **General Description**

The Fairchild Switch FST16210 provides 20-Bits of highspeed CMOS TTL-compatible bus switching. The low on resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise.

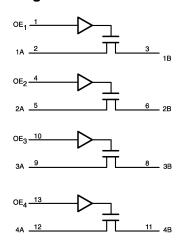

The device is organized as a 10-bit or 20-Bit bus switch. When  $\overline{OE}_1$  is LOW, the switch is ON and Port 1A is connected to Port 1B. When  $\overline{OE}_2$  is LOW, Port 2A is connected to Port 2B

#### **Features**

- $\blacksquare$  4 $\Omega$  switch connection between two ports.

- Minimal propagation delay through the switch.

- Low I<sub>CC</sub>.

- Zero bounce in flow-through mode.

- Control inputs compatible with TTL level.

# **Ordering Code:**

| Order Number | Package Number | Package Description                                                         |

|--------------|----------------|-----------------------------------------------------------------------------|

| FST16210MTD  | MTD48          | 48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

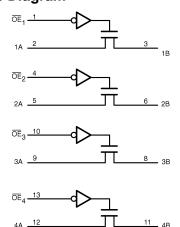

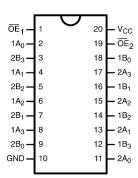

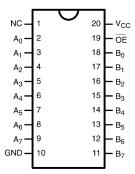

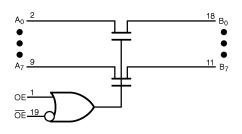

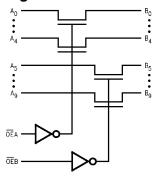

## **Connection Diagram**

## **Pin Descriptions**

| Pin Name                           | Description        |

|------------------------------------|--------------------|

| $\overline{OE}_1, \overline{OE}_2$ | Bus Switch Enables |

| 1A, 2A                             | Bus A              |

| 1B, 2B                             | Bus B              |

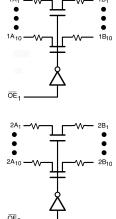

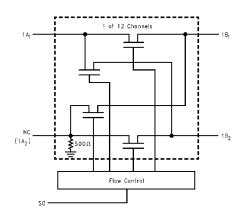

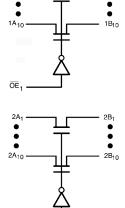

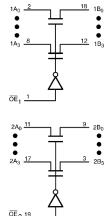

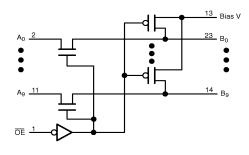

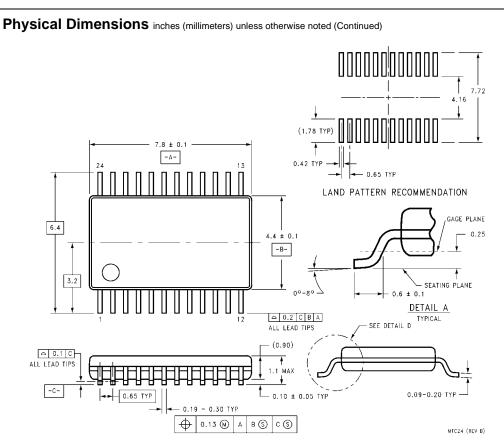

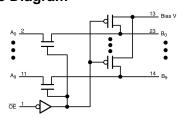

### **Logic Diagram**

### **Truth Table**

| Inputs          |                 | Inputs/Outputs |         |  |

|-----------------|-----------------|----------------|---------|--|

| OE <sub>1</sub> | OE <sub>2</sub> | 1A, 1B         | 2A, 2B  |  |

| L               | L               | 1A = 1B        | 2A = 2B |  |

| L               | Н               | 1A = 1B        | Z       |  |

| Н               | L               | Z              | 2A = 2B |  |

| Н               | Н               | Z              | Z       |  |

## Absolute Maximum Ratings(Note 1)

| Supply Voltage (V <sub>CC</sub> )                                    | -0.5V to +7.0V   |

|----------------------------------------------------------------------|------------------|

| DC Switch Voltage (V <sub>S</sub> )                                  | -0.5V to +7.0V   |

| DC Input Voltage (V <sub>IN</sub> ) (Note 2)                         | -0.5V to +7.0V   |

| DC Input Diode Current ( $I_{IK}$ ) $V_{IN}$ <0V                     | –50mA            |

| DC Output (I <sub>OUT</sub> ) Sink Current                           | 128mA            |

| DC V <sub>CC</sub> /GND Current (I <sub>CC</sub> /I <sub>GND</sub> ) | +/- 100mA        |

| Storage Temperature Range (Texa)                                     | -65°C to +150 °C |

# Recommended Operating Conditions (Note 3)

$\begin{array}{ll} \mbox{Power Supply Operating ($V_{CC}$)} & 4.0 \mbox{V to } 5.5 \mbox{V} \\ \mbox{Input Voltage ($V_{IN}$)} & 0 \mbox{V to } 5.5 \mbox{V} \\ \mbox{Output Voltage ($V_{OUT}$)} & 0 \mbox{V to } 5.5 \mbox{V} \\ \end{array}$

Input Rise and Fall Time (t<sub>r</sub>, t<sub>f</sub>)

Switch Control Input 0nS/V to 5nS/V Switch I/O 0nS/V to DC Free Air Operating Temperature ( $T_A$ ) -40 °C to +85 °C

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

**Note 2:** The input and output negative voltage ratings may be exceeded if the input and output diode current ratings are observed.

Note 3: Unused control inputs must be held high or low. They may not float.

## **DC Electrical Characteristics**

|                  |                                       | V <sub>CC</sub> | $T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}$ |                 |      |       |                                                |  |

|------------------|---------------------------------------|-----------------|---------------------------------------------------------------|-----------------|------|-------|------------------------------------------------|--|

| Symbol           | Parameter                             | (V)             | Min                                                           | Typ<br>(Note 4) | Max  | Units | Conditions                                     |  |

| V <sub>IK</sub>  | Clamp Diode Voltage                   | 4.5             |                                                               |                 | -1.2 | V     | I <sub>IN</sub> = -18mA                        |  |

| V <sub>IH</sub>  | HIGH Level Input Voltage              | 4.0-5.5         | 2.0                                                           |                 |      | V     |                                                |  |

| V <sub>IL</sub>  | LOW Level Input Voltage               | 4.0-5.5         |                                                               |                 | 0.8  | V     |                                                |  |

| II               | Input Leakage Current                 | 5.5             |                                                               |                 | ±1.0 | μΑ    | 0≤ V <sub>IN</sub> ≤5.5V                       |  |

|                  |                                       | 0               |                                                               |                 | 10   | μΑ    | V <sub>IN</sub> = 5.5V                         |  |

| I <sub>OZ</sub>  | OFF-STATE Leakage Current             | 5.5             |                                                               |                 | ±1.0 | μΑ    | 0 ≤A, B ≤V <sub>CC</sub>                       |  |

| R <sub>ON</sub>  | Switch On Resistance                  | 4.5             |                                                               | 4               | 7    | Ω     | V <sub>IN</sub> = 0V, I <sub>IN</sub> = 64mA   |  |

|                  | (Note 5)                              | 4.5             |                                                               | 4               | 7    | Ω     | V <sub>IN</sub> = 0V, I <sub>IN</sub> = 30mA   |  |

|                  |                                       | 4.5             |                                                               | 8               | 12   | Ω     | V <sub>IN</sub> = 2.4V, I <sub>IN</sub> = 15mA |  |

|                  |                                       | 4.0             |                                                               | 11              | 20   | Ω     | V <sub>IN</sub> = 2.4V, I <sub>IN</sub> = 15mA |  |

| I <sub>CC</sub>  | Quiescent Supply Current              | 5.5             |                                                               |                 | 3    | μΑ    | $V_{IN} = V_{CC}$ or GND, $I_{OUT} = 0$        |  |

| ΔI <sub>CC</sub> | Increase in I <sub>CC</sub> per Input | 5.5             |                                                               |                 | 2.5  | mA    | One input at 3.4V                              |  |

|                  |                                       |                 |                                                               |                 |      |       | Other inputs at V <sub>CC</sub> or GND         |  |

Note 4: Typical values are at V<sub>CC</sub> = 5.0V and T<sub>A</sub> = +25°C

Note 5: Measured by the voltage drop between A and B pins at the indicated current through the switch. On resistance is determined by the lower of the voltages on the two (A or B) pins.

## **AC Electrical Characteristics**

| Symbol                              | Parameter                      | $T_A = -40$ °C to +85 °C, $C_L = 50 pF$ , $RU = RD = 500 \Omega$ |      |                 |      | Units | Conditions                                             | Figure No.            |

|-------------------------------------|--------------------------------|------------------------------------------------------------------|------|-----------------|------|-------|--------------------------------------------------------|-----------------------|

| Symbol                              |                                | $V_{CC} = 4.5 - 5.5V$                                            |      | $V_{CC} = 4.0V$ |      | Units | Conditions                                             | rigule No.            |

|                                     |                                | Min                                                              | Max  | Min             | Max  | 1     |                                                        |                       |

| t <sub>PHL</sub> ,t <sub>PLH</sub>  | Prop Delay Bus to Bus (Note 6) |                                                                  | 0.25 |                 | 0.25 | ns    | V <sub>I</sub> = OPEN                                  | Figure 1,<br>Figure 2 |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Output Enable Time             | 1.5                                                              | 6.0  |                 | 6.5  | ns    | $V_I = 7V$ for $t_{PZL}$<br>$V_I = OPEN$ for $t_{PZH}$ | Figure 1,<br>Figure 2 |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Output Disable Time            | 1.5                                                              | 7.0  |                 | 7.2  | ns    | $V_I = 7V$ for $t_{PLZ}$<br>$V_I = OPEN$ for $t_{PHZ}$ | Figure 1,<br>Figure 2 |

Note 6: This parameter is guaranteed by design but is not tested. The bus switch contributes no propagation delay other than the RC delay of the typical On resistance of the switch and the 50pF load capacitance, when driven by an ideal voltage source (zero output impedance).

## Capacitance (Note 7)

| Symbol           | Parameter                     | Тур | Max | Units | Conditions                        |

|------------------|-------------------------------|-----|-----|-------|-----------------------------------|

| C <sub>IN</sub>  | Control pin Input Capacitance | 3   |     | pF    | V <sub>CC</sub> = 5.0V            |

| C <sub>I/O</sub> | Input/Output Capacitance      | 6   |     | pF    | $V_{CC}$ , $\overline{OE} = 5.0V$ |

Note 7: T<sub>A</sub> = +25°C, f = 1 MHz, Capacitance is characterized but not tested.

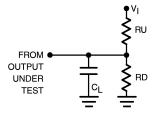

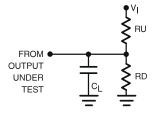

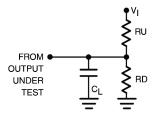

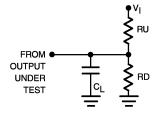

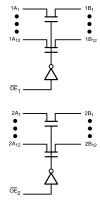

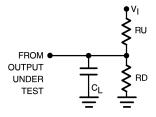

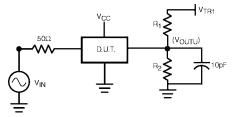

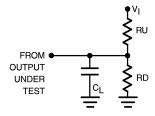

# **AC Loading and Waveforms**

Note: Input driven by 50  $\Omega$  source terminated in 50  $\Omega$  Note: C\_l includes load and stray capacitance

Note: Input PRR = 1.0 MHz,  $t_W = 500 \text{ ns}$

#### FIGURE 1. AC Test Circuit

FIGURE 2. AC Waveforms

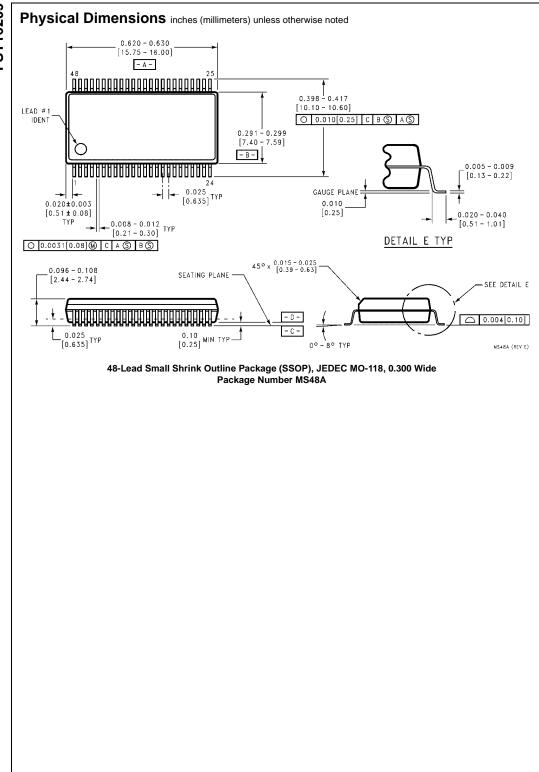

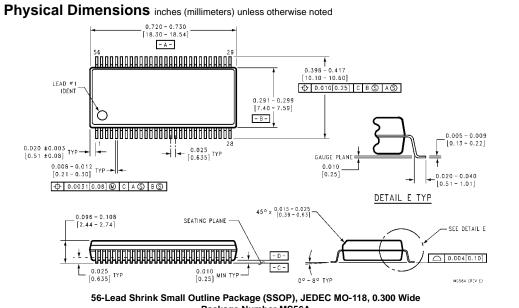

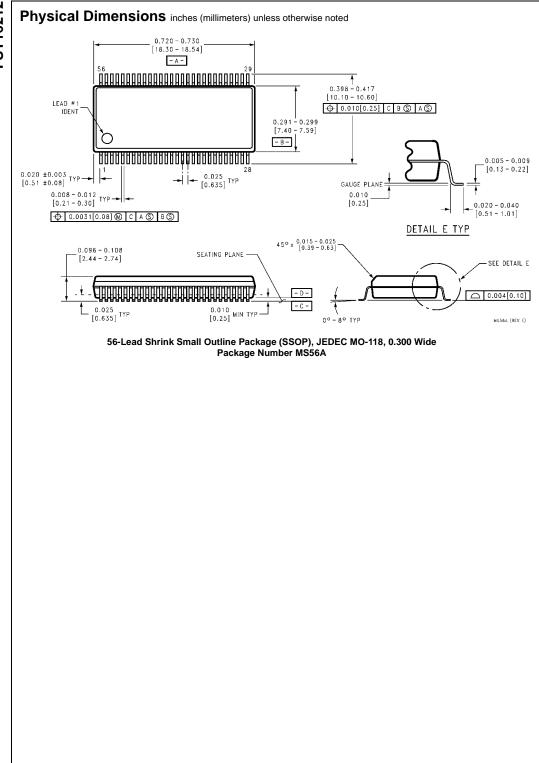

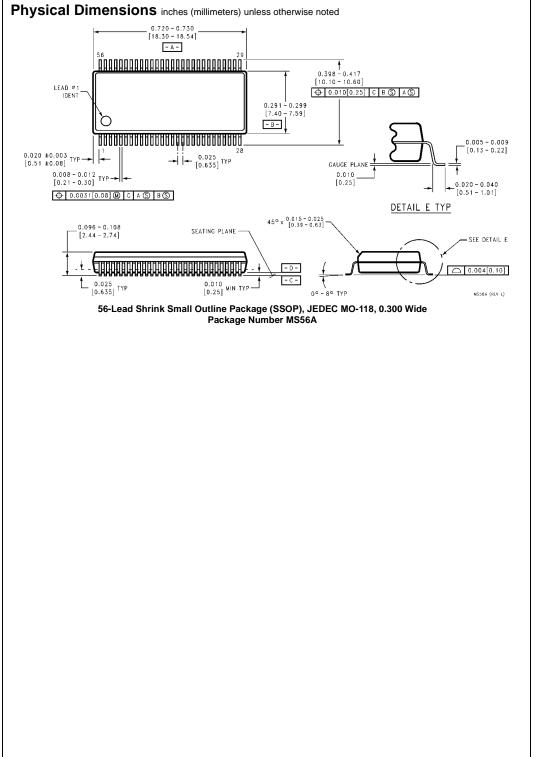

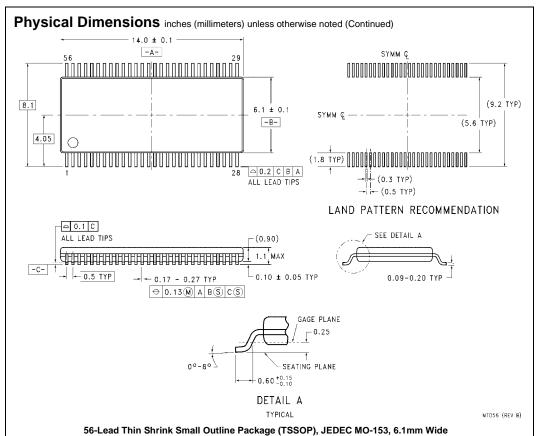

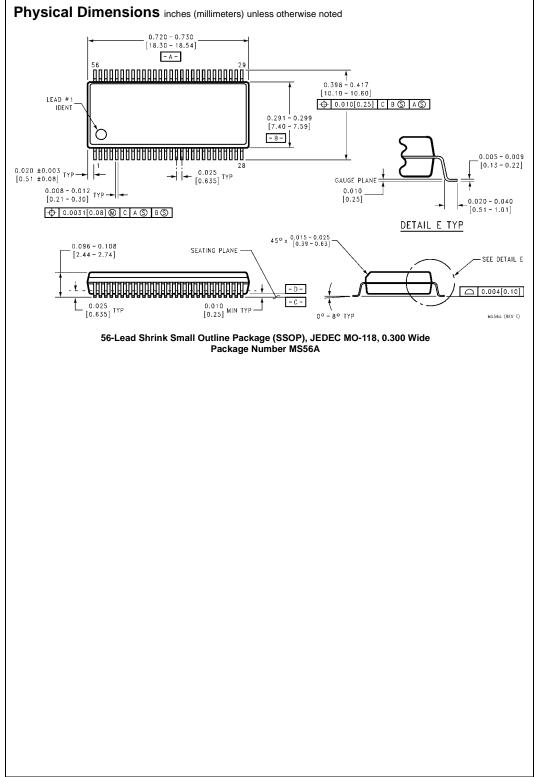

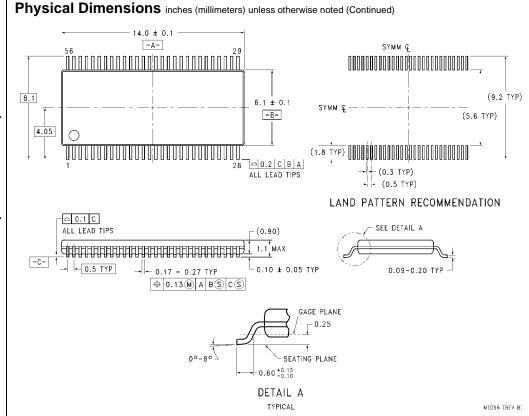

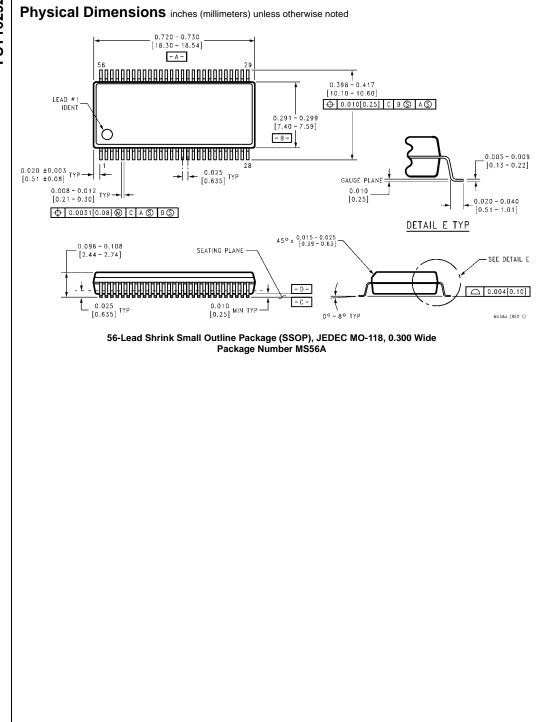

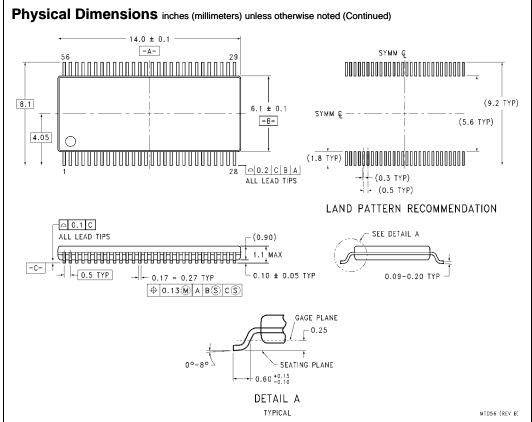

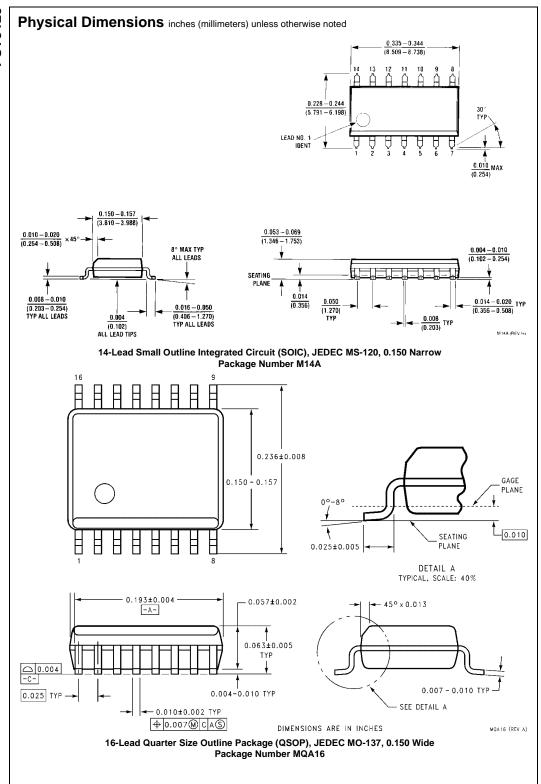

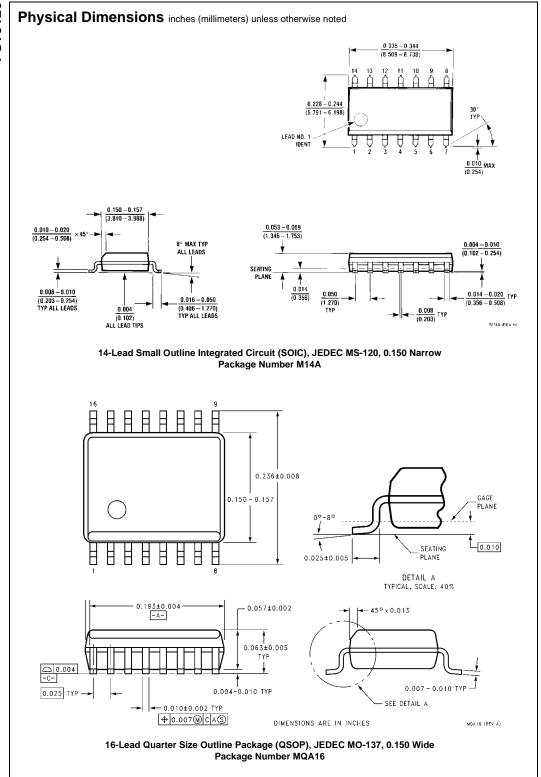

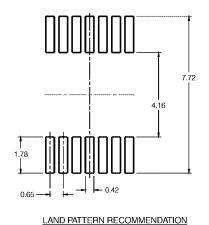

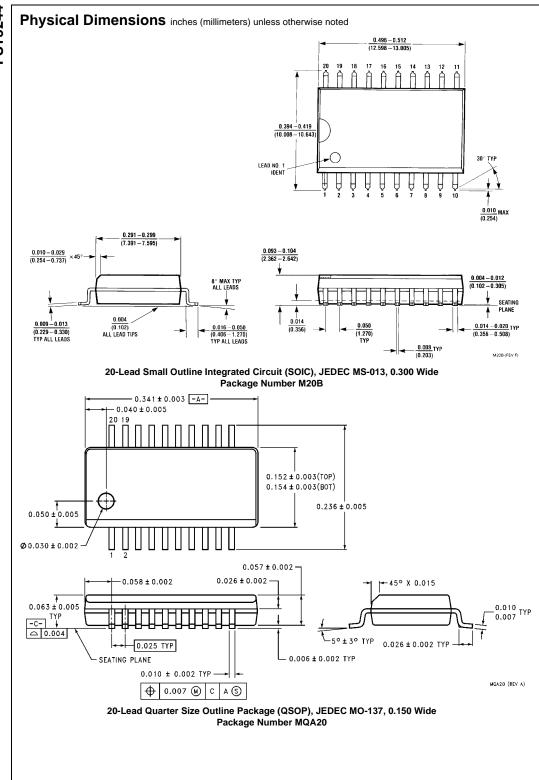

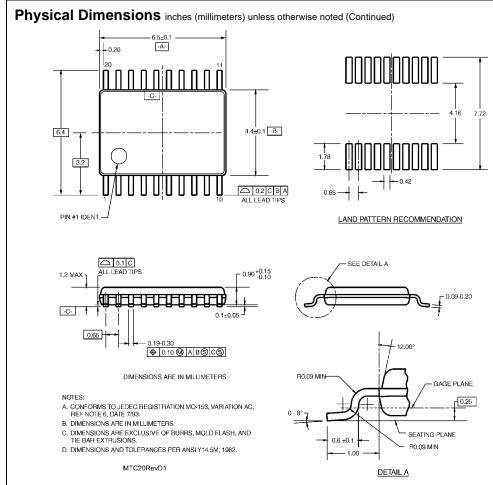

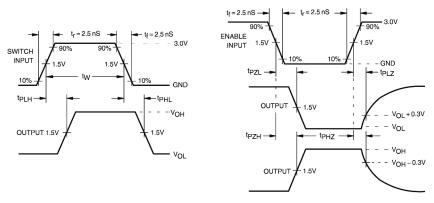

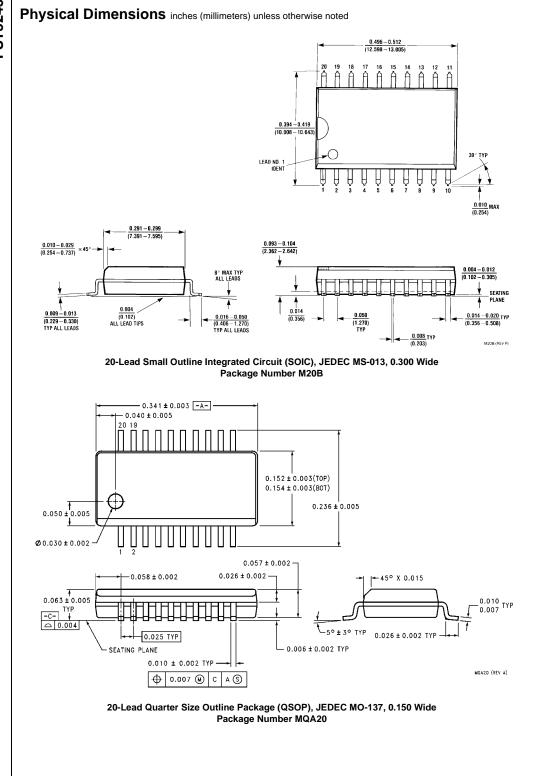

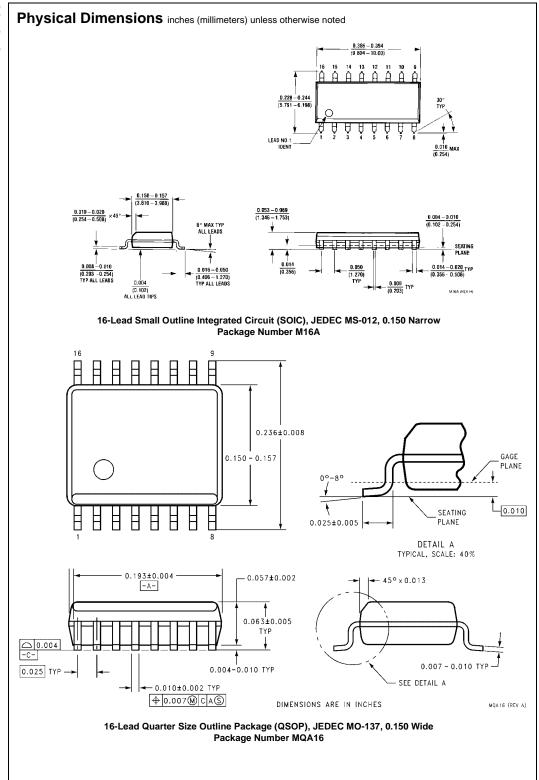

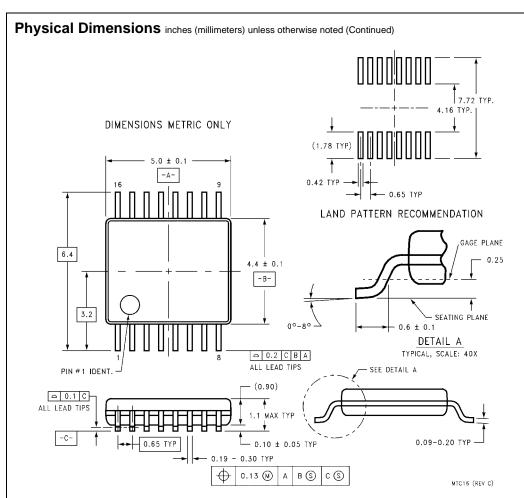

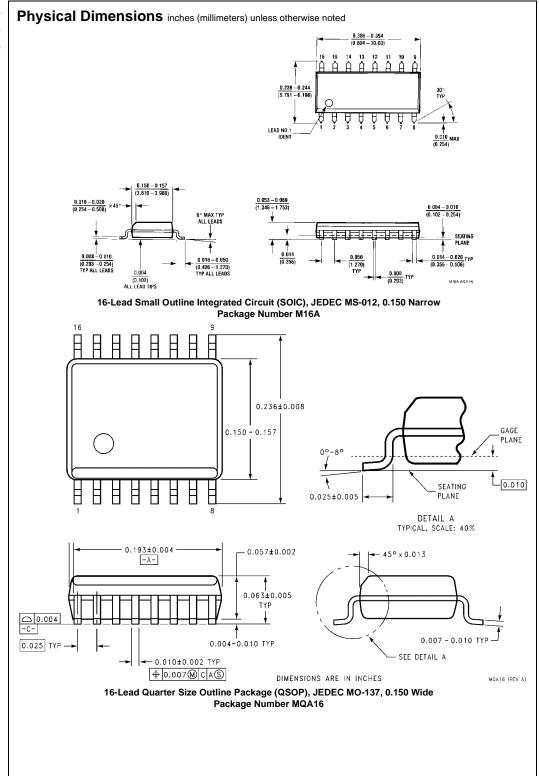

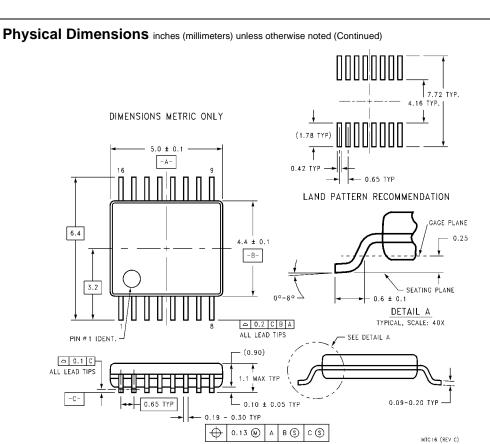

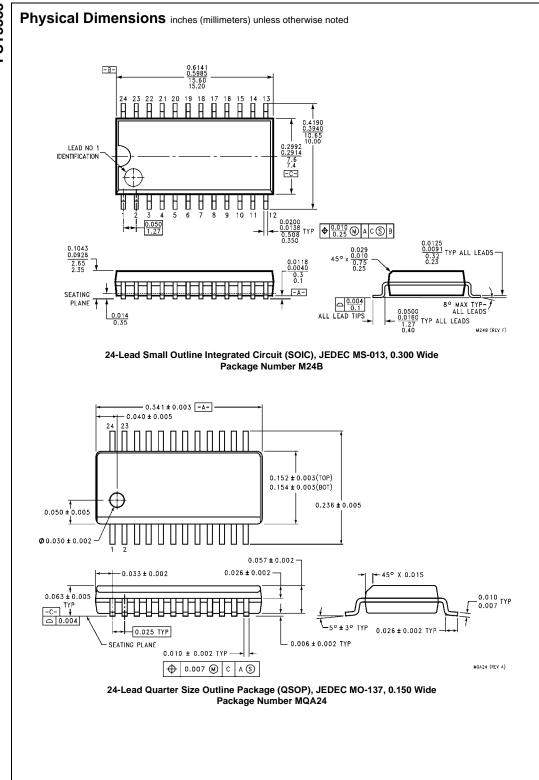

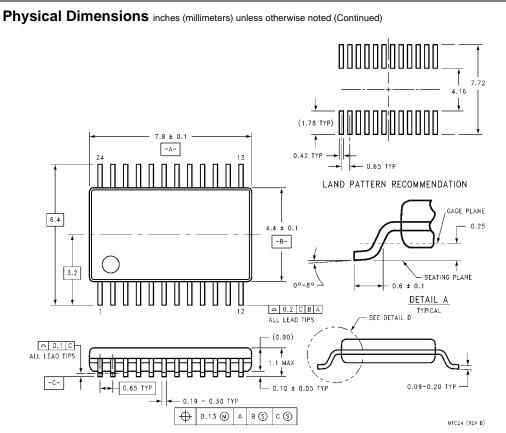

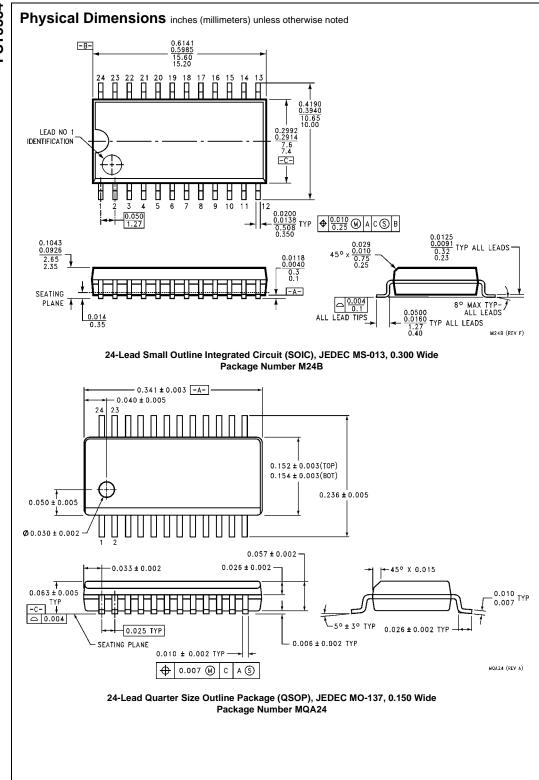

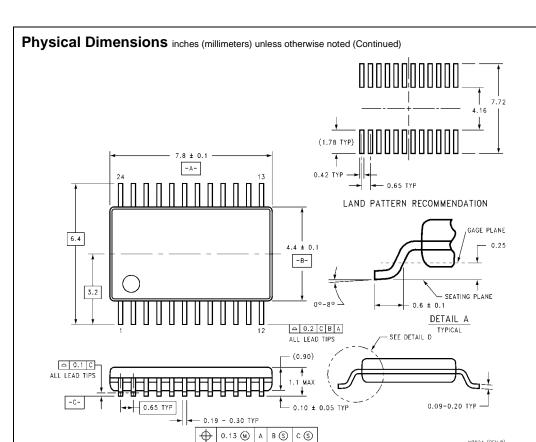

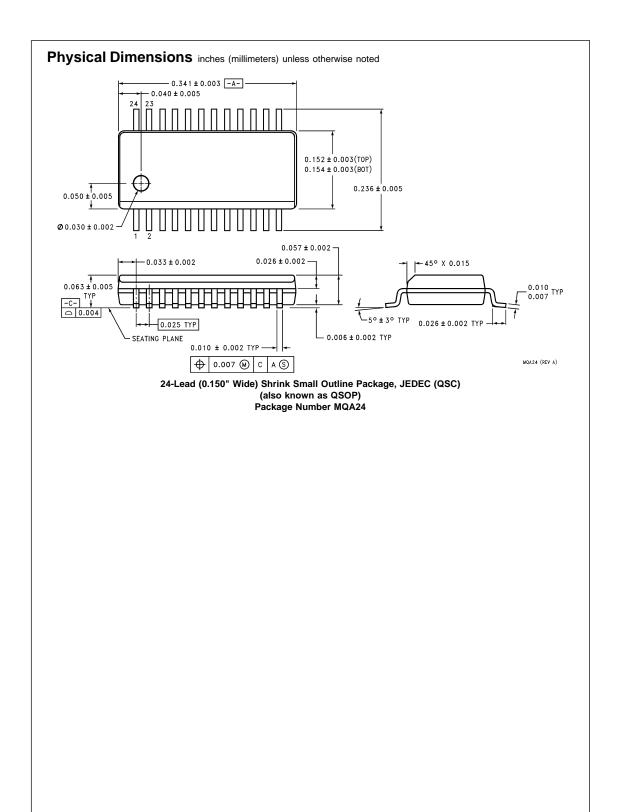

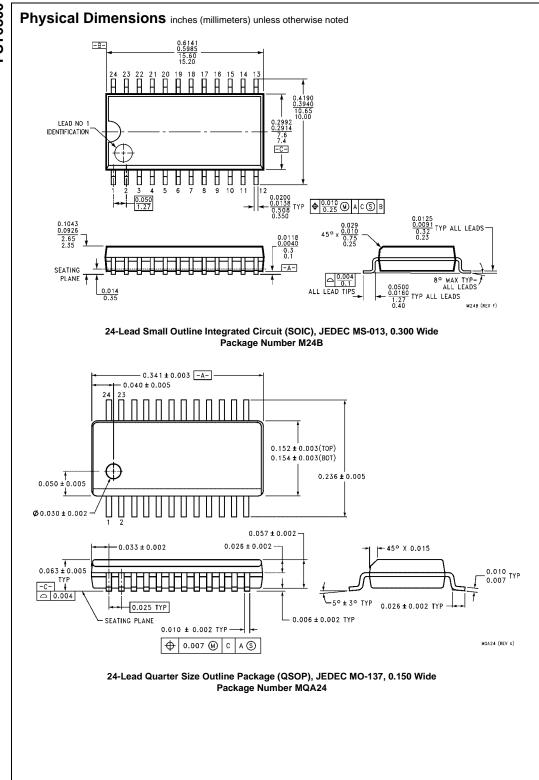

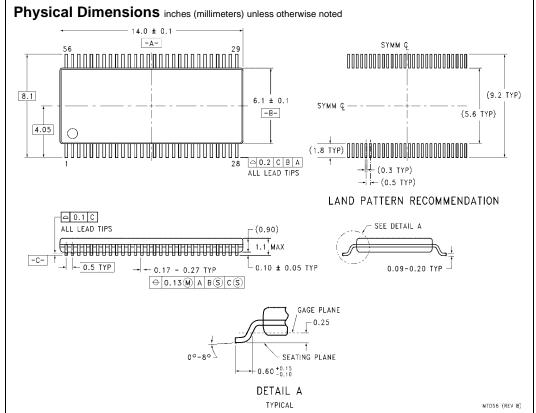

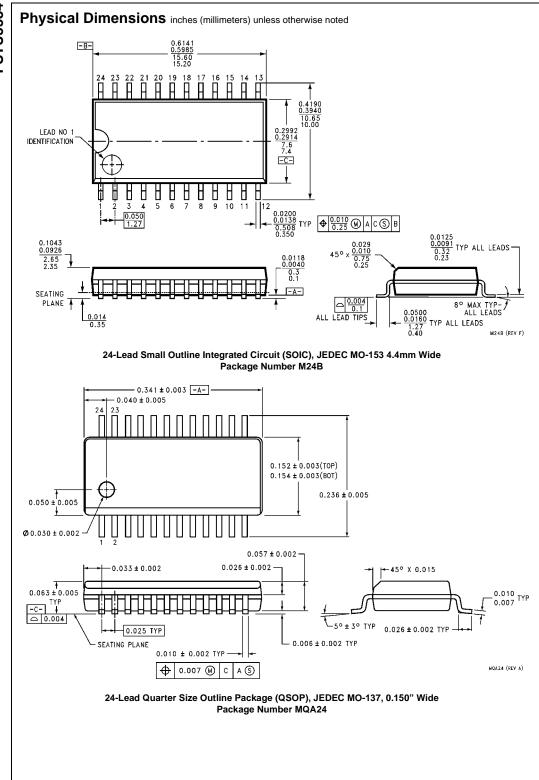

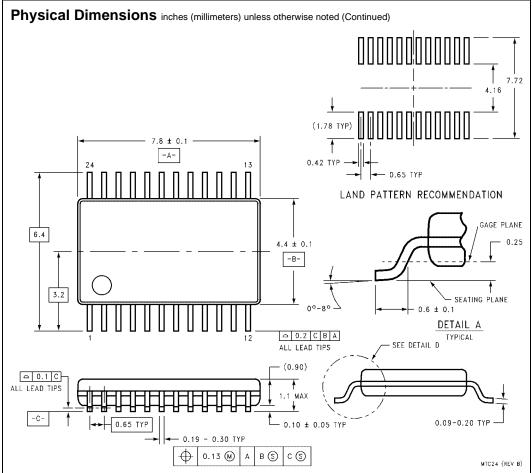

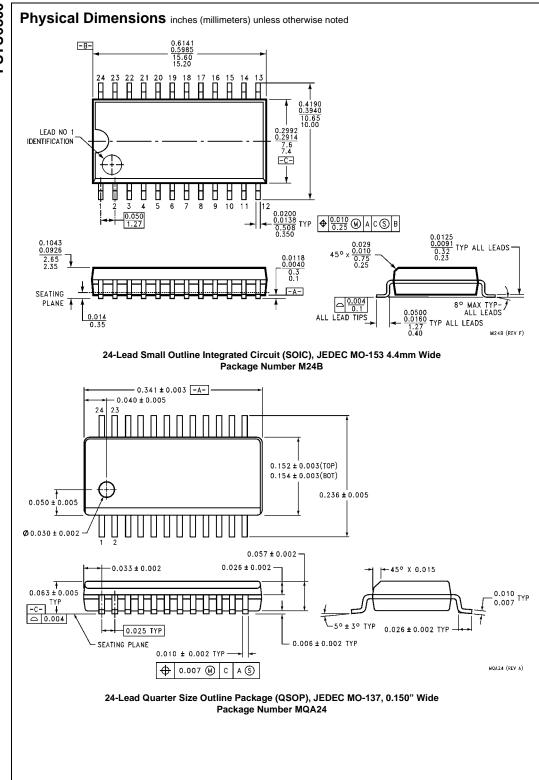

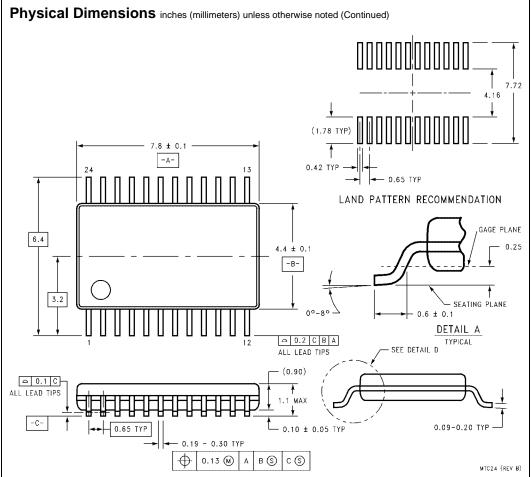

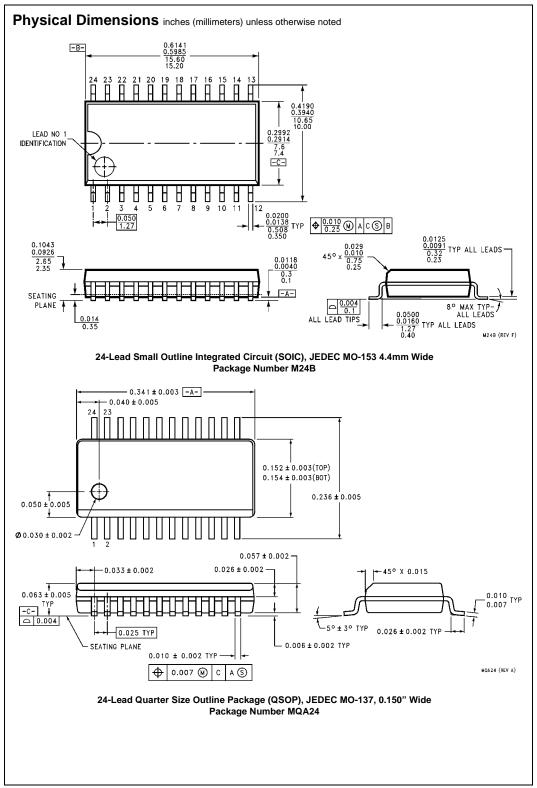

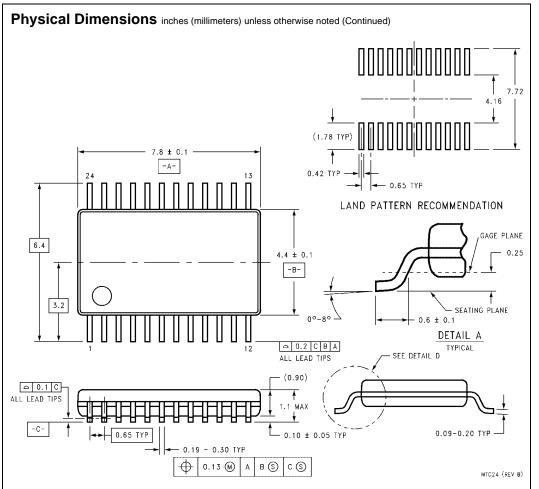

## Physical Dimensions inches (millimeters) unless otherwise noted

48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide Package Number MTD48

## **Technology Description**

The Fairchild Switch family derives from and embodies Fairchild's proven switch technology used for several years in its 74LVX3L384(FST3384) bus switch product.

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

July 1997 Revised December 1999

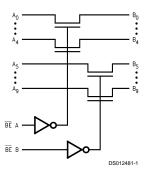

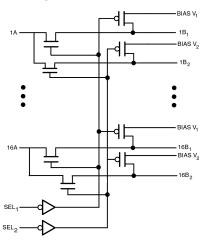

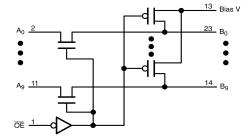

# FST16211 24-Bit Bus Switch

## **General Description**

The Fairchild Switch FST16211 provides 24-bits of highspeed CMOS TTL-compatible bus switching. The low on resistance of the switch allows inputs to be connected to outputs without adding propagation delay or generating additional ground bounce noise.

The device is organized as a 12-bit or 24-bit bus switch. When  $\overline{OE}_1$  is LOW, the switch is ON and Port 1A is connected to Port 1B. When  $\overline{OE}_2$  is LOW, Port 2A is connected to Port 2B

#### **Features**

- $\blacksquare$  4 $\Omega$  switch connection between two ports.

- Minimal propagation delay through the switch.

- Low I<sub>CC</sub>.

- $\blacksquare$  Zero bounce in flow-through mode.