## MX 82C171

#### **FEATURES**

- Pixel rates up to 35 MHz

- 256 colors

- Single monolithic, high performance CMOS design

- Up to 8 bits per pixel

- Pixel word mask

- RGB analong output, 6 bit DAC per gun, composite blank

- Low DAC glitch energy

- Video signal output into 75 ohms or doubly terminated 75 ohm cable

- TTL compatible inputs

- Microprocessor compatible interface

- Single +5V ±10% power supply

- Low power dissipation, 750 mW max. at maximum pixel rate

- Standard 600 mil 28 pin DIP package

- The contents of the look-up table and all microprocessor interface registers can be read.

#### **DESCRIPTION**

THE MX82C171 video DAC is an integration of three 6 bit digital to analog converters and a color look up table. The DAC section can handle loads of 37.5 or 75 ohms. The microprocessor interface is bidirectional for this 28 pin integrated circuit.

The MX82C171 can display 256 colors from a palette of 256K. The part replaces TTL & ECL components, thereby reducing costs and board space. Full CMOS design also reduces power consumption.

The pixel work mask changes colors displayed in single write cycles rather than by changing the entire palette.

#### PIN CONFIGURATION Timing PCLK VCC generato RED 28 VCC RS[1] GREEN 2 27 VSS Memory Array 256 deep RS[0] BLUE . notWR 8 bits REF 25 Pixel P[0]-P[7] laton & P(0) 24 mask P(1) 6 23 [] D(6) P[2] 22 D[5] 7 P(3) 8 21 D[4] D[0]-D[7] D[3] P[4] 9 Micro-D[2] notWD P(5) 19 10 processo interface notRD P(6) 18 [1]C 11. RED GREEN \_\_\_\_ D(0) 3 x 6 Bits P[7] 12 17 Latch DACs BLUE notBLANK PCLK 13 16 vss 🗀 notRD 15 IREF notBLANK PIN NAMES Pixel address inputs P[O]-P[7] Program data bus D[0]-D[7] RS[0]-RS[1] Register select Analog video outputs RED, GREEN, BLUE PCLK Pixel clock Write enable notWR Read enable notRD Video blanking input notBLANK Reference current IREF VCC +5 volt supply input Ground **VSS**

#### APPLICATION INFORMATION

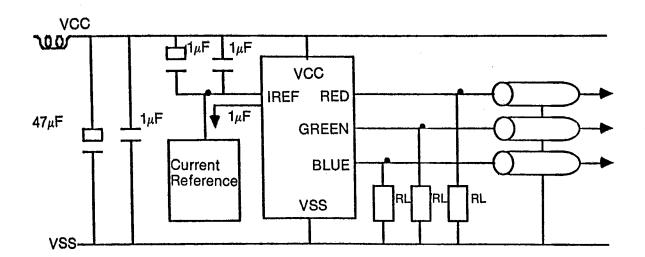

Analog output - Power supply distribution

To ensure the proper operation of the MX 82C171 it is necessary to adopt a high frequency board layout and power supply distribution technique.

The impedance in the decoupling path between the power supply pins (Vcc pin 28 and Vss pin 14) should be kept to a minimum. It is recommended that the decoupling capacitance between Vcc and Vss should be a  $0.1\mu F$  high frequency capacitor in parallel with a larger tantalum capacitor with a value between  $22\mu F$  and  $47\mu F$ . An inductance may be added in series with the positive supply to form a low pass filter and further improve the power supply local to the MX 82C171.

#### Analog output - Line driving

The DACs in the MX82C171 are made from switched current sources. Each current source is based on a current mirror such that the current source will provide one thirtieth of the reference current IREF when it is active.

Each of the three DACs contains 63 current sources. The binary data input to the DAC controls 63 sources.

The output current from the DACs and the output voltage is determined by the reference current IREF. This reference current develops a voltage reference within the MX82C171 relative to Vcc. IREF should be decoupled to the Vcc input to prevent a noise differential between the IREF input and Vcc and hence prevent noise on the analog outputs of the MX82C171.

#### Signal termination

34E D

The trace lines between the outputs of the TTL devices driving the MX 82C171 and the inputs of the MX 82C171 behave like low impedance transmission lines driven from a low impedance source and terminated by a high impedance load. In order to reduce or eliminate the reflectons of the TTL signals propagating down the lines, especially low going signals, line termination is recommended. The termination may be either series or parallel.

The recommended technique is to use series termination. The series technique termination has the advantages of drawing no DC current and using fewer components. This is accomplished by placing a series resistor in the signal line at the output of the TTL driver to dampen the reflection on the line. The resistor should be placed as close to the driver package as is practical. The line should be kept short by placing the driver-termination combination close to the MX82C171.

Some experimentation will have to be done to find proper value to use for the series termination to minimize reflections, but generally a value around 100 ohms will be required. Because each design will result in a different signal impedance, a resistor of a predetermined value may not properly match the signal path impedance. The proper value of the resistance should therefore be selected empirically.

34E D

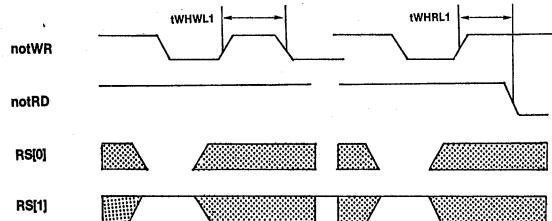

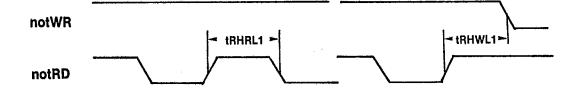

Microprocessor Interface: Read from (a) Pixel Mask register

(b) Pixel Address register (Read Mode)

(c) Pixel Address register (Write Mode)

followed by any access.

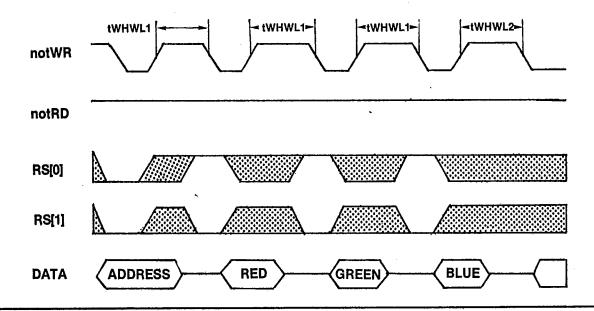

Microprocessor Interface: Color value write followed by any write.

notRD

tSVRL

tRLSX

REGISTER SELECT

tRLQY

tRHQX

tRHQX

tRHQX

tRHQX

34E D

|                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MX 82C1                                                                                                                  | 71-35 |                                                    |                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------|--------------------------------------|

| Symbol                                                                                                                                                                | l Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                          | Max   | Units                                              | Notes                                |

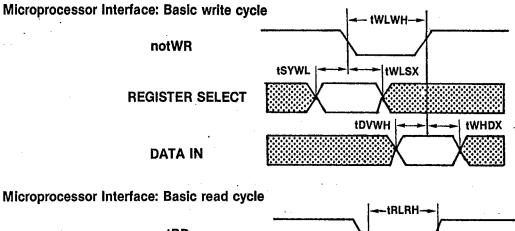

| tWLWH<br>tRLRH<br>tSVWL<br>tSVRL<br>tWLSX<br>tRLSX<br>tDVWH<br>tWHDX<br>tRLQX<br>tRLQX<br>tRHQZ<br>tWHWL1<br>tWHRL1<br>tRHWL1<br>tRHWL1<br>tRHWL2<br>tWHRL2<br>tRHWL2 | notWR pulse width low notRD pulse width low Register select setup time Register select setup time Register select hold time Register select hold time Write data setup time Write data hold time Output turn-on delay Read enable access time Output hold time Output turn-off delay Successive write interval Write followed by read Successive read interval Read followed by write Write after color write Read after color read Write after color read Write enable transition time Read enable transition time | 50<br>50<br>15<br>15<br>15<br>15<br>15<br>15<br>5<br>5<br>3*tCHCH<br>3*tCHCH<br>3*tCHCH<br>3*tCHCH<br>3*tCHCH<br>6*tCHCH |       | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns | Note 1<br>Note 1<br>Note 1<br>Note 1 |

#### Notes

<sup>1.</sup> This parameter allows for synchronization with the pixel stream when a new color value is being written to the look-up table or read from it, therefore this parameter is specified in terms of the pixel clock period tCHCH.

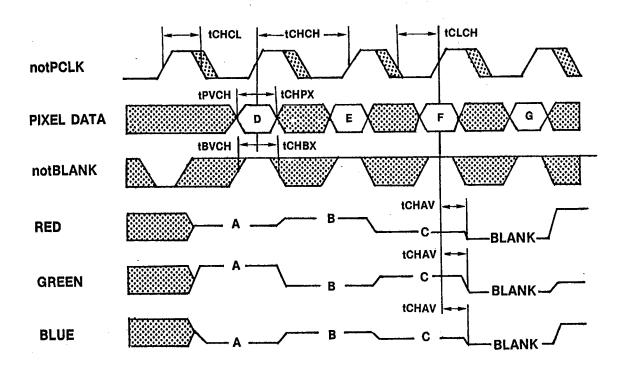

| Symbol                                                                                   |                                                                                                                                                                                                                         | MX 82                                  | C171-35                                           |                                             |                            |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------|---------------------------------------------|----------------------------|

|                                                                                          | Parameter                                                                                                                                                                                                               | Min                                    | Max                                               | Units                                       | Notes                      |

| tCHCH<br>AtCHCH<br>tCLCH<br>tCHCL<br>tPVCH<br>tCHPX<br>tBVCH<br>tCHBX<br>tCHAV<br>AtCHAV | PCLK period PCLK jitter PCLK width low PCLK width high Pixel word setup time Pixel word hold time notBLANK setup time notBLANK hold time PCLK to valid DAC output Differential output delay Pixel clock transition time | 25<br>9<br>9<br>4<br>4<br>4<br>4<br>15 | 10000<br>± 2.5<br>10000<br>10000<br>45<br>1<br>50 | ns<br>%<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns | Note 1<br>Note 2<br>Note 3 |

#### Notes:

- 1. This parameter allowed variation in the Pixel Clock frequency does not permit the Pixel Clock period to vary outside the minimum and maximum values for Pixel Clock (tCHCH) period specified above.

- 2. A valid analog output is defined as when the changing analog signal is half way between its successive values.

- 3. Between different analog outputs on the same device.

- \*\*NOTE\*\* The values given here are preliminary and are subject to change.

34E D

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage on VCC 7.0V Voltage on other pin Vss -1.5V to Vcc + 0.5V Temperature under blas -40°C to 85°C Storage temperature (ambient) -65°C to 150°C Power dissipation 1 W Reference curent -15 mA Analog output current (per output) 45 mA DC digital output current 25 mA Stresses above those listed may cause permanent damage to the device. These are stress ratings only, functional operation of this device at these or any other conditions above those indicated in this data sheet is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC OPERATING CONDITION (a)

| Symbol           | Parameter                                                                           | Min              | Тур      | Max                    | Units                |

|------------------|-------------------------------------------------------------------------------------|------------------|----------|------------------------|----------------------|

| Vcc<br>Vss       | Positive supply voltage<br>Ground                                                   | 4.5              | 5.0<br>0 | 5.5                    | Volts<br>Volts       |

| VIH<br>VIL<br>TA | Input logic "1" voltage<br>Input logic "0" voltage<br>Ambient operating temperature | 2.0<br>-1.0<br>0 |          | Vcc + 0.5<br>0.8<br>70 | Volts<br>Volts<br>°C |

## DC ELECTRICAL CHARACTERISTICS (a,b) ( $0^{\circ}$ C $\leq$ TA $\leq$ 70 $^{\circ}$ C)(Vcc = 5.0V $\pm$ 10%)

| Symbol   | Parameter                                | Min       | Max  | Units | Notes       |

|----------|------------------------------------------|-----------|------|-------|-------------|

| ICC      | Average power supply current             |           | 150  | mA    | C           |

| IREF     | Reference current                        | -1.5      | -10  | mΑ    | d           |

| VOA(max) | Maximum analog output voltage            | 1.5       |      | ٧.    | 10A ≤ 10 mA |

| IOA(max) | Maximum analog output current            | 21        |      | mΑ    | VOA≤0.7V    |

| ` '      | Full scale accuracy                      | ±5        |      | %     |             |

|          | Differential accuracy                    | ±1        |      | %     | е           |

|          | Linearity                                | $\pm 0.5$ |      | LSB   | F           |

| IIN      | Digital input current (any input)        |           | ± 10 | μΑ    | g,n         |

| ioz      | Off state digital output leakage current |           | ± 50 | μΑ    | g,o         |

| VOH      | Output logic "1" voltage                 | 2.4       |      | V     | 105 mA      |

| VOL      | Output logic "0" voltage                 |           | 0.4  | V     | 10-5 mA     |

## AC ELECTRICAL CHARACTERISTICS (b) $(0^{\circ}C \le TA \le 70^{\circ}C)(Vcc = 5.0V \pm 10\%)$

| Symbol | Parameter                           | Min | Max            | Units              | Notes         |

|--------|-------------------------------------|-----|----------------|--------------------|---------------|

|        | (10%`to 90%)<br>setting time<br>rgy |     | 8<br>28<br>200 | ns<br>ns<br>pVsec` | h<br>h,i<br>j |

### CAPACITANCE(j,k)

| Symbol | Parameter                  | Max | Units | Notes |

|--------|----------------------------|-----|-------|-------|

| CI     | Digital input capacitance  | 7   | pF    | n     |

| CO     | Digital output capacitance | 7   | pF    | I,o   |

| COA    | Analog output capacitance  | 10  | pF    | m     |

#### **AC TEST CONDITIONS**

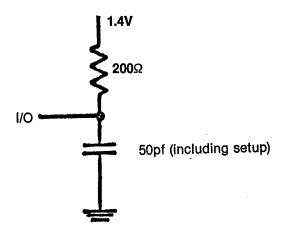

Input pulse levels Vss to 3V Input rise and fall times 2.5m Digital input timing reference level 1.5V Digital output timing reference level 0.8V and 2.4V Digital output load See Figure 1

#### Notes:

a - All voltages in this data sheet are with respect to Vss unless specified otherwise

- b The Pixel Clock frequency must be stable for a period of at least 20 μs after power-up (or after a change in Pixel Clock frequency before proper device operation is quaranteed.

c - Pixel Clock frequency = 35 MHz. 10A = 10A(max).

d - Voltage at IREF input (pin 4) Vcc to Vcc - 3V.

- e Between different analogue outputs on the same device.

- f Monotonicity guaranteed.

g Vcc = max, Vss ≤ Vin ≤ Vcc.

h Load = 75Ω + 30 pF.

i Between 1% and 99% of full scale voltage.

- . This parameter is sampled, not 100% tested.

- k Capacitance measured with a Hewlett Parkard meter.

- I notRD ≥ VIH(min) to disable D[0]-D[7]. m- notBLANK ≤ VIL(max) to disable RED, GREEN and BLUE.

- n On pin numbers 5 to 16 and 25 to 27.

- o On pin numbers 17 to 24.

Figure 1. Output Load

<sup>\*\*</sup>NOTE\*\* The values given here are preliminary and are subject to change.

#### **DEVICE OPERATION**

#### Video path

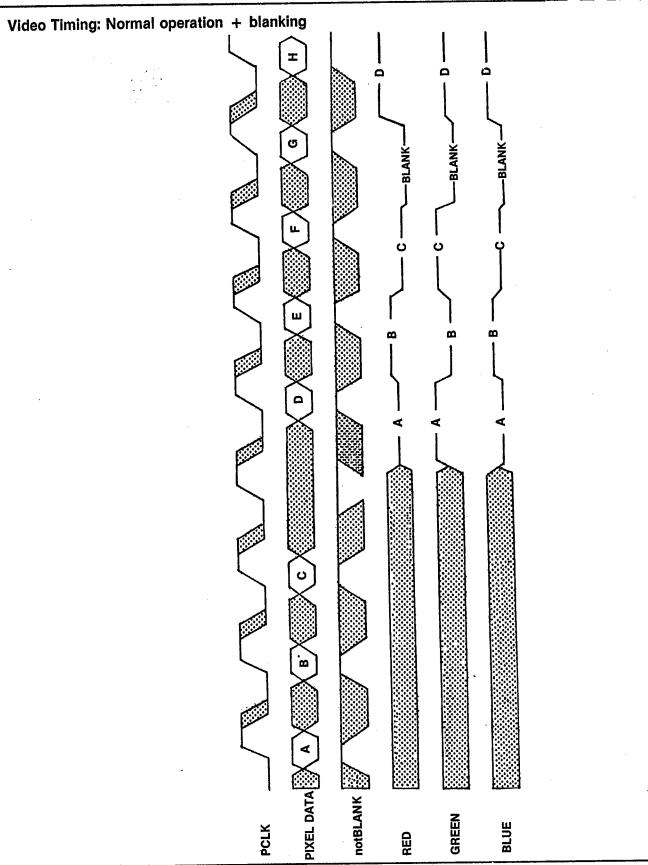

The Pixel Address and notBLANK inputs are sampled on the rising edge of Pixel Clock and appear at the analog outputs after three further rising edges of Pixel Clock.

#### **Analog Outputs**

The outputs of the DACs are intended to product 0.7 volt peak white amplitude when driving a 75 ohms load with 4.44mA IREF suplied, or a doubly terminated 75 ohm cable with 8.88 mA IREF supplied.

The notBLANK input to the MX 82C171 acts on all three of the analog outputs. When the notBLANK input is low a binary zero is applied to the inputs of the DACs.

The expressions for peak white voltage/output loading combinations given below:

Vpeak white =  $\frac{IREF \times 63 \times Rload}{IREF \times 63 \times Rload}$

Vblack level = 0

#### Microprocessor interface

There are three internal registers in the MX82C171. Each register can both be written to and read from. The registers are:-

| RS1 | RS <sub>0</sub> | REGISTER | NAME |

|-----|-----------------|----------|------|

|     |                 |          |      |

- Pixel Address (Write Mode) 0 1

- Pixel Address (Read Mode)

- **Color Value** 0

- **Pixel Mask**

The Value in the Pixel Address register specifies a location in the look-up table. The Color Value register allows data to be written to or read from the look-up table at the location specified by the Pixel Address register. The Pixel Mask register is an 8 bit register. The value in the mask register is bitwise ANDed with the incoming pixel address to give a masked pixel

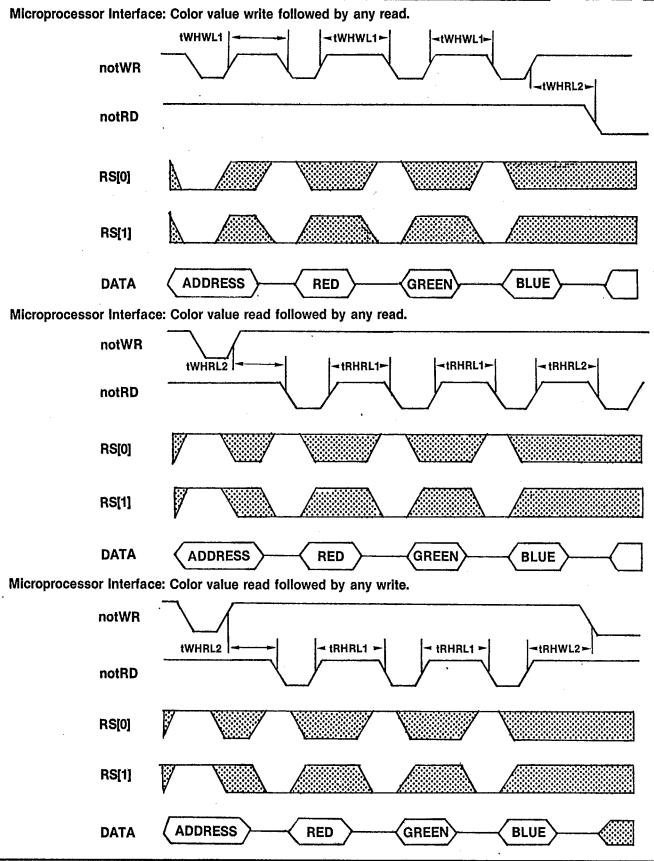

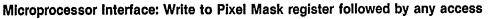

The microprocessor interface is asynchronous with the video path, the timing of operations on the interface registers being controlled by the Write Enable signal (not WR) and the Read Enable signal (not RD). After certain accesses to the microprocessor interface data has to be written to or from the look-up table. To allow these operations to be synchroniseed to the pixel stream minimum inactive periods (noth notWR and notRD high) are specified between accesses to the microprocessor interface. Each time a color value is written to (or read from) the look-up table the write (or read) cycle will replace the colour value red cycle for one pixel.

To access a color definition in the look-up table first both the mode of access (read or write) and the pixel address must be specified, then an 18 bit data word must be read from or written to the location specified.

The mode of access (read or write) is determined by writing a value into the Pixel Address register with RS[0] = RS[1] = 1 to enter Read Mode or RS[0] = RS[1] = 0 to enter Write Mode.

Once the mode and pixel address have been set one or more locations in the look-up table can be accessed. The first access will occur at the location specified by the value written to the Pixel Address register then, (as the Pixel Address register increments after each complete color value write or color value read sequence) further accesses can occur to a succession of locations.

A color value write sequence can occur when the MX 82C171 is in write mode. A color value write sequence is three successive byte writes to the Color Value register. The least significant 6 bits are taken from each byte written and concatenated into an 18-bit word in the Color Value register. The first byte written will define the red intensity, the second the green and the last the blue. When the three values have been written to the register its contents are written to the look-up table and the Pixel Address register is then incremented.

A color value read sequence can occur when MX 82C171 is in read mode. A color value read sequence is three successive byte reads from the Color Value register. The least significant 6 bits of each byte read are taken from the 18 bit word in the Color Value register. The most significant two bits of each byte will be set to zero. The first byte read will contain the data for the red intensity, the second the green and the last the blue. When the three values have been read from the register the Pixel Address register is incremented and a new color value is read from the look-up table into the Color Value register.

The pixel address supplied to the Pixel Address inputs is bitwise ANDed with the Pixel Mask register before it is used to access the look-up table. This pixel masking process can be used to alter the displayed colors without altering the video memory or the lookup table contents. By partitioning the color definitions by one or more bits in the pixel address rapid animation and flashing objects can be produced.

If the Pixel Address register is written to during either a color value read or a color value write sequence the Color Value register is initialised, aborting any unfinished read or write sequence. The effects of reading from the color value register during a color value write sequence or writing to the register during a read sequence are not defined and may change the lookup table contents.

Accesses to the Pixel Mask register and read from the Pixel Address register can occur without reference to the state of colour value read or write sequences.

#### **DEVICE DESCRIPTION**

The MX 82C171 is intended for use as the output stage of raster scan video systems. It contains a high speed random access store of 256 x 18 bit words, three 6 bit high speed DACs, 6 micro-processor interface and a pixel word mask.

An 8 bit value read in on the Pixel Address input is used as a read address for the store and results in an 18 bit data word. This data is partitioned as three fields of 6 bits, with each fields being applied to the

inputs of a 6 bit DAC.

Pixel rates of upto 35 MHz are achieved by pipelining the memory access over three clock periods.

An externally generated blanking signal can be input to the MX 82C171; this signal acts on all three of the analog outputs. The notBLANK signal is delayed internally by pipelining so that it appears at the analogue outputs with the correct relationship to the pixel stream.

The contents of the look-up table can be modified and examined via an 8 bit wide microprocessor interface. The use of an internal synchronising circuit allows operations on the interface to be totally asynchronous to the video path.

A pixel word mask is included to allow the incoming pixel address to be masked. The permits rapid changes of the effective contents of the Color Look-Up Table to facilitate such operations as

| Internal F | Registers |                |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|-----------|----------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS[1]      | RS[0]     | SIZE<br>(bits) | Register<br>Name                          | Description (All registers can be written to and read from)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0          | 0         | 8              | Pixel Address<br>Register (Write<br>Mode) | Writing to the Pixel Address register in Write Mode sets the start address for one or more color value write sequences. Writing to the Pixel Address register in Read Mode set the start address for one or more colour value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1          | 1         | 8              | Pixel Address Register (Read Mode)        | read sequences. Reading the Pixel Address register will read the current pixel address and will leave the device in its existing mode (Read Mode or Write Mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0          | 1         | 18             | Color Value                               | The Color Value register is 18 bits wide. In Write Mode it is used to assemble a new color value before it is written to the loop-up table. In Read Mode it holds a color value read from the look-up table. The Color Value register is loaded by a sequence of three accesses. The first access is to the red DAC data, the second to the green DAC data and the third to the blue DAC data. In write sequences the least significant 6 bits of each byte are written to the Color Value register where they are concatenated to form an 18 bit color word. In read sequences the least significant 6 bits of each byte read come from the Color Value register and contain the data for one color in the 18 bit color word; the most significant two bits of the byte are set to zero. |

| 1          | 0         | 8              | Pixel Mask                                | The Pixel Mask register can be used to mask selected bits of the Pixel Address value applied to the Pixel address inputs (P[0]-P[7]. A one in a position in the mask register leaves the corresponding bit in the Pixel Address unaltered, a zero setting that bit to zero. The Pixel Mask register does not affect the Pixel Address used when the look-up table is being accesses via the microprocessor interface.                                                                                                                                                                                                                                                                                                                                                                     |

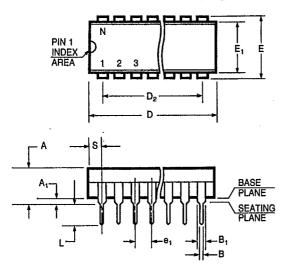

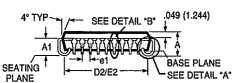

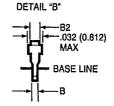

# PLASTIC DUAL-IN-LINE PACKAGES (PDIP) 16, 18, 20, 24, 28 LEAD 300 MIL WIDE AND 24, 28, 32, 40 LEAD 600 MIL WIDE

| LEADS<br>WIDTH          |                  | 4<br>00 | .50<br>.50       | )0      | .30              |             | .60              |               | .60              | 00        | .60              | 10<br>00    |

|-------------------------|------------------|---------|------------------|---------|------------------|-------------|------------------|---------------|------------------|-----------|------------------|-------------|

| SYMBOL                  | MIN              | MAX     | MIN              | MAX     | MIN              | <b>EMAX</b> | MIN              | <b>愛MAX</b> 序 | MIN              | SMAX F    | SMIN             | <b>≋MAX</b> |

| A                       | ,150             | ,200    | .150             | .200    | .150             | .200        | .150             | .200          | .150             | .200      | .150             | .200        |

|                         | (3.81)           | (5.08)  | (3.81)           | (5.08)  | (3.81)           | (5.08)      | (3.81)           | (5.08)        | (3.81)           | (5.08)    | (3.81)           | (5.08)      |

| A1                      | .015             | .070    | .015             | .070    | .015             | .070        | .015             | .070          | .015             | .070      | .015             | .070        |

|                         | (.381)           | (1.78)  | (.381)           | (1.78)  | (.381)           | (1.78)      | (.381)           | (1.78)        | (.381)           | (1.78)    | (.381)           | (1.78)      |

| A2                      | .125             | .155    | .135             | .165    | .125             | .155        | .135             | .165          | .135             | .165      | .135             | .165        |

|                         | (3.18)           | (3.94)  | (3.43)           | (4.19)  | (3.18)           | (3.94)      | (3.43)           | (4.19)        | (3.43)           | (4.19)    | (3.43)           | (4.19)      |

| В                       | .015             | .023    | .015             | .023    | .015             | .023        | .015             | .023          | .015             | .023      | .015             | .023        |

|                         | (.381)           | (.584)  | (.381)           | (.584)  | (.381)           | (.584)      | (.381)           | (.584)        | (.381)           | (.584)    | (.381)           | (.584)      |

| B1                      | .060<br>(1.52)   | TYP     | .060<br>(1.52)   | TYP     | .060<br>(1.52)   | TYP         | .060<br>(1.52)   | TYP           | .050<br>(1.27)   | TYP       | .060<br>(1.52)   | TYP         |

| С                       | .008             | .015    | .008             | .015    | .008             | .015        | .008             | .015          | .008             | .015      | .008             | .015        |

|                         | (.203)           | (.381)  | (.203)           | (.381)  | (.203)           | (.381)      | (.203)           | (.381)        | (.203)           | (.381)    | (.203)           | (.381)      |

| D                       | 1.230            | 1.270   | 1.230            | 1.280   | 1.345            | 1.355       | 1.390            | 1,470         | 1.640            | 1.660     | 2.030            | 2.080       |

|                         | (31.24)          | (32.26) | (31.24)          | (32.51) | (34.16)          | (34.42)     | (35.31)          | (37.34)       | (41.66)          | (42.16)   | (51.56)          | (52.83)     |

| D2                      | 1.100<br>(27.94) | TYP     | 1.100<br>(27.94) | TYP     | 1.300<br>(33.02) | TYP         | 1.300<br>(33.02) | TYP           | 1.400<br>(35.56) | TYP       | 1.900<br>(48.26) | TYP         |

| E                       | .300             | .320    | .600             | .620    | .300             | .325        | .600             | .620          | .600             | .620      | ,600             | .620        |

|                         | (7.62)           | (8.13)  | (15.24)          | (15.75) | (7.62)           | (8.26)      | (15.24)          | (15.75)       | (15.24)          | (15.75)   | (15.24)          | (15.75)     |

| E1 (4)                  | .240             | .280    | .520             | .560    | .270             | .290        | .520             | .560          | .520             | .560      | ,520             | .560        |

|                         | (6.10)           | (7.11)  | (13.21)          | (14.22) | (6.86)           | (7.37)      | (13.21)          | (14.22)       | (13.21)          | (14.22)   | (13.21)          | (14.22)     |

| e1 (3)                  | .100<br>(2.54)   | TYP     | .100<br>(2.54)   | TYP     | .100<br>(2.54)   | TYP         | .100<br>(2.54)   | TYP           | .100<br>(2.54)   | TYP       | .100<br>(2.54)   | TYP         |

| eA(3)                   | .300<br>(7.62)   | TYP     | .600<br>(15.24)  | TYP     | .300<br>(7.62)   | TYP         | .600<br>(15.24)  | TYP           | .600<br>(15.24)  | TYP       | .600<br>(15.24)  | TYP         |

| eB (3)                  | .350<br>(8.89)   | TYP     | .650<br>(16.51)  | TYP     | .350<br>(8.89)   | TYP         | .650<br>(16.51)  | TYP           | .650<br>(16.51)  | TYP       | .650<br>(16.51)  | TYP         |

| L                       | .120             | .140    | .120             | .140    | .120             | .140        | .120             | .140          | .120             | .140      | .120             | .140        |

|                         | (3.05)           | (3.56)  | (3.05)           | (3.56)  | (3.05)           | (3.56)      | (3.05)           | (3.56)        | (3.05)           | (3.56)    | (3.05)           | (3.56)      |

| N                       | 2                | 24      | 2                | 24      | 2                | 28          | 2                | :8            | 3                | 32        | 4                | 10          |

| S                       | .040             | .085    | .040             | .085    | .020             | .030        | .040             | .085          | .040             | .085      | .040             | .090        |

|                         | (1.02)           | (2.16)  | (1.02)           | (2.16)  | (.508)           | (.762)      | (1.02)           | (2.16)        | (1.02)           | (2.16)    | (1.02)           | (2.29)      |

| ∞ (5)                   | 0                | 15      | 0                | 15      | 0                | 15          | 0                | 15            | 0                | 15        | 0                | 15          |

| Theta JA (<br>°C/Watt A |                  |         | 55<br>110        |         | 50<br>105        | 1           | 55<br>10         | 45<br>105     |                  | 45<br>105 |                  | 45<br>100   |

- NOTES:

1. Refer to applicable symbol glossary.

2. All dimensions are in inches (mm).

- e1, eA and eB apply for installing on a PC board.

D and E1 do not include mold flash.

- ≤ In degrees applies to spread of leads.

- 6. The Thermal Resistance, Theta JA, In °C/Watt, quoted above is for a 10,000 sq. mill die in still air and shown for both copper and alloy-42 frames. Values are approximate.

7. Lead frame material: alloy 42 or copper.

8. Lead finish: Matte tin or Sn/Pb solder.

- Note: Call Manufacturer for dimensional information on 16, 18, 20, 48 and 64 lead packages.

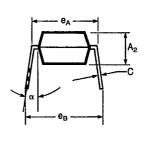

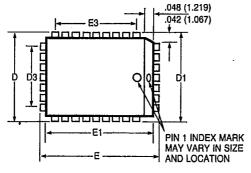

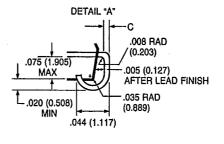

# PLASTIC LEADED CHIP CARRIERS (PLCC)

24, 32, 44, 68, AND 84 LEAD

**LEADS**

32

68

84

| SYMBOL -                  | MIN             | JULY.           | . MIN.          | MAX             | MIN               | MAXO            | S MINE          | - MAY           | > NIV            | ALL IN          |

|---------------------------|-----------------|-----------------|-----------------|-----------------|-------------------|-----------------|-----------------|-----------------|------------------|-----------------|

| Α                         | .165<br>(4.19)  | .180<br>(4.57)  | .100<br>(2.54)  | .140<br>(3.56)  | .165<br>(4.19)    | .180<br>(4.57)  | .165<br>(4.19)  | .200<br>(5.08)  | .165<br>(4.19)   | .200<br>(5.08)  |

| A1 .                      | .090<br>(2.29)  | .120<br>(3.05)  | .060<br>(1.52)  | .095<br>(2.41)  | .090<br>(2.29)    | .120<br>(3.05)  | .090<br>(2.29)  | .130<br>(3.30)  | .090<br>(2.29)   | .130<br>(3.30   |

| В                         | .013<br>(.330)  | .021<br>(.533)  | .013<br>(.330)  | .021<br>(.533)  | .013<br>(.330)    | .021<br>(.533)  | .013<br>(.330)  | .021<br>(.533)  | .013<br>(.330)   | .021<br>(.533   |

| B2                        | .026<br>(.660)  | .032<br>(.813)  | .026<br>(.660)  | .032<br>(.813)  | .026<br>(.660)    | .032<br>(.813)  | .026<br>(.660)  | .032<br>(.813)  | .026<br>(.660)   | .032<br>(.813   |

| С                         | .008<br>(.203)  | .010<br>(.254)  | .008<br>(.203)  | .010<br>(.254)  | .008<br>(.203)    | .010<br>(.254)  | .008<br>(.203)  | .010<br>(.254)  | .008<br>(.203)   | .010<br>(.254   |

| D                         | .485<br>(12.32) | .495<br>(12.57) | .485<br>(12.32) | .495<br>(12.57) | ,685<br>(17.40)   | .695<br>(17.65) | .985<br>(25.02) | .995<br>(25.27) | 1.185<br>(30.10) | 1.195<br>(30.35 |

| D1                        | .450<br>(11.43) | .456<br>(11.58) | .447<br>(11.35) | .453<br>(11.51) | .650<br>(16.51)   | .656<br>(16.66) | .950<br>(24.13) | ,958<br>(24.33) | 1.150<br>(29.21) | 1.158           |

| D2                        | .390<br>(9.91)  | .430<br>(10.92) | .390<br>(9.91)  | .430<br>(10.92) | .590<br>(14.99) - | .630<br>(16.00) | .890<br>(22.61) | .930<br>(23,62) | 1.090<br>(27.69) | 1.130           |

| D3                        | .300<br>(7.62)  | REF             | .300<br>(7.62)  | REF             | .500<br>(12.70)   | REF             | .800<br>(20.32) | REF             | 1.000<br>(25,40) | REF             |

| E                         | .485<br>(12.32) | .495<br>(12.57) | .585<br>(14.86) | .595<br>(15.11) | .685<br>(17.40)   | .695<br>(17.65) | .985<br>(25.02) | .995<br>(25.27) | 1.185<br>(30.10) | 1.19<br>(30.3   |

| E1                        | .450<br>(11.43) | .456<br>(11.58) | .547<br>(13.89) | .553<br>(14.05) | .650<br>(16.51)   | .656<br>(16.66) | .950<br>(24.13) | .958<br>(24.33) | 1.150<br>(29.21) | 1.158           |

| E2                        | .390<br>(9.91)  | .430<br>(10.92) | .490<br>(12.45) | .530<br>(13.46) | .590<br>(14.99)   | .630<br>(16.00) | .890<br>(22.61) | .930<br>(23.62) | 1.090<br>(27.69) | 1.130           |

| E3                        | .300<br>(7.62)  | REF             | .400<br>(10.16) | REF             | .500<br>(12.70)   | REF             | .800<br>(20.32) | REF             | 1.000<br>(25.40) | REF             |

| e1                        | .050<br>(1.27)  | TYP             | .050<br>(1.27)  | TYP             | .050<br>(1.27)    | TYP             | .050<br>(1.27)  | TYP             | .050<br>(1.27)   | TYP             |

| N                         | 2               | 8               | 3               | 2               | 4                 | 4               | 6               | 8               | 8                | 4               |

| ND                        |                 | 7               |                 | 7               | 11                |                 | 17              |                 | 2                | :1              |

| NE                        |                 | 7               | (               | 9               | 11                |                 | 17 -            |                 | 21               |                 |

| Theta JA (5)<br>(°C/Watt) | 4               | 5               | 4               | 5               | 4                 | 5               | 4               | 5               | 4                | 5               |

- NOTES:

1. Refer to applicable symbol glossary.

2. All dimensions are in inches (mm).

3. Controlling dimension inch.

4. D1 and E1 do not include mold flash.

- The Thermal Resistance, Theta JA, In °C/Watt, quoted above is for a 10,000 sq. mil die in still air with copper frame. Values are approximate,

- 6. Lead frame material: copper.

7. Lead finish: Matte tin or Sr/Pb solder dip.

8. Note: Call Manufacturer for dimensional information on 20, 52 and 84 lead packages.