## iFX740 10 ns FLEXIogic FPGA WITH SRAM OPTION

- High Performance FPGA (Field Programmable Gate Array)

- Deterministic 10 ns Pin-to-Pin Propagation Delays

- 80 MHz System Clock Frequency

- 2,500 Equivalent Logic Gates or up to 5,120 Bits of SRAM

- 0.8µ CMOS Technology

- Power Management Options

Minimize Active Power Consumption

(1 mA/MHz)

- 1 mA Standby Version Available

- JTAG 1149.1 Compatible Test Port

- Supports Boundary Scan and In-Circuit Reconfiguration/ Programming

- Four Configurable Function Blocks (CFBs) Linked by a 100% Connectable Matrix

- Improves Fitting of Complex Designs

- Any CFB Can Be Either 24V10 Logic or SRAM Block

- Up to 40 Complex Macrocells

- 128 x 10 SRAM Configuration

- CFB Selectable 3.3V or 5V Outputs

- Open-Drain Output Option

- **24V10 Macrocell Features**

- Dual Feedback on All I/O Pins

- Allocation Supports up to 16 Product Terms per Macrocell with No Performance Penalty

- 12 Clocking Options

- Flexible Preset/Clear Options

- Selectable D/T Flip-Flops

- Fast 12-Bit Identity Compare Option

- Supported by Industry Standard Design and Programming Tools

## **Package Options**

| Pins | Package | Macrocells | 1/0 | Inputs | Clocks | JTAG/V <sub>PP</sub> | Vcc | GND |

|------|---------|------------|-----|--------|--------|----------------------|-----|-----|

| 44   | PLCC    | 40         | 30  | 0      | 2      | 5                    | 3   | 4   |

| 68   | PLCC    | 40         | 40  | 10     | 2      | 5                    | 5   | 6   |

November 1993 Order Number: 290460-003

#### INTRODUCTION

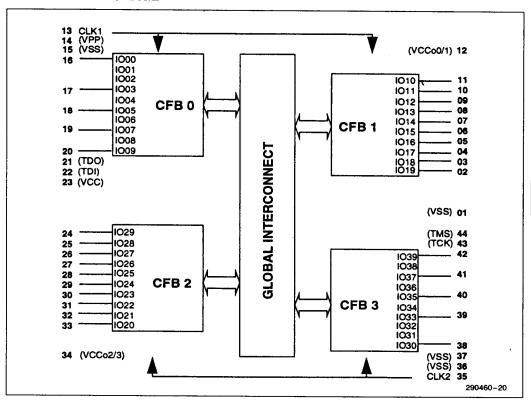

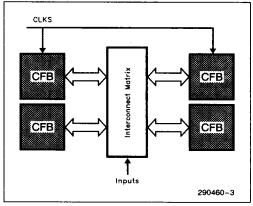

The iFX740 is the second member of the Intel FLEXlogic FPGA (Field Programmable Gate Array) family. The iFX740 consists of four configurable function blocks (CFBs) linked by a 100% connectable matrix. Each CFB can be defined either as a 24V10 logic block or as a block of 128 x 10 SRAM. This combination will provide approximately 2,500 gates of logic in a choice of two PLCC packages.

#### **FLEXIBLE PERFORMANCE**

The iFX740 uses Intel's  $0.8\mu$  CHMOS EPROM technology to provide an 80 MHz external clock frequency with predictable 10 ns pin-to-pin delays. This advanced process technology combined with power management options enables very low active and standby power consumption.

#### **FLEXIBLE FEATURES**

The unique combination of features available in the iFX740 makes it ideal for a wide variety of applications. For example, the high performance and flexible clock options provided are designed to support functions such as bus control, custom cache control, and DRAM control for the current and next generation of Intel microprocessors. The very low power consumption and user selectable 5V/3.3V outputs allow the iFX740 to be used in mixed voltage applications such as portable or embedded systems where CPUs operating at 3.3V still need to communicate to 5V peripherals. The combination of SRAM and logic in a single device becomes a big advantage when designing communication controllers or bus interface controllers where memory is required for buffering data in addition to the logic for the controller design itself.

#### FLEXIBLE TESTING AND PROGRAMMING

The iFX740 also provides dedicated JTAG 1149.1 compatible pins to support boundary scan, in-circuit reconfiguration, and programming modes. In-circuit reconfiguration not only allows the designer ultimate flexibility in prototyping new designs but also supports applications where the final configuration is not fixed. New configurations may be downloaded to the iFX740 upon power-up to reflect changes in system organization or design requirements that cannot be determined at production time.

#### FLEXIBLE TOOLS SUPPORT

The FLEXIogic FPGA family is supported by industry standard design entry/programming environments

including Intel's PLDshell Plus software. This software runs on Intel386™ or higher PC-compatible platforms.

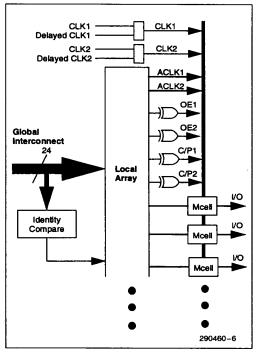

#### INTERCONNECT

The Global interconnect Matrix that connects each of the CFB blocks is 100% connectable. Any combination of signals in the matrix can be routed into any CFB block, up to the maximum fan-in of the block (24).

This high degree of connectivity between CFB blocks eliminates routing problems during rework of a complex design.

Figure 1. Interconnect Matrix

#### CONFIGURABLE FUNCTION BLOCKS

#### 24V10 Mode

Each 24V10 block contains a product term array, a P-Term Allocation circuit, 10 macrocells, clocks and I/O logic in the familiar architecture of a simple PLD.

The 24V10 CFB blocks have a generous fan-in to macrocell ratio (2.4:1). This improves the fitting capacity of the iFX740 architecture by providing more available interconnect lines from the global interconnect matrix for each macrocell.

The 24V10 blocks also provide two asynchronous Clear/Preset control terms and two Output Enable control terms (with an inversion option for each). Within each 24V10 block an identity compare circuit is available that can perform a compare of up to 12 bits within the tp0 of the device.

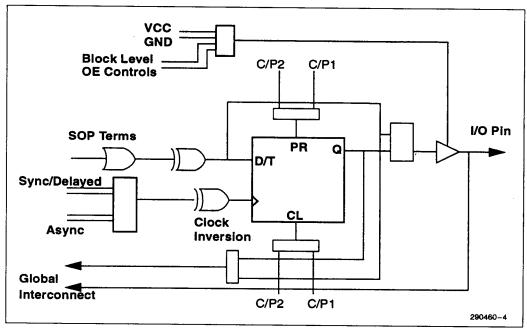

Figure 2. CFB as 24V10 Block

#### **MACROCELL CONFIGURATIONS**

Each I/O of the device has dual (internal and pin) feedback paths (see Figure 2). This allows macrocells to be used for buried logic while the I/O pins are used as inputs. Depending on the package used, some macrocell outputs may not be brought outside the package. These I/Os may still be used to provide buried logic since internal feedback is available. The macrocells can be configured either as a fast combinatorial block, a D-register, or a T-register. J/K and S/R registers are available as software emulations.

#### **CLOCKING MODES**

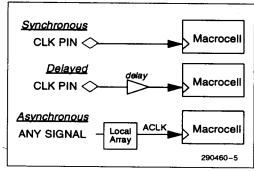

There are three clocking modes available for every macrocell (see Figure 3): synchronous, delayed, asynchronous. Table 1 shows the different timing options each clock mode offers.

Synchronous is the standard clock mode where the register clock is driven directly from one of the two global clock pins.

Figure 3. Clock Modes

Delayed clock is similar to synchronous, but there is a local delay added (within the CFB) to either of the two synchronous clock signals.

Asynchronous mode is where the register clock uses one of the two local CFB ACLK product terms.

#### Clock Mode Timings for iFX740Z

| Mode         | T <sub>SU</sub> | THOLD | тсо |

|--------------|-----------------|-------|-----|

| Synchronous  | 6               | 0     | 6   |

| Delayed      | 4.5             | 2     | 8   |

| Asynchronous | 2               | 5     | 12  |

#### **Clock Mode Timings for iFX740**

| Mode         | T <sub>SU</sub> | THOLD | Tco |

|--------------|-----------------|-------|-----|

| Synchronous  | 6               | 0     | 6.5 |

| Delayed      | 4.5             | 2     | 8.5 |

| Asynchronous | 2               | 5     | 12  |

In addition, each clocking mode may be inverted to allow the macrocell register to be clocked either on the rising or falling edge of the clock signal. This combination provides up to twelve different clock options for each macrocell.

#### **CONTROL SIGNALS**

There are 4 control signals in each CFB in addition to the clocks (see Figure 4). These include two Output Enable (OE) signals, and two asynchronous Clear/Preset signals. Each control signal is generated by a single product term from the local 24V10 AND array with an inversion option. This allows multiple product term control equations to be implemented.

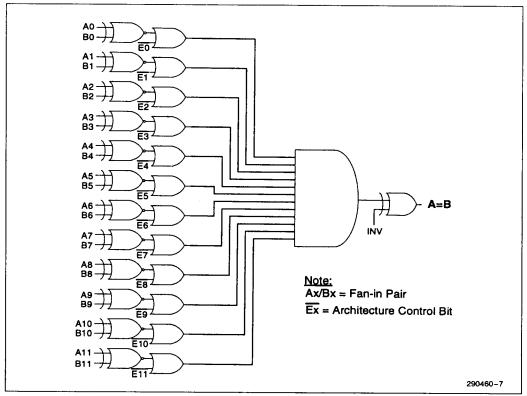

#### COMPARATOR LOGIC

Each 24V10 block provides a comparator circuit (see Figure 5). This circuit can do an identity compare of up to 12 signals within the TPD of the device.

Figure 4. Control Signals

Figure 5. 12-Bit Identity Compare Logic

The number of bits that can be compared is only limited by the fan-in of the CFB. Since the fan-in is 24 signals, a 12-bit comparator is the maximum implementation possible.

When less than 12 bits are being compared, the other signals available from the Interconnect Matrix can be used in equations. For instance, doing an 8-bit compare still leaves 8 other signals on the block fanin (24-16=8). The bits being compared may also be used to implement SOP logic in parallel with the compare function.

The output of the comparator circuit may be used in place of any of the product term pairs in the product term allocation logic allowing the compare result to be used in any macrocell. However, only one of the ten macrocells in the CFB can use the comparator output.

#### PRODUCT TERM ALLOCATION

The iFX740 uses the patented Intel product term allocation scheme, which gives better utilization of the P-term resources without the performance penalty of other approaches. The P-terms are typically grouped into sets of two product terms each, and there are two sets per macrocell.

Each macrocell may borrow from adjacent macrocells in order to increase the total number of P-terms to a maximum of 8. In addition, the macrocells located at the "ends" of each CFB have access to additional product terms and can support up to 16 P-term equations (see Figure 6). The performance of any macrocell is the same whether 2 or 16 P-terms are being used.

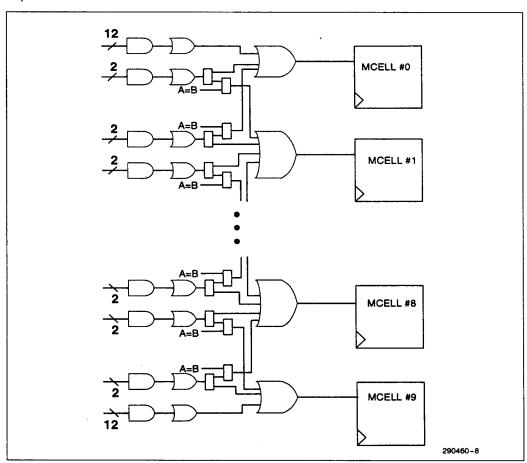

Figure 6. CFB Product Terms

## SRAM Configuration

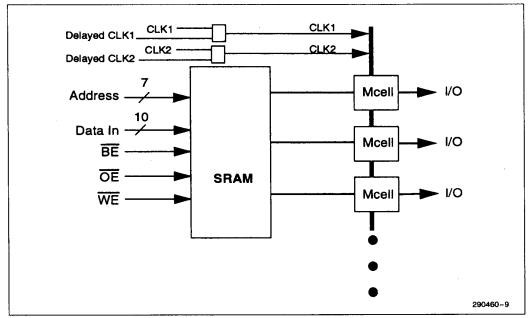

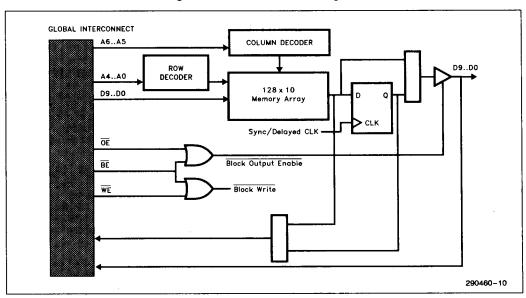

Each iFX740 CFB block can be configured as a 128 x 10 (128 words by 10 bits) SRAM block (see Figures 7 and 8). The SRAM is accessed in a conventional manner by using 7 bits of the 24 signal famin as address information and 10 bits as data-in. Three bits are used for  $\overline{\rm BE}$  (Block Enable),  $\overline{\rm WE}$ , and  $\overline{\rm OE}$  controls (see Table 1).

**Table 1. SRAM Function Table**

|    | Inputs |    | 0     |          |

|----|--------|----|-------|----------|

| BE | WE     | ŌĒ | Cycle | I/O Pins |

| 1  | Х      | Х  | None  | Disabled |

| 0  | 1      | 1  | Read  | Disabled |

| 0  | 1      | 0  | Read  | Enabled  |

| 0  | 0      | 1  | Write | Disabled |

| 0  | 0      | 0  | Write | Enabled  |

It is possible to define the SRAM memory either with a bidirectional I/O data bus or with a separate input data bus and output data bus.

The SRAM memory bits are initialized by the on-chip non-volatile configuration cells during power-up. Therefore, the data in the SRAM can be pre-configured at programming time. As long as no memory writes to this block are executed, the SRAM will contain a copy of the nonvolatile cells. In this way, the SRAM block can be used as read only memory (ROM).

When a CFB is configured as a SRAM, regular Sumof-Product logic is unavailable in that block. All of the macrocells and p-terms have been converted to SRAM use.

Different sized SRAM organizations are possible by cascading multiple CFBs to increase the width or depth of the memory.

## **Input Configuration**

Inputs, as well as I/O pins that are used as inputs. can be optimized for minimum standby current during either CMOS or TTL operation by using the "CMOS\_LEVEL" and "TTL\_LEVEL" keywords available in the PLDasm design language of PLDshell Plus. For 5V CMOS inputs. "CMOS\_LEVEL" keyword (the default condition for PLDasm) should be used. For TTL or 3.3V CMOS inputs, the "TTL\_\_LEVEL" keyword should be used to minimize standby power consumption. Third party tools that support the FLEXlogic family provide input configuration in a method specific to each tool. For Additional information refer to Application Brief AB-27.

ADVANCE INFORMATION

## **Output Configuration**

#### 3.3V SELECTION

The pins in an I/O block can operate at 3.3V by tying the appropriate  $V_{\rm CCO}$  pins to a 3.3V power supply. While the iFX740 still requires 5V  $V_{\rm CC}$  for normal operation, the  $V_{\rm CCO}$  pin associated with each CFB block may be connected to either 5V or 3.3V to control the output voltages of the I/O pins in that block. This allows the iFX740 to be used in mixed voltage systems. For example, the iFX740 device may be used as an interface to bridge between a 3.3V CPU and 5V peripheral logic. In addition, all input pins are 5V safe so mixing 3.3V outputs and 5V inputs is supported.

#### **OPEN DRAIN OUTPUT OPTION**

The device can also be configured to enable an open drain output option for each I/O pin. If desired, more complex equations can be implemented by using multiple open drain outputs with an externally supplied pull-up resistor to emulate an additional OR plane.

#### TTL VERSUS CMOS OUTPUTS

There is a weak pullup provided for CMOS-compatible outputs. This pullup is always active in both 3.3V and 5V modes.

## JTAG/IEEE 1149.1 TESTABILITY

The JTAG/IEEE 1149.1 Standard Boundary Scan architecture is implemented in the iFX740. This feature supports fault isolation testing of board designs at the component level and enhances production testing, field repair, and is ideal for Fault Tolerant applications.

The iFX740 boundary scan support consists of an Instruction Register, a Data Register, scan cells, and associated logic which are accessed through the Test Access Port (TAP). The TAP interface consists of three inputs: Test Mode Select (TMS), Test Data In (TDI) and Test Clock (TCK), and one output: Test Data Out (TDO).

The boundary scan cells of the iFX740 external signals are linked to form a shift register chain for all active pins. This chain provides a path which can be used to shift in test stimulus as well as shift out test response data for inspection.

For example, a continuity test may be performed between two JTAG devices on a circuit board by placing a known value on the output buffers of one de-

Figure 7. SRAM Overall Block Diagram

Figure 8. SRAM Functional Block Diagram

vice while observing the input buffers of the other device. This same technique may be used to perform simple in-circuit functional testing of the iFX740 for prototyping new system designs.

The 4-pin JTAG test interface is also used for standard programming, in-circuit reconfiguration, and incircuit programming.

### **Boundary Scan Instructions**

The iFX740 boundary scan Instruction Register (IR) supports public instruction opcodes, extended instruction opcodes used for the Program/Verify modes, and additional Intel private instructions.

#### **Public Instructions**

#### EXTEST (IR opcode 00000 binary):

The EXTEST instruction drives the output pins to the values contained in the boundary scan cells which allows testing of circuitry external to the iFX740 package, typically for printed circuit board interconnects.

### BYPASS (IR opcode 11111 binary):

The BYPASS instruction selects the one bit ByPass Register, (BPR), to be connected to TDI and TDO.

#### SAMPLE/PRELOAD (IR opcode 00001 binary):

The SAMPLE/PRELOAD instruction is used for two functions. The SAMPLE/PRELOAD instruction 1) allows a snapshot of the values of the pins of the iFX740 in an unobtrusive manner and 2) preloads data to the iFX740 pins to be driven to the system circuit board when executing the EXTEST instruction.

#### IDCODE (IR opcode 00010 binary):

The IDCODE instruction selects the ID code register to be connected to TDI and TDO allowing the IDcode to be serially shifted out of TDO.

#### **UESCODE (IR opcode 10110 binary):**

The UESCODE instruction selects the User Electronic Signature (UES) register to be connected to TDI and TDO allowing the UES code to be serially shifted out of TDO.

#### HIZ (IR opcode 01000 binary):

The HIZ instruction sets all I/Os to a high impedance state.

## ADVANCE INFORMATION

## IN-CIRCUIT RECONFIGURATION

The iFX740 supports in-circuit reconfiguration and in-circuit programming through the use of the 4-pin JTAG test port. Downloading a new configuration can be accomplished by simply shifting the new data into the device.

This may be done as many times as desired in a prototyping scenario. Once the final version of the design is confirmed it may be programmed into the non-volatile cells so that the configuration will not be lost even when the power is turned off. This is also done through the use of the JTAG test port plus the programming voltage pin (V<sub>PP</sub>).

For more details on in-circuit reconfiguration and programming please refer to the iFX740 Device Programming and In-Circuit Reconfiguration Specification and supporting application notes.

#### SECURITY

A programmable security bit controls access to the data programmed into the device. Once this security bit is set, the design cannot be read out of the non-volatile cells or the SRAM. The state of the non-volatile security bit at power-up determines access and cannot be changed by in-circuit reconfiguration.

#### SOFTWARE SUPPORT

#### **PLDshell Plus**

PLDshell Plus is a sophisticated development tool for Intel programmable logic and is all you need to begin designing with Intel FPGAs. With PLDshell Plus, you can develop, compile, and simulate efficient designs for Intel FPGAs and PLDs.

PLDshell Plus includes several enhancements over earlier versions:

- -Design Merge

- -SRAM Configuration Support

- -Compare Operation Support

- -Simulation Support for Intel FPGA

- -Vector Notation

- -Full Mouse Support

- -Device Selector

#### **DESIGN MERGE**

PLDshell Plus can merge multiple PDS design files into any Intel PLD, including the Intel iFX740. The Merge function makes it easy for designers to consolidate multiple PLDs into a single, high-performance FPGA or PLD.

#### FPGA ARCHITECTURAL FEATURE SUPPORT

PLDshell Plus supports all of the innovative architectural features of the iFX740 through the implementation of new language syntax such as:

- SRAM configuration

- Compare operation

- Buried macrocells

- Clocking options

- 3.3V and 5V options

#### **FUNCTIONAL SIMULATION**

PLDshell Plus allows the designer to simulate the internal function of any Intel FPGA or PLD for rapid design verification.

PLDshell Plus provides the following simulation capabilities:

- Event-driven simulation of combinatorial, registered, and state machine designs

- Ability to set any input, preload any register, and compare any output against an expected value

- Ability to group signals together (form a vector) to simulate a bus

- Generation of test vectors from simulation results for inclusion in the JEDEC file

- Simulation history file with ability to output a subset of signals to a secondary trace file

#### **DEVICE SELECTOR**

The designer can develop the logic design first, and then use the PLDshell Plus device selector to pick a list of appropriate devices. After a design is compiled or estimated through PLDshell Plus a report file is generated. Contained in the report file is a listing of suggested devices appropriate for the target design.

#### SYSTEM REQUIREMENTS

Listed below are the minimum requirements for a system in order to use PLDshell Plus:

- Intel 386 based PC compatible

- 4MB RAM (minimum)

- VGA monitor/adaptor

- DOS 3.1 (or later)

# THIRD-PARTY SUPPORT DESIGN SOFTWARE

Third party tools support will be provided by the following vendors:

#### Cadence

- Composer\*: Comprehensive suite of design entry, debug and documentation capabilities.

- Verilog-XL\*: Digital logic simulator and interactive debug environment.

#### Data I/O

ABEL\*: Design software allowing you to describe and implement logic designs.

#### Logical Devices

CUPL\*: High level, universal design software package.

#### Mentor Graphics

- Design Architect\*: Integrated system of schematic, symbol, and text editors for capturing designs.

- QuickSim\*: High performance logic simulator for function and performance verification.

#### Minc

PLDesigner-XL\*: Powerful design tool that can be used for all types of programmable logic with automatic device selection, automatic partitioning and functional simulation.

#### OrCAD

- PLD Tools\* Schematic Design Tool\*: Software tool environment including schematic entry, test vector generation and multiple forms of input.

- Verification/Simulation Tool\*: Series of software tools for performing timing-based simulation of designs.

#### Viewlogic

ViewPLD\* & Powerview\*: Integrated schematic capture and simulation environment.

## PROGRAMMING SUPPORT

Programming Support will be provided by a number of leading vendors, such as:

- Products in Motion (916) 363-0571

PROTAG JTAG Programmer

- BP Microsystems

PLD 1100

- Data I/O-Unisite-2900/3900

- Elan -Model 6000

- Advin Systems Inc

PILOT-U84

PILOT-U40

- Logical Devices

ALLPRO

- SMSSprint Plus

## **DEVICE MODELS**

Simulation models will be provided by the following vendors:

Logic Modeling Corporation

Smart Model: Device model support for behavioral simulation through a variety of simulators.

Viewlogic

## ORDERING INFORMATION

| f <sub>CNT1</sub><br>(MHz) | F <sub>MAX</sub><br>(MHz) | t <sub>PD</sub><br>(ns) | I <sub>SB</sub><br>(mA) | Icc<br>(mA/MHz) | Order Code   | Package     |

|----------------------------|---------------------------|-------------------------|-------------------------|-----------------|--------------|-------------|

| 80                         | 100                       | 10                      | 20                      | 1.0             | N68FX740-10  | 68-Pin PLCC |

|                            |                           |                         |                         |                 | N44FX740-10  | 44-Pin PLCC |

| 50                         | 66.7                      | 15                      | 20                      | 1.0             | N68FX740-15  | 68-Pin PLCC |

|                            |                           |                         |                         |                 | N44FX740-15  | 44-Pin PLCC |

| 80                         | 100                       | 10                      | 1                       | 1.0             | N68FX740Z-10 | 68-Pin PLCC |

|                            |                           |                         |                         |                 | N44FX740Z-10 | 44-Pin PLCC |

| 50                         | 66.7                      | 15                      | 1                       | 1.0             | N68FX740Z-15 | 68-Pin PLCC |

|                            |                           |                         |                         |                 | N44FX740Z-15 | 44-Pin PLCC |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage $(V_{CC})^{(1)}$ 2.0V to +7.0V                    |

|------------------------------------------------------------------|

| Programming Supply                                               |

| Voltage (V <sub>PP</sub> )(1)2.0V to +13.5V                      |

| DC Input Voltage $(V_1)^{(1, 2)} \dots -0.5V$ to $V_{CC} + 0.5V$ |

| Storage Temperature (t <sub>stg</sub> )65°C to +150°C            |

| Ambient Temperature (t <sub>amb</sub> )(3) 10°C to +85°C         |

#### NOTES:

- 1. Voltages with respect to ground.

- 2. Minimum DC input is -0.5V. During transitions, the inputs may undershoot to -2.0V or overshoot to +7.0V for periods less than 20 ns under no load conditions.

- Under bias. Extended temperature versions are also available.

NOTICE: This data sheet contains information on products in the sampling and initial production phases of development. The specifications are subject to change without notice. Verify with your local Intel Sales office that you have the latest data sheet before finalizing a design.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

| Symbol                            | Parameter                   | Min  | Max  | Units |

|-----------------------------------|-----------------------------|------|------|-------|

| V <sub>CC</sub> /V <sub>CCO</sub> | Supply Voltage -5V          | 4.75 | 5.25 | V     |

| V <sub>CCO</sub>                  | Output Supply Voltage -3.3V | 3.0  | 3.6  | ٧     |

| V <sub>IN</sub>                   | Input Voltage               | 0    | Vcc  | ٧     |

| V <sub>O</sub>                    | Output Voltage              | 0    | Vcco | ٧     |

| T <sub>A</sub>                    | Operating Temperature       | 0    | + 70 | °C    |

| t <sub>R</sub>                    | Input Rise Time             |      | 500  | ns    |

| t <sub>F</sub>                    | Input Fall Time             |      | 500  | ns    |

## D.C. CHARACTERISTICS ( $T_A = 0$ °C to +70°C, $V_{CC} = 5.0 V \pm 5\%$ )(4)

| Symbol              | Parameter                    | Min                  | Тур | Max                   | Units | Test Conditions                                                   |

|---------------------|------------------------------|----------------------|-----|-----------------------|-------|-------------------------------------------------------------------|

| V <sub>IH</sub> (5) | High Level Input Voltage     | 2.0                  |     | V <sub>CC</sub> + 0.3 | V     |                                                                   |

| V <sub>IL</sub> (5) | Low Level Input Voltage      | -0.3                 |     | 0.8                   | V     |                                                                   |

| V <sub>OH</sub>     | 5V TTL High Level Output     | 2.4                  |     |                       | ٧     | $1/O = -4.0 \text{ mA D.C.}, V_{CC} = \text{Min.}$                |

|                     | 5V CMOS High Level Output    | V <sub>CC</sub> -0.2 |     |                       | V     | $I/O = -20 \mu A  D.C.,  V_{CC} = Min.$                           |

|                     | 3V High Level Output Voltage | V <sub>CC</sub> -0.2 |     |                       | ٧     | $I/O = -20 \mu\text{A D.C.}, V_{CC} = \text{Min.}$                |

| VOL                 | 5V Low Level Output Voltage  |                      |     | 0.45                  | ٧     | I/O = 12 mA D.C., V <sub>CC</sub> = Min.                          |

|                     | 3V Low Level Output Voltage  |                      |     | 0.2                   | ٧     | I/O = 20 μA D.C., V <sub>CC</sub> = Min.                          |

| (10)                | input Leakage Current        |                      |     | ±10                   | μΑ    | V <sub>CC</sub> = Max., V <sub>IN</sub> = GND or V <sub>CC</sub>  |

| loz                 | Output Leakage Current       |                      |     | ± 50                  | μΑ    | V <sub>CC</sub> = Max., V <sub>OUT</sub> = GND or V <sub>CC</sub> |

| I <sub>SC</sub> (6) | Output Short Circuit Current | -30                  |     | - 120                 | mA    | V <sub>CC</sub> = Max., V <sub>OUT</sub> = 0.5V                   |

## **D.C. CHARACTERISTICS** ( $T_A = 0^{\circ}\text{C to } + 70^{\circ}\text{C}, V_{CC} = 5.0\text{V } \pm 5\%$ )(4) (Continued)

| Symbol          | Parameter                              | Min | Тур | Max | Units            | Test Conditions                                                                         |

|-----------------|----------------------------------------|-----|-----|-----|------------------|-----------------------------------------------------------------------------------------|

| I <sub>SB</sub> | Standby Power Supply<br>Current FX740  |     | 20  |     | mA               | V <sub>IN</sub> = V <sub>CC</sub> or GND, Outputs Open                                  |

|                 | Standby Power Supply<br>Current FX740Z |     | 1   |     | mA               |                                                                                         |

| ICC<br>Active   | Power Supply Current<br>FX740          |     | 1   |     | mA<br>per<br>MHz | V <sub>IN</sub> = V <sub>CC</sub> or GND,<br>Device Programmed a Two 20-Bit<br>Counters |

|                 | Power Supply Current<br>FX740Z         |     | 1   |     | mA<br>per<br>MHz |                                                                                         |

#### NOTES:

- 4. Typical values are at  $T_A = 25$ °C,  $V_{CC} = 5$ V.

- 5. Absolute values with respect to device GND; all over and undershoots due to system and tester noise are included. Do not attempt to test these values without suitable equipment.

- 6. Not more than 1 output should be tested at a time. Duration of that test should not exceed 1 second.

- 10. Input leakage current on JTAG pins:  $\pm 25 \mu A$ .

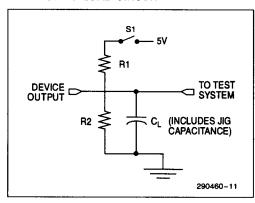

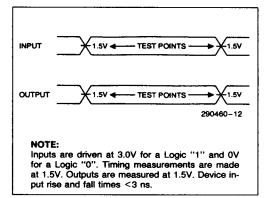

#### A.C. TESTING LOAD CIRCUIT

#### A.C. TESTING INPUT, OUTPUT WAVEFORM

## SWITCHING TEST CIRCUIT

| Specification    | S1                           |            | Commercial |      | Manager de la constant                                                                                  |

|------------------|------------------------------|------------|------------|------|---------------------------------------------------------------------------------------------------------|

| Specification    | 5.                           | CL         | R1         | R2   | Measured Output Value                                                                                   |

| t <sub>PD</sub>  | Closed                       |            |            |      | 1.5V                                                                                                    |

| <sup>t</sup> PZX | Z → H: Open<br>Z → L: Closed | 35 pF 330Ω | 330Ω       | 200Ω | 1.5V                                                                                                    |

| t <sub>PXZ</sub> | H → Z: Open<br>L → Z: Closed | 5 pF       |            |      | $\begin{array}{c} H \longrightarrow Z: V_{OH} - 0.5V \\ L \longrightarrow Z: V_{OL} + 0.5V \end{array}$ |

## PIN CAPACITANCE ( $T_A = 0$ °C to +70°C, $V_{CC} = 5.0 V \pm 5\%$ )(7)

| Symbol           | Parameter                       | Conditions                         | Min | Тур | Max | Units |

|------------------|---------------------------------|------------------------------------|-----|-----|-----|-------|

| C <sub>IN</sub>  | Input Capacitance               | V <sub>IN</sub> = 2V, f = 1.0 MHz  |     | 10  | 12  | pF    |

| C <sub>IO</sub>  | I/O Capacitance                 | V <sub>OUT</sub> = 2V, f = 1.0 MHz |     | 12  | 15  | pF    |

| C <sub>CLK</sub> | Clock Pin Capacitance           | V <sub>OUT</sub> = 2V, f = 1.0 MHz |     | 15  | 18  | pF    |

| C <sub>VPP</sub> | V <sub>PP</sub> Pin Capacitance | f = 1.0 MHz                        |     | 12  | 15  | pF    |

#### NOTES:

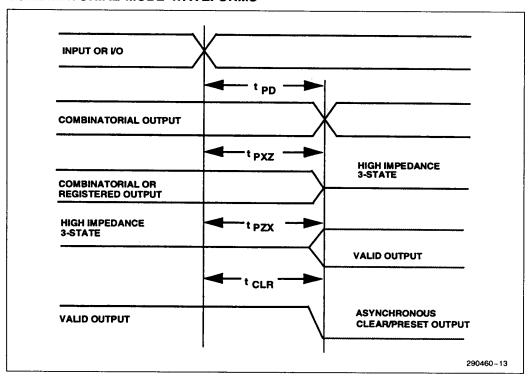

## **COMBINATORIAL MODE A.C. CHARACTERISTICS**

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C, V_{CC} = 5.0V \pm 5\%)$

| Symbol               | Parameter                                        |  | -10 |     |     | -15 |     |       |

|----------------------|--------------------------------------------------|--|-----|-----|-----|-----|-----|-------|

|                      |                                                  |  | Тур | Max | Min | Тур | Max | Units |

| t <sub>PD</sub>      | Input or I/O to Output Valid                     |  |     | 10  |     |     | 15  | ns    |

| t <sub>PZX</sub> (8) | Input or I/O to Output Enable                    |  |     | 12  |     |     | 18  | ns    |

| t <sub>PXZ</sub> (8) | Input or I/O to Output Disable                   |  |     | 12  |     |     | 18  | ns    |

| t <sub>CLR</sub>     | Input or I/O to Asynchronous Clear/Preset        |  |     | 15  |     |     | 20  | ns    |

| <sup>t</sup> COMP    | Comparator Input or I/O Feedback to Output Valid |  |     | 10  |     |     | 15  | ns    |

<sup>7.</sup> These values are evaluated at initial characterization and whenever design modifications occur that may affect capacitance.

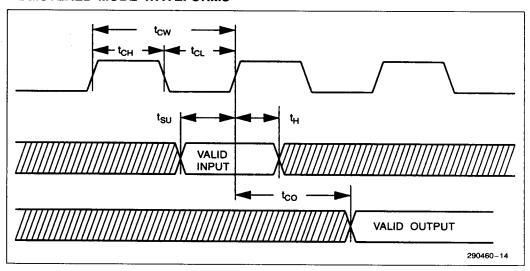

### REGISTER MODE—IFX740Z-10 CLOCK A.C. CHARACTERISTICS

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C, V_{CC} = 5.0V \pm 5\%)$

| Symbol            | So-ro-motor:                                                                            | Synch | ronous | Delaye | Delayed Sync |      | ync  | T     |

|-------------------|-----------------------------------------------------------------------------------------|-------|--------|--------|--------------|------|------|-------|

| Symbol            | Parameter                                                                               | Min   | Max    | Min    | Max          | Min  | Max  | Units |

| <sup>f</sup> CNT1 | Max Counter Frequency<br>1/(t <sub>SU</sub> + t <sub>CO1</sub> ) -<br>External Feedback | 83.3  |        | 80     |              | 71.4 |      | MHz   |

| fCNT2             | Max Counter Frequency<br>1/(t <sub>CNT</sub> ) - Internal Feedback                      | 83.3  |        | 80     |              | 74.1 |      | MHz   |

| f <sub>MAX</sub>  | Max Frequency (Pipelined) 1/(t <sub>CP</sub> ) - No Feedback                            | 100   |        | 92.9   |              | 80   |      | MHz   |

| tsu               | Input or I/O Setup Time to CLK                                                          | 6     |        | 4.5    |              | 2    |      | ns    |

| t <sub>H</sub>    | Input or I/O Hold Time from CLK                                                         | 0     |        | 2      |              | 5    |      | ns    |

| <sup>‡</sup> CO1  | CLK to Output Valid                                                                     |       | 6      |        | 8            |      | 12   | ns    |

| t <sub>CO2</sub>  | CLK to Output Valid Fed Through<br>Combinatorial Macrocell                              |       | 16     |        | 18           |      | 22   | ns    |

| tCNT              | Register Output Feedback to<br>Register Input—Internal Path                             |       | 12     |        | 12.5         |      | 13.5 | ns    |

| t <sub>CL</sub>   | CLK Low Time                                                                            | 4.5   |        | 4.5    |              | 5    |      | ns    |

| <sup>t</sup> CH   | CLK High Time                                                                           | 4.5   |        | 4.5    |              | 5    |      | ns    |

| t <sub>CP</sub>   | CLK Period                                                                              | 10    |        | 10.5   |              | 12.5 |      | ns    |

## REGISTER MODE—IFX740-10 CLOCK A.C. CHARACTERISTICS

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C, V_{CC} = 5.0V \pm 5\%)$

| Cumbal           | Powerstan                                                                               | Synch | ronous | Delaye | Delayed Sync |      | ync  | 1     |

|------------------|-----------------------------------------------------------------------------------------|-------|--------|--------|--------------|------|------|-------|

| Symbol           | Parameter M                                                                             | Min   | Max    | Min    | Max          | Min  | Max  | Units |

| fCNT1            | Max Counter Frequency<br>1/(t <sub>SU</sub> + t <sub>CO1</sub> ) -<br>External Feedback | 80    |        | 76.9   |              | 71.4 |      | MHz   |

| fCNT2            | Max Counter Frequency<br>1/(t <sub>CNT</sub> ) - Internal Feedback                      | 80    |        | 76.9   |              | 71.4 |      | MHz   |

| f <sub>MAX</sub> | Max Frequency (Pipelined)<br>1/(t <sub>CP</sub> ) - No Feedback                         | 100   |        | 92.9   |              | 80   |      | MHz   |

| tsu              | Input or I/O Setup Time to CLK                                                          | 6     |        | 4.5    |              | 2    |      | ns    |

| t <sub>H</sub>   | Input or I/O Hold Time from CLK                                                         | 0     |        | 2      |              | 5    |      | ns    |

| t <sub>CO1</sub> | CLK to Output Valid                                                                     |       | 6.5    |        | 8.5          |      | 12   | ns    |

| t <sub>CO2</sub> | CLK to Output Valid Fed Through<br>Combinatorial Macrocell                              |       | 16.5   |        | 18.5         |      | 22.5 | ns    |

| tCNT             | Register Output Feedback to<br>Register Input—Internal Path                             |       | 12.5   |        | 13           | ,    | 14   | ns    |

| t <sub>CL</sub>  | CLK Low Time                                                                            | 4.5   |        | 4.5    |              | 5    |      | ns    |

| <sup>t</sup> CH  | CLK High Time                                                                           | 4.5   |        | 4.5    |              | 5    |      | ns    |

| t <sub>CP</sub>  | CLK Period                                                                              | 10    |        | 10.5   |              | 12.5 |      | ns    |

#### NOTE:

8. Tp<sub>ZX</sub> and t<sub>PXZ</sub> are measured at  $\pm 0.5V$  from steady state voltage as driven by specified output load. t<sub>PXZ</sub> is measured with A C<sub>L</sub> = 5 pF. Z  $\rightarrow$  H and Z  $\rightarrow$  L are measured at 1.5V on output.

ADVANCE INFORMATION

## REGISTER MODE—iFX740-15/iFX740Z-15 CLOCK A.C. CHARACTERISTICS

$(T_A = 0^{\circ}C \text{ to } +70^{\circ}C, V_{CC} = 5.0V \pm 5\%)$

| Symbol           | Parameter                                                                               | Synch | ronous | Delaye | Delayed Sync |      | ync |       |

|------------------|-----------------------------------------------------------------------------------------|-------|--------|--------|--------------|------|-----|-------|

| - Symbol         | Farameter                                                                               | Min   | Max    | Min    | Max          | Min  | Max | Units |

| fCNT1            | Max Counter Frequency<br>1/(t <sub>SU</sub> + t <sub>CO1</sub> ) -<br>External Feedback | 50    |        | 50     |              | 50   |     | MHz   |

| fCNT2            | Max Counter Frequency<br>1/(t <sub>CNT</sub> ) - Internal Feedback                      | 50    |        | 50     |              | 50   |     | MHz   |

| f <sub>MAX</sub> | Max Frequency (Pipelined)<br>1/(t <sub>CP</sub> ) - No Feedback                         | 66.7  |        | 62.5   |              | 62.5 |     | MHz   |

| tsu              | Input or I/O Setup Time to CLK                                                          | 11    |        | 8      |              | 3    |     | ns    |

| t <sub>H</sub>   | Input or I/O Hold Time from CLK                                                         | 0     |        | 2      |              | 6    |     | ns    |

| t <sub>CO1</sub> | CLK to Output Valid                                                                     |       | 9      |        | 12           |      | 17  | ns    |

| t <sub>CO2</sub> | CLK to Output Valid Fed Through<br>Combinatorial Macrocell                              |       | 24     |        | 27           |      | 32  | ns    |

| <sup>t</sup> CNT | Register Output Feedback to Register Input—Internal Path                                |       | 20     |        | 20           |      | 20  | ns    |

| t <sub>CL</sub>  | CLK Low Time                                                                            | 7     |        | 7      |              | 7    |     | ns    |

| t <sub>CH</sub>  | CLK High Time                                                                           | 7     |        | 7      |              | 7    |     | ns    |

| t <sub>CP</sub>  | CLK Period                                                                              | 15    |        | 15     |              | 15   |     | ns    |

## **COMBINATORIAL MODE WAVEFORMS**

## REGISTERED MODE WAVEFORMS

advance information

2-17

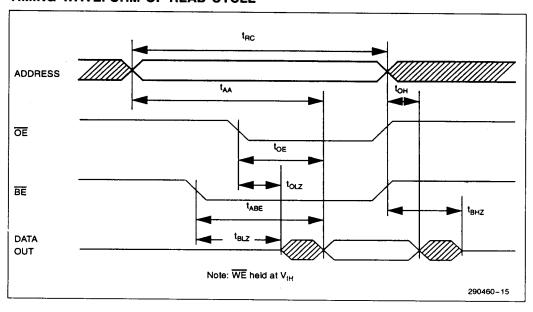

SRAM READ—A.C. CHARACTERISTICS ( $T_A = 0$ °C to +70°C,  $V_{CC} = 5.0 V \pm 5\%$ )

| Symbol                  | Parameter                         | -10 |     | -15 |     |       |

|-------------------------|-----------------------------------|-----|-----|-----|-----|-------|

|                         |                                   | Min | Max | Min | Max | Units |

| t <sub>RC</sub>         | Read Cycle Time                   | 15  |     | 20  |     | ns    |

| t <sub>AA</sub>         | Address Access Time               |     | 15  |     | 20  | ns    |

| t <sub>ABE</sub>        | Block Enable Access Time          |     | 15  |     | 20  | ns    |

| t <sub>OE</sub> (1)     | Output Enable to Output Valid     |     | 12  |     | 15  | ns    |

| toH                     | Output Hold from Address Change   | 2   |     | 3   |     | ns    |

| t <sub>BLZ</sub> (1)    | Block Enable to Output in Low Z   | 3   |     | 5   |     | ns    |

| t <sub>BHZ</sub> (1, 2) | Block Disable to Output in High Z |     | 10  |     | 15  | ns    |

| toLZ <sup>(1)</sup>     | Output Enable to Output in Low Z  | 3   |     | 5   |     | ns    |

## TIMING WAVEFORM OF READ CYCLE

## SRAM WRITE—A.C. CHARACTERISTICS ( $T_A = 0$ °C to +70°C, $V_{CC} = 5.0V \pm 5$ %)

| Symbol                     | Parameter                       | -10 |     | -15 |     | T     |

|----------------------------|---------------------------------|-----|-----|-----|-----|-------|

|                            | Faianietei                      | Min | Max | Min | Max | Units |

| twc                        | Write Cycle Time                | 15  |     | 20  |     | ns    |

| t <sub>BW</sub>            | Block Enable to End of Write    | 10  |     | 13  |     | ns    |

| t <sub>AW</sub>            | Address Valid to End of Write   | 13  |     | 17  |     | ns    |

| t <sub>AS</sub>            | Address Set-up Time             | 3   |     | 4   |     | ns    |

| t <sub>WP</sub>            | Write Pulse Width               | 10  |     | 13  |     | ns    |

| twR                        | Write Recovery Time             | 2   |     | 3   |     | ns    |

| t <sub>DW</sub>            | Data Valid to End of Write      | 10  |     | 13  |     | ns    |

| t <sub>DH</sub>            | Data Hold Time                  | 2   |     | 3   |     | ns    |

| t <sub>OHZ</sub> (1, 2, 3) | Output Disable to Valid Data In | 10  |     | 13  |     | ns    |

#### NOTES:

- 1. These signals are measured at  $\pm 0.5$ V from steady state voltage as driven by specified output load. Z  $\rightarrow$  H and Z  $\rightarrow$  L are measured at 1.5V on output.

- 2. These signals are measured with C<sub>L</sub> = 5 pF.

- 3. Does not apply for separate data in and data out buses.

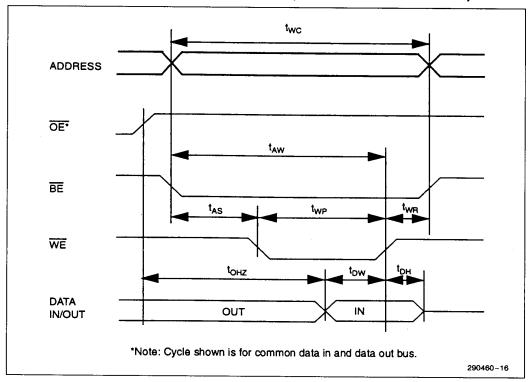

## TIMING WAVEFORM OF WRITE CYCLE #1 (WE CONTROLLED TIMING)

ADVANCE INFORMATION

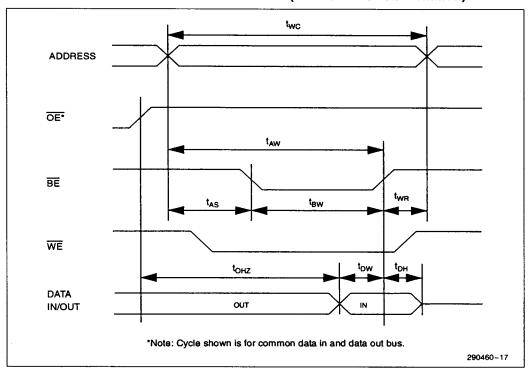

## TIMING WAVEFORM OF WRITE CYCLE #2 (BE CONTROLLED TIMING)

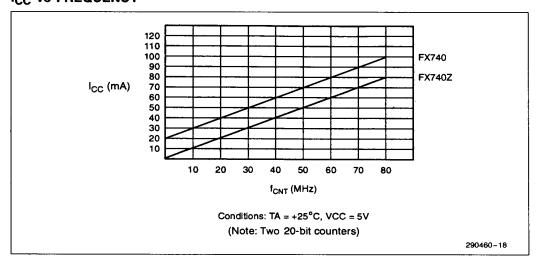

## I<sub>CC</sub> vs FREQUENCY

## **POWER-UP RESET**

Because  $V_{CC}$  rise can vary significantly from one application to another,  $V_{CC}$  rise must be monotonic. The power-up cycle is complete within a delay of  $t_{PR}$  after  $V_{CC}$  reaches the  $V_{ON}$  value.

Internal power-up reset circuits ensure that all flipflops will be reset to a logic 0 after the device has powered-up. Also, the JTAG TAP controller will be put into the *Test-Logic-Reset* state. The outputs on an unprogrammed device will power-up in a high impedance state.

# POWER-UP RESET CHARACTERISTICS

| Symbol          | Parameter           | Value      |  |  |

|-----------------|---------------------|------------|--|--|

| t <sub>PR</sub> | Power-Up Reset Time | 100 μs Max |  |  |

| V <sub>ON</sub> | Turn-On Voltage     | 4.75V Min  |  |  |

## **PIN DESCRIPTIONS**

Table 4 lists the dedicated pin names and descriptions.

#### Table 4. Dedicated Pins

| Pin<br>Name     | Description                                                                                                                                                                                                                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc             | Supply voltage for the iFX740. All must be connected to 5V.                                                                                                                                                                                                                                                      |

| V <sub>SS</sub> | Ground connections for the iFX740. All must be connected to GND.                                                                                                                                                                                                                                                 |

| V <sub>PP</sub> | Programming voltage for the iFX740. During programming, 12.75V must be supplied to this pin. When not in programming mode, this pin may be connected to V <sub>CC</sub> , V <sub>PP</sub> or left floating (not GND).                                                                                            |

| INx             | Input only pins. These pins may not be available on all packages. Unused inputs should be connected to $V_{CC}$ or GND.                                                                                                                                                                                          |

| TDI             | The Testability Data input is the boundary scan serial data input to the iFX740. JTAG instructions and data are shifted into the iFX740 on the TDI input pin on the rising edge of TCK. TDI may be left floating if unused.                                                                                      |

| TDO             | The Testability Data Output is the boundary scan serial data output from the iFX740. JTAG instructions and data are shifted out of the iFX740 on the TDO output on the failing edge of TCK.                                                                                                                      |

| TCK             | The Testability Clock input provides the boundary scan clock for the iFX740. TCK is used to clock state information and data into and out of the iFX740 during boundary scan or programming modes. The maximum operating frequency of the boundary scan test clock is 8 MHz. TCK may be left floating if unused. |

| TMS             | The Testability Control input is the boundary scan test mode select for the iFX740. TMS may be left floating if unused.                                                                                                                                                                                          |

Table 5 lists the user-defined pin names and descriptions.

## Table 5. User-defined Pins

| Pin<br>Name       | Description                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| V <sub>CCOx</sub> | Supply voltage for the outputs of the CFBs. Connecting these pins to $+5$ V causes the CFB to output 5V signals. Connecting these pins to $+3.3$ V causes the CFB to output 3.3V signals. These pins must always be connected to the desired output drive voltage. |  |  |  |  |  |

| CLKx              | Global clocks.                                                                                                                                                                                                                                                     |  |  |  |  |  |

| I/Oxx             | Pins that can be configured either as an input or an output. Unused I/O pins should be connected to $V_{CC}$ or GND.                                                                                                                                               |  |  |  |  |  |

ADVANCE INFORMATION

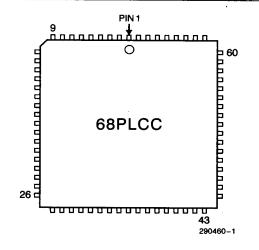

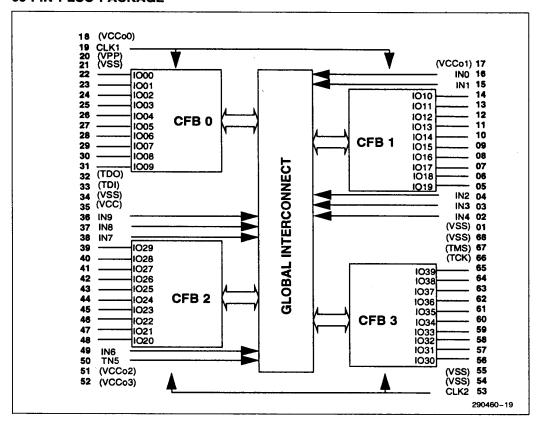

## **68-PIN PLCC PACKAGE**

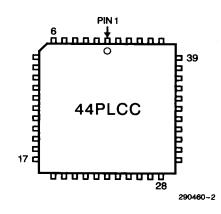

## **44-PIN PLCC PACKAGE**