## Philips Components-Signetics

| Document No.    | 853-0136              |  |  |

|-----------------|-----------------------|--|--|

| ECN No.         | 86487                 |  |  |

| Date of issue   | November 11, 1986     |  |  |

| Status          | Product Specification |  |  |

| Memory Products |                       |  |  |

#### DESCRIPTION

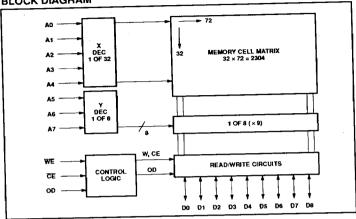

The organization of the 82S212 and 82S212A allow byte wide storage of data, including parity. Where parity is not required, the ninth bit can be used as a tag for each word stored. The 82S212 and 82S212A are ideal for scratch pads, push down stacks, buffer memories, and other internal memory applications in which space and performance requirements dictate a wide data path in favor of word depth.

Data inputs and outputs are common (common I/O) with separate output disable (OD) line that allows ease of Read/Write operations using a common bus.

Ordering information can be found on the following page.

The 82S212 and 82S212A devices are also processed to military requirements for operation over the military temperature range. For specifications and ordering information consult the Signetics Military Data Handbook.

#### **FEATURES**

- Address access time:

- N82S212: 45ns max

- N82S212A: 35ns max

- Power dissipation: 0.3mW/bit typ

- Schottky clamped TTL

- One Chip Enable input

- Common I/O

- Inputs: PNP Buffered

- Outputs: 3-State

# 82S212 82S212A 2304-bit TTL bipolar RAM

### **APPLICATIONS**

- · Cache memory

- Buffer storage

- · Writable control store

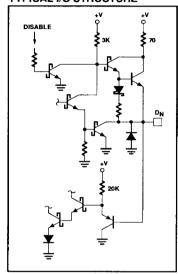

## **TYPICAL I/O STRUCTURE**

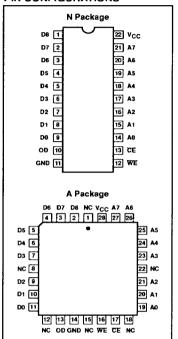

### **PIN CONFIGURATIONS**

# 2304-bit TTL bipolar RAM (256 imes 9)

# **BLOCK DIAGRAM**

# ORDERING INFORMATION

| ADEAING IN CHIMATION                                |                       |  |  |

|-----------------------------------------------------|-----------------------|--|--|

| DESCRIPTION                                         | ORDER CODE            |  |  |

| 22-Pin Plastic Dual-In-Line<br>400mil-wide          | N82S212 N, N82S212A N |  |  |

| 28-Pin Plastic Leaded Chip Carrier<br>450mil-square | N82S212 A, N82S212A A |  |  |

# **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                   | RATING      | UNIT            |  |

|------------------|-----------------------------|-------------|-----------------|--|

| V <sub>CC</sub>  | Supply voltage              | +7.0        | V <sub>DC</sub> |  |

| V <sub>IN</sub>  | Input voltage               | +5.5        | V <sub>DC</sub> |  |

| V <sub>OH</sub>  | Output voltage High         | +5.5        | V <sub>DC</sub> |  |

| <del>-</del>     | Operating temperature range | 0 to +75    | °C              |  |

| T <sub>stq</sub> | Storage temperature range   | -65 to +150 | °C              |  |

# 2304-bit TTL bipolar RAM (256 $\times$ 9)

## 82S212 / 82S212A

135

5

8

185

mΑ

ρF

pΕ

# DC ELECTRICAL CHARACTERISTICS $0^{\circ}C \le T_{amb} \le +75^{\circ}C$ , $4.75V \le V_{CC} \le 5.25V$

LIMITS SYMBOL **PARAMETER TEST CONDITIONS** UNIT TYP1 MIN MAX Input voltage<sup>2</sup>  $V_{IL}$  $V_{CC} = 4.75V$ ٧ V<sub>CC</sub> = 5.25V  $V_{\text{IH}}$ High 2.0 ν V<sub>IC</sub> Clamp3 V<sub>CC</sub> = 4.75V, I<sub>IN</sub> = -12mA -1.5 ٧ Output voltage2 ν V<sub>OH</sub>  $I_{OL} = -2mA$ 2.4 V<sub>CC</sub> = 4.75V, I<sub>OL</sub> = 8.0mA 0.5 ν VOL Low<sup>3</sup> Input current Low  $V_{IN} = 0.45V$ -100 μΑ liH Hiah  $V_{IN} = 5.5V$ 25 uА Output current Hi-Z State CE = High or OD = High, Vout = 5.5V loz 40 μА CE = High or OD = High, V<sub>OUT</sub> = 0.5V μА -100 Short circuit3, 4 CE = OD = Low, VOUT = 0V -15 -70 mΑ los Supply current<sup>5</sup>

$V_{CC} = 5.25V$

$V_{CC} = 5.0V$

$V_{IN} = 2.0V$

$V_{OUT} = 2.0V$

#### CIN COUT NOTES:

lcc

Capacitance

Input

Output

- 1. All typical values are at V<sub>CC</sub> = 5V, T<sub>amb</sub> = +25°C.

2. All voltage values are with respect to network ground terminal.

3. Measured on one pin at a time.

4. Duration of I<sub>OS</sub> test should not exceed one second.

5. I<sub>CC</sub> is measured with the Write Enable and Memory Enable inputs grounded, all other inputs at 0.45V, and the outputs open.

### **TRUTH TABLE**

| MODE           | WE | ÇE | OD | D <sub>N</sub><br>IN/OUT |

|----------------|----|----|----|--------------------------|

| Disable output | ×  | Х  | 1  | Hi-Z                     |

| Disable R/W    | ×  | 1  | ×  | Hi-Z                     |

| Write          | 0  | 0  | 1  | Data in                  |

| Read           | 1  | 0  | 0  | Data out                 |

X = Don't care

## 82S212 / 82S212A

## **AC ELECTRICAL CHARACTERISTICS**

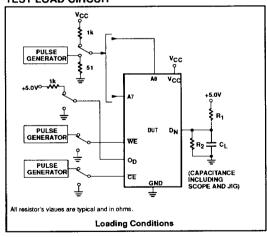

$R_1 = 600\Omega$ ,  $R_2 = 900\Omega$ ,  $C_L = 30pF$ ,  $0^{\circ}C \le T_{amb} \le +75^{\circ}C$ ,  $4.75V \le V_{CC} \le 5.25V$

| SYMBOL                       | PARAMETER <sup>1</sup>           | TO FROM     |             | N82S21 | 2        | N82S212A |     |                  | UNIT |    |

|------------------------------|----------------------------------|-------------|-------------|--------|----------|----------|-----|------------------|------|----|

|                              |                                  |             | -           | MIN    | TYP2     | MAX      | MIN | TYP <sup>2</sup> | MAX  |    |

| Access time                  | e                                |             |             |        |          |          |     |                  |      |    |

| taa                          | Address                          | Output      | Address     |        |          | 45       |     |                  | 35   | ns |

| Enable time                  | 9                                |             |             |        |          |          |     |                  |      |    |

| t <sub>OD</sub>              | Output                           | Output      | OD          | 5      |          | 25       |     |                  | 25   | ns |

| t <sub>CE</sub>              | Output                           | Output      | Chip Enable |        | <u> </u> | 25       |     | İ                | 25   | ns |

| Disable tim                  | e <sup>3</sup>                   |             |             |        |          |          |     |                  |      |    |

| top                          | Output                           | Output      | OD          | 1      |          | 25       |     |                  | 25   | ns |

| <b>t</b> CD                  | Output                           | Output      | Chip Enable |        |          | 25       |     | <u> </u>         | 25   | ns |

| Pulse width                  | 1                                |             |             |        |          |          |     |                  |      |    |

| t <sub>WP</sub> <sup>4</sup> | Write                            |             |             | 25     |          |          | 25  | 1                | l    | ns |

| Setup and                    | hold time                        |             |             |        |          |          |     |                  | _    |    |

| twsc                         | Setup time                       | Write       | Chip Enable | 5      |          |          | 5   |                  |      | ns |

| twec                         | Hold time                        | Chip Enable | Write       | 5      |          |          | 5   | <u> </u>         |      | ns |

| twsp                         | Setup time                       | Write       | Data        | 25     |          |          | 25  |                  |      | ns |

| twHD                         | Hold time                        | Data        | Write       | 5      |          | <u> </u> | 5   |                  | ļ    | ns |

| twsa <sup>5</sup>            | Setup time                       | Write       | Address     | 5      |          | 1        | 5   |                  |      | ns |

| twhA                         | Hold time                        | Address     | Write       | 5      | <u> </u> | L        | 5   | <u> </u>         |      | ns |

| tso                          | Setup time (from disabled state) | Chip Enable | OD          | 5      | 1        |          | 5   |                  |      | ns |

| t <sub>HO</sub>              | Hold time                        | OD          | Chip Enable | 5      | l        | 1        | 5   | I                | l    | ns |

### NOTES:

- 1. The operating ambient tempeature ranges are guaranteed with transverse air flow exceeding 400 linear feet per minute and a 2-minute warmup.

- warmup. 2. All typical values are at  $V_{CC}$  = 5V,  $T_{amb}$  = +25°C. 3. Measured at a delta of 0.5V from Logic level with  $R_1$  = 750 $\Omega$ ,  $R_2$  = 750 $\Omega$  and  $C_L$  = 5pF.

- Measured with minimum twsa.

- 5. Measured with minimum two

## **TEST LOAD CIRCUIT**

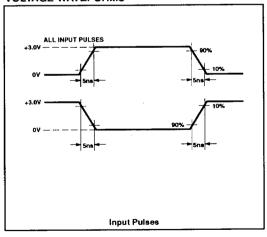

### **VOLTAGE WAVEFORMS**

265

# 2304-bit TTL bipolar RAM (256 $\times$ 9)

# TIMING DIAGRAMS OD \* top\* **toF** tco. VOH VALID DATA OUT VOL NOTE: Assumes tAA from address to valid data W = High. Enable/Disable +3.07 DOUT Read Mode +3.0V tuci +3.0V CE 0**V** ₽WHC WSC\* +3.07 1.5V twsa. Vон Hi-Z Hi-Z VALID DATA IN VOL twHD +3.0V 1.5V ٥V Data Bus conflict can occur with $\overline{\text{CE}}$ = 0, apply data source after t<sub>OD</sub> (max) and remove data source before tOE (min). Write Mode

### **MEMORY TIMING DEFINITIONS**

| SYMBOL           | PARAMETER                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| t <sub>AA</sub>  | Delay between beginning of<br>valid Address (with Chip<br>Enable Low) and when Data<br>Output becomes valid.    |

| t <sub>OE</sub>  | Delay between beginning of<br>Output Disable Low (with<br>Address valid) and when Data<br>Output becomes valid. |

| t <sub>CE</sub>  | Delay between beginning of<br>Chip Enable Low (with<br>Address valid) and when Data<br>Output becomes valid.    |

| t <sub>OD</sub>  | Delay between when Output<br>Disable becomes High and<br>Data Output is in Off-State.                           |

| t <sub>CD</sub>  | Delay between when Chip<br>Enable becomes High and<br>Data Output is in Off-State.                              |

| t <sub>WP</sub>  | Width of Write Enable pulse.                                                                                    |

| twsc             | Required delay between<br>beginning of valid Chip<br>Enable and beginning of Write<br>Enable pulse.             |

| t <sub>WHD</sub> | Required delay between end<br>of Write Enable pulse and end<br>of valid input data.                             |

| t <sub>WSD</sub> | Required delay between<br>beginning of valid Data Input<br>and end of Write Enable<br>pulse.                    |

| t <sub>WHD</sub> | Required delay between end of Write Enable pulse and end of valid input data.                                   |

| lwsa             | Required delay between<br>beginning of valid Address<br>and beginning of Write Enable<br>pulse.                 |

| twhA             | Required delay between end<br>of Write Enable pulse and end<br>of valid Address.                                |

| t <sub>so</sub>  | Set-up time between OD going High and CE going Low.                                                             |

| t <sub>HO</sub>  | Hold time for OD after CE goes High.                                                                            |