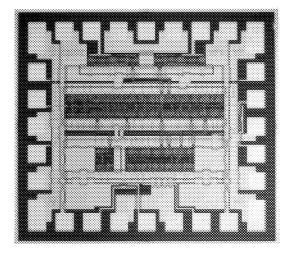

# **Oki Semiconductor**

# **GHDD4414**

**Decision Circuit with Phase Detectors**

#### **GENERAL DESCRIPTION**

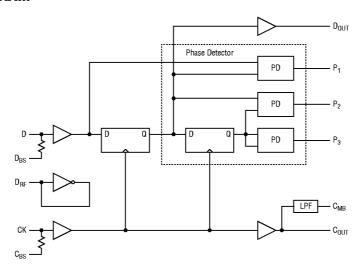

Oki's GHDD4414 is a 10-GHz decision circuit designed to strip data from high-speed serial bit streams in 10-Gbps communication links. Using a clock input at up to 10 GHz and using D-flip-flops, EX-ORs, and phase detectors, this circuit separates a 10-Gbps data stream into: clock output, data output, "phase" variation output, and data density output.

A 10-GHz master clock drives two D-flip-flops in this circuit. Buffered input data is clocked through the first flip-flop, then the second, "data out" is taken from the first flip-flop. The data input buffer is composed of a series of inverters to delay the signal and obtain a small decision ambiguity. A phase comparison is made of the buffered data and data from flip-flop one; a second phase comparison is made of the output of flip-flops one and two. The phase detectors are modified EX-OR circuits with resistor summing of the logic gates to permit analog measurement of their outputs. Any change in the timing relationships between the clock and data is seen at the output of the first phase detector. The second flip-flop operates as a 1-bit shift register with fixed 360-deg phase shift. The second phase detector output depends only upon the transition density (speed of rise and fall transitions) of the input data signal.

All signal interfaces are  $50-\Omega$  with all inputs internally terminated in  $50~\Omega$ . The 10-GHz clock and data inputs are AC capacitively-coupled for ease of interfacing at microwave speeds and reducing ground noise induced phase jitter. Data and phase outputs are DC-coupled.

#### **FEATURES**

- Phase detectors on chip: verifies data integrity

- Isolated 10-Gbps input pins: minimizes noise and impedance variation

- 1.5 V, 1 W: lowest power with 50- $\Omega$  interfaces

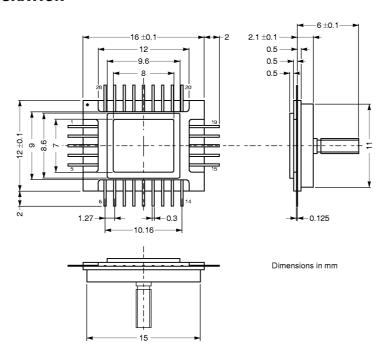

- 28-pin ceramic flat package with impedance controlling ground plane and flush mount heat sink

## PIN CONFIGURATION

| Pin | Signal           | Function                  | Pin | Signal          | Function                     |

|-----|------------------|---------------------------|-----|-----------------|------------------------------|

| 1   | C <sub>BS</sub>  | Clock bias input          | 15  | V <sub>B</sub>  | Power supply (buffer)        |

| 2   | NC               |                           | 16  | P1              | Phase detector output        |

| 3   | C <sub>MB</sub>  | Clock output duty monitor | 17  | P2              | Phase detector ref. output 1 |

| 4   | NC               |                           | 18  | P3              | Phase detector ref. output 2 |

| 5   | V <sub>B</sub>   | Powr supply (buffer)      | 19  | $V_D$           | Power supply (logic circuit) |

| 6   | GND              |                           | 20  | GND             |                              |

| 7   | D <sub>OUT</sub> | Data output               | 21  | D <sub>IN</sub> | Data input                   |

| 8   | GND              |                           | 22  | GND             |                              |

| 9   | NC               |                           | 23  | D <sub>BS</sub> | Data bias input              |

| 10  | NC               |                           | 24  | D <sub>RF</sub> | Data bias reference output   |

| 11  | NC               |                           | 25  | $V_D$           | Power supply (logic circuit) |

| 12  | GND              |                           | 26  | GND             |                              |

| 13  | C <sub>OUT</sub> | Clock output              | 27  | CK              | Clock input                  |

| 14  | GND              |                           | 28  | GND             |                              |

#### **BLOCK DIAGRAM**

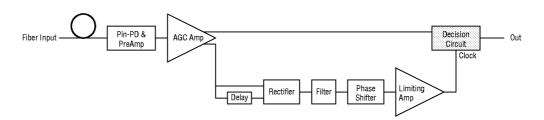

#### **APPLICATION BLOCK DIAGRAM**

#### **ELECTRICAL CHARACTERISTICS**

$V_{DD}$  = 1.5 V ±0.1 V,  $V_{B}$  = 1.5 V ±0.1 V,  $T_{S}$  = 0  $^{\circ}$  to 70  $^{\circ}C$

| Parameter                                    | Symbol            | Condition                           | Min. | Max. | Unit             |

|----------------------------------------------|-------------------|-------------------------------------|------|------|------------------|

| Power dissipation                            | Р                 |                                     |      | 1    | w                |

| Decision ambiguity                           | V <sub>IDEC</sub> | 10 Gbps                             |      | 0.05 | V <sub>P-P</sub> |

| Phase margin                                 | Δθ                | PRBS: 2 <sup>15</sup> -1            | 250  |      | degree           |

| Data input voltage amplitude V <sub>ID</sub> |                   | Capacitive coupling                 |      | 0.8  | V <sub>P-P</sub> |

| Clock input voltage amplitude                | V <sub>IC</sub>   |                                     | 0.4  | 0.8  | V <sub>P-P</sub> |

| Data output voltage amplitude                | V <sub>OD</sub>   | 50Ω load                            | 0.7  |      | V <sub>P-P</sub> |

| Clock output voltage amplitude               | V <sub>oc</sub>   | capacitive coupling                 | 0.7  |      | V <sub>P-P</sub> |

| Clock output duty cycle                      | D <sub>TYC</sub>  |                                     | 40   | 60   | %                |

| Clock to data delay                          | τ <sub>CD</sub>   |                                     | 25   | 45   | ps               |

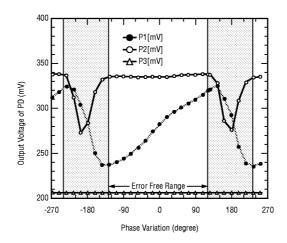

| Phase detection sensitivity                  | Δ۷θ               | 10 Gbps<br>PRBS: 2 <sup>15</sup> -1 | 0.28 |      | mV/degree        |

### Phase Detection Characteristics ( $D_{IN}$ Amplitude = $0.7-V_{P-P}$ )

| CIN Delay (ps) | P1 (V) | P2 (V) | P3 (V) | Comments                                |

|----------------|--------|--------|--------|-----------------------------------------|

| +29            | 0.350  | 0.343  | 0.443  | Maximum delay for ER <10 <sup>-10</sup> |

| 0              | 0.383  | 0.340  | 0.443  | Center of phase margin                  |

| -29            | 0.424  | 0.342  | 0.443  | Minimum delay for ER <10 <sup>-10</sup> |

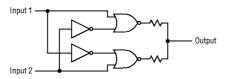

#### PHASE DETECTOR CIRCUIT

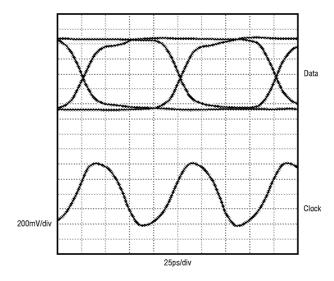

#### PHASE DETECTION BETWEEN SIGNAL AND CLOCK AT 10 Gbps

#### **TIMING**