# GENLINX D2 SERIAL DIGITAL CABLE EQUALIZER – GS9006A

Preliminary Data Sheet

## **FEATURES**

- automatic equalization up to 350 metres of 8281 cable at 143 MB/s data rates.

- · 8 pin PDIP packaging

- · single -5 volt power supply operation

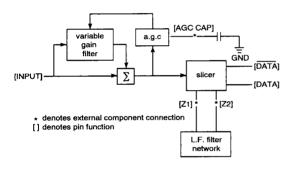

#### **FUNCTIONAL BLOCK DIAGRAM**

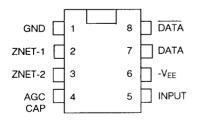

# PIN OUTS

#### **DEVICE DESCRIPTION**

The Gennum *GENLINX* GS9006A is a monolithic automatic cable equalizer developed for scrambled NRZI Serial Digital Video signals. It is fabricated on Gennum's proprietary LSI process and is suitable for 143 MB/s and 177 MB/s D2 signals.

The GS9006A accepts scrambled SMPTE/EBU Serial Digtal Video signals and is driven as unbalanced using a  $75\Omega$  termination resistor. The DATA and  $\overline{\text{DATA}}$  outputs typically deliver 750 mV p-p equalized signals into 220 ohm loads. These signals can be used to feed cable driver circuits for Serial Distribution Amplifier applications.

Packaging is 8 pin PDIP with the pin outs as shown below. Operating with a single -5 volts supply, the GS9006A typically draws 23 mA of current.

The circuitry of the GS9006A is protected by Patents Pending.

## **APPLICATIONS**

- Front-end cable equalization for D2 serial digital routers.

- Input equalization for serial digital DAs.

### **AVAILABLE PACKAGING**

8 PIN PDIP

# **ORDERING INFORMATION**

| Part Number | Package    | Temperature |  |  |

|-------------|------------|-------------|--|--|

| GS9006ACDA  | 8 pin PDIP | 0°C to 70°C |  |  |

Document No. 520 - 31

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise stated, Vs = -5V,  $T_A = 0$  to  $70^{\circ}C$ ,  $R_i = 220\Omega$

|      | PARAMETER                       | SYMBOL               | CONDITIONS                          | MIN  | TYP  | MAX  | UNITS  |

|------|---------------------------------|----------------------|-------------------------------------|------|------|------|--------|

| D.C. | Supply Voltage                  | V <sub>EE</sub>      | T <sub>A</sub> = 25°C               | -4.5 | -5.0 | -5.5 | volts  |

|      | Supply Current                  | I.                   | T <sub>A</sub> = 25°C               | -    | 23   | -    | mA     |

| A.C. | Gain Lift relative<br>to 10 MHz |                      | T <sub>A</sub> = 25°C<br>f = 70 MHz | 22   | -    | -    | dB     |

|      | Input Signal Level              | V <sub>SIG-in</sub>  | R <sub>IN</sub> = 75Ω               | 720  | -    | 880  | mV p-p |

|      | Output Signal Level             | V <sub>SIG-out</sub> | R <sub>ουτ</sub> = 220Ω             | -    | 750  | •    | mV p-p |

|      | Input Resistance                | R <sub>IN</sub>      |                                     | зк   | -    | -    | Ω      |

|      | Input Capacitance               | C <sub>IN</sub>      |                                     | -    | 1.0  | -    | рF     |

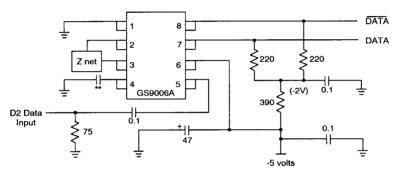

## **TEST CIRCUIT**

unless otherwise shown, all resistors are in ohms, all capacitors in uF

Figure 2

NOTES: The block marked [Znet] is a series R-C network used to control the amount of Low Frequency (DC component) rejection. In scrambled NZRI data, there should be no net DC component.

As a starting point, R can be 470  $\Omega$  and C can be 4.7 pF. The optimal values may be determined by observing the 'eye pattern' of the output data.

If no LF rejection is needed pins 2 and 3 may be directly connected together.

\*\*The value of the AGC capacitor is also determined experimentally. It should fall between 0.1uF and 10 uF.

520 - 31

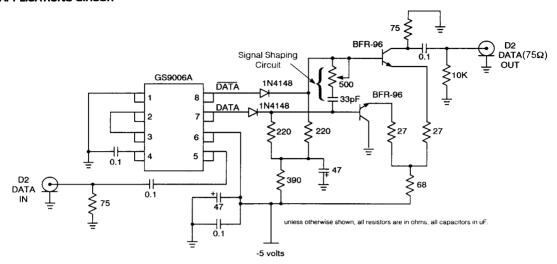

#### **APPLICATIONS CIRCUIT**

NON- RECLOCKING DISTRIBUTION AMPLIFIER

Figure 3.

#### APPLICATIONS INFORMATION

Due to the high bit rates of the signals involved, care should be taken to assure minimum track lengths and the liberal use of ground plane around the device. Figure 3 shows one application of the GS9006A used as a non-reclocking serial distribution amplifier.

The input signal is AC coupled to the device and the signal is terminated with a 75  $\Omega$  resistor placed at the input side of the capacitor.

The output stages of the GS9006A are designed for a minimum load resistance of 220  $\Omega$ . Reducing this load resistance or increasing the supply voltage in order to boost the output signal swing will cause damage to the output stages.

Discrete transistor circuitry as shown in Figure 3. or a monolithic cable driver should be used after the device in order to boost the output signals.

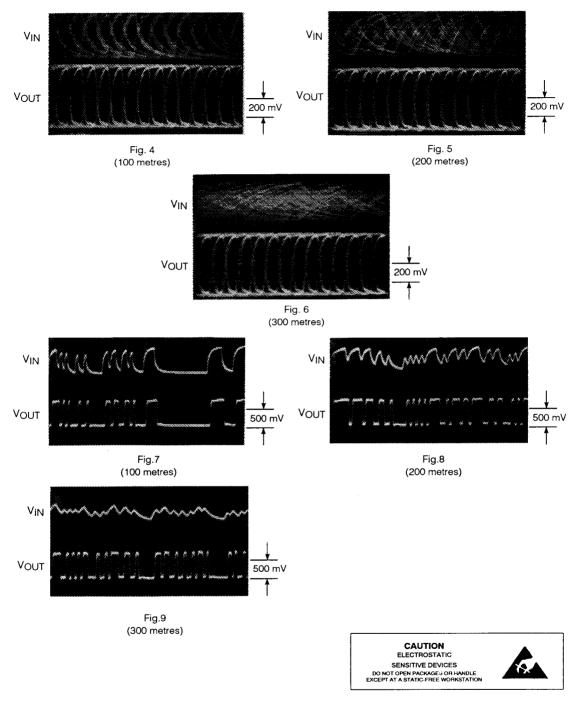

Figures 4, 5 and 6 show the input serial data 'eye pattern' after 100, 200 and 300 metres of belden 8281 cable. In each case, the corresponding equalized output 'eye pattern' is also shown.

Figures 7 through 9 show typical 143 MB/s input and output data waveforms for similar lengths of cable. Even though there is some signal jitter evident in the output signal (approximately ±1 ns), this would not show up as a problem in a system if the equalized data is reclocked.

For non-reclocking applications, this jitter will limit the usefulness of the GS9006A to a single pass through of data.

Gennum Corporation assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement.

© Copyright August 1991 Gennum Corporation. All rights reserved. Printed in Canada.

520 - 31