# NMC98C10/C20/C40 Electrically Erasable, Programmable Memories

### **General Description**

The NMC98C10, NMC98C20 and NMC98C40 are 128 by 8, 256 by 8 and 512 by 8, 5-volt programmable, non-volatile, parallel access memories built with CMOS floating gate process. Data and address lines are multiplexed, enabling these devices to be packaged in an 18-pin DIP or 20-pin SO, saving board space. The pin-out is identical to the Intel 8185 static RAM and the 2001 non-volatile RAM, allowing the memories to directly interface with popular 8-bit and 16-bit microprocessors and microcontrollers.

The write cycle is simplified by a self-timed erase before write circuit on-chip. The end of write cycle can be determined by polling the data pins or the controller can simply allow a minimum time between a write command and the subsequent command. To prevent undesirable modification of the memory contents during system power up or power down, a lockout circuit ignores write commands while V<sub>CC</sub> is below the prescribed level of VLKO.

Applications for these memories include storing position data in robotic systems, storing local area network node address and parameter settings in data communications equipment, storing set-up and last position data in industrial control systems and storing PBX switch data in telecommunications equipment.

#### **Features**

- Single 5-volt supply

- Reliable CMOS floating gate process

- Eighteen-pin package

- Multiplexed address and data bus

- Self timed write operation

- 20,000 erase/write cycles typical

- Very low power dissipation

- Ten year data retention

- Minimum board space

- Directly compatible with NSC800, HPC and other standard microprocessors and microcontrollers

- No external sequencing of erase/write cycle

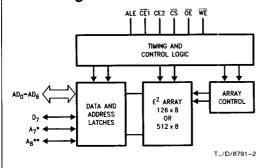

### **Block Diagram**

- \*A7 not used on NMC98C10

- \*\*A8 not used on NMC98C10 or NMC98C20

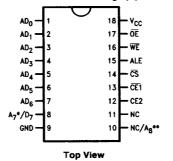

#### Pin Names

| AD <sub>0</sub> -AD <sub>7</sub> | Multiplexed address and data bits. Pin 8 is DATA only for NMC98C10. |

|----------------------------------|---------------------------------------------------------------------|

| GND                              | Ground                                                              |

| A8                               | MSB of address for NMC98C40                                         |

| NC                               | No Connection                                                       |

| CE2                              | Chip Enable 2                                                       |

| CE1                              | Chip Enable 1                                                       |

| ĊŚ                               | Chip Select                                                         |

| ALE                              | Address Latch Enable                                                |

| WE                               | Write Enable                                                        |

| ŌĒ                               | Output Enable                                                       |

| V <sub>CC</sub>                  | Power Supply                                                        |

# **Connection Diagrams**

#### Dual-In-Line Package (N)

#### See NS Package Number N18A

- \*A7 not used on NMC98C10

- \*\*A8 not used on NMC98C10 or NMC98C20

# **Ordering Information**

### Commercial Temp. Range (0°C to +70°C)

| Parameter/Order Number  | Comments                 |  |  |  |

|-------------------------|--------------------------|--|--|--|

| NMC98C10N/NMC98C20N     | Plastic 18-Pin DIP       |  |  |  |

| NMC98C40N               | t <sub>LD</sub> = 300 ns |  |  |  |

| NMC98C10N-1/NMC98C20N-1 | Plastic 18-Pin DIP       |  |  |  |

| NMC98C40N-1             | t <sub>LD</sub> = 180 ns |  |  |  |

### Extended Temp. Range (-40°C to +85°C)

TL/D/8791-1

| Parameter/Order Number    | Comments                 |

|---------------------------|--------------------------|

| NMC98C10EN/NMC98C20EN     | Plastic 18-Pin DIP       |

| NMC98C40EN                | t <sub>LD</sub> = 300 ns |

| NMC98C10EN-1/NMC98C20EN-1 | Plastic 18-Pin DIP       |

| NMC98C40EN-1              | t <sub>LD</sub> = 180 ns |

## Military Temp. Range ( $-55^{\circ}$ C to $+125^{\circ}$ C)

| Parameter/Order Number    | Comments                 |

|---------------------------|--------------------------|

| NMC98C10MN/NMC98C20MN     | Plastic 18-Pin DIP       |

| NMC98C40MN                | t <sub>LD</sub> = 300 ns |

| NMC98C10MN-1/NMC98C20MN-1 | Plastic 18-Pin DIP       |

| NMC98C40MN-1              | t <sub>LD</sub> = 180 ns |

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-0.5V to 6.5VVoltage on Any Pin -65°C to +150°C Storage Temperature Range

Maximum Power Dissipation @ 25°C

500 mW 300°C >2000V

Lead Temp. (Soldering, 10 seconds) ESD rating

Operating Conditions (Applies to DC and AC Characteristics)

Positive Supply Voltage Ambient Temperature

Commercial Industrial Military

4.5V to 5.5V

0°C to +70°C -40°C to +85°C -55°C to +125°C

### **DC Electrical Characteristics**

| Symbol           | Parameter                               | Test Conditions                    | Min | Тур | Max                   | Units |

|------------------|-----------------------------------------|------------------------------------|-----|-----|-----------------------|-------|

| V <sub>OH</sub>  | Output High Voltage                     | $I_{OH} = -400 \mu\text{A}$        | 2.4 |     |                       | V     |

| V <sub>OL</sub>  | Output Low Voltage                      | I <sub>OL</sub> = 2.1 mA           |     |     | 0.4                   | ٧     |

| V <sub>IH</sub>  | Input High Voltage                      |                                    | 2.0 |     | V <sub>CC</sub> + 0.5 | ٧     |

| VIL              | Input Low Voltage                       |                                    | 0   |     | 0.8                   | V     |

| V <sub>LKO</sub> | V <sub>CC</sub> Level for Write Lockout |                                    | 4.0 |     | 4.4                   | V     |

| l <sub>L</sub> i | Input Leakage Current                   | $V_{IN} = V_{CC}$                  |     |     | ± 10.0                | μΑ    |

| ILO              | Output Leakage Current                  | V <sub>OUT</sub> = V <sub>CC</sub> |     |     | ± 10.0                | μΑ    |

| Icc              | Operating Supply Current                | TTL Inputs                         |     |     | 15.0                  | mA    |

|                  |                                         | CMOS Inputs                        |     |     | 10.0                  | mA    |

| ICCPD            | Standby Supply Current                  | TTL Inputs                         |     |     | 5.0                   | mA    |

|                  |                                         | CMOS Inputs                        |     |     | 100                   | μΑ    |

| Isc              | Short-Circuit Current                   | One Output Pin Shorted             |     | 40  |                       | mA    |

## **AC Electrical Characteristics**

| Symbol           | Parameter                                                       | NMC98C10,<br>NMC98C20,<br>NMC98C40 |     | NMC9<br>NMC9<br>NMC9 | Units |    |

|------------------|-----------------------------------------------------------------|------------------------------------|-----|----------------------|-------|----|

|                  |                                                                 | Min                                | Max | Min                  | Max   |    |

| t <sub>AL</sub>  | Address to Latch Setup Time                                     | 50                                 |     | 50                   |       | ns |

| tLA              | Address Hold Time after Latch                                   | 45                                 |     | 30                   |       | ns |

| tLC              | Latch to OE/WE Control                                          | 80                                 |     | 35                   |       | ns |

| toE              | Valid Data Out Delay from Read Control                          |                                    | 170 |                      | 120   | ns |

| tLD              | ALE to Data Out Valid                                           |                                    | 300 |                      | 180   | ns |

| t <sub>LL</sub>  | Latch Enable Width                                              | 100                                |     | 60                   |       | ns |

| tон              | Output Held from Addresses, CS, or OE (Whichever Changes First) | 0                                  |     | 0                    |       | ns |

| tolz             | OE Low to Output Driven                                         | 10                                 |     | 10                   |       | ns |

| t <sub>RDF</sub> | Data Bus Float after Read                                       | 0                                  | 95  | 0                    | 60    | ns |

| toL              | OE/WE Control to Latch Enable                                   | 0                                  |     | 0                    |       | ns |

| toc              | OE/WE Control Width                                             | 250                                |     | 150                  |       | ns |

| t <sub>DW</sub>  | Data In to Write Setup Time                                     | 150                                |     | 150                  |       | ns |

| twp              | Data In Hold Time after Write                                   | 20                                 |     | 15                   |       | ns |

| tsc              | Chip Select Set-Up to OE/WE Control                             | 0                                  |     | 0                    |       | ns |

| t <sub>CS</sub>  | Chip Select Hold Time after OE/WE Control                       | 0                                  |     | 0                    |       | ns |

| tALCE            | Chip Enable Set-Up to ALE Falling                               | 30                                 |     | 30                   |       | ns |

### **AC Electrical Characteristics** (Continued)

| Symbol          | Parameter                               | NMC98C10,<br>NMC98C20,<br>NMC98C40 |     | NMC98C10-1,<br>NMC98C20-1,<br>NMC98C40-1 |     | Units  |

|-----------------|-----------------------------------------|------------------------------------|-----|------------------------------------------|-----|--------|

|                 |                                         | Min                                | Max | Min                                      | Max | 7      |

| tLACE           | Chip Enable Hold Time after ALE Falling | 45                                 |     | 40                                       |     | ns     |

| t <sub>WR</sub> | Byte Write Cycle Time                   |                                    | 20  |                                          | 20  | ms     |

| t <sub>WH</sub> | Data Invalid Time after WE Falling      |                                    | 1   |                                          | 1   | ms     |

| Endurance       | Number of Erase/Write Cycles            | Typical 20,000                     |     | Typical 20,000                           |     | Cycles |

# Capacitance T<sub>A</sub> = 25°C, f = 1 MHz (Note 3)

| Parameter        | Description              | Test Conditions                                                         | Тур | Max | Units |

|------------------|--------------------------|-------------------------------------------------------------------------|-----|-----|-------|

| C <sub>IN</sub>  | Input Capacitance        | V <sub>IN</sub> := 0V                                                   | 5   | 10  | pF    |

| C <sub>I/O</sub> | Input/Output Capacitance | $\overline{OE} = \overline{CE1} = \overline{CS} = V_{IH}, CE2 = V_{IL}$ |     | 10  | pF    |

### **AC Test Conditions**

Input Rise and Fall Times (10% to 90%) ......20 ns Input/Output Timing Reference Level . . . . . . . 0.8V to 2.0V Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range",

the device should not be operated at these limits. The table of "Electrical Characteristics" provides actual operating limits. Note 2: Power dissipation temperature derating-plastic "N" package: - 12 mW/°C from 65°C to 85°C.

Note 3: This parameter is sampled and not 100% tested.

## **Typical Applications**

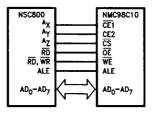

TL/D/8791-5

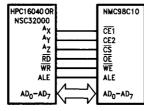

Note: A<sub>X</sub>, A<sub>Y</sub>, A<sub>Z</sub> are any three of the NSC800™ address pins A8-A15. By connecting CE1, CE2, and CS to specific address lines, the NMC98C10, NMC98C20 and NMC98C40 can be mapped to a particular range in memory without the need for an external memory address decoder

FIGURE 1. Using the NMC98C10 with an NSC800 Microcontroller

TL/D/8791-6

FIGURE 2. Using the NMC98C10 with the HPC 16040 Microcontroller or NSC Series 32000®

# **Functional Description**

Table I shows the different modes of operation as a function of the control signals. Standby power down mode: both write and read are inhibited and the device's power consumption is greatly reduced. Standby power up mode: the device consumes the operating power, but read and write are inhibited. Inhibit mode: the device is write protected to avoid inadvertent modifications while the read and write pins are changing.

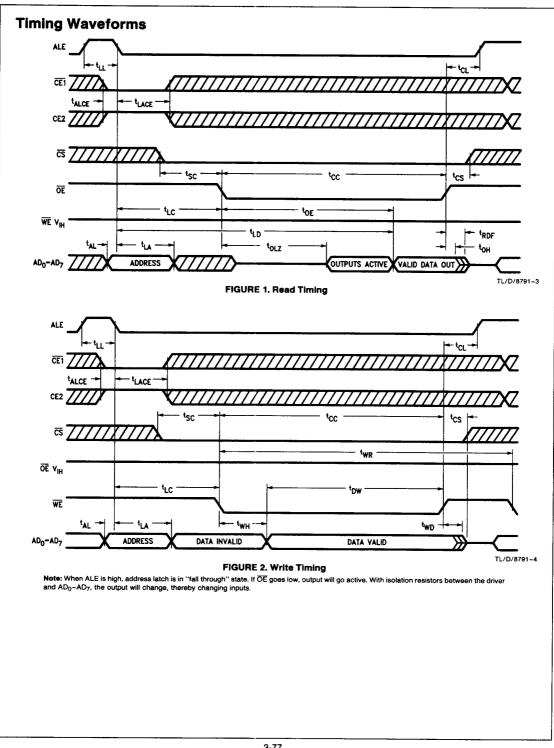

#### **READ OPERATION**

Figure 3 shows the timing diagram for READ operation. The address is latched on the falling edge of ALE. The NMC98C10 pins 1 through 7 are used for address bits, the NMC98C20 uses pin 8 in addition, the NMC98C40 uses pins 8 and 10 in addition to pins 1 through 7 for address bits.

Data appear on pins 1 through 8 after  $\overline{\text{OE}}$  becomes active (low).

#### WRITE OPERATION

Figure 4 shows the timing for a write operation. Address is latched on the falling edge of ALE. CE1 and CE2 are latched on the falling edge of ALE with the addresses. The write cycle is initiated by cycling WE low for the specified time. The internally timed write cycle begins on the falling edge of WE. No external ERASE cycle is needed since there is an internally timed ERASE before WRITE. The internal programming cycle requires 20 ms maximum, although once the minimum external cycle is completed the interface signals may change.

Before initiating any subsequent operations, the internally timed programming cycle must be completed. The completion of the programming cycle can be determined by  $\overline{\text{DATA}}$  POLLING, as described below, or by simply waiting 20 ms after the falling edge of  $\overline{\text{WE}}$ .

#### **DATA POLLING**

After the write operation is initiated, its conclusion can be monitored by putting the device in the READ mode and polling the D7 data bit. The data bit will be logical inverse of the bit being written to a location in memory until the write operation is completed. At this time the D7 data bit will be the same as the last D7 data bit written into memory.

#### WRITE LOCKOUT

During system power up or power down, an on-chip write lockout circuit prevents spurious WRITES into the memory locations while  $V_{\rm CC}$  is lower than the specified lockout voltage  $V_{\rm LKO}$ . This frees the system designer from having to design external write protection circuits.

**TABLE I. Mode Table**

| Mode                 | CE1*            | CE2*            | CS  | ŌE  | WE  | AD <sub>0</sub> -AD <sub>7</sub> |

|----------------------|-----------------|-----------------|-----|-----|-----|----------------------------------|

| Standby Powered Down | VIH             | х               | ×   | X   | ×   | Hi-Z                             |

| Standby Powered Down | х               | VIL             | x   | х   | Х   | Hi-Z                             |

| Standby Powered Up   | VIL             | V <sub>IH</sub> | VιΗ | Х   | Х   | Hi-Z                             |

| Read                 | VIL             | VIH             | VIL | VIL | VIH | Data Out                         |

| Write                | VIL             | VIH             | VIL | νн  | VIL | Data In                          |

| Inhibit              | V <sub>1L</sub> | VIH             | VIL | VIH | VIH | Hi-Z                             |

| Inhibit†             | VIL             | VIH             | VIL | VIL | VIL | Hi-Z                             |

VIL = Logical Low Input

VIH = Logical High Input

Hi-Z = High Impedance State

X = Don't Care

\* = CE1 and CE2 are latched by ALE

$\dagger$  = This inhibit mode not recommended