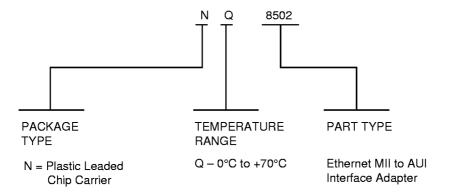

## *8502*

# Ethernet MII to AUI Interface Adapter

98210

This document is an LSI Logic document. Any reference to SEEQ Technology should be considered LSI Logic.

#### **Features**

- Single Chip Connecting MII and AUI Interfaces

- AUI Interface to Ethernet Transceiver

- MII Interface to Ethernet Controller

- MI Interface for Configuration & Status

- Few External Components

- Meets All Applicable IEEE 802.3 Standards

- Interface to External E<sup>2</sup>PROM for Automatic Preloading of MI Serial Port Bits

- Many User Features and Options

- Full Duplex

- Powerdown

- Transmitter Disable/Powerdown

- Loopback

- MII Disable

- Link and Jabber Status Passthrough

- Multiple Register Access

#### ■ LED Outputs

- Activity, Transmit, Receive

- Collision

- Link

- User Programmable

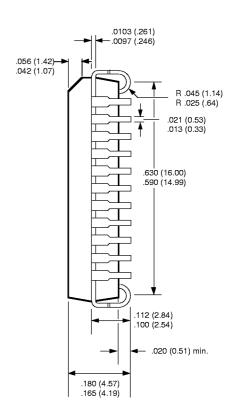

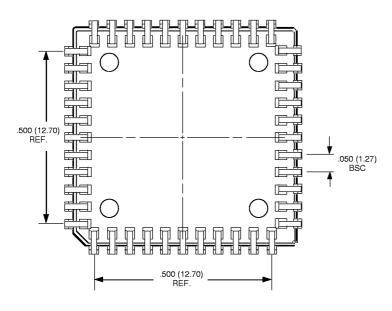

- 44L PLCC

Note: Check for latest Data Sheet revision before starting any designs.

SEEQ Data Sheets are now on the Web, access SEEQ Home Page www.seeq.com

- or -

LSI Logic at www.lsilogic.com

#### Description

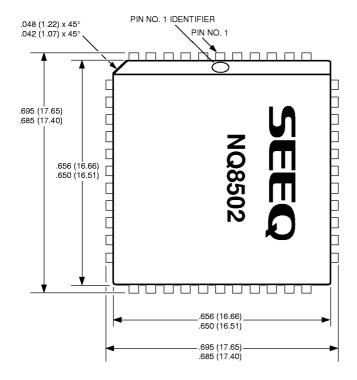

The 8502 is a interface IC that provides a single chip link between an Ethernet AUI (Attachment Unit Interface) and an Ethernet MII (Media Independent Interface). The 8502 is in a 44L package.

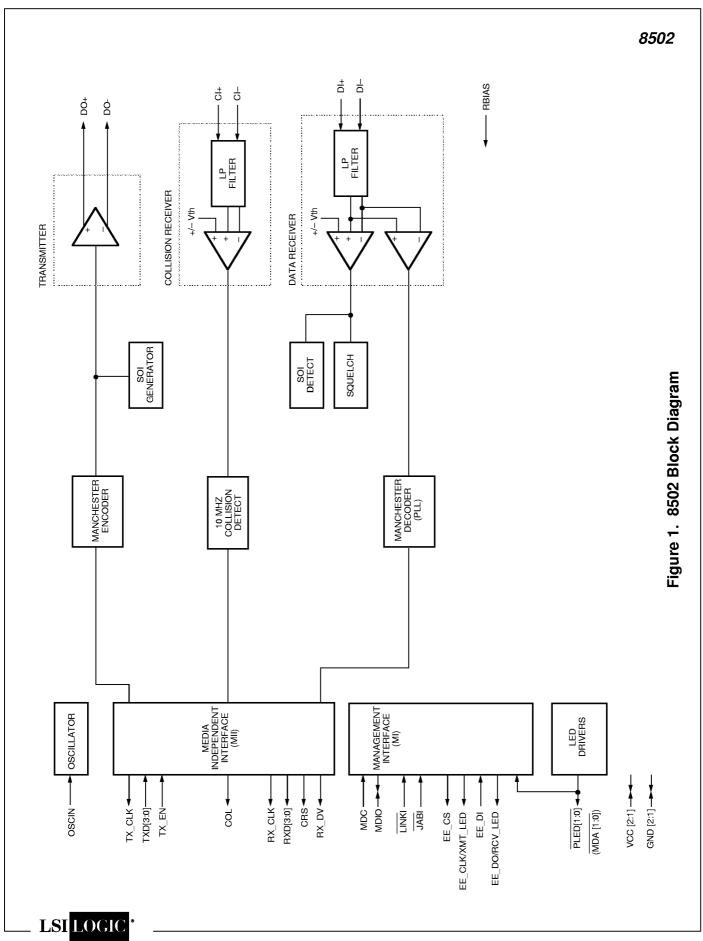

The 8502 consists of Manchester encoder, AUI transmitter, AUI receiver, Manchester decoder, Media Independent Interface (MII) to an external controller, and Management Interface (MI) serial port.

The 8502 can access five 16 bit registers though the MI serial port. These registers contain configuration inputs, status outputs, and device capabilities.

The 8502 is ideal for external PHY's that connect AUI or other media to MII. They are also ideal as an AUI interface to MII based Ethernet controllers in adapter cards, motherboards, and hubs.

#### 8502 Table of Contents

- 1.0 Pin Description

- 2.0 Block Diagram

- 3.0 Functional Description

- 3.1 General

- 3.2 Media Independent Interface (MII)

- 3.2.1 General

- 3.2.2 MII Disable

- 3.3 Manchester Encoder

- 3.4 Manchester Decoder

- 3.5 AUI Transmitter

- 3.5.1 Transmitter

- 3.5.2 Transmit Activity Indication

- 3.5.3 Transmit Disable

- 3.5.4 Transmit Powerdown

- 3.6 AUI Receiver

- 3.6.1 Receiver

- 3.6.2 Squelch

- 3.6.3 Receive Activity Indication

- 3.7 Collision

- 3.7.1 General

- 3.7.2 Collision Detect Algorithm

- 3.7.3 Collision Indication

- 3.7.4 Collision Test

- 3.8 SOI (Start of Idle)

- 3.9 Full Duplex Mode

- 3.10 Loopback

- 3.11 Link

- 3.11.1 General

- 3.11.2 Link Algorithm

- 3.11.3 Link Indication

- 3.12 Jabber

- 3.13 Reset

- 3.14 Powerdown

- 3.15 Oscillator

- 3.16 LED Drivers

- 3.17 MI Serial Port

- 3.17.1 Signal Description

- 3.17.2 Timing

- 3.17.3 Multiple Register Access

- 3.17.4 Bit Types

- 3.17.5 Frame Structure

- 3.17.6 Register Structure

- 3.17.7 Link Status Bit

- 3.17.8 Jabber Detect Bit

- 3.18 Register Description

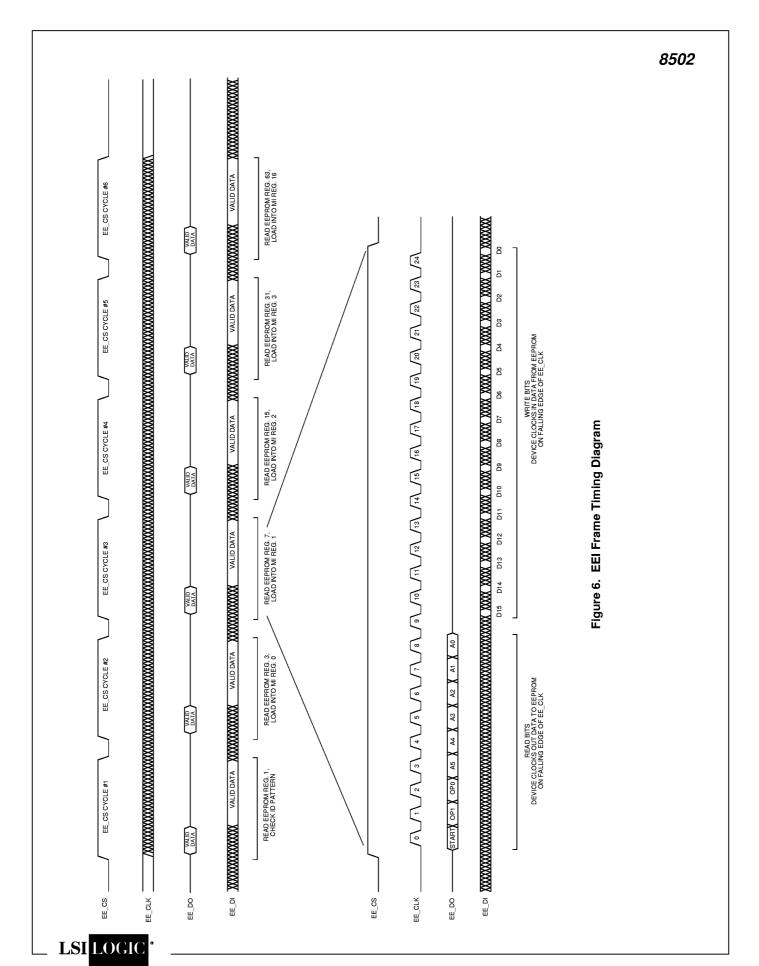

- 3.19 External EEPROM Interface (EEI)

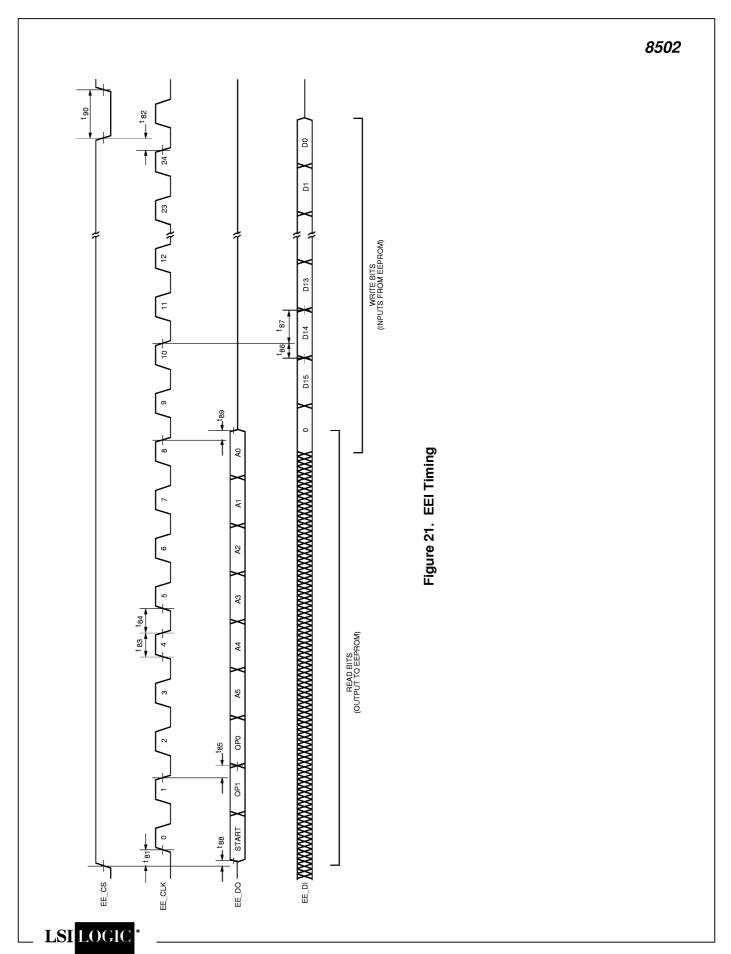

- 3.19.1 General

- 3.19.2 Signal Description

- 3.19.3 Frame Structure

- 3.19.4 EE CS Cycle Structure

- 3.19.5 Timing

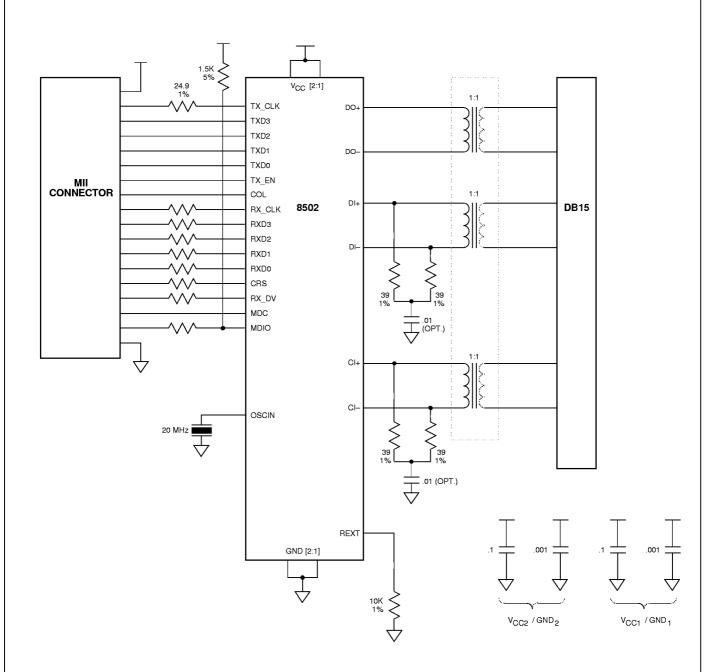

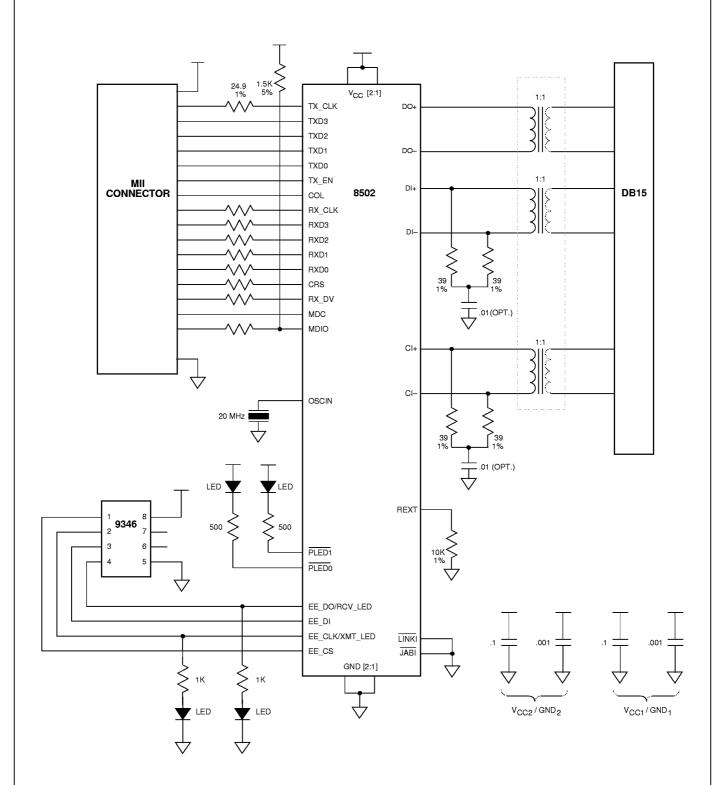

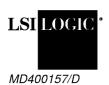

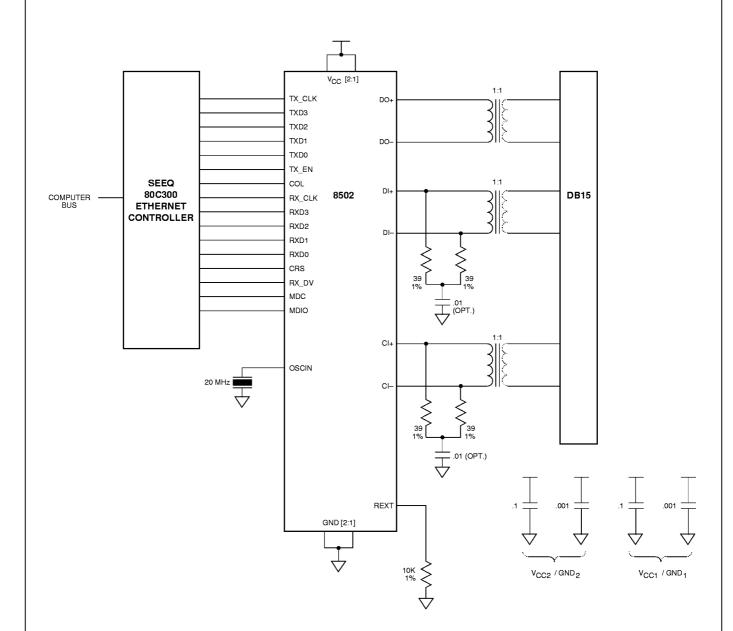

- 4.0 Application Information

- 4.1 Example Schematics

- 4.2 AUI Transmit Interface

- 4.3 AUI Receive Interface

- 4.4 Controller Interface

- 4.4.1 General

- 4.4.2 Output Drivers

- 4.4.3 MII Disable

- 4.5 MI Serial Port

- 4.5.1 General

- 4.5.2 Multiple Register Access

- 4.5.3 Serial Port Addressing

- 4.6 Reset

- 4.7 External EEPROM

- 4.8 Oscillator

- 4.9 Programmable Led Drivers

- 4.10 Link Passthrough

- 4.11 Jabber Passthrough

- 4.12 Power Supply Decoupling

- 5.0 Specifications

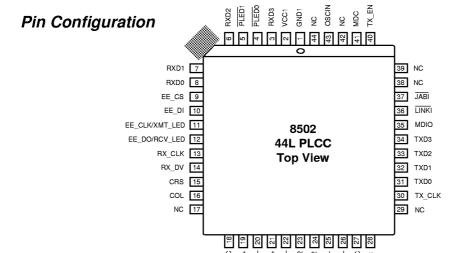

# 1.0 Pin Description

| Pin #<br>44L<br>8502 | Pin Name                     | I/O | Description                                                                                                                                                                                                     |

|----------------------|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>23              | VCC2<br>VCC1                 | _   | Positive Supply. +5 +/-5% Volts.                                                                                                                                                                                |

| 1<br>24              | GND2<br>GND1                 | _   | Ground. 0 Volts.                                                                                                                                                                                                |

| 25                   | DO+                          | 0   | AUI Transmit Output, Positive.                                                                                                                                                                                  |

| 26                   | DO-                          | 0   | AUI Transmit Output, Negative.                                                                                                                                                                                  |

| 19                   | DI+                          | I   | AUI Receive Input, Positive.                                                                                                                                                                                    |

| 20                   | DI-                          | I   | AUI Receive Input, Negative.                                                                                                                                                                                    |

| 21                   | CI+                          | ı   | AUI Collision Input, Positive.                                                                                                                                                                                  |

| 22                   | CI-                          |     | AUI Collision Input, Negative.                                                                                                                                                                                  |

| 28                   | RBIAS                        | _   | Internal Bias Current Set. An external resistor connected between this pin and GND will create a reference current for the internal bias circuits.                                                              |

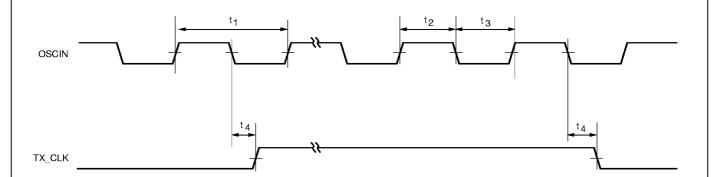

| 43                   | OSCIN                        |     | Clock Oscillator Input. There must be either a 20 MHz crystal or a 20 MHz clock tied between this pin and GND. TX_CLK output clock is generated from this input.                                                |

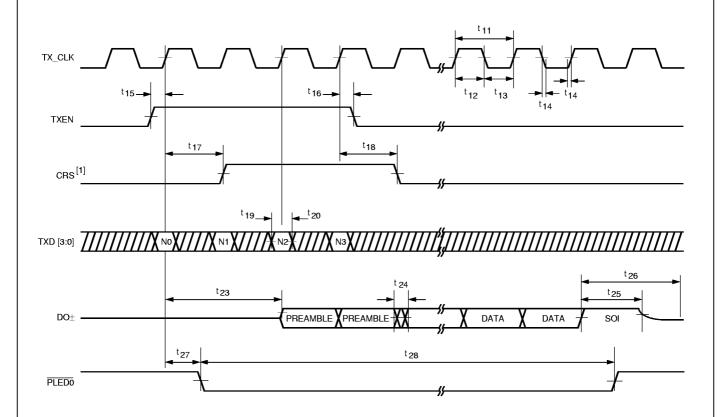

| 30                   | TX_CLK                       | 0   | <b>Transmit Clock Output.</b> This Media Independent Interface output provides a clock to the controller. Transmit data from the controller on TXD and TX_EN is clocked in on rising edges of TX_CLK and OSCIN. |

| 40                   | TX_EN                        | I   | <b>Transmit Enable Input.</b> This Media Independent Interface input has to be asserted active high to indicate that data on TXD is valid and is clocked in on rising edges of TX_CLK and OSCIN.                |

| 34<br>33<br>32<br>31 | TXD3<br>TXD2<br>TXD1<br>TXD0 | I   | <b>Transmit Data Input.</b> These Media Independent Interface inputs contain input nibble data to be transmitted on the AUI outputs and are clocked in on rising edges of TX_CLK and OSCIN.                     |

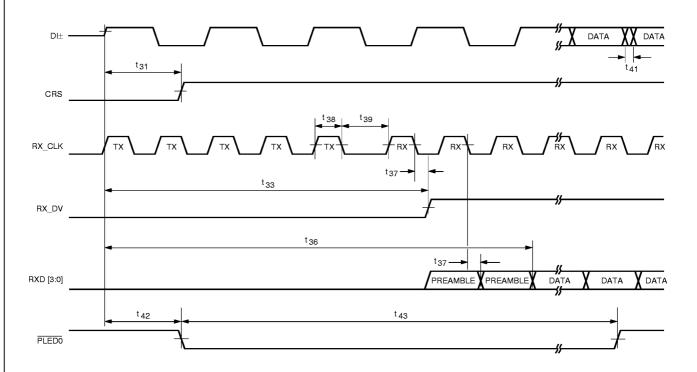

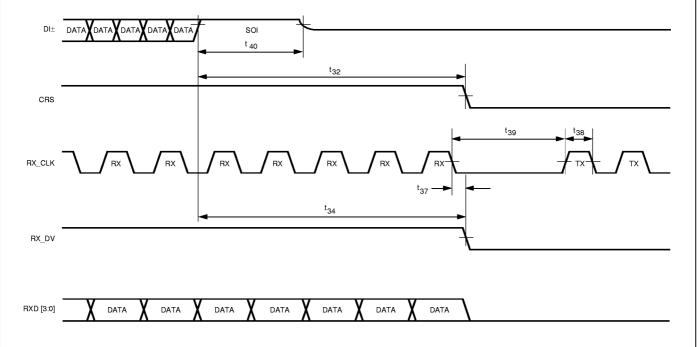

| 13                   | RX_CLK                       | 0   | Receive Clock Output. This Media Independent Interface output provides a clock to the controller. Receive data on RXD and RX_DV is clocked out to the controller on falling edges of RX_CLK.                    |

| 15                   | CRS                          | 0   | Carrier Sense Output. This Media Independent Interface output is asserted when valid data is detected on the AUI inputs and is clocked out on falling edges of RX_CLK.                                          |

| 14                   | RX_DV                        | 0   | Receive Data Valid Output. This Media Independent Interface output is asserted active high when valid decoded data is present on the RXD outputs and is clocked out on falling edges of RX_CLK.                 |

| 3<br>6<br>7<br>8     | RXD3<br>RXD2<br>RXD1<br>RXD0 | 0   | <b>Receive Data Output.</b> These Media Independent Interface outputs contain receive nibble data from the AUI input and are clocked out on falling edges of RX_CLK.                                            |

# 1.0 Pin Description continued

| Pin #<br>44L<br>8502 | Pin Name           | I/O               | Description                                                                                                                                                                                                                                                                                                        |

|----------------------|--------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16                   | COL                | 0                 | Collision Output. This Media Independent Interface output is asserted when collision between transmit and receive data is detected.                                                                                                                                                                                |

| 41                   | MDC                | I                 | Management Interface Clock Input. This Management Interface clock shifts serial data into and out of MDIO on rising edges.                                                                                                                                                                                         |

| 35                   | MDIO               | I/O               | Management Interface Data Input/Output. This bidirectional pin contains serial Management Interface data that is clocked in and out on rising edges of the MDC clock.                                                                                                                                              |

| 36                   | LINKI              | I<br>Pullup<br>To | <b>Link Input.</b> The value on this pin is either passed through to the internal MI serial port Link Status output bit In Register 1 or it enables the internal Link algorithm.                                                                                                                                   |

|                      |                    | VCC/2             | <ul> <li>1 = Link Status Bit Is Set To 0 (Link Fail)</li> <li>float = Link Status Bit Determined By The Internal Link Algorithm</li> <li>0 = Link Status Bit Is Set To 1 (Link Pass)</li> </ul>                                                                                                                    |

|                      |                    |                   | In 28L 8501, the Link Status Bit is always forced to 1 (Link Pass).                                                                                                                                                                                                                                                |

| 37                   | JABI               | I<br>Pullup       | <b>Jabber Input.</b> The value on this pin is passed through to the internal MI serial port Jabber Detect output bit In Register 1.                                                                                                                                                                                |

|                      |                    |                   | <ul> <li>1 = Jabber Detect Bit Is Set To 0 (No Jabber Detect)</li> <li>0 = Jabber Detect Bit Is Set To 1 (Jabber Detect)</li> </ul>                                                                                                                                                                                |

|                      |                    |                   | In 28L 8501, the Jabber Detect Bit is always forced to 0 (No Jabber Detect).                                                                                                                                                                                                                                       |

| 9                    | EE_CS              | 0                 | <b>External EEPROM Chip Select Output.</b> During powerup or reset, this pin is a chip select output to an external EEPROM that can preload the MI serial port input bits to values other than the defaults.                                                                                                       |

| 11                   | EE_CLK/<br>XMT_LED | 0                 | External EEPROM Clock Output/Transmit LED. During powerup or reset, this pin is serial data clock output to an external EEPROM that can preload the MI serial port input bits to values other than the defaults. Data is shifted in and out on EE_DI and EE_DO, respectively, on rising edges of the EE_CLK clock. |

|                      |                    |                   | During normal operation, this pin can be used as Transmit LED and can drive an LED to GND.                                                                                                                                                                                                                         |

|                      |                    |                   | 0 = No Detect<br>1 = Transmit Activity Detected, On for 50 mS                                                                                                                                                                                                                                                      |

| 10                   | EE_DI              | I<br>Pullup       | <b>External EEPROM Data Input.</b> During powerup or reset, this pin is a data input from an external EEPROM that can preload the MI serial port input bit to values other than the defaults.                                                                                                                      |

| 12                   | EE_DO/<br>RCV_LED  | 0                 | External EEPROM Data Output/Receive LED. During powerup or reset, this pin is a data output to an external EEPROM that can preload the MI serial port input bit to values other than the defaults.                                                                                                                 |

|                      |                    |                   | During normal operation, this pin can be used as Receive LED and can drive an LED to GND.                                                                                                                                                                                                                          |

|                      |                    |                   | <ul><li>0 = No Detect</li><li>1 = Receive Activity Detected, On for 50 mS</li></ul>                                                                                                                                                                                                                                |

# 1.0 Pin Description continued

| Pin #<br>44L<br>8502                   | Pin Name        | I/O                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------|-----------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

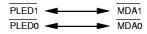

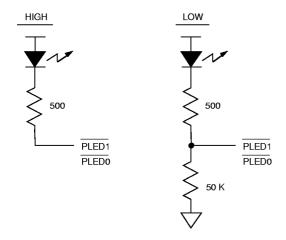

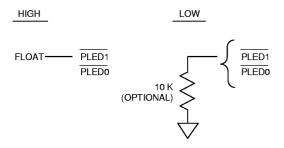

| 5                                      | PLED1<br>(MDA1) | I/O<br>O.D.<br>Pullup | Programmable LED Output/Management Interface Address Input. This pin can be programmed through the MI serial port to be either a Collision Detect output or a user select output. This pin can drive an LED from VCC. During powerup or reset, this pin is high impedance and the value on this pin is latched in as an address for the MI serial port.  When programmed as Collision Detect Output:  1 = No Detect 0 = Collision Detected, On For 50 mS |

| 4                                      | PLEDO<br>(MDAO) | I/O<br>O.D.<br>Pullup | Programmable LED Output/Management Interface Address Input. This pin can be programmed through the MI serial port to be either a Activity Detect output or a user select output. This pin can drive an LED from VCC. During powerup or reset, this pin is high impedance and the value on this pin is latched in as an address for the MI serial port.  When programmed as Activity Detect Output:  1 = No Detect 0 = Activity Detected, On For 50 mS    |

| 17<br>18<br>27<br>29<br>38<br>39<br>42 | NC              | _                     | No Connect. These pins are not connected but should be tied to GND to minimize noise.                                                                                                                                                                                                                                                                                                                                                                    |

#### 3.0 Functional Description

#### 3.1 GENERAL

The 8502 is a single chip interface IC's for connecting MII to AUI. MII and AUI are acronyms for Media Independent Interface and Attachment Unit Interface, respectively. Both of these interfaces are defined by IEEE 802.3 specifications.

The 8502 has six main sections: Media Independent Interface (MII), Manchester encoder, Manchester decoder, AUI transmitter, AUI receiver, and MI serial port.

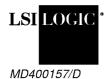

On the transmit side, NRZ data is received on the MII from an external Ethernet controller per the MII format described in Figure 2. The NRZ data is then sent to the Manchester encoder for formatting. The Manchester encoded data is then sent to the AUI transmitter. The AUI transmitter shapes the output and drives a 78 ohm AUI cable. In addition, the transmitter generates start of idle (SOI) pulses.

On the receive side, the AUI receiver receives incoming Manchester encoded data from the AUI cable, removes high frequency noise from the input, determines if the input signal is a valid packet, and then converts the data from AUI levels to internal digital levels. The AUI receiver also detects start of idle (SOI) pulses and implements a squelch algorithm to reject invalid signals. The output of the AUI receiver then goes to the Manchester decoder which recovers a clock from the AUI data stream, recovers the data, and converts the data back to NRZ. The NRZ data is then transmitted to an external Ethernet controller through the MII using the format shown in Figure 2.

The MI (Management Interface) serial port is a two pin bidirectional port through which configuration inputs can be set, and device capabilities and status outputs can be read out.

A crystal oscillator generates a master clock for the device.

Each block plus the operating modes are described in more detail in the following sections. A block diagram of the 8502 is shown in Figure 1.

#### 3.2 MEDIA INDEPENDENT INTERFACE (MII)

#### 3.2.1 General

The Media Independent Interface, called MII, provides a standardized interface between the 8502 and an external Ethernet controller. The MII is a nibble wide packet data interface defined in IEEE 802.3 specifications and shown in Figure 2. The 8502 meets all the MII requirements outlined in IEEE 802.3 specifications. The 8502 can directly connect, without any external logic, to any Ethernet controllers which also comply with the IEEE 802.3 MII specifications.

The MII consists of fourteen signals: four transmit data bits (TXD[3:0]), transmit clock (TX\_CLK), transmit enable (TX\_EN), four receive data bits (RXD[3:0]), receive clock (RX\_CLK), carrier sense (CRS), receive data valid (RX\_DV), and collision (COL). The transmit and receive clocks operate at 2.5 MHz.

On the transmit side, the TX\_CLK output runs continuously. When no data is to be transmitted, TX\_EN input is deasserted and any data on TXD[3:0] is ignored. When TX\_EN is asserted on rising edge of TX\_CLK, data on TXD[3:0] is clocked into the device on rising edges of the TX\_CLK. TXD[3:0] input data is actually nibble wide packet data whose format needs to be the same as specified in IEEE 802.3 specifications and shown in Figure 2. When all the data on TXD[3:0] has been latched into the device, TX\_EN is deasserted on rising edge of TX\_CLK.

On the receive side, when invalid data is sensed on the AUI inputs, the receiver is idle. During idle, RX\_CLK follows TX\_CLK, RXD[3:0] is held low, and CRS and RX\_DV are deasserted. When a valid packet is detected on the AUI receive inputs, CRS is asserted and the clock recovery process starts on the incoming data. After the receive clock has been recovered from the data, the RX\_CLK is switched over to the recovered clock and the data valid signal RX\_DV is asserted on a falling edge of RX\_CLK. While RX\_DV is asserted, valid data is clocked out of

#### a.) MII Frame Format

b.) MII Nibble Order

| Signals |   |   |                |   |   |   |   |   | Bi | t Va | lue |   |   |   |   |   |                       |   |                 |         |

|---------|---|---|----------------|---|---|---|---|---|----|------|-----|---|---|---|---|---|-----------------------|---|-----------------|---------|

| TXDO    | Χ | Χ | 1 <sup>1</sup> | 1 | 1 | 1 | 1 | 1 | 1  | 1    | 1   | 1 | 1 | 1 | 1 | 1 | <b>1</b> <sup>2</sup> | 1 | D0 <sup>3</sup> | <br>D4⁴ |

| TXD1    | Χ | Χ | 0              | 0 | 0 | 0 | 0 | 0 | 0  | 0    | 0   | 0 | 0 | 0 | 0 | 0 | 0                     | 0 | D1              | D5      |

| TXD2    | Χ | Χ | 1              | 1 | 1 | 1 | 1 | 1 | 1  | 1    | 1   | 1 | 1 | 1 | 1 | 1 | 1                     | 1 | D2              | D6      |

| TXD3    | Χ | Χ | 0              | 0 | 0 | 0 | 0 | 0 | 0  | 0    | 0   | 0 | 0 | 0 | 0 | 0 | 0                     | 1 | D3              | D7      |

| TX_EN   | 0 | 0 | 1              | 1 | 1 | 1 | 1 | 1 | 1  | 1    | 1   | 1 | 1 | 1 | 1 | 1 | 1                     | 1 | 1               | 1       |

- 1. 1st preamble nibble transmitted.

- 2. 1st sfd nibble transmittted.

- 3. 1st data nibble transmitted.

- 4. D0 thru D7 are the first 8 bits of the data field.

#### c.) Transmit Preamble and SFD bits

| Signals | Bit \ | /alu | е |   |   |   |   |   |   |   |   |   |    |   |   |   |    |   |     |                 |

|---------|-------|------|---|---|---|---|---|---|---|---|---|---|----|---|---|---|----|---|-----|-----------------|

| RXDO    | Х     | Χ    | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 11 | 1 | 1 | 1 | 12 | 1 | D03 | D4 <sup>4</sup> |

| RXD1    | Χ     | Χ    | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 0  | 0 | 0 | 0 | 0  | 0 | D1  | D5              |

| RXD2    | Χ     | Χ    | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 1  | 1 | 1 | 1 | 1  | 1 | D2  | D6              |

| RXD3    | Χ     | Χ    | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | Χ | 0  | 0 | 0 | 0 | 0  | 1 | D3  | D7              |

| $RX_DV$ | 0     | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1  | 1 | 1 | 1 | 1  | 1 | 1   | 1               |

- 1. 1st preamble nibble received. Device guaranteed to provide a minimum of 6 preamble nibbles.

- 2. 1st sfd nibble received.

- 3. 1st data nibble received.

- 4. D0 thru D7 are the first 8 bits of the data field.

#### d.) Receive Preamble and SFD Bits

Figure 2. MII Data Packet Format

RXD[3:0] on falling edges of the RX\_CLK clock. The RXD[3:0] data has the same packet format as the TXD[3:0] data and is specified in IEEE 802.3 specifications as shown in Figure 2. When the end of packet is detected, CRS and RX\_DV are deasserted. CRS and RX\_DV also stay deasserted if the Link Detect bit in the MI serial port bit is set to the Link Fail state.

The collision output, COL, is asserted whenever the collision condition is detected.

#### 3.2.2 MII Disable

The MII inputs and outputs can be disabled by setting the MII disable bit in the MI serial port Control register. When the MII is disabled, the MII inputs are ignored, the MII outputs are high impedance, and the AUI transmitter is idle. If the MI address lines, MDA[1:0], are pulled high during reset or powerup, the 8502 powers up and resets with the MII disabled. Otherwise, the 8501/8502 powers up and resets with the MII enabled.

#### 3.3 MANCHESTER ENCODER

The Manchester encoder converts the NRZ nibble data from the MII into a single Manchester encoded serial data stream and adds a start of idle (SOI) pulse at the end of the packet as specified in the IEEE 802.3 specifications. The Manchester encoding process combines clock and data such that the first half of the data bit contains the complement of the data, and the second half of the data bit contains the true data, as described in IEEE 802.3 specifications. This guarantees that a transition always occurs in the middle of the data bit cell. Manchester encoding of the data from TXD occurs only when TX EN is asserted.

#### 3.4 MANCHESTER DECODER

The Manchester decoder converts the serial data stream from the AUI receiver into NRZ data for the MII. Thus, the Manchester decoder performs clock and data recovery from the Manchester encoded serial data stream. In Manchester encoded data, the first half of the data bit contains the complement of the data, and the second half of the data bit contains the true data.

Clock recovery is done with a PLL. When valid data is not detected on the AUI input, an internal 10 MHz clock is applied to the input of the PLL. When valid data is detected on the AUI input, the PLL input is switched to the incoming AUI data. The PLL then recovers the clock by locking onto zero crossings of the preamble of the incoming signal from the AUI cable. The recovered clock frequency is 10 MHz. The PLL can lock onto the preamble signal in less than 12 transitions (bit times) and can reliably perform the data

recovery process with up to  $\pm 18$  nS of jitter on the AUI input. While the PLL is in the process of locking onto the preamble signal, some of the preamble data symbols are lost. The clock recovery process recovers enough preamble data symbols to pass at least 6 nibbles to the receive MII Media Independent Interface as shown in Figure 2.

Data recovery is performed by latching in data from the receiver with the recovered clock extracted by the PLL. The data is also converted from a single bit stream into nibble data according the format shown in Figure 2.

#### 3.5 AUI TRANSMITTER

#### 3.5.1 Transmitter

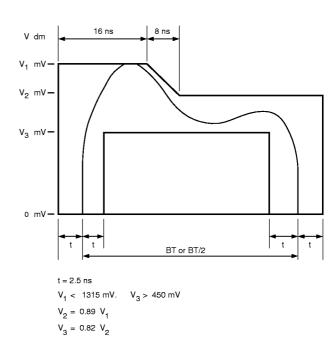

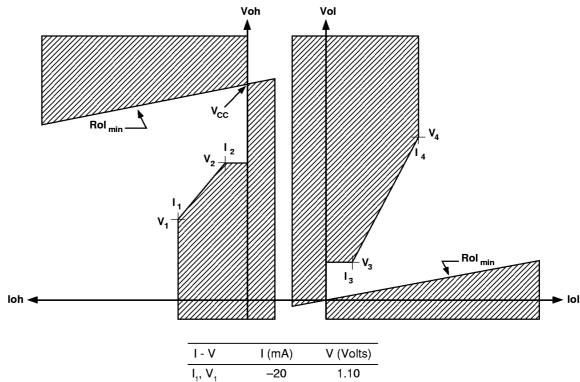

The AUI (Attachement Unit Interface) transmitter takes the Manchester encoded data, shapes it to meet the pulse template outlined in IEEE 802.3 and shown in Figure 3, adjusts the output voltage to meet the IEEE 802.3 required levels for AUI, and drives the 78 Ohm AUI cable.

Figure 3. AUI Transmit Output Voltage Template

#### 3.5.2 Transmit Activity Indication

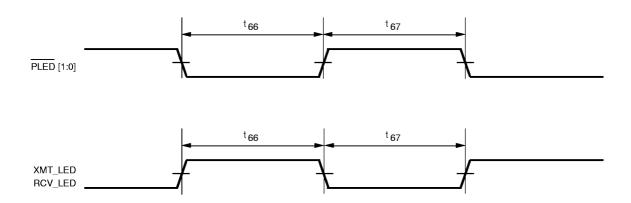

Activity can be programmed to appear on the PLED0 pin by appropriately setting the programmable LED output select bits in the MI serial port Configuration register. When the PLED0 pin is programmed to be an activity detect output, this pin is asserted low for 50 mS every time a transmit or receive packet occurs. The PLED0 output is open drain with resistor pullup and can drive an LED from VCC or can drive another digital input.

XMT\_LED is transmit activity output during normal operation. This pin is asserted high for 50 mS every time a transmit packet occurs. The XMT\_LED output can drive an LED to GND or can drive another digital input.

#### 3.5.3 Transmit Disable

The AUI transmitter can be disabled by setting the transmit disable bit in the MI serial port Configuration register. When the transmit disable bit is set, the AUI transmitter is forced into the idle state, and no data is transmitted regardless of the state of TX EN.

#### 3.5.4 Transmit Powerdown

The AUI transmitter can be powered down by setting the transmit powerdown bit in the MI serial port Configuration register. When the transmit powerdown bit is set, the AUI transmitter is powered down, the AUI transmit output is high impedance, and the rest of the device operates normally.

#### 3.6 AUI RECEIVER

#### 3.6.1 Receiver

The AUI (Attachement Unit Interface) receiver converts AUI levels to internal digital levels. There are two AUI receivers on the 8502, one for data (DI $\pm$ ) and one for collision (CI $\pm$ ).

The AUI inputs on the DI $\pm$  pins are internally biased to about 3V by internal 10K bias resistors. The AUI inputs first pass through a low pass filter designed to eliminate high frequency noise on the input. The output of the receive filter then goes to two different types of comparators, threshold and zero crossing. The threshold comparator determines whether the signal is valid, and the zero crossing comparator is used to sense the actual data transitions once the signal is determined to be valid data. The output of the threshold comparator goes to the

squelch circuit; the output of the zero crossing comparator is used for clock and data recovery.

The AUI inputs on the  $Cl\pm$  pins are internally biased to about 3V by internal 10K bias resistors. The AUI inputs first pass through low pass filter designed to eliminate high frequency noise on the input. The output of the collision receive filter then goes to a collision threshold comparator which converts the  $Cl\pm$  inputs to internal digital levels. The output of the collision threshold comparator then goes to the collision detect circuit.

#### 3.6.2 Squelch

The squelch block determines if the data from the threshold comparators (and hence, AUI inputs) contains valid data. The threshold comparator compares the DI $\pm$  and CI $\pm$ inputs against a fixed negative threshold, called the AUI squelch level. If the input voltage to the threshold comparator does not exceed the fixed negative threshold level, the receiver is in the squelched state. If the input voltage exceeds the negative squelch level for more than 20 nS, the data is considered to be valid and the receiver now enters into the unsquelch state. In the unsquelch state, the AUI receive threshold level is reduced by approximately 30% for noise immunity reasons and is called the unsquelch level. While in the unsquelch state, the receive squelch circuit looks for SOI (Start Of Idle) pulse to locate the end of the packet. When the SOI signal is detected, the receive squelch is turned on again. The AUI receiver meets the AUI receive requirements defined in IEEE 802.3 Section 7.

#### 3.6.3 Receive Activity Indication

Activity can be programmed to appear on the PLED0 pin by appropriately setting the programmable LED output select bits in the MI serial port Configuration register. When the PLED0 pin is programmed to be an activity detect output, this pin is asserted low for 50 mS every time a transmit or receive packet occurs. The PLED0 output is open drain with resistor pullup and can drive an LED from VCC or can drive another digital input.

RCV\_LED is receive activity output during normal operation. This pin is asserted high for 50 mS every time a receive packet occurs. The RCV\_LED output can drive an LED to GND or can drive another digital input.

#### 3.7 COLLISION

#### 3.7.1 General

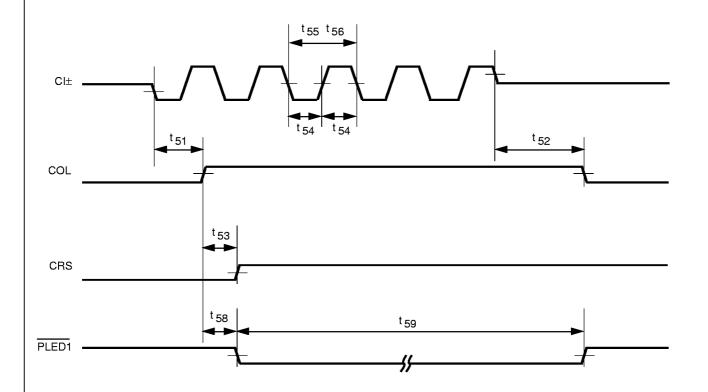

Collision is detected whenever the collision detect algorithm senses a valid 10 MHz signal on the Cl± collision inputs. When collision is detected, the COL output is asserted, CRS is asserted, and RX\_DV is deasserted. The collision function is disabled if the device is in the Full Duplex mode or if the Link Status bit in the MI serial port Status register is set to the Link Fail state.

#### 3.7.2 Collision Detect Algorithm

The collision detect circuit looks for a valid 10 MHz signal by monitoring the period of the waveform from the  $Cl\pm$  inputs. If the period of the input waveform on  $Cl\pm$  is between 77-200 nS, the collision signal is considered to be valid and collision is asserted. If the period of the input waveform on  $Cl\pm$  is less than 48 nS or greater than 400 nS, then collision is deasserted. Any high and low pulse widths less than 10 nS are rejected as noise.

#### 3.7.3 Collision Indication

Collision detect can be programmed to appear on the PLED1 pin by appropriately setting the programmable LED output select bits in the MI serial port Configuration register. When the PLED1 pin is programmed to be a collision detect output, this pin is asserted low for 50 mS every time a collision occurs. The PLED1 output is open drain with resistor pullup and can drive an LED from VCC or can drive another digital input.

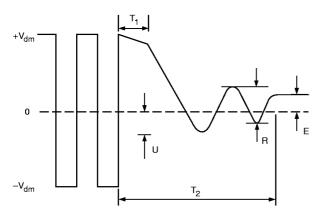

$T_1 = 200 \text{ ns Minimum}$

$T_2 = 8000 \text{ ns}$

U = −100 mV Maximum Undershoot

E = +/-40 mV Max

$R = \langle 200 \text{ mV PK} - \text{PK} \rangle$

Figure 4. AUI Transmit SOI Output Voltage Template

#### 3.7.4 Collision Test

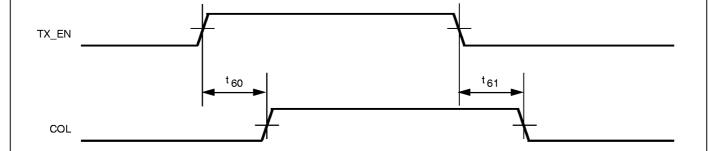

The MII collision signal, COL, can be tested by setting the collision test bit in the MI serial port Control register. When this bit is set, TX\_EN is looped back onto COL and the AUI trasmitter is forced to the idle state.

#### 3.8 SOI (START OF IDLE)

The SOI pulse is a positive pulse inserted at the end of every transmitted packet to indicate the end of data transmission and the start of idle.

The AUI transmitter generates an SOI pulse at the end of data transmission when TX\_EN is deasserted. The transmitted SOI output pulse meets the pulse template requirements specified in IEEE 802.3 Section 7 and shown in Figure 4.

The AUI receiver detects the SOI pulse by sensing missing data transitions. Once the SOI pulse is detected, data reception is ended and CRS is deasserted.

#### 3.9 FULL DUPLEX MODE

Full Duplex mode allows transmission and reception to occur simultaneously without a collision being signalled. When Full Duplex mode is enabled, collision is disabled, COL is deasserted regardless of the input on Cl±, and any loopback of TX EN to CRS is disabled, if enabled.

The device can be forced into the Full Duplex Mode by setting the duplex bit in the MI serial port Control register.

#### 3.10 LOOPBACK

Two different loopback modes are available on the 8502: (1) TX\_EN to CRS Loopback, and (2) diagnostic loopback.

TX\_ENto CRS Loopback is enabled by setting the TX\_EN to CRS Loopback bit in the MI serial port Configuration register. When this loopback mode is enabled, TX\_EN is looped back onto CRS during every transmit packet. This TX\_EN to CRS Loopback is disabled during collision, when the device is placed in the Full Duplex mode, when the Link Status bit in the MI serial port Status register is in the Link Fail state, when the transmit disable bit is set in the MI serial port Configuration register, and any other conditions where the transmitter is disabled.

A diagnostic loopback mode can also be selected by setting the loopback bit in the MI serial port Control register. When diagnostic loopback is enabled, TXD[3:0] data is looped back onto RXD[3:0], TX\_EN is looped back onto CRS, RX\_DV operates normally, and the AUI receive and transmit paths are disabled.

#### 3.11 LINK

#### 3.11.1 General

The status of the link is reported with the link status bit in the MI serial port Status register. The Link Status bit (LINK bit) can either be controlled by an internal link algorithm or externally with the LINKI pin. The selection of the method to set the LINK bit is determined by the LINKI pin. The LINKI input pin is a three level pin. If LINKI=1 or 0, the 1 or 0 value is inverted and automatically passed through to the LINK bit in the MI serial port Status register. If the LINKI pin is left floating, the pin floats to VCC/2 and this level indicates to the device that the internal link algorithm should be used for setting the LINK bit.

#### 3.11.2 Link Algorithm

The internal link algorithm is enabled by letting the  $\overline{LINKI}$  pin float. The internal link algorithm starts by setting the LINK bit to the pass state when the device is powered up. This bit stays in the pass state until a packet is transmitted. When a packet is transmitted, the internal link algorithm expects a corresponding receive packet to arrive at the AUI inputs within 2  $\mu$ S. If the expected receive packet arrives within 2  $\mu$ S after the start of a transmission, the LINK bit stays in the Link Pass state. If the expected receive packet doesn't arrive within 2  $\mu$ S, then the LINK bit goes to the Link Fail state. Since the LINK bit is an R/LL bit (see section 3.18.4), it latches itself whenever it goes low (Link Fail) and stays low until read out. Once it is read out, then it returns high to the Link Pass state.

#### 3.11.3 Link Indication

Link Detect can be programmed to appear on the PLED1 pin by appropriately setting the PLED configuration bit and the programmable LED output select bits in the MI serial port Configuration register. When the PLED1 pin is programmed to be a link detect output, this pin is asserted low whenever the device is in the Link Pass State. The PLED1 output is open drain with resistor pullup and can drive an LED from VCC or can drive another digital input.

#### 3.12 JABBER

The Jabber Detect bit in the MI serial port Status register is used to report the jabber condition. The 8502 does not have a jabber detect circuit, but the Jabber Detect bit (JAB bit) can be controlled externally with the JABI pin. Thus, if JABI = 1 or 0, the 1 or 0 value is inverted and automatically passed through to the JAB bit in the MI serial port Status register.

#### 3.13 RESET

The 8502 is reset when either VCC is applied to the device or when the reset bit is set in the MI serial port Control register. When reset bit is set to a 1, an internal power-on reset pulse is generated which resets all internal circuits, attempts to access an external EEPROM to load the MI serial port bits, forces the MI serial port bits to either their default values or to the contents of the external EEPROM, and latches in the MI physical address values on PLED[1:0]/MDA[1:0]. After the power-on reset pulse has finished, the reset bit in the MI serial port Control register is cleared to a 0 and the device is ready for normal operation 500 mS after the reset was initiated.

#### 3.14 POWERDOWN

The 8502 can be powered down by setting the powerdown bit in the MI serial port Control register. In powerdown mode, the AUI outputs are in high impedance state, all functions are disabled except the MI serial port, and the power consumption is reduced to less than 10 mW. When the device goes from powerdown to powerup state, the device is ready for normal operation 500 mS after powerdown was deaserted (powerdown bit cleared).

#### 3.15 OSCILLATOR

The 8502 requires a 20 MHz reference frequency for internal signal generation. This 20 MHz reference frequency can be generated by either connecting an external 20 MHz crystal between OSCIN and GND or an external 20 MHz clock on OSCIN.

#### 3.16 LED DRIVERS

The PLED[1:0] outputs are open drain with a resistor pullup. These outputs can drive LED's tied to VCC.

The PLED[1:0] outputs can be individually programmed through the MI serial port to do 4 different functions: (1) Normal Function (2) On, (3) Off, and (4) Blink.

PLED[1:0] can be individually programmed by appropriately setting the LED output select bits in the MI serial port Configuration register. When PLED[1:0] are programmed for their Normal function, these outputs indicate the specific functions described in the MI serial port Configuration register shown on Table 9 (Collision, Activity, respectively). When PLED[1:0] are programmed to be On, the LED output drivers goes low, thus turning on the LED under user control. When PLED[1:0] are programmed to be Off, the LED output drivers will turn off, thus turning off

the LED under user control. When PLED[1:0] are programmed to Blink, the LED output drivers will continuously blink at a rate of 50 mS on, 50 mS off.

The default Normal functions for PLED1 and PLED0 are Collision Detect and Activity, respectively. The Normal function for PLED1 can be changed from Collision Detect to Link Detect by setting the PLED1 Configuration Select bit in the MI serial port Configuration register. When this bit is set, the Normal function for PLED1 changes from Collision to Link. That is, for PLED1 to be a Link Detect output, the PLED1 Configuration Select and PLED1 Output Select bits must all be high.

XMT\_LED and RCV\_LED outputs can drive LEDs to GND indicating transmit and receive activity respectively. They are asserted high for 50 mS every time a transmit or a receive packet occurs.

#### 3.17 MI SERIAL PORT

#### 3.17.1 Signal Description

The MI serial port has four pins, MDC, MDIO, and MDA[1:0]. MDC is the serial shift clock input. MDIO is a bidirectional data I/O pin. MDA[1:0] are address pins for the MI serial port.

MDA[1:0] inputs share the same pins as the PLED[1:0] outputs, respectively. At powerup or reset, the PLED[1:0] output drivers are high impedance for an interval towards the end of the poweron reset time. During this interval, the values on these pins are latched into the device, inverted, and used as the MI serial port addresses.

#### 3.17.2 Timing

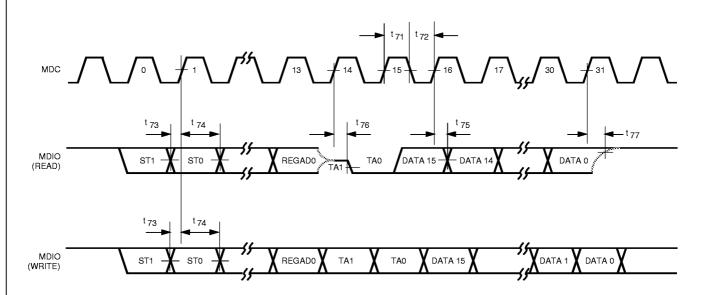

The MI serial port is idle when at least 32 continuous 1's are detected on MDIO, and it remains idle as long as continuous 1's are detected. During idle, MDIO is in the high impedance state. When the MI serial port is in the idle state, a 01 pattern on the MDIO pin initiates a serial shift cycle. Data on MDIO is then shifted in on the next 14 rising edges of MDC (MDIO is high impedance). If the multiple register access mode is not enabled, on the next 16 rising edges of MDC, data is either shifted in or out on MDIO,

depending on whether a write or read cycle was selected with the bits READ and WRITE. After the 32 MDC cycles have been completed, one complete register has been read/written, the serial shift process is halted, data is latched into the device, and MDIO goes into high impedance state. Another serial shift cycle cannot be initiated until the the idle condition (at least 32 continuous 1's) is detected.

#### 3.17.3 Multiple Register Access

Multiple registers can be accessed on a single MI serial port access cycle with the multiple register access feature. The multiple register access feature can be enabled by setting the multiple register access enable bit in the MI serial port Configuration register. When the multiple register access feature is enabled, multiple registers can be accessed on a single MI serial port access cycle by setting the register address to 11111 during the first 16 MDC clock cycles. There is no actual register residing in register address location 11111, so when the register address is then set to 11111, all five registers are accessed on the 80 rising edges of MDC that occur after the first 16 MDC clock cycles of the MI serial port access cycle. The registers are accessed in numerical order from 0 to 16. After all 96 MDC clocks have been completed, all the registers have been read/written, the serial shift process is halted, data is latched into the device, and MDIO goes into high impedance state. Another serial shift cycle cannot be initiated until the the idle condition (at least 32 continuous 1's) is detected.

#### 3.17.4 Bit Types

Since the serial port is bidirectional, there are many types of bits. Write bits (W) are inputs during a write cycle and are high impedance during a read cycle. Read bits (R) are outputs during a read cycle and high impedance during a write cycle. Read/Write bits (R/W) are actually write bits which can be read out during a read cycle. R/WSC bits are R/W bits that clear themselves after a set period of time or after a specific event has completed. R/LL bits are read bits that latch themselves when they go low, and they stay latched low until read. After they are read, they are reset

high. R/LH bits are the same as R/LL bits except that they latch high. The bit type definitions are summarized in Table 1

Table 1. MI Register Bit Type Definition

| Sym.     | Name                | Definit             | tion                                   |

|----------|---------------------|---------------------|----------------------------------------|

|          |                     | Write Cycle         | Read Cycle                             |

| W        | Write               | Input               | NoOperation,<br>HiZ                    |

| R        | Read                | NoOperation,<br>HiZ | Output                                 |

| RW       | Read/<br>Write      | Input               | Ouput                                  |

| RWS<br>C | Read/<br>Write Self | Input               | Output                                 |

|          | Clearing            |                     | Clears Itself After                    |

|          |                     |                     | Operation                              |

|          |                     |                     | Completed                              |

| RILL     | Read/<br>Latching   | NoOperation,<br>HiZ | Output                                 |

|          | Low                 |                     | When Bit Goes                          |

|          |                     |                     | Low,<br>BitLatched.                    |

|          |                     |                     |                                        |

|          |                     |                     | When Bit Is Read,<br>Bit Updated.      |

| RLH      | Read/<br>Latching   | NoOperation,<br>HiZ | Output                                 |

|          | High                |                     | When Bit Goes<br>High,<br>Bit Latched. |

|          |                     |                     | When Bit Is Read,<br>Bit Updated.      |

#### 3.17.5 Frame Structure

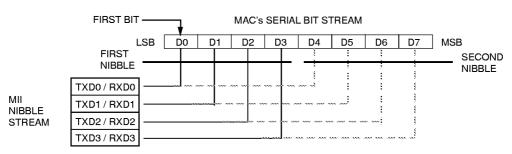

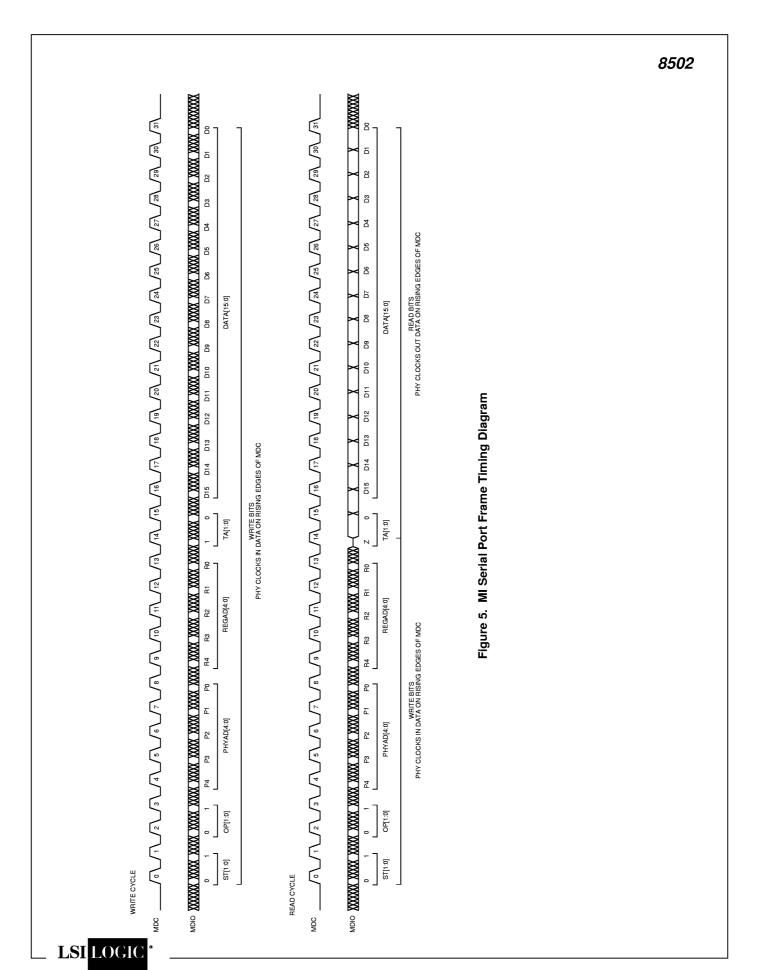

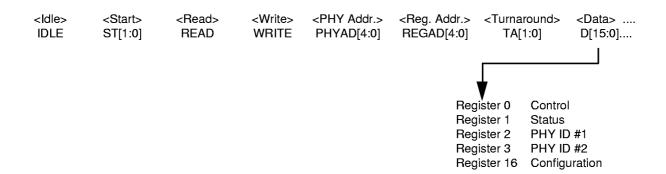

The structure of the serial port frame is shown in Table 2 and a timing diagram of a frame is shown in Figure 5. Each serial port access cycle consists of 32 bits (or 96 bits if multiple register access is enabled and REGAD=11111), exclusive of idle. The first 16 bits of the serial port cycle are always write bits and are used for addressing. The last 16(80) bits are to or from one(all) of the five data registers.

The first 2 bits in Table 2 and Figure 5 are start bits and need to be written as a 01 for the serial port cycle to continue. The next 2 bits are a read and write bit which determine if the accessed data register bits will be read from or written to. The next 3 bits are upper device addresses and they must be written as 111 for the serial

port access to continue. The next 2 bits are lower device address and must match the inverted values latched in from pins MDA[1:0] during the poweron reset time for the serial port access to continue. The next 5 bits are register address select bits which select one or all of the five data registers for access. The next 2 bits are turnaround bits which are not actual register bits but extra time to switch MDIO from write to read if necessary, as shown in Figure 5. The final 16 bits of the MI serial port cycle (or 80 bits if multiple register access is enabled and REGAD=11111) are to or from the data register designated in the register address bits REGAD[4:0].

#### 3.17.6 Register Structure

The 8502 has five internal 16 bit registers. All five registers are available for setting configuration inputs and reading status outputs. A map of the registers is shown in Table 3. The five registers consist of four registers that are defined by the IEEE 802.3 specification (Registers 0-3) and one register that is unique to the 8502 (Register 16).

The structure and bit definition of the Control register is shown in Table 4. This register stores various configuration inputs and its bit definition complies with the IEEE 802.3 specifications.

The structure and bit definition of the Status register is shown in Table 5. This register contains device capabilities and status output information. and its bit definition complies with the IEEE 802.3 specifications.

The structure and bit definition of the PHY ID #1 and #2 registers is shown in Tables 6 and 7, respectively. These registers contain an identification code unique to the 8502 and their bit definition complies with the IEEE 802.3 specifications.

The structure and bit definition of the Configuration register is shown in Table 8. This register stores various configuration inputs.

#### 3.17.7 Link Status Bit

The Link Status bit in the Status register is controlled by either the internal link algorithm or by direct pass through from the LINKI pin. Refer to the Link section for further details.

#### 3.17.8 Jabber Detect Bit

The Jabber Detect bit in the Status register is controlled by direct pass through from the JABI pin. Refer to the Jabber section for further details.

#### 3.18 Register Description

Table 2. MI Serial Port Frame Structure

| Symbol     | Name                       | Definition                                                                                                                                                                          | R/W |

|------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| IDLE       | Idle Pattern               | These Bits Are an Idle Pattern. Device Will Not Initiate An MI Cycle Until It Detects At Least 32 1's.                                                                              | W   |

| ST1<br>ST0 | Start Bits                 | When ST[1:0]=01, A MI Serial Port Access Cycle Starts.                                                                                                                              | W   |

| READ       | Read Select                | 1 = Read Cycle                                                                                                                                                                      | W   |

| WRITE      | Write Select               | 1 = Write Cycle                                                                                                                                                                     | W   |

| PHYAD[4:0] | Physical Device<br>Address | When PHYAD[4:2]=000 and PHY[1:0]=MDA[1:0] Pins Inverted, The MI Serial Port Is Selected For Operation.                                                                              | W   |

| REGAD[4:0] | Register Address           | If REGAD=00000-11111, These Bits Determine The Register From Which D[15:0] Is Read/Written. If Multiple Register Access Is Enabled And REGAD=11111, All Registers Are Read/Written. | W   |

| TA1<br>TA0 | Turnaround Time            | These Bits Provide Some Turnaround Time For MDIO  When READ=1, TA[1:0]=Z0 When WRITE=1, TA[1:0]=ZZ                                                                                  | R/W |

| D[15:0]    | Data                       | These 16 Bits Contain Data To/From One Of The Five Registers Selected By Register Address Bits REGAD[4:0].                                                                          | Any |

IDLE is shifted in first

Table 3. MI Serial Port Register Map

| SPEED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | # Register       | x.15       | x.14     | x.13     | x.12     | Ę,       | x.10   | x.9      | 8.<br>X   | X.7      | <b>x.</b> 6 | X.5      | ×          | 4        |          | x.4 x.3 x.2    | x.3 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|----------|----------|----------|----------|--------|----------|-----------|----------|-------------|----------|------------|----------|----------|----------------|-----|

| RW         RW<                                                                                                                                                                                                                                                                                                               | 0 Control        | RST        | LPBK     | SPEED    |          | PDN      | _      | ANEG_RST | DPLX      | COLTST   | 0           | 0        | 0          |          | 0        | 0              |     |

| CAP_TXH         CAP_TF         CAP_TH         0         0         0         0         CAP_SUPR         ANEG_ACK           R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R <t< td=""><td></td><td>R/WSC<br/>0</td><td>R/W<br/>0</td><td>R/W<br/>0</td><td>B/W<br/>0</td><td>R/W<br/>0</td><td>1 or 0</td><td>B/W<br/>0</td><td>B/W<br/>0</td><td>R/W<br/>0</td><td>B/W<br/>0</td><td>B/W<br/>0</td><td>B/W<br/>0</td><td></td><td>B/W<br/>0</td><td>R/W R/W<br/>0 0</td><td></td></t<>                                                      |                  | R/WSC<br>0 | R/W<br>0 | R/W<br>0 | B/W<br>0 | R/W<br>0 | 1 or 0 | B/W<br>0 | B/W<br>0  | R/W<br>0 | B/W<br>0    | B/W<br>0 | B/W<br>0   |          | B/W<br>0 | R/W R/W<br>0 0 |     |

| COUIZ1         OUIZ2         OUIZ3         OUIZ4         OUIZ4 <t< td=""><td></td><td>CAB</td><td></td><td></td><td></td><td>OF GAC</td><td>c</td><td>c</td><td>c</td><td></td><td>00119</td><td></td><td>1</td><td>H</td><td>Sala</td><td></td><td></td></t<> |                  | CAB        |          |          |          | OF GAC   | c      | c        | c         |          | 00119       |          | 1          | H        | Sala     |                |     |

| R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R                                                                                                                                                                                                                                                                                                                                                                    | 1 Status         | 1          | _        | 7        |          |          | >      | >        | >         |          | OAL SULL    | AINEG AC | יא בואן על | _        | CAP      |                | LIN |

| 0         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                    |                  | Œ          | <u>~</u> | Œ        | Œ        | Œ        | Œ      | Œ        | Œ         | Œ        | Œ           | Œ        | Œ          |          | Œ        | R R/LL         |     |

| OUIS         OUIG         OUIS         OUIS         OUIS         OUID         OUIT         OUIT <th< td=""><td></td><td>0</td><td>0</td><td>0</td><td>-</td><td>-</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td>0</td><td></td><td>0</td><td></td><td>-</td></th<>                                             |                  | 0          | 0        | 0        | -        | -        | 0      | 0        | 0         | 0        | 0           | 0        | 0          |          | 0        |                | -   |

| OUIS         OUIS         OUIS         OUIS         OUIS         OUIS         OUIT         OUITS         OUITS<                                                                                                                                                                                          |                  |            |          |          |          |          |        |          |           |          |             |          |            |          |          |                |     |

| B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B                                                                                                                                                                                                                                                                                                                                                                    | 2 PHY ID#1       | SINO       | OUI4     | OUIS     | 9INO     | 2INO     | SINO   | 6INO     | OUI10     | OUI11    | OUI12       | OUI13    | OUI14      | OUI15    | 15       | 115 OU116      |     |

| 0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                    |                  | Œ          | Œ        | œ        | œ        | Œ        | Œ      | Œ        | <u>«</u>  | <u>~</u> | <u>~</u>    | <u>~</u> | œ          | <u>~</u> |          |                |     |

| OUI21         OUI22         OUI23         OUI24         PART5         PART4         PART3         PART2         PART1           R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R         R                                                                                                                                                                                                                                                                                                                                                            |                  | 0          | 0        | 0        | 0        | 0        | 0      | 0        | 0         | 0        | 0           | 0        | -          | 0        |          | -              | -   |

| OUI21         OUI22         OUI23         OUI24         PARI5         PARI5         PARI7         PARI7 <th< td=""><td></td><td>222.655</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>-</td><td></td><td></td></th<>               |                  | 222.655    |          |          |          |          |        |          |           |          |             |          |            |          | -        |                |     |

| R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3 PHY ID #2      | OUI19      | ONI20    | OUI21    | OUI22    | OUI23    | OUI24  | PART5    | PART4     | PART3    | PART2       | PART1    | PART0      | RE       | ဗ        | /3 REV2        |     |

| 1 1 1 1 0 0 0 0 0 1 0 TXEN_CRS MREG 0 0 0 0 PLED1_1 PLED1_0 PLED0_1 RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  | Œ          | Œ        | œ        | œ        | œ        | œ      | Œ        | <u>ac</u> | Œ        | <u>ac</u>   | Œ        | Œ          |          | ~        | - B            |     |

| 0 TXEN_CRS MREG 0 0 0 PLED1_1 PLED1_0 PLED0_1 PLED0_1 PLED0_1 PLED0_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | -          | -        | -        | -        | -        | 0      | 0        | 0         | 0        | 0           | -        | 0          | 0        |          |                | 0   |

| 0 TXEN_CRS MREG 0 0 0 PLED1_1 PLED1_0 PLED0_1 PLED0_1 PLED0_1 PLED0_1 PLED0_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |            |          |          |          |          |        |          |           |          |             |          |            |          |          |                |     |

| BW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16 Configuration | XMT DIS    | XMT_PDN  | 0        | TXEN_CRS |          | 0      | 0        | 0         | PLED1_1  | PLED1_0     |          | PLED0_0    | PLED1    | CFG      | CFG 0          |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  | RW         | B/W      | ₽.W      | B/W      | B/W      | R/W    | B/W      | B/W       | B/W      | B/W         | R/W      | RW         | R/W      | >        | V R/W          |     |

Table 4. MI Register 0 (Control) Structure And Bit Definition

| 0.15   | 0.14 | 0.13  | 0.12    | 0.11 | 0.10    | 0.9      | 8.0  |

|--------|------|-------|---------|------|---------|----------|------|

| RST    | LPBK | SPEED | ANEG_EN | PDN  | MII_DIS | ANEG_RST | DPLX |