## **NS32203-10 Direct Memory Access Controller**

## **General Description**

The NS32203 Direct Memory Access Controller (DMAC) is a support chip for the Series 32000® microprocessor family designed to relieve the CPU of data transfers between memory and I/O devices. The device is capable of packing data received from 8-bit peripherals into 16-bit words to reduce system bus loading. It can operate in local and remote configurations. In the local configuration it is connected to the multiplexed Series 32000 bus and shares with the CPU, the bus control signals from the NS32201 Timing Control Unit (TCU). In the remote configuration, the DMAC, in conjunction with its own TCU, communicates with I/O devices and/or memory through a dedicated bus, enabling rapid transfers between memory and I/O devices. The DMAC provides 4 16-bit I/O channels which may be configured as two complementary pairs to support chaining.

### **Features**

- Direct or Indirect data transfers

- Memory to Memory, I/O to I/O or Memory to I/O transfers

- Remote or Local configurations

- 8-Bit or 16-Bit transfers

- Transfer rates up to 5 Megabytes per second

- Command Chaining on complementary channels

- Wide range of channel commands

- Search capability

- Interrupt Vector generation

- Simple interface with the Series 32000 Family of Microprocessors

- High Speed XMOS™ Technology

- Single +5V Supply

- 48-Pin Dual-In-Line Package

## **Block Diagram**

## 4

## **Table of Contents**

| 1.0 PRODUCT INTRODUCTION                 | 3.0 ARCHITECTURAL DESCRIPTION (Continued)    |

|------------------------------------------|----------------------------------------------|

| 2.0 FUNCTIONAL DESCRIPTION               | 3.3 Parameter Registers                      |

| 2.2 Data Transfer Operations             | 3.3.1 SRC - Source Address Register          |

| 2.2.1 Indirect Data Transfers            | 3.3.2 DST - Destination Address Register     |

| 2.2.2 Direct (FLYBY) Data Transfers      | 3.3.3 LNGT - Block Length Register           |

| 2.3 Local Configuration                  | 4.0 DEVICE SPECIFICATIONS                    |

| 2.4 Remote Configuration                 | 4.1 NS32203 Pin Descriptions                 |

| 2.5 Data Source (Destination) Attributes | 4.1.1 Supplies                               |

| 2.6 Word Assembly/Disassembly            | 4.1.2 Input Signals                          |

| 2.7 Auto Transfer                        | 4.1.3 Output Signals                         |

| 2.8 Search                               | 4.1.4 Input/Output Signals                   |

| 2.9 Interrupts                           | 4.2 Absolute Maximum Ratings                 |

| 2.10 Transfer Modes                      | 4.3 Electrical Characteristics               |

| 2.11 Chaining                            | 4.4 Switching Characteristics                |

| 2.12 Channel Priorities                  | 4.4.1 Definitions                            |

| 3.0 ARCHITECTURAL DESCRIPTION            | 4.4.2 Timing Tables                          |

| 3.1 Global Registers                     | 4.4.2.1 Output Signals: Internal Propagation |

| 3.1.1 CONF - Configuration Register      | Delays                                       |

| 3.1.2 HVCT - Hardware Vector Register    | 4.4.2.2 Input Signal Requirements            |

| 3.1.3 SVCT - Software Vector Register    | 4.4.2.3 Clocking Requirements                |

| 3.1.4 STAT - Status Register             | 4.4.3 Timing Diagrams                        |

| 3.2 Control Registers                    | Appendix A: Interfacing Suggestions          |

### List of Illustrations

3.2.1 COM - Command Register 3.2.2 SRCH - Search Register

| List of filestrations                                          |

|----------------------------------------------------------------|

| Power-on Reset Requirements2-1                                 |

| General Reset Timing2-2                                        |

| Recommended Reset Connections                                  |

| Indirect Read Cycle2-4                                         |

| Indirect Write Cycle (Single Transfer Mode)                    |

| Direct Memory-To-I/O Data Transfer (Single Transfer Mode)      |

| Direct I/O-To-Memory Data Transfer (Single Transfer Mode)      |

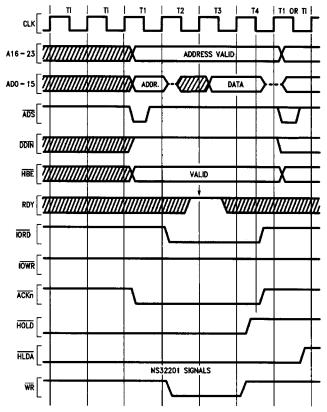

| NS32203 Interconnections2-8                                    |

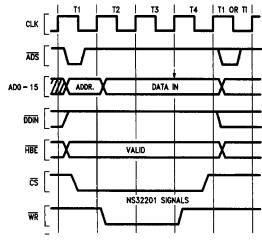

| Write to NS32203 Internal Registers                            |

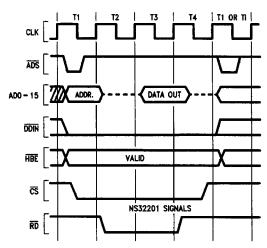

| Read from NS32203 Internal Registers                           |

| NS 32203 Internal Registers                                    |

| NS32203 Connection Diagram4-1                                  |

| Timing Specification Standard (Signal Valid After Clock Edge)  |

| Timing Specification Standard (Signal Valid Before Clock Edge) |

| Write to DMAC Registers                                        |

| Read From DMAC Registers                                       |

| Clock Timing                                                   |

| Indirect Write Cycle                                           |

| Indirect Read Cycle                                            |

| Direct I/O-To-Memory Transfer                                  |

| Direct Memory-To-I/O Transfer                                  |

| HOLD/HOLDA Sequence Start                                      |

| HOLD/HOLDA Sequence End 4-12                                   |

| Bus Request/Grant Sequence Start                               |

| Bus Request/Grant Sequence End                                 |

| Ready Sampling                                                 |

| REQn/ACKn Sequence (DMAC Initially Not Idle)                   |

| REQn/ACKn Sequence (DMAC Initially Idle)                       |

| Halted Cycle                                                   |

| Interrupt On Match/No Match                                    |

| Interrupt On Halt4-21                                          |

| Power-on Reset                                                 |

| Non-Power-on Reset                                             |

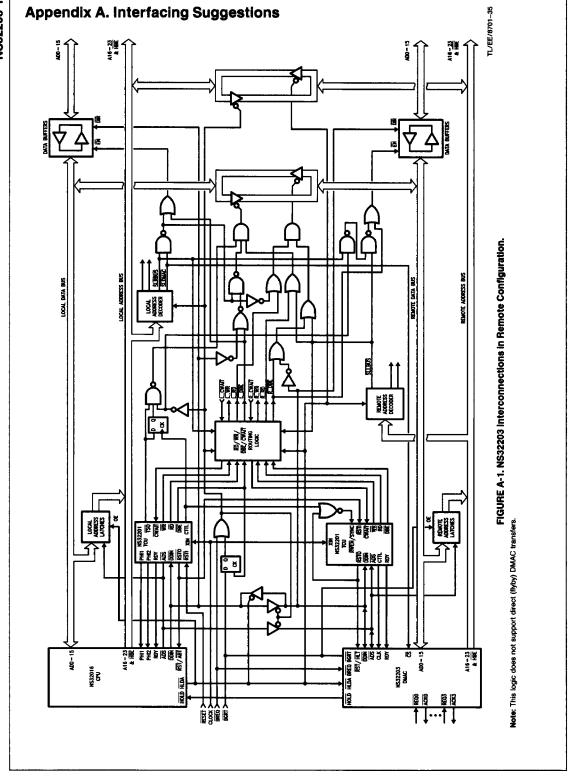

| NS32203 Interconnections in Remote Configuration               |

| A-1                                                            |

### 1.0 Product Introduction

The NS32203 Direct Memory Access Controller (DMAC) is specifically designed to minimize the time required for high speed data transfers in a Series 32000-based computer system. It includes a wide variety of options and operating modes to enhance data throughput and system optimization, and to allow dynamic reconfiguration under program control.

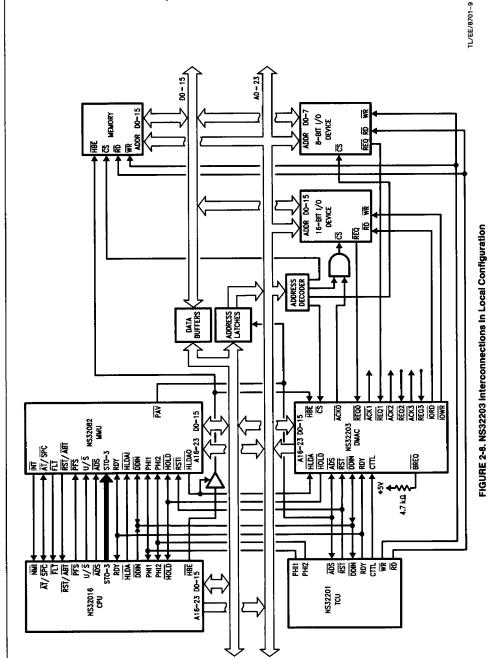

The NS32203 can operate in two basic system configurations: local and remote. In the local configuration, the DMAC and the CPU share the same bus (address, data and control) and only one of them can perform data transfers on the bus at any one time. In this configuration, the DMAC and the CPU also share a Timing Control Unit (TCU) and a single set of address latches. Since this configuration yields a minimum part-count system, it offers a good cost/performance trade-off in many situations.

The remote configuration is intended to minimize the CPU bus use. In this configuration, the NS32203 I/O devices and optional buffer memory have their own dedicated bus (remote bus) so that an I/O transfer may be performed without loading the CPU bus (local bus).

Communication between the dedicated bus and the CPU bus may be initiated at any time by either the CPU or the NS32203. The DMAC accesses the CPU bus whenever a data transfer to/from memory or any I/O device residing on this bus is to be performed. The CPU, in turn, accesses the dedicated bus for reading status data or for programming either the DMAC or its I/O devices.

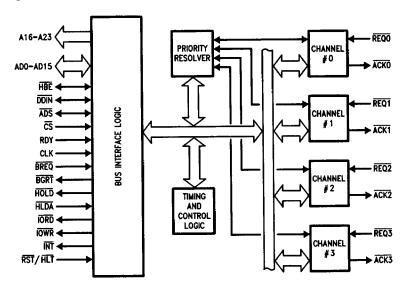

The NS32203 internal organization consists of seven functional blocks as illustrated in the block diagram. Descriptions of these blocks are given below.

**DMA Channels.** The NS32203 provides four channels. Each channel accepts a request from a peripheral I/O device and informs it when data transfer cycles are about to

begin. A set of registers is provided for each channel to control the type of operation for that channel.

Bus Interface Unit. The bus interface unit controls all data transfers between peripheral I/O devices and memory whenever the DMAC is in control of the bus. This unit also controls the transfer of data between the CPU and the DMAC internal registers.

Timing and Control Logic. This block generates all the sequencing and control signals necessary for the operation of the DMAC.

**Priority Resolver.** This block resolves contentions among channels requesting service simultaneously.

## 2.0 Functional Description

#### 2.1 RESETTING

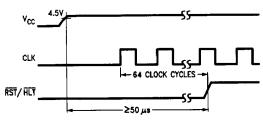

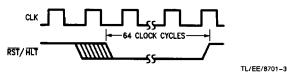

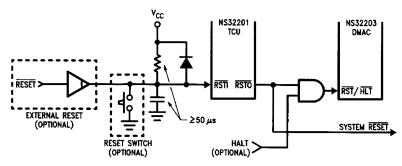

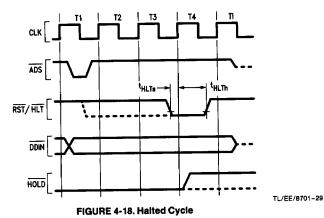

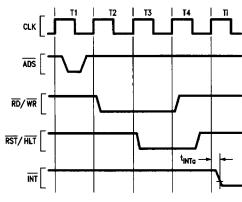

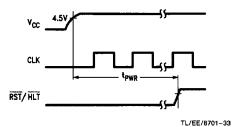

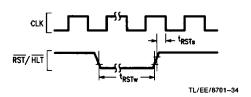

The RST/HLT line serves both as a reset input for the onchip logic and as a DMAC HALT input. Resetting is accomplished by pulling RST/HLT low for at least 64 clock cycles. Upon detecting a Reset, the DMAC terminates any Data transfer in progress, resets its internal logic and enters an inactive state. On application of power, RST/HLT must be held low for at least 50 µs after VCC is stable. This is to ensure that all on-chip voltages are stable before operation. Whenever reset is applied, the rising edge must occur while the clock signal on the CLK pin is high (see Figure 2-1 and 2-2). The NS32201 TCU provides circuitry to meet the reset requirements. Figure 2-3 shows the recommended connections. The HALT function is accomplished when RST/HLT is activated for 1 or 2 clock cycles and then released. It can be used to stop any data transfer in progress in case of a bus error. As soon as HALT is acknowledged by the NS32203, the current transfer operation is terminated. See Figure 4-18.

FIGURE 2-1. Power-On Reset Requirements

FIGURE 2-2. General Reset Timing

FIGURE 2-3. Recommended Reset Connections

TL/EE/8701-4

#### 2.2 DATA TRANSFER OPERATIONS

After the NS32203 has been initialized by software, it is ready to transfer blocks of data, containing up to 64 kbytes, between memory and I/O devices, without further intervention required of the CPU. Upon receiving a transfer request from an I/O device, the DMAC performs the following operations:

- 1) Acquires control of the bus

- Acknowledge the requesting I/O device which is connected to the highest priority channel.

- Starts executing data transfer cycles according to the values stored into the control registers of the channel being serviced.

- Terminates data transfers and relinquishes control of the bus as soon as one of the programmed conditions is met.

Each channel can be programmed for indirect or direct data transfers. Detailed descriptions of these transfer types are provided in the following sub-sections.

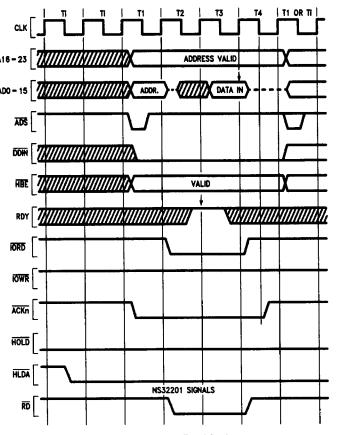

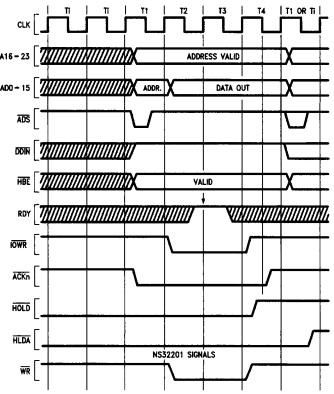

#### 2.2.1 Indirect Data Transfers

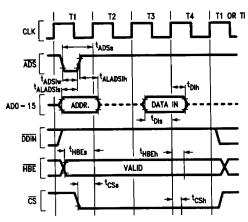

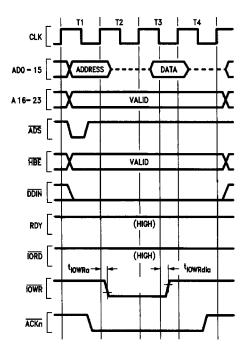

In this mode of operation, each byte or word transfer between source and destination requires at least two bus cycles. The data is first read into the DMAC and subsequently it is written into the destination. The bus cycles in this case are similar to the CPU bus cycles when the MMU is not used. This mode is slower than the direct mode, but is the only one that allows some data manipulation like Byte Search or Word Assembly/Disassembly. Figure 2-4 and 2-5 show the read and write cycle timing diagrams related to indirect data transfers. If a search operation is specified, extra clock cycles may be added following each read cycle.

TL/EE/8701-5 FIGURE 2-4. Indirect Read Cycle

TL/EE/8701-6

FIGURE 2-5. Indirect Write Cycle (Single Transfer Mode)

Note: If burst mode is selected, HOLD is released at the end of the transfer operation.

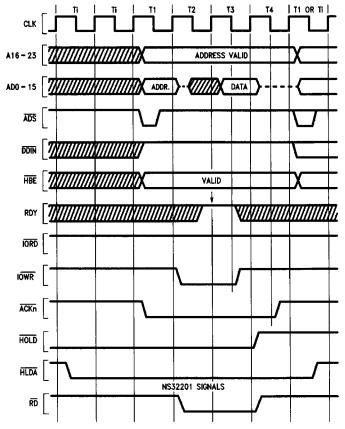

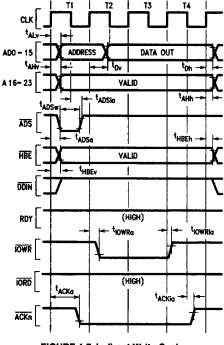

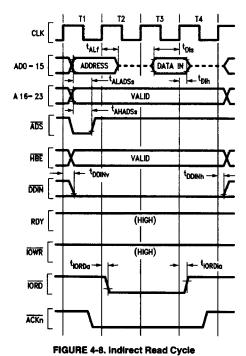

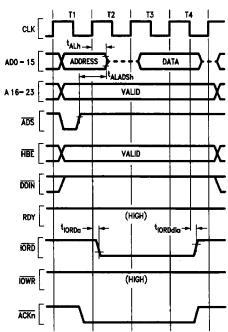

### 2.2.2 Direct (Flyby) Data Transfers

This mode of operation allows a very high data transfer rate between source and destination. Each data byte or word to be transferred requires only a single bus cycle instead of two separate read and write cycles, which are typical of the indirect mode. The DMAC accomplishes direct data transfers by activating  $\overline{IORD}$ , during memory write cycles, and  $\overline{IOWR}$ , during memory read cycles.

An I/O device, in the direct mode, is usually enabled by the proper acknowledge signal (ACKn) from the DMAC. No search or word assembly/disassembly are possible during

direct data transfers. Figures 2-6 and 2-7 show the timing diagrams of direct memory-to-I/O and I/O-to-memory transfers respectively.

Note 1: In the direct mode each channel can control only one I/O device because the I/O device is hardwired to the ACKR output of the corresponding channel, in the indirect mode, a channel can control multiple devices as long as each device is selected through its own address rather than the ACKR output. However, the possibility of selecting a single I/O device by the ACKR output is maintained in the indirect mode as well.

Note 2: Whenever the DMAC is either idle or is performing indirect transfers, it generates the IORD and IOWR signals as a replica of RD and WR. This simplifies the logic required to access I/O devices wired for direct data transfers.

FIGURE 2-6. Direct Memory-To-I/O Data Transfer (Single Transfer Mode)

#### 2.3 LOCAL CONFIGURATION

As previously mentioned, in the local configuration the DMAC shares with CPU and MMU the multiplexed address/data bus as well as the control signals from the NS32201 TCU. A typical local configuration is shown in Figure 2-8. The DMAC, in the local configuration, must gain control of the bus whenever a data transfer cycle is to be performed,

even though it is directed to an I/O device and is related to an indirect data transfer. This causes the system to be quite sensitive to the volume of data handled by the DMAC. Thus, the overall system performance decreases as the volume of data increases. A possible solution to this problem is to use the remote configuration, described in the following section. A significant advantage of the local configuration is its simplicity.

FIGURE 2-7. Direct I/O-To-Memory Data Transfer (Single Transfer Mode)

Nate 1: The 16 Bit I/O device is wired for direct transfers.

Note 2: The data buffers should not be enabled during direct data transfers or CPU accesses to the DMAC registers.

#### 2.4 REMOTE CONFIGURATION

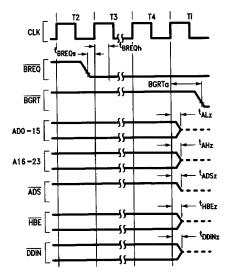

The remote configuration is intended to minimize CPU Bus usage. In this configuration, the DMAC, buffer memory and I/O devices reside on a dedicated bus. Communication between the dedicated bus and the CPU bus is achieved by means of TRI-STATE buffers. Whenever the CPU needs to access the dedicated bus, it issues a bus request to the NS32203 by activating the BREQ signal. As the dedicated bus becomes idle, the DMAC pulls off the bus and acknowledges the CPU request by activating BGRT. This output is also used as a control signal for the interconnection logic of the two buses.

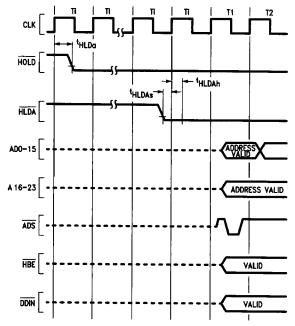

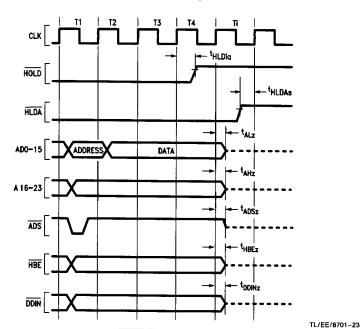

The CPU can either be interrupted by BGRT or it can poll BGRT to determine when the dedicated bus can be accessed. The DMAC, in turn, before accessing the CPU bus, has to gain control of it. This is accomplished through the usual request-acknowledge mechanism performed by means of the HOLD and HLDA signals.

Figure A-1 in Appendix A shows an interconnection diagram of a basic remote configuration. Both TCUs are clocked by the same clock signal. They are synchronized during reset by the RWEN/SYNC signal so that their output clocks are in phase. Figures 2-9 and 2-10 show the timing diagrams for read and write accesses to the NS32203 internal registers.

FIGURE 2-9. Write to NS32203 Internal Registers

TL/EE/8701-10

FIGURE 2-10. Read from NS32203 Internal Registers

#### 2.5 DATA SOURCE (DESTINATION) ATTRIBUTES

Two types of data source (destination) are recognized: I/O device and memory. If the source (destination) is an I/O device, its address register is not changed after a data transfer; if it is memory, its address register is either incremented or decremented after any data transfer, according to the value of the corresponding direction bit. In the remote configuration, any data source (destination) may reside either on the CPU bus or on the dedicated bus. If it resides on the dedicated bus, the NS32203 does not activate the HOLD request line when an access to the source (destination) is performed, unless a direct transfer with a data destination (source) residing on the CPU bus is required.

Data can be transferred in either 8 bit or 16 bit units. The DMAC always considers the memory to be 16 bits wide. Thus, if an 8 bit transfer is specified, address bit A0 will determine the byte of the data-bus where the transfer takes place. If A0=0, the transfer occurs on the low order byte. If A0=1, it occurs on the high order byte. Different transfer widths can be specified for source and destination. However, some limitations exist in specifying these transfer widths when certain operations must be performed. These limitations are explained below.

- If a transfer block has an odd number of bytes or is not word aligned, an 8 bit width for source and destination should be selected.

- 16-bit I/O transfers can not be specified with 8 bit memory transfers.

- 3) Memory to memory transfers should have the same width

Note 1: If source and destination are both memory, DMAC transfers can only be performed in indirect mode.

Note 2: If source and destination are both I/O devices and direct mode is being used, the source device is accessed by IORD and ACKn; the destination device is accessed by WR (from the NS32201) and CS (from the address decoder). This allows a one direction data transfer only from one I/O device (source) to another. If data is to be transferred in both directions in direct mode between two I/O devices, two channels must be used (one for each direction of transfer), and extra hardware is required to control the read and write signals to the two I/O devices.

Note 3: When an 8-bit transfer is related to an I/O device, the other half of the 16-bit data bus is considered as DON'T CARE, and the HBE/ signal may be activated.

#### 2.6 WORD ASSEMBLY/DISASSEMBLY

This feature is automatically enabled when indirect transfers are selected, with data transferred between an 8-bit wide I/O device and a 16-bit I/O device or memory. For every 16-bit I/O device or memory access, the DMAC accesses the 8-bit I/O device twice, assembling two data bytes into a 16-bit word or breaking a 16-bit word into two data bytes, depending on the direction of transfer. The word assembly/disassembly feature allows a significant increase in the transfer speed and minimizes the CPU bus usage when the transfer occurs between an 8-bit I/O device residing on the dedicated bus, and a 16-bit I/O device or memory residing on the CPU bus. Word assembly/disassembly is not possible during direct data transfers.

Note: Requests from other channels are not acknowledged in the middle of a word assembly disassembly. If this is unacceptable, 8 bit transfers should be specified for both source and destination.

#### 2.7 AUTO TRANSFER

The NS32203 initiates a data transfer as a result of a request from an I/O device. In some cases a data transfer may be necessary without the corresponding request signal being asserted. This can happen, for example, when a block of data is to be moved from one memory region to another. In such cases, the auto transfer mode can be selected by setting an appropriate bit in the command register. The DMAC will initiate a data transfer regardless of the REQn signal for that channel.

Note: For proper operation, when auto transfer is required, the low order byte of the command register (containing the auto-transfer enable bit) should be written into after the other registers controlling the channel operation have been initialized.

#### 2.8 SEARCH

The NS32203 provides a search capability that can be used to detect the occurrence of a certain data pattern. The search is performed by comparing each data byte with the search register, in conjunction with the mask register. An appropriate bit in the command register indicates whether the search continues 'UNTIL' a match occurs, or 'WHILE' a match exists. The search operation does not necessarily involve a data transfer. The DMAC allows a block of data to be searched without requiring any data transfer between source and destination. When performing a search, the user can specify whether or not the matched byte will be transferred. If 'INCLUSIVE SEARCH' is specified (INC = 1), the matched byte will be transferred, and the channel parameters will be updated accordingly. In this case, if a 16 bit word has been read from the data source and the search condition is satisfied by the low order byte, then the high order byte is transferred as well. If 'EXCLUSIVE SEARCH' is specified (INC = 0), the transfer will terminate with the last byte before the search condition was satisfied, and the parameters will point to the last transferred byte.

Search is not possible during direct transfers.

### 2.9 INTERRUPTS

The NS32203 provides interrupt circuitry that can be used to generate an interrupt whenever a data transfer is completed or a search condition is met. If an NS32202 ICU is used, the INT signal from the DMAC should be connected to an interrupt input of the ICU. When an interrupt occurs and the corresponding interrupt acknowledge (INTA) or return from interrupt (RETI) cycle is executed by the CPU, the NS32203 supplies its own vector as if it were a cascaded ICU. For such operation the virtual address of the interrupt vector register should be placed in the ICU cascade table, described in the NS32016 and NS32202 data sheets. See section 3.1.2.

#### 2.10 TRANSFER MODES

When the NS32203 is in the inactive state and a channel requests service, the DMAC gains control of the bus and enters the active state. It is in this state that the data transfer takes place in one of the following modes:

#### SINGLE TRANSFER MODE

In single transfer mode, the NS32203 makes a single byte or word transfer for each  $\overline{\text{HOLD}}/\overline{\text{HLDA}}$  handshake sequence.

In this case the request signal from the I/O device is edge sensitive, that is, a single transfer is performed each time a

falling edge on  $\overline{\text{REQ}}$ n occurs. To perform multiple transfers, it is therefore necessary to temporarily deassert  $\overline{\text{REQ}}$ n after each transfer is initiated. If auto transfer mode is selected, the bus is released between two transfers for at least one clock cycle.

#### **BURST (DEMAND) TRANSFER MODE**

In burst transfer mode the DMAC will continue making data transfers until REQn goes inactive. Thus, the I/O device requesting service may suspend data transfer by bringing REQn inactive. Service may be resumed by asserting REQn again. If the auto transfer mode is selected, the DMAC will perform a single burst of data transfers until the end-transfer condition is reached.

Note 1: In either of the transfer modes described above, data transfers can only occur as long as the byte count is not zero or a search condition is not met. Whenever any of these conditions occur, the NS32203 terminates the current operation and releases the bus for at least one clock cycle.

Note 2: Whenever the DMAC releases HOLD, it waits for HLDA to go inactive for at least one clock cycle before reasserting HOLD again to continue the transfer operation.

#### 2.11 CHAINING

The NS32203 provides a chaining feature that allows the four DMAC channels to be regarded as two complementary pairs. Channels 0 and 1 form the first pair, while channels 2 and 3 form the second pair. Each pair is programmed independently by setting the corresponding bit in the configuration register. When two channels are complementary, only the even channel can perform transfer operations, while the odd one serves as temporary storage for the new control values and parameters loaded for the chaining operation. If an operation is being performed by the even channel of a pair and an end-condition is reached, the channel is not returned to the inactive state; rather, a new set of control values with or without parameters is loaded from the complementary channel and a new operation is started. During the reload operation the bus is released for at least two clock cycles. At the end of the second operation the channel returns to the inactive state, unless a new set of values has been loaded into the complementary channel by the CPU.

The chaining feature can be used to transfer blocks of data to/from non-contiguous memory segments. For example, the CPU can load channel 0 and 1 with control values and parameters for the first two blocks. After the operation for the first block is completed by channel 0, the control values and parameters stored in channel 1 are transferred to channel 0, during an update cycle, and a second operation is started. The CPU, being notified by an interrupt, can load channel 1 registers with control values and parameters for the third data block.

Note 1: Whenever a reload operation occurs, the register values of the complementary channel are affected. Thus, the CPU must always load a new set of values into the complementary channel if another chaining operation is required.

Note 2: When the chain option is selected, the CPU must be given the opportunity to acquire the bus for enough time between DMAC operations, in order for the complementary channel to be updated.

#### 2.12 CHANNEL PRIORITIES

The NS32203 has four I/O channels, each of which can be connected to an I/O device. Since no dependency exists between the different I/O devices, a priority level is assigned to each I/O channel, and a priority resolver is provided to resolve multiple requests activated simultaneously.

The priority resolver checks the priorities on every cycle. If a channel is being serviced and a higher priority request is received, the channel operation is suspended and control passes to the higher priority channel, unless the lock bit for the lower priority channel is set. If the lock bit is set, that channel operation is continued until completion before control passes to the higher priority channel. The bus is always released for at least two clock cycles when control passes from one channel to another.

Two types of priority encodings are available as software selectable options.

The first is fixed priority which fixes the channels in priority order based on the decreasing values of their numbers. Channel 3 has the lowest priority, while channel 0 has the highest.

The second option is variable priority. The last channel that receives service becomes the lowest priority channel among all other channels with variable priority, while the channels which previously had lower priority will get their priorities increased. If variable priority is selected for all four channels, any I/O device requesting service is guaranteed to be acknowledged after no more than three higher priority services have occurred. This prevents any channel from monopolizing the system. Priority types can be intermixed for different channels.

As an example, let channels 0, 2 and 3 have variable priority and channel 1 fixed priority. Channel 2 receives service first, followed by channel 0. The priority levels among all channels will change as follows.

#### Priority Initial Order Next Order Final Order

| High | 3 |       | ch.0 ACK → | ch.0 |        | ch.3           |

|------|---|-------|------------|------|--------|----------------|

|      | 2 |       | ch.1       | ch.1 | ch.1 → | fixed priority |

|      | 1 | ACK → | ch.2       | ch.3 |        | ch.2           |

| Low  | 0 |       | ch.3       | ch.2 |        | ch.0           |

Whenever the PT bit (priority type) in the command register is changed, the priority levels of all the channels are reset to the initial order. If only one channel has variable priority, then no change in priority will occur from the initial order.

Note: If the lock bit is not set, three idle states are inserted between the write cycle of a previous burst indirect transfer and the next read cycle.

## 3.0 Architectural Description

The NS32203 has 128 8-bit registers that can be addressed either individually or in pairs, using the 7 least significant bits of the address bus and the high byte enable signal HBE. Seventy-one of these registers are reserved, while the rest are accessible by the CPU for read/write operations. Figure 3-1 shows the NS32203 internal registers together with their address offsets. Detailed descriptions of these registers are given in the following sections.

#### 3.1 GLOBAL REGISTERS

The global registers consist of one configuration, one status and two interrupt vector registers. They are shared by all channels, and they control the overall operation of the NS32203.

### 3.1.1 CONF—Configuration Register

This register controls the hardware configuration of the NS32203 as well as the chaining feature.

## 3.0 Architectural Description (Continued)

The CONF register format is shown below:

7 6 5 4 3 2 1 0 XXXXXX C1 C0 CNF

CNF — Configuration Bit. Determines whether the NS32203 is in local or remote configuration.

$\mathsf{CNF} = 0 = > \mathsf{Local} \; \mathsf{Configuration}$

CNF = 1 = > Remote Configuration

C0 — Chaining bit for channels 0 and 1. Determines whether or not channel 0 and 1 are complementary. C0 = 0 = > Channels not complementary

C0 = 1 = > Channel 1 complementary to channel 0

C1 — Chaining bit for channels 2 and 3. Determines whether or not channels 2 and 3 are complementary.

C1 = 0 = > Channels not complementary

C1 = 1 = > Channel 3 complementary to channel 2

XXXXX — Reserved. These bits should be set to 0.

At reset, all CONF bits are reset to zero.

Note: The CNF bit should never be set by the software if the DMAC is wired for local configuration, otherwise bus conflicts will result.

|                     |              |                     |         | 101                 | ooai ooiniga allo | ii, ou loi wiso suc | s conflicts will result. |

|---------------------|--------------|---------------------|---------|---------------------|-------------------|---------------------|--------------------------|

| ſ                   | 23           | 16                  | 15      | 8                   | 7                 | 0                   |                          |

| annel 0             | COM(H)       | (02 <sub>16</sub> ) | COM(M)  | (01 <sub>16</sub> ) | COM(L)            | (00 <sub>16</sub> ) | Command                  |

| ntrol               |              |                     |         |                     | SRCH              | (04 <sub>16</sub> ) | Search Pattern           |

| gisters             |              |                     |         |                     | MSK               | (08 <sub>16</sub> ) | Search Mask              |

|                     | SRC(H)       | (0E <sub>16</sub> ) | SRC(M)  | (0D <sub>16</sub> ) | SRC(L)            | (0C <sub>16</sub> ) | Source Address           |

| annel 0 }           | DST(H)       | (12 <sub>16</sub> ) | DST(M)  | (11 <sub>16</sub> ) | DST(L)            | (10 <sub>16</sub> ) | Destination Addre        |

| gisters             | <del>-</del> |                     | LNGT(H) | (15 <sub>16</sub> ) | LNGT(L)           | (14 <sub>16</sub> ) | Block Length             |

|                     | COM(H)       | (22 <sub>16</sub> ) | COM(M)  | (21 <sub>16</sub> ) | COM(L)            | (20 <sub>16</sub> ) | Command                  |

| annel 1  <br>ntrol  | <u></u>      |                     |         |                     | SRCH              | (24 <sub>16</sub> ) | Search Pattern           |

| gisters             |              |                     |         |                     | MSK               | (28 <sub>16</sub> ) | Search Mask              |

|                     | SRC(H)       | (2E <sub>16</sub> ) | SRC(M)  | (2D <sub>16</sub> ) | SRC(L)            | (2C <sub>16</sub> ) | Source Address           |

| annel 1<br>rameter  | DST(H)       | (32 <sub>16</sub> ) | DST(M)  | (31 <sub>16</sub> ) | DST(L)            | (30 <sub>16</sub> ) | Destination Addre        |

| gisters             |              |                     | LNGT(H) | (35 <sub>16</sub> ) | LNGT(L)           | (34 <sub>16</sub> ) | Block Length             |

| [                   | COM(H)       | (42 <sub>16</sub> ) | COM(M)  | (41 <sub>16</sub> ) | COM(L)            | (40 <sub>16</sub> ) | Command                  |

| annel 2<br>ntrol    |              |                     |         |                     | SRCH              | (44 <sub>16</sub> ) | Search Pattern           |

| gisters             |              |                     |         |                     | MSK               | (48 <sub>16</sub> ) | Search Mask              |

| [                   | SRC(H)       | (4E <sub>16</sub> ) | SRC(M)  | (4D <sub>16</sub> ) | SRC(L)            | (4C <sub>16</sub> ) | Source Address           |

| annel 2<br>rameters | DST(H)       | (52 <sub>16</sub> ) | DSC(M)  | 51 <sub>16</sub> )  | DST(L)            | (50 <sub>16</sub> ) | Destination Addre        |

| egisters            |              |                     | LNGT(H) | (55 <sub>16</sub> ) | LNGT(L)           | (54 <sub>16</sub> ) | Block Length             |

|                     | COM(H)       | (62 <sub>16</sub> ) | COM(M)  | (61 <sub>16</sub> ) | COM(L)            | (60 <sub>16</sub> ) | Command                  |

| annel 3<br>Introl   |              |                     |         |                     | SRCH              | (64 <sub>16</sub> ) | Search Pattern           |

| gisters             |              |                     |         |                     | MSK               | (68 <sub>16</sub> ) | Search Mask              |

|                     | SRC(H)       | (6E <sub>16</sub> ) | SRC(M)  | (6D <sub>16</sub> ) | SRC(L)            | (6C <sub>16</sub> ) | Source Address           |

| annel 3<br>rameter  | DST(H)       | (72 <sub>16</sub> ) | DST(M)  | (71 <sub>16</sub> ) | DST(L)            | (70 <sub>16</sub> ) | Destination Addre        |

| egisters            |              |                     | LNGT(H) | (75 <sub>16</sub> ) | LNGT(L)           | (74 <sub>16</sub> ) | Block Length             |

| ſ                   |              |                     |         |                     | CONF              | (78 <sub>16</sub> ) | Configuration            |

| obal                |              |                     |         |                     | SVCT              | (5C <sub>16</sub> ) | Software Vector          |

| egisters            |              |                     |         |                     | HVCT              | (7C <sub>16</sub> ) | Hardware Vector          |

| Į                   |              |                     | STAT(H) | (7F <sub>16</sub> ) | STAT(L)           | (7E <sub>16</sub> ) | Status                   |

channel #0

## 3.0 Architectural Description (Continued)

#### 3.1.2 HVCT — Hardware Vector Register

This register contains the interrupt vector byte that is supplied to the CPU during an interrupt acknowledge (INTA) or return from interrupt (RETI) cycle. The HVCT register format is shown below.

| 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0 |

|---|---|------|---|---|---|---|---|

|   |   | BIAS |   |   | E | С | N |

- CN Channel number. Represents the number of the interrupting channel

- E Error code. Determines whether a normal operation completion or an error condition has occurred on the interrupting channel.

- E = 0 = > Normal Operation Completion

- E = 1 => A second interrupt was generated by the same channel before the first interrupt was serviced.

- BIAS Programmable bias. This field is programmed by writing the pattern BBBBB000 into the HVCT register.

The NS32203 always interprets a read of the HVCT register as either an interrupt acknowledge (INTA) cycle or a return from interrupt (RETI) cycle. Since these cycles cause internal changes to the DMAC, normal programs should never read the HVCT register (see next section). The DMAC distinguishes an INTA cycle from a RETI cycle by the state of an internal flip-flop, called Interrupt Service Flip-Flop, that toggles every time the HVCT register is read. This flip-flop is cleared on reset or when the HVCT register is written into. When an interrupt is acknowledged by the CPU, the  $\overline{\text{INT}}$  signal is deasserted unless another interrupt from a lower priority channel is pending. In this case the  $\overline{\text{INT}}$  signal is deasserted when the acknowledge cycle for the second interrupt is performed.

For this reason, if the INT signal is connected to an interrupt input of the NS32202 ICU, the triggering mode of that interrupt position should be 'low level'.

Furthermore, if that ICU interrupt input is programmed for cascaded operation and nesting of interrupts from other devices connected to the ICU is to be allowed, then the ICU interrupt input connected to the DMAC should be masked off during the interrupt service routine, before the CPU interrupt is reenabled. This is because the DMAC does not provide interrupt nesting capability.

An interrupt from a certain channel can be acknowledged only after the return from interrupt from a previously acknowledged interrupt is performed.

### 3.1.3 SVCT --- Software Vector Register

The SVCT register is an image of the HVCT register. It is a read-only register used for diagnostics. It allows the programmer to read the interrupt vector without affecting the interrupt logic of the NS32203. The format of the SVCT register is the same as that of the HVCT register.

#### 3.1.4 STAT — Status Register

The status register contains status information of the NS32203, and can be used when the interrupts are not enabled. Each set bit is automatically cleared when a read operation is performed. The format of this register is shown in the following figure.

| 15 14 |    |    |    |   | -  | _  |    | -  | -  | •  | _  | -  | •  | 0  |

|-------|----|----|----|---|----|----|----|----|----|----|----|----|----|----|

| ME CH | MN | тс | ME | 퓮 | MN | TC | ME | СН | MN | TC | ME | СН | MN | тс |

channel #3 channel #2 channel #1

The status of each channel is defined in a four-bit field as described below:

TC — Transfer Complete.

Indicates the completion of a channel operation, regardless of the state of the length register or whether a match/no match condition occurred.

MN - Match/No Match Bit.

This bit is set when a match/no match condition occurs.

CH - Channel Halted.

Set when a channel operation is halted by pulling the  $\overline{\text{RST}}/\overline{\text{HLT}}$  pin.

ME — Multiple events. This bit is set when more than one of the above conditions have occurred.

Note: If an interrupt is enabled, the corresponding bit in the status register is not cleared upon read, unless the interrupt is acknowledged.

#### **3.2 CONTROL REGISTERS**

Each of the four channels has three control registers, consisting of a 24-bit command register, an 8-bit search register and an 8-bit mask register.

#### 3.2.1 COM -- Command Register

The command register controls the operation of the associated channel. It is divided into three separately addressable parts: COM(L), COM(M) and COM(H). The format of each part and bit functions are shown below.

COM(L) — Command Register (Low-Byte)

| 7  | 6  | 5  | 4  | 3   | 2  | 1 | 0 |

|----|----|----|----|-----|----|---|---|

| ΑT | LK | PT | UW | INC | DI | С | С |

CC - Command Code

CC = 00 = > Channel Disabled.

CC = 01 = > Search

CC = 10 = > Data Transfer

CC = 11 ≈ > Data Transfer and Search

DI — Direct/Indirect Transfers

DI = 0 = > Indirect Transfers

DI = 1 = > Direct Transfers

INC - Inclusive/Exclusive Search

INC =0 => Exclusive Search

INC =1 => Inclusive Search

UW — Search type

UW =0 =>Search UNTIL

UW =1 =>Search WHILE

PT -- Priority type

PT = 0 = > Fixed

PT = 1 = > Variable

LK - Priority lock

LK =0 => Priority Unlocked

LK = 1 = > Priority Locked

### 3.0 Architectural Description (Continued)

AT -- Auto transfer

AT = 0 = > Auto Transfer Disabled

AT = 1 = > Auto Transfer Enabled

At Reset, the CC bits in COM(L) are cleared, disabling the channel.

Note: The CC bits can be cleared by software during an indirect data transfer to stop the transfer. This, however, should not be done during direct data transfers. See section 3.3.3.

COM(M) - Command Register (Middle-Byte)

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| DD | DW | DL | DT | SD | SW | SL | ST |

ST --- Source Type

ST = 0 = > I/O Device

ST = 1 = > Memory

SL - Source Location

(Effective only in the remote configuration)

SL = 0 = > Local

SL = 1 = > Remote

SW - Source Width

SW = 0 = > 8 Bits

SW = 1 = > 16 Bits

SD - Source Direction

SD = 0 = > Up

SD = 1 = > Down

DT — Destination Type

DT =0 => I/O Device

SD =1 => Memory

DL - Destination Location

(Effective only in the remote configuration)

DL =0 =>Local

DL =1 =>Remote

DW - Destination Width

DW = 0 = > 8 Bits

DW = 1 = > 16 Bits

DD - Destination Direction.

DD = 0 = > Up

DD = 1 = > Down

COM(H) - Command Register (High-Byte)

| 7   | 6   | 5   | 4  | <u>`3</u> | 2   | 1  | 0 |  |

|-----|-----|-----|----|-----------|-----|----|---|--|

| HLI | MNI | TCI | ΑN | ΙN        | ATC | DM | х |  |

X - Reserved. (Should be set to 0)

TM -- Transfer Mode

DM = 0 = > Single Transfer

DM = 1 = > Burst Transfer

ATC - Action after Transfer Complete

ATC = 0 = > Disable Channel

ATC = 1 = > Load Control Values and Parameters from Complementary Channel and Continue

AMN - Action after Match/No Match

AMN = 00 = > Disable Channel

AMN = 01 = > Continue

AMN = 10 = > Load Control Values from Complementary Channel and Continue

AMN = 11 = > Load Control Values and Parameters from Complementary Channel and Continue

TCI - Interrupt Mask on "Transfer Complete"

TCI = 0 = > No Interrupt

TCI = 1 = > Interrupt

MNI - Interrupt Mask on "Match/No Match"

MNI = 0 = > No Interrupt

MNi = 1 = > Interrupt

HLI - Interrupt Mask on "Channel Halted"

HLI =0 => No Interrupt

HLI = 1 = > Interrupt

#### 3.2.2 SRCH - Search Register

This 8-bit register holds the value to be compared with the data transferred during the channel operation.

#### 3.2.3 MSK - Mask Register

The 8-bit mask register determines which bits of the transferred data are compared with corresponding search register bits. If a mask register bit is set to 0, the corresponding search register bit is ignored in the compare operation. At reset, all the MSK bits are set to 0.

#### 3.3 PARAMETER REGISTERS

Each channel has three parameter registers, consisting of a 24-bit source address register, a 24-bit destination address register and a 16-bit block length register.

#### 3.3.1 SRC — Source Address Register

The source address register points to the physical address of the data source. When the data source is an I/O device, the register does not change during the transfer operation. When the data source is memory, the register is incremented or decremented by either one or two after each transfer.

#### 3.3.2 DST - Destination Address Register

The destination address register points to the physical address of the data destination. When the data destination is an I/O device, the register does not change during the transfer operation. When the data destination is memory, the register is incremented or decremented by either one or two after each transfer.

#### 3.3.3 LNGT - Block Length Register

The block length register holds the number of bytes in the block to be transferred. It is decremented by either one or two after each transfer.

Note: A direct data transfer can be stopped by writing zeroes into the LNGT register. The number of bytes transferred can be determined in this case, from the value of either the SRC or the DST register.

## 4.0 Device Specifications

#### 4.1. NS32203 PIN DESCRIPTIONS

The following is a brief description of all NS32203 pins. The descriptions reference portions of the Functional Description, Section 2.0.

## **Connection Diagram**

TL/EE/8701-12

Top View

### FIGURE 4-1. NS32203 Dual-In-Line Package

Order Number NS32203D or NS32203N See NS Package Number D48A or N48A

#### 4.1.1 SUPPLIES

Power (V<sub>cc</sub>): +5V positive supply.

Ground (GND): Ground reference for on-chip logic.

#### 4.1.2 INPUT SIGNALS

Reset/Halt (RST/HLT): Active low. If held active for 1 or 2 clock cycles and released, this signal halts the DMAC operation on the active channel. If held longer, it resets the DMAC. Section 2.1.

Chip Select (CS): When low, the device is selected, enabling CPU access to the DMAC internal registers.

Ready (RDY): Active high. When inactive, the DMA Controller extends the current bus cycle for synchronization with slow memory or peripherals. Upon detecting RDY active, the DMAC terminates the bus cycle.

Channel Request 0-3 (REQ0 - REQ3): Active low. These lines are used by peripheral devices to request DMAC service.

Bus Request (BREQ): Used only in the remote configuration. This signal, when asserted, forces the DMAC to stop transferring data and to release the bus. It must be activated by the CPU before any CPU access to the remote bus is performed. In the local configuration this signal should be connected to  $V_{CC}$  via a 4.7k resistor. Section 2.4.

Hold Acknowledge (HLDA): Active low. When asserted, indicates that control of the system bus has been relinquished by the current bus master and the DMAC can take control of the bus.

Clock (CLK): Clock signal supplied by the CTTL output of the NS32201 TCU.

#### 4.1.3 OUTPUT SIGNALS

Address Bits 16-23 (A16-A23): Most significant 8 bits of the address bus.

**Hold Request (HOLD):** Active low. Used by the DMAC to request control of the system bus.

Channel Acknowledge 0-3 (ACKO - ACK3): These lines indicate that a channel is active. When a channel's request is honored, the corresponding acknowledge line is activated to notify the peripheral device that it has been selected for a transfer cycle. Section 2.2.2.

**Bus Grant (BGRT):** Used only in the remote configuration. This signal is used by the DMAC to inform the CPU that the remote bus has been relinquished by the DMAC and can be accessed by the CPU. Section 2.4.

I/O Read (IORD): Active low. Enables data to be read from a peripheral device. Section 2.2.2.

I/O Write (IOWR): Active low. Enables data to be written to a peripheral device. Section 2.2.2.

Interrupt (INT): Active low. Used to generate an interrupt request when a programmed condition has occurred. Section 2.9.

#### 4.1.4 INPUT/OUTPUT SIGNALS

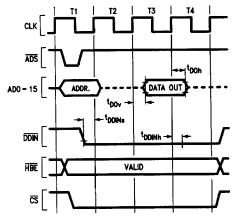

Address/Data 0-15 (AD0-AD15): Multiplexed Address/ Data bus lines. Also used by the CPU to access the DMAC internal registers.

High Byte Enable (HBE): Active low. Enables data transfers on the most significant byte of the data bus.

Address Strobe (ADS): Active low. Controls address latches and indicates the start of a bus cycle.

**Data Direction in (DDIN):** Active low. Status signal indicating the direction of data flow in the current bus cycle.

#### **4.2 ABSOLUTE MAXIMUM RATINGS**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Temperature Under Bias

0°C to +70°C

Storage Temperature

-65°C to +150°C

All Input or Output Voltages with Respect to GND

-0.5V to +7V

Power Dissipation

1.1 Watt

## 4.3 ELECTRICAL CHARACTERISTICS T<sub>A</sub> = 0 to $+70^{\circ}$ C, $V_{CC} = 5V \pm 5\%$ , GND = 0V

| Symbol          | Parameter                                                   | Conditions                                  | Min  | Тур | Max                   | Units |

|-----------------|-------------------------------------------------------------|---------------------------------------------|------|-----|-----------------------|-------|

| V <sub>IH</sub> | High Level Input Voltage                                    |                                             | 2.0  |     | V <sub>CC</sub> + 0.5 | ٧     |

| VIL             | Low Level input Voltage                                     |                                             | -0.5 |     | 0.8                   | V     |

| V <sub>OH</sub> | High Level Output Voltage                                   | $I_{OH} = -400 \mu\text{A}$                 | 2.4  |     |                       | ٧     |

| V <sub>OL</sub> | Low Level Output Voltage                                    | I <sub>OL</sub> = 2 mA                      |      |     | 0.45                  | ٧     |

| կ               | Input Load Current                                          | 0 < V <sub>IN</sub> ≤ V <sub>CC</sub>       | -20  |     | 20                    | μА    |

| IL              | Leakage Current Output and I/O Pins in TRI-STATE/Input Mode | $0.4 \le V_{IN} \le V_{CC}$                 | -20  |     | 20                    | μΑ    |

| lcc             | Active Supply Current                                       | I <sub>OUT</sub> = 0, T <sub>A</sub> = 25°C |      | 180 | 300                   | mA    |

#### 4.4 SWITCHING CHARACTERISTICS

### 4.4.1 Definitions

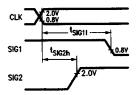

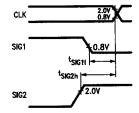

All the timing specifications given in this section refer to 0.8V and 2.0V on all the input and output signals as illustrated in *Figures 4-2* and *4-3*, unless specifically stated otherwise.

TL/EE/8701-13

FIGURE 4-2. Timing Specification Standard (Signal Valid after Clock Edge)

#### ABBREVIATIONS:

L.E. - leading edge R.I

R.E. — rising edge

Note: Absolute maximum ratings indicate limits beyond

which permanent damage may occur. Continuous operation at these limits is not intended; operation should be limited to

those conditions specified under Electrical Characteristics.

T.E. — trailing edge F.E. — falling edge

FIGURE 4-3. Timing Specification Standard (Signal Valid before Clock Edge)

### 4.4.2 Timing Tables

# 4.4.2.1 Output Signals: Internal Propagation Delays, NS32203-10 Maximum Times Assume Capacitive Loading of 100 pF.

| Name                | Figure          | Description                            | Reference/                  | NS32 | 203-10 | Unit |

|---------------------|-----------------|----------------------------------------|-----------------------------|------|--------|------|

|                     |                 | •                                      | Conditions                  | Min  | Max    | 0    |

| t <sub>ALv</sub>    | 4-7             | Address Bits 0-15 Valid                | After R.E., CLK T1          |      | 50     | ns   |

| <sup>t</sup> ALh    | 4-9             | Address Bits 0-15<br>Hold Time         | After R.E., CLK T2          | 5    |        | ns   |

| t <sub>AHv</sub>    | 4-7             | Address Bits 16-23 Valid               | After R.E., CLK T1          |      | 50     | ns   |

| t <sub>AHh</sub>    | 4-7             | Address Bits 16-23 Hold                | After R.E., CLK T1<br>or Ti | 5    |        | ns   |

| t <sub>ALADSs</sub> | 4-8             | Address Bits 0-15 Set Up               | Before ADS T.E.             | 25   |        | ns   |

| <sup>†</sup> AHADSs | 4-8             | Address Bits 16-23 Set Up              | Before ADS T.E.             | 25   |        | ns   |

| <sup>t</sup> ALADSh | 4-9             | Address Bits 0-15<br>Hold Time         | After ADS T.E.              | 15   |        | μs   |

| <sup>t</sup> ALf    | 4-8             | Address Bits 0-15 Floating             | After R.E., CLK T2          |      | 25     | ns   |

| t <sub>Dv</sub>     | 4-7             | Data Valid (Write Cycle)               | After R.E., CLK T2          |      | 50     | ns   |

| t <sub>Dh</sub>     | 4-7             | Data Hold (Write Cycle)                | After R.E., CLK T1<br>or Ti | 0    |        | ns   |

| <sup>t</sup> DOv    | 4-5             | Data Valid (Reading<br>DMAC Registers) | After R.E., CLK T3          |      | 50     |      |

| <sup>t</sup> DOh    | 4-5             | Data Hold (Reading<br>DMAC Registers)  | After R.E., CLK T4          | 10   |        |      |

| t <sub>HBEv</sub>   | 4-7             | HBE Signal Valid                       | After R.E., CLK T1          |      | 50     | ns   |

| <sup>t</sup> HBEh   | 4-7             | HBE Signal Hold                        | After R.E., CLK T1<br>or Ti | 0    |        | ns   |

| t <sub>DDINV</sub>  | 4-8             | DDIN Signal Valid                      | After R.E., CLK T1          |      | 65     | ns   |

| <sup>†</sup> DDINh  | 4-8             | DDIN Signal Hold                       | After R.E., CLK T1 or Ti    | 0    |        | ns   |

| ADSa                | 4-7             | ADS Signal Active                      | After R.E., CLK T1          |      | 35     | ns   |

| t <sub>ADSia</sub>  | 4-7             | ADS Signal Inactive                    | After R.E., CLK T1          |      | 40     | ns   |

| <sup>t</sup> ADSw   | 4-7             | ADS Pulse Width                        | at 0.8V<br>(Both Edges)     | 30   |        | ns   |

| t <sub>ALz</sub>    | 4-12. 4-13      | AD0-AD15 Floating                      | After R.E., CLK Ti          |      | 55     | ns   |

| AHz                 | 4-12, 4-13      | A16-A23 Floating                       | After R.E., CLK Ti          |      | 55     | ns   |

| t <sub>ADSz</sub>   | 4-12, 4-13      | ADS Floating                           | After R.E., CLK Ti          |      | 55     | ns   |

| HBEz                | 4-12, 4-13      | HBE Floating                           | After R.E., CLK Ti          |      | 55     | ns   |

| t <sub>DDINz</sub>  | 4-12, 4-13      | DDIN Floating                          | After R.E., CLK Ti          |      | 55     | ns   |

| tHLDa               | 4-11            | HOLD Signal Active                     | After R.E., CLK Ti          |      | 50     | ns   |

| HLDia               | 4-12            | HOLD Signal Inactive                   | After R.E., CLK Ti<br>or T4 |      | 50     | ns   |

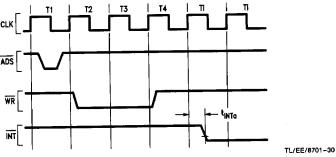

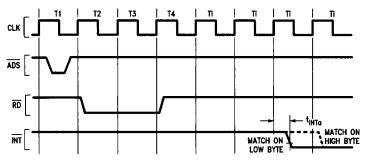

| tinta               | 4-19, 4-21      | INT Signal Active                      | After R.E., CLK Ti          |      | 40     | ns   |

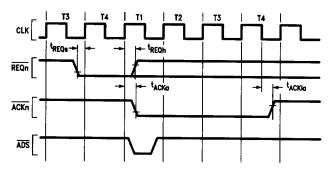

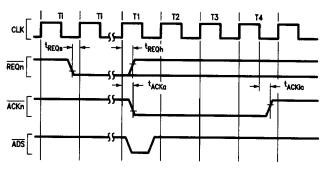

| ACKa                | 4-16, 4-17, 4-7 | ACKn Signal Active                     | After R.E., CLK T1          |      | 50     | ns   |

| t<br>ACKia          | 4-16, 4-17, 4-7 | ACKn Signal Inactive                   | After F.E., CLK T4          |      | 35     | ns   |

| Name                 | Figure           | Description                                       | Reference/                             | NS32: | Units |     |

|----------------------|------------------|---------------------------------------------------|----------------------------------------|-------|-------|-----|

| Name                 | i igui e         | 2000/ipii0ii                                      | Conditions                             | Min   | Max   |     |

| t <sub>BGRTa</sub>   | 4-13             | BGRT Signal Active                                | After R.E., CLK                        |       | 65    | ns  |

| t <sub>BGRTia</sub>  | 4-14             | BGRT Signal Inactive                              | After R.E., CLK                        |       | 65    | ns  |

| t <sub>IORDa</sub>   | 4-8, 4-9         | IORD Active                                       | After R.E., CLK T2                     |       | 40    | ns  |

| tiORDia              | 4-8              | IORD Inactive (During<br>Indirect Transfers)      | After R.E., CLK T4                     |       | 40    | ns  |

| <sup>t</sup> IORDia  | 4-9              | IORD Inactive (During<br>Direct Transfers)        | After F.E., CLK T4                     |       | 40    | ns  |

| †IOWRa               | 4-7, 4-10        | IOWR Active                                       | After R.E., CLK T2                     |       | 40    | ns  |

| <sup>t</sup> IOWRia  | 4-7              | IOWR Inactive (During Indirect Transfers)         | After R.E., CLK T4                     |       | 40    | ns  |

| <sup>†</sup> IOWRdia | 4-10             | IOWR Inactive (During<br>Direct Transfers)        | After F.E., CLK T3                     |       | 40    | ns  |

| 4.4.2.2 Inpu         | t Signal Require | ements: NS32203-10                                |                                        |       |       |     |

| t <sub>PWR</sub>     | 4-22             | Power Stable to RST/HLT R.E.                      | After V <sub>CC</sub> Reaches<br>4.75V | 50    |       | μs  |

| t <sub>RSTw</sub>    | 4-23             | RST/HLT Pulse Width (Resetting the DMAC)          | at 0.8V (Both Edges)                   | 64    |       | tCp |

| <sup>t</sup> RSTs    | 4-24             | RST/HLT Set Up Time<br>(Resetting the DMAC)       | Before F.E., CLK                       | 15    |       | ns  |

| <sup>†</sup> HLTs    | 4-18             | RST/HLT Setup Time<br>(Halting a DMAC Transfer)   | Before R.E., CLK T3                    | 25    |       | ns  |

| <sup>t</sup> HLTh    | 4-19             | RST/HLT Hold Time<br>(Halting a DMAC Transfer)    | After R.E., CLK T4                     | 10    |       | ns  |

| t <sub>DIs</sub>     | 4-6              | Data in Setup Time                                | Before R.E., CLK T3                    | 15    |       | ns  |

| t <sub>Dlh</sub>     | 4-6              | Data in Hold                                      | After R.E., CLK T4                     | 3     |       | ns  |

| t <sub>DIs</sub>     | 4-6              | Data in Setup Time<br>(Writing to DMAC Registers) | After R.E., CLK T3                     | 15    | 15    |     |

| <sup>t</sup> Dih     | 4-6              | Data in Hold<br>(Writing to DMAC Registers)       | After R.E., CLK T4                     | 3     |       | ns  |

| tHLDAs               | 4-11, 4-12       | HOLDA Setup Time                                  | Before R.E., CLK                       | 25    |       | ns  |

| tHLDAh               | 4-11             | HLDA Hold Time                                    | After R.E., CLK                        | 10    |       | ns  |

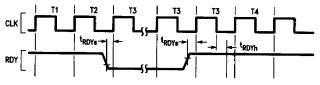

| tRDYs                | 4-15             | RDY Setup Time                                    | Before R.E.,<br>CLK T2 or T3           | 20    |       | ns  |

| t <sub>RDYh</sub>    | 4-15             | RDY Hold Time                                     | After R.E., CLK T3                     | 5     |       | ns  |

| tREQs                | 4-16, 4-17       | REQn Setup Time                                   | Before R.E., CLK                       | 50    |       | ns  |

| t <sub>REQh</sub>    | 4-16, 4-17       | REQn Hold Time                                    | After R.E., CLK                        | 10    |       |     |

| t <sub>BREQs</sub>   | 4-13             | BREQ Setup Time                                   | Before R.E., CLK                       | 25    |       | ns  |

| Name                 | Figure | Description            | Reference/<br>Conditions | NS32203-10 |     | Units |

|----------------------|--------|------------------------|--------------------------|------------|-----|-------|

|                      |        |                        |                          | Min        | Max | Onits |

| t <sub>BREQh</sub>   | 4-13   | BREQ Hold Time         | After R.E., CLK          | 10         |     | ns    |

| t <sub>ALADSis</sub> | 4-6    | Address Bits 0-5 Setup | Before ADS T.E.          | 20         |     | ns    |

| <sup>t</sup> ALADSih | 4-6    | Address Bits 0-5 Hold  | After ADS T.E.           | 20         |     | ns    |

| t <sub>HBEs</sub>    | 4-6    | HBE Setup Time         | Before R.E., CLK T1      | 10         |     | ns    |

| <sup>t</sup> HBEih   | 4-6    | HBE Hold Time          | After R.E., CLK T4       | 40         |     | ns    |

| t <sub>ADSs</sub>    | 4-6    | ADS L.E. Setup Time    | Before R.E., CLK T1      | 40         |     | ns    |

| t <sub>ADSiw</sub>   | 4-6    | ADS Pulse Width        | ADS L.E. to ADS T.E.     | 35         |     | ns    |

| t <sub>CSs</sub>     | 4-6    | CS Setup Time          | Before R.E., CLK T1      | 15         |     | ns    |

| t <sub>CSh</sub>     | 4-6    | CS Hold Time           | After R.E., CLK T4       | 40         |     | ns    |

| <sup>t</sup> DDINs   | 4-6    | DDIN Setup Time        | Before R.E., CLK T2      | 30         |     | ns    |

| t <sub>DDINh</sub>   | 4-6    | DDIN Hold Time         | After R.E., CLK T4       | 40         |     | ns    |

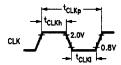

### 4.4.2.3 Clocking Requirements: NS32203-10

| Name              | Figure | Description     | Reference/<br>Conditions      | NS32203-10 |     | Units |

|-------------------|--------|-----------------|-------------------------------|------------|-----|-------|

|                   |        |                 |                               | Min        | Max | Cints |

| <sup>t</sup> CLKh | 4-4    | Clock High Time | At 2.0V (Both Edges)          | 42         |     | ns    |

| t <sub>CLK1</sub> | 4-4    | Clock Low Time  | At 0.8V (Both Edges)          | 42         |     | ns    |

| t <sub>CLKp</sub> | 4-4    | Clock Period    | R.E., CLK to Next<br>R.E. CLK | 100        |     | ns    |

### 4.4.3 Timing Diagrams

TL/EE/8701-17

FIGURE 4-4. Clock Timing

FIGURE 4-5. Read from DMAC Registers

TL/EE/8701-16

FIGURE 4-6. Write to DMAC Registers

FIGURE 4-7. Indirect Write Cycle

TL/EE/8701-18

TL/EE/8701-19

FIGURE 4-9. Direct I/O to Memory Transfer

FIGURE 4-10. Direct Memory to I/O Transfer

TL/EE/8701-21

FIGURE 4-11. HOLD/HOLDA Sequence Start

FIGURE 4-12. HOLD/HOLDA Sequence End

Note 1: DMAC in local configuration.

Note 2: The HOLD/HOLDA sequence shown above is related to the single transfer mode. In burst transfer mode HOLD is deactivated two cycles later.

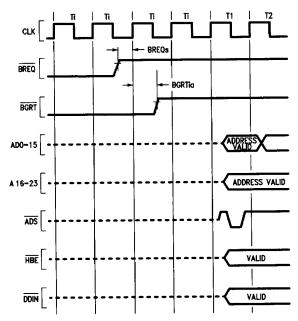

FIGURE 4-13. Bus Request/Grant Sequence Start

TL/EE/8701-24

TL/EE/8701-25

FIGURE 4-14. Bus Request/Grant Sequence End

Note 1: DMAC in remote configuration.

Note 2: If BREQ is asserted in the middle of a DMAC transfer, the transfer will always be completed.

FIGURE 4-15. Ready Sampling

TL/EE/8701-26

FIGURE 4-16. REQn/ACKn Sequence (DMAC Initially Not Idle)

TL/EE/8701-27

FIGURE 4-17. REQn/ACKn Sequence (DMAC Initially Idle)

Note 1: Halt may occur in previous T-States. It must be applied for 1 or 2 clock cycles.

Note 2: If BREQ is asserted in the middle of a DMAC transfer, the transfer will always be completed.

FIGURE 4-20. Interrupt on Match/No Match

TL/EE/8701-31

Note: If inclusive search is specified a write cycle is performed before  $\overline{\text{INT}}$  is activated.

FIGURE 4-21. Interrupt on Halt

FIGURE 4-22. Power on Reset

FIGURE 4-23. Non Power on Reset