**PRELIMINARY**

# NS32C201-10/NS32C201-15 Timing Control Units

# **General Description**

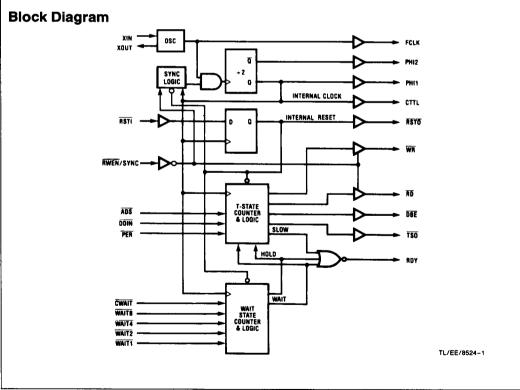

The NS32C201 Timing Control Unit (TCU) is a 24-pin device fabricated using National's microCMOS technology. It provides a two-phase clock, system control logic and cycle extension logic for the Series 32000® microprocessor family. The TCU input clock can be provided by either a crystal or an external clock signal whose frequency is twice the system clock frequency.

In addition to the two-phase clock for the CPU and MMU (PHI1 and PHI2), it also provides two system clocks for general use within the system (FCLK and CTTL). FCLK is a fast clock whose frequency is the same as the input clock, while CTTL is a replica of PHI1 clock.

The system control logic and cycle extension logic make the TCU very attractive by providing extremely accurate bus control signals, and allowing extensive control over the bus cycle timing.

### **Features**

- Oscillator at twice the CPU clock frequency

- 2 phase full V<sub>CC</sub> swing clock drivers (PHI1 and PHI2)

- 4-bit input (WAITn) allowing precise specification of 0 to 15 wait states

- Cycle Hold for system arbitration and/or memory refresh

- System timing (FCLK, CTTL) and control (RD, WR, and DBE) outputs

- General purpose Timing State Output (TSO) that identifies internal states

- Peripheral cycle to accommodate slower MOS peripherals

- Provides "ready" (RDY) output for the Series 32000 CPUs

- Synchronous system reset generation from Schmitt trigger input

- Phase synchronization to a reference signal

- High-speed CMOS technology

- TTL compatible inputs

- Single 5V power supply

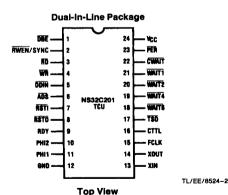

- 24-pin dual-in-line package

1.0

1.8 Bus Cycle Extension Combinations

1.9 Overriding WAIT Wait States

## **Table of Contents**

| FUNCTIONAL DESCRIPTION                | 2.0 DEVICE SPECIFICATIONS      |  |  |  |

|---------------------------------------|--------------------------------|--|--|--|

| .1 Power and Grounding                | 2.1 Pin Descriptions           |  |  |  |

| .2 Crystal Oscillator Characteristics | 2.1.1 Supplies                 |  |  |  |

| .3 Clocks                             | 2.1.2 Input Signals            |  |  |  |

| .4 Resetting                          | 2.1.3 Output Signals           |  |  |  |

| .5 Synchronizing Two or More TCUs     | 2.2 Absolute Maximum Ratings   |  |  |  |

| .6 Bus Cycles                         | 2.3 Electrical Characteristics |  |  |  |

| .7 Bus Cycle Extension                | 2.4 Switching Characteristics  |  |  |  |

| 1.7.1 Normal Wait States              | 2.4.1 Definitions              |  |  |  |

| 1.7.2 Peripheral Cycle                | 2.4.2 Output Loading           |  |  |  |

| 1.7.3 Cycle Hold                      | 2.4.3 Timing Tables            |  |  |  |

# **List of Illustrations**

2.4.4 Timing Diagrams

| Crystal Connection                                        | J |

|-----------------------------------------------------------|---|

| PHI1 and PHI2 Clock Signals                               | 2 |

| Recommended Reset Connections (Non Memory-Managed System) | ì |

| Recommended Reset Connections (Memory-Managed System)     | ) |

| Slave TCU does not use RWEN during Normal Operation       | ı |

| Slave TCU Uses Both SYNC and RWEN                         | , |

| Synchronizing Two TCUs                                    | 5 |

| Synchronizing One TCU to an External Pulse                | j |

| Basic TCU Cycle (Fast Cycle)                              | , |

| Wait State Insertion Using CWAIT (Fast Cycle)             | J |

| Wait State Insertion Using WAITn (Fast Cycle)             | , |

| Peripheral Cycle                                          | ) |

| Cycle Hold Timing Diagram                                 |   |

| Fast Cycle with 12 Wait States                            | 2 |

| Peripheral Cycle with Six Wait States                     | j |

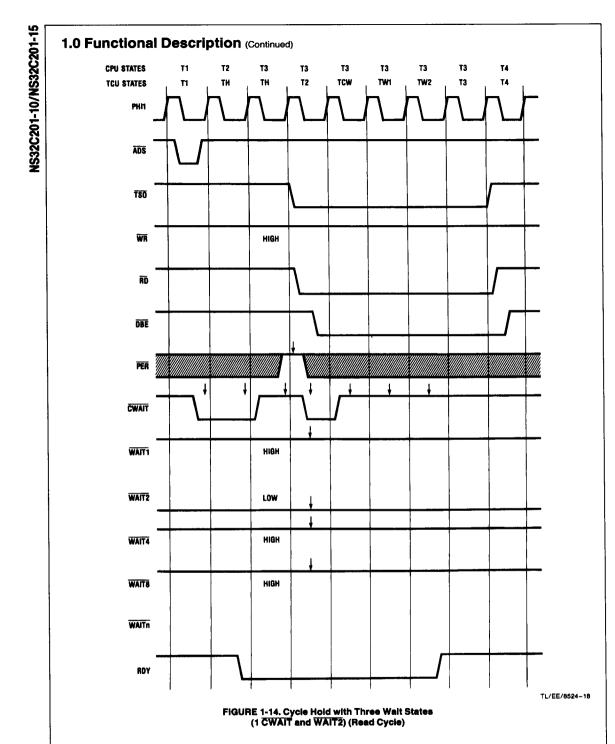

| Cycle Hold with Three Wait States                         | ļ |

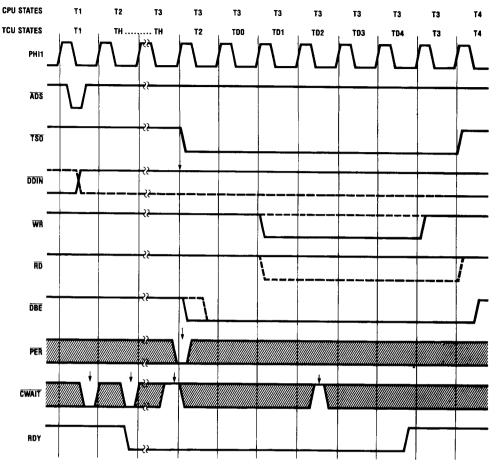

| Cycle Hold of a Peripheral Cycle                          | j |

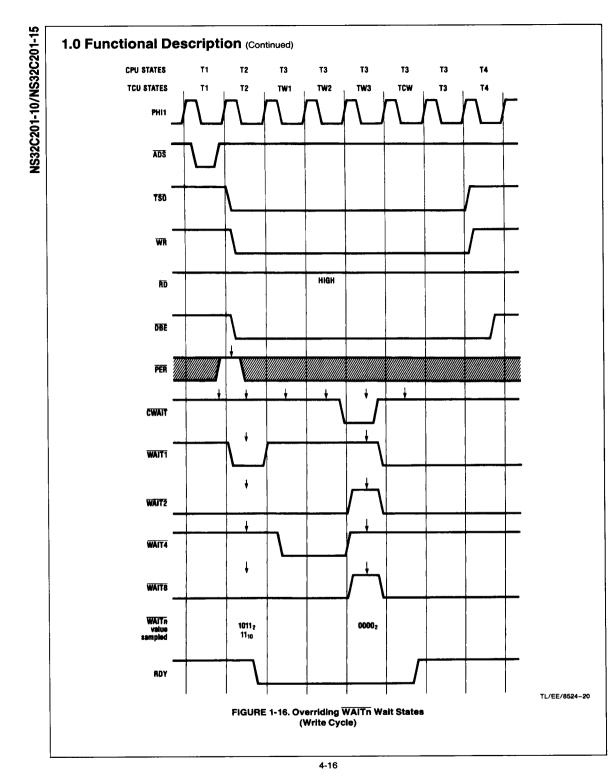

| Overriding WAITn Wait States                              | j |

| Connection Diagram                                        |   |

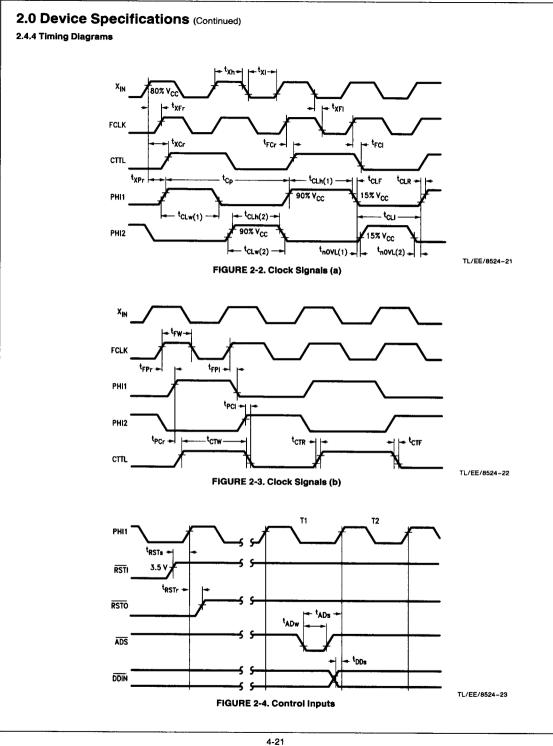

| Clock Signals (a)         2-2                             | 2 |

| Clock Signals (b) 2-3                                     | 3 |

| Control Inputs                                            | ţ |

| Control Outputs (Fast Cycle)                              | j |

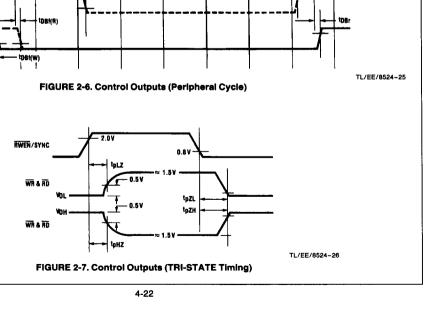

| Control Outputs (Peripheral Cycle)                        | ì |

| Control Outputs (TRI-STATE Timing)                        | , |

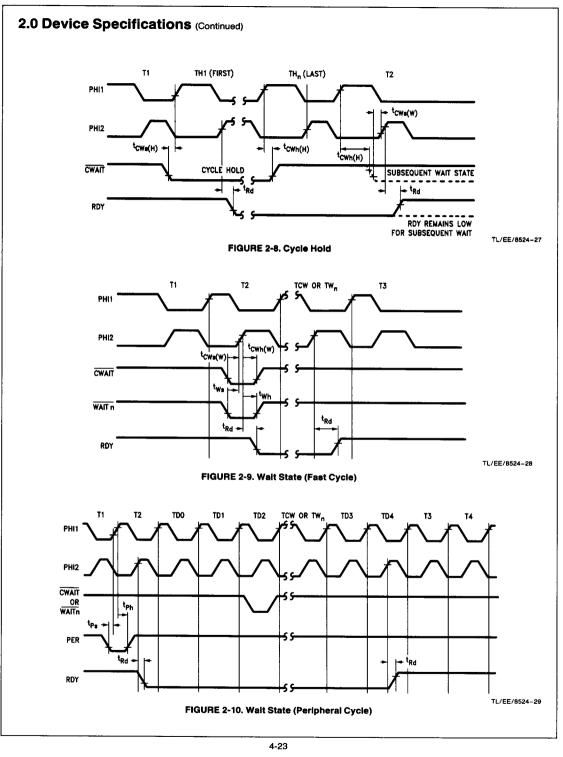

| Cycle Hold                                                | 3 |

| Wait States (Fast Cycle)                                  | ) |

| Wait States (Peripheral Cycle)                            | ) |

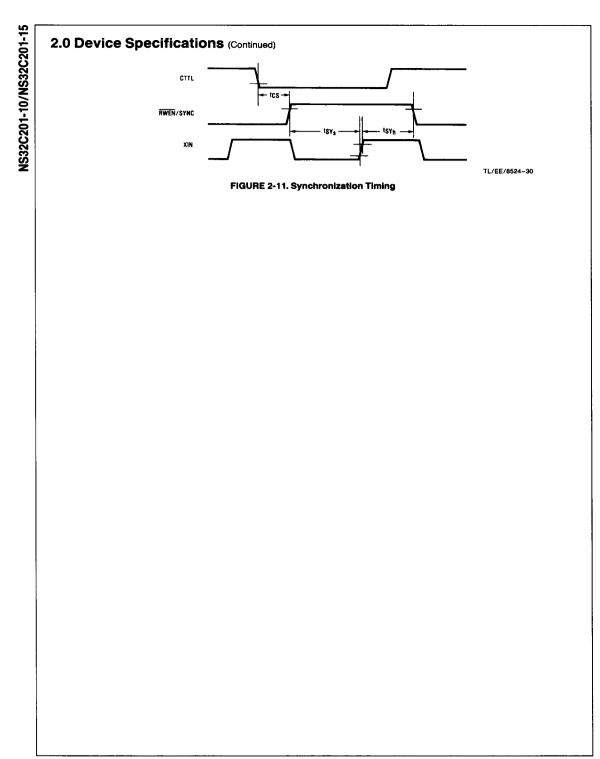

| Synchronization Timing 2.11                               |   |

## 1.0 Functional Description

#### 1.1 POWER AND GROUNDING

The NS32C201 requires a single +5V power supply, applied to pin 24 ( $V_{CC}$ ). See Electrical Characteristics. The Logic Ground on pin 12 (GND), is the common pin for the TCU.

A 0.1  $\mu F$ , ceramic decoupling capacitor must be connected across  $V_{CC}$  and GND, as close to the TCU as possible.

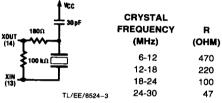

## 1.2 CRYSTAL OSCILLATOR CHARACTERISTICS

The NS32C201 has an internal oscillator that requires connections of the crystal and bias components to XIN and XOUT as shown in *Figure 1-1*. It is important that the crystal and the RC components be mounted in close proximity to the XIN, XOUT and  $V_{\rm CC}$  pins to keep printed circuit trace lengths to an absolute minimum.

### **Typical Crystal Specifications:**

| Туре                       |                        |

|----------------------------|------------------------|

| Tolerance                  |                        |

| Stability                  | 0.01% from 0° to 70°C  |

| Resonance                  | Fundamental (parallel) |

| Capacitance                | 20 pF                  |

| Maximum Series Resistance. | 50Ω                    |

FIGURE 1-1. Crystal Connection Diagram

#### 1.3 CLOCKS

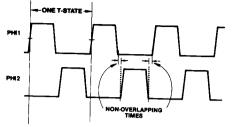

The NS32C201 TCU has four clock output pins. The PHI1 and PHI2 clocks are required by the Series 32000 CPUs. These clocks are non-overlapping as shown in Figure 1-2.

TL/EE/8524~4

### FIGURE 1.2. PHI1 and PHI2 Clock Signals

Each rising edge of PHI1 defines a transition in the timing state of the CPU.

As the TCU generates the various clock signals with very short transition timings, it is recommended that the conductors carrying PHI1 and PHI2 be kept as short as possible. It is also recommended that only the Series 32000 CPU and, if used, the MMU (Memory Management Unit) be connected to the PHI1 and PHI2 clocks.

CTTL is a clock signal which runs at the same frequency as PHI1 and is closely balanced with it.

FCLK is a clock, running at the frequency of XIN input. This clock has a frequency that is twice the CTTL clock frequency. The exact phase relationship between PHI1, PHI2, CTTL and FLCK can be found in Section 2.

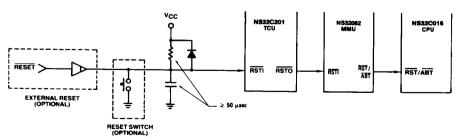

FIGURE 1-3a. Recommended Reset Connections (Non Memory-Managed System)

TL/EE/8524-5

FIGURE 1-3b. Recommended Reset Connections (Memory-Managed System)

TL/EE/8524-6

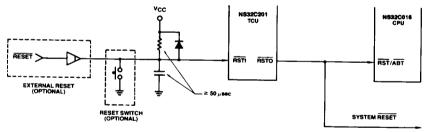

#### 1.4 RESETTING

The NS32C201 TCU provides circuitry to meet the reset requirements of the Series 32000 CPUs. If the Reset Input line, RSTI is pulled low, the TCU asserts RSTO which resets the Series 32000 CPU. This Reset Output may also be used as a system reset signal. Figure 1-3a illustrates the reset connections for a non Memory-Managed system. Figure 1-3b illustrates the reset connections for a Memory-Managed system.

### 1.5 SYNCHRONIZING TWO OR MORE TCUs

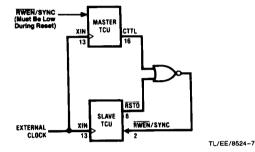

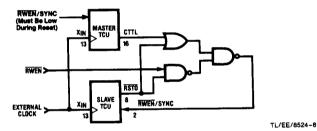

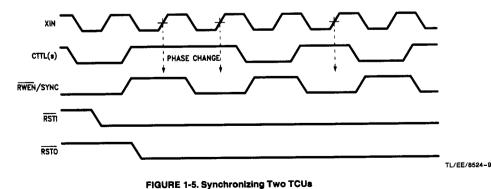

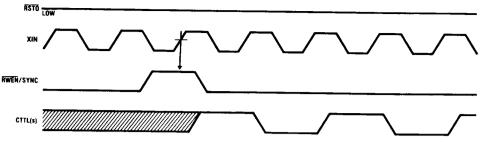

During reset, (when RSTO is low), one or more TCUs can be synchronized with a reference (Master) TCU. The

RWEN/SYNC input to the slave TCU(s) is used for synchronization. The Slave TCU samples the RWEN/SYNC input on the rising edge of XIN. When RSTO is low and CTTL is high (see Figure 1-5), if RWEN/SYNC is sampled high, the phase of CTTL of the Slave TCU is shifted by one XIN clock cycle.

Two possible circuits for TCU synchronization are illustrated in Figures 1-4a and 1-4b. It should be noted that when  $\overline{\text{RWEN}}/\text{SYNC}$  is high, the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  signals will be TRI-STATE on the slave TCU.

Note: RWEN/SYNC should not be kept constantly high during reset, otherwise the clock will be stopped and the device will not exit reset when RSTI is deasserted.

FIGURE 1-4a. Slave TCU Does Not Use RWEN During Normal Operation

FIGURE 1-4b. Slave TCU Uses Both SYNC and RWEN

Note: When two or more TCUs are to be synchronized, the XIN of all the TCUs should be connected to an external clock source. For details on the external clock, see Switching Specifications in Section 2.

FIGURE 1-6. Synchronizing One TCU to An External Pulse

TL/EE/8524-10

In addition to synchronizing two or more TCUs, the RWEN/ SYNC input can be used to "fix" the phase of one TCU to an external pulse. The pulse to be used must be high for only one rising edge of XIN. Independent of CTTL's state at the XIN rising edge, the CTTL state following the XIN rising edge will be high. Figure 1-6 shows the timing of this sequence.

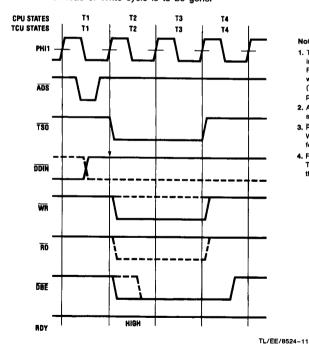

#### 1.6 BUS CYCLES

In addition to providing all the necessary clock signals, the NS32C201 TCU provides bus control signals to the system. The TCU senses the ADS signal from the CPU or MMU to start a bus cycle. The  $\overline{\mbox{DDIN}}$  input signal is also sampled to determine whether a Read or Write cycle is to be gener-

ated. In addition to  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$ , other signals are provided: DBE and TSO. DBE is used to enable data buffers. The leading edge of DBE is delayed a half clock period during Read cycles to avoid bus conflicts between data buffers and either the CPU or the MMU. This is shown in Figure 1-7.

The Timing State Output (TSO) is a general purpose signal that may be used by external logic for synchronizing to a System cycle. TSO is activated at the beginning of state T2 and returns to the high level at the beginning of state T4 of the CPU cycle. TSO can be used to gate the CWAIT signal when continuous waits are required. Another application of TSO is the control of interface circuitry for dynamic RAMs.

#### FIGURE 1-7. Basic TCU Cycle (Fast Cycle)

#### Notes:

- 1. The CPU and TCU view some timing states (T-states) differently. For clarity, references to T-states will sometimes be followed by (TCU) or (CPU). (CPU) also implies (MMU).

- 2. Arrows indicate when the TCU samples the input.

- 3. RWEN is assumed low (RD and WR enabled) unless specified differently.

- 4. For clarity, T-states for both the TCU and CPU are shown above the diagrams. (See Note 1.)

4-7

## 1.7 BUS CYCLE EXTENSION

The NS32C201 TCU uses the Wait input signals to extend normal bus cycles. A normal bus cycle consists of four PHI1 clock cycles. Whenever one or more Wait inputs to the TCU are activated, a bus cycle is extended by at least one PHI1 clock cycle. The purpose is to allow the CPU to access slow memories or peripherals. The TCU responds to the Wait signals by pulling the RDY signal low as long as Wait States are to be inserted in the Bus cycle.

There are three basic cycle extension modes provided by the TCU, as described below.

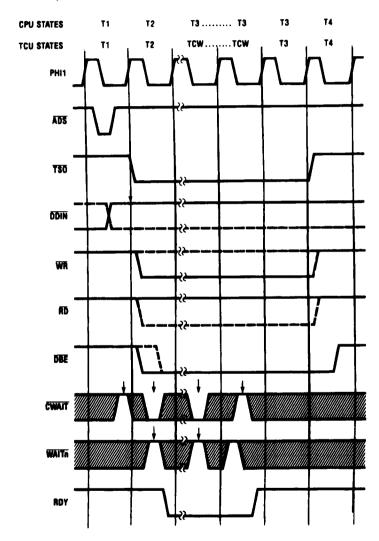

#### 1.7.1 Normal Wait States

This is a normal Wait State insertion mode. It is initiated by pulling CWAIT or any of the WAITn lines low in the middle of T2. Figure 1-8 shows the timing diagram of a bus cycle when CWAIT is sampled high at the end of T1 and low in the middle of T2.

FIGURE 1-8. Wait State Insertion Using CWAIT (Fast Cycle)

TL/EE/8524-12

The RDY signal goes low during T2 and remains low until CWAIT is sampled high by the TCU. RDY is pulled high by the TCU during the same PHI1 cycle in which the CWAIT line is sampled high.

If any of the  $\overline{\text{WAITn}}$  signals are sampled low during T2 and

CWAIT is high during the entire bus cycle, then the RDY line goes low for 1 to 15 clock cycles, depending on the binary weighted value of WAITn. If, for example, WAIT1 and WAIT4 are sampled low, then five wait states will be inserted. This is shown in *Figure* 1-9.

FIGURE 1-9. Wait State Insertion Using WAITn (Fast Cycle)

TL/EE/8524-13

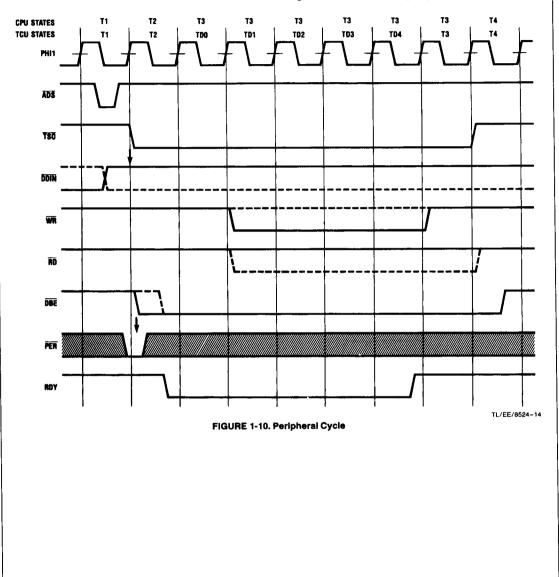

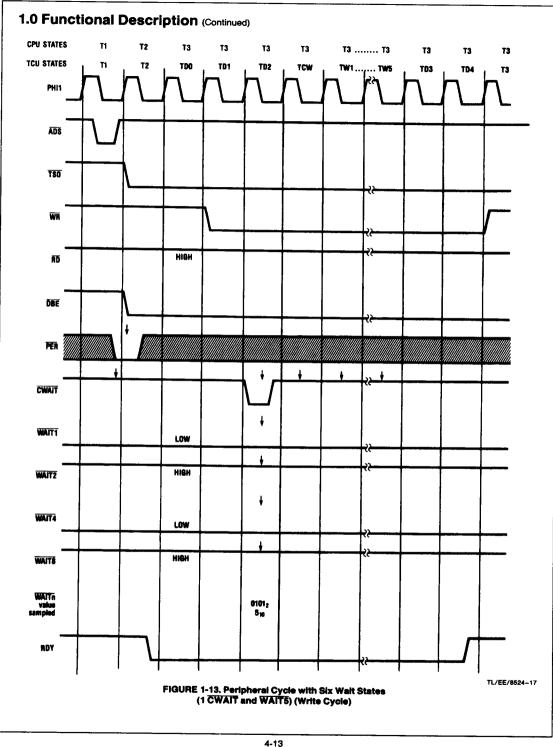

## 1.7.2 Peripheral Cycle

This cycle is entered when the PER signal line is sampled low at the beginning of T2. The TCU adds five wait states identified as TD0-TD4 into a normal bus cycle. The RD and

$\overline{WR}$  signals are also re-shaped so the setup and hold times for address and data will be increased.

This may be necessary when slower peripherals must be accessed.

Figure 1-10 shows the timing diagram of a peripheral cycle.

## 1.7.3 Cycle Hold

If the CWAIT input is sampled low at the end of state T1, the TCU will go into cycle hold mode and stay in this mode for as long as CWAIT is kept low. During this mode the control signals RD, WR. TSO and DBE are kept inactive; RDY is

pulled low, thus causing wait states to be inserted into the bus cycle. The cycle hold feature can be used in applications involving dynamic RAMs. A timing diagram showing the cycle hold feature is shown in *Figure 1-11*.

FIGURE 1-11. Cycle Hold Timing Diagram

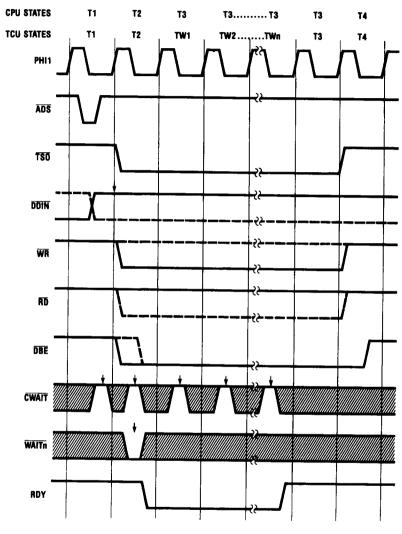

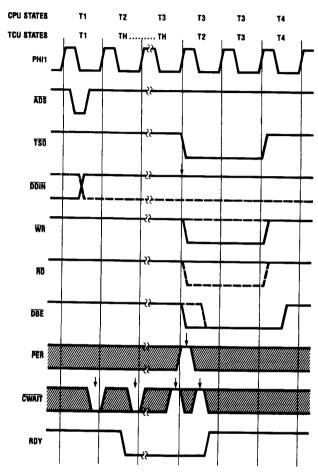

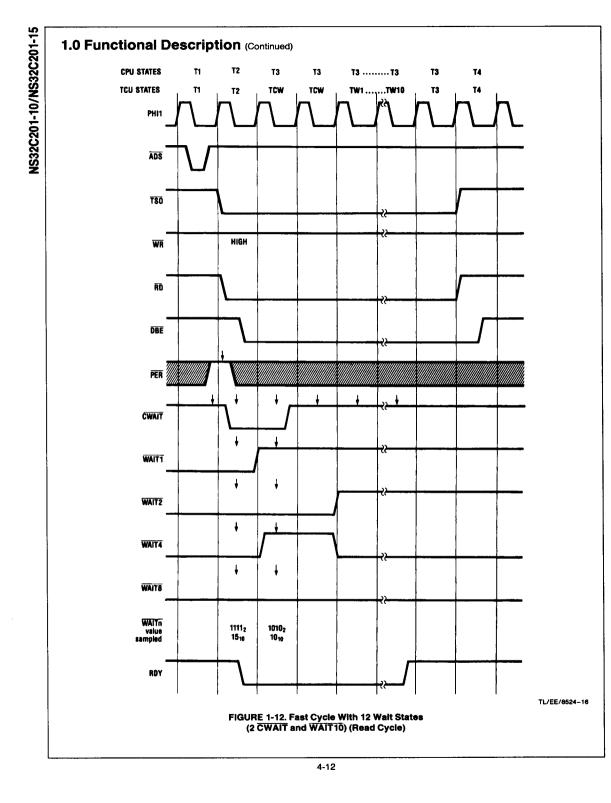

### 1.8 BUS CYCLE EXTENSION COMBINATIONS

Any combination of the TCU input signals used for extending a bus cycle can be activated at one time. The TCU will honor all of the requests according to a certain priority scheme. A cycle hold request is assigned top priority. It follows a peripheral cycle request, and then CWAIT and WAIT respectively.

If, for example, all the input signals CWAIT, PER and WAITn are asserted at the beginning of the cycle, the TCU will enter the cycle hold mode. As soon as CWAIT goes high, the

input signal PER is sampled to determine whether a peripheral cycle is requested.

TL/EE/8524-15

Next, the TCU samples CWAIT again and WAITn to check whether additional wait states have to be inserted into the bus cycle. This sampling point depends on whether PER was sampled high or low. If PER was sampled high, then the sampling point will be in the middle of the TCU state T2, (Figure 1-14), otherwise it will occur three clock cycles later (Figure 1-15). Figures 1-12 to 1-15 show the timing diagrams for different combinations of cycle extensions.

FIGURE 1-15. Cycle Hold of a Peripheral Cycle

TL/EE/8524~19

### 1.9 OVERRIDING WAITN WAIT STATES

The TCU handles the WAITn Wait States by means of an internal counter that is reloaded with the binary value corresponding to the state of the WAITn inputs each time CWAIT is sampled low, and is decremented when CWAIT is high.

This allows to either extend a bus cycle of a predefined number of clock cycles, or prematurely terminate it. To ter-

minate a bus cycle, for example,  $\overline{\text{CWAIT}}$  must be asserted for at least one clock cycle, and the  $\overline{\text{WAITn}}$  inputs must be forced to their inactive state.

At least one wait state is always inserted when using this procedure as a result of CWAIT being sampled low. Figure 1-16 shows the timing diagram of a prematurely terminated bus cycle where eleven wait states were being inserted.

## 2.0 Device Specifications

#### 2.1 PIN DESCRIPTIONS

The following is a description of all NS32C201 pins. The descriptions reference portions of the Functional Description, Section 1.

#### 2.1.1 Supplies

Power (Vcc): +5V positive supply. Section 1.1.

Ground (GND): Power supply return. Section 1.1.

#### 2.1.2 Input Signals

Reset Input (RSTI): Active low. Schmitt triggered, asynchronous signal used to generate a system reset. Section 1.4.

Address Strobe (ADS): Active low. Identifies the first timing state (T1) of a bus cycle.

Data Direction Input (DDIN): Active low. Indicates the direction of the data transfer during a bus cycle. Implies a Read when low and a Write when high.

Note: In Rev. A of the NS32C201 this signal is CMOS compatible. In later revisions it is TTL compatible.

Read/Write Enable and Synchronization (RWEN/SYNC): TRI-STATE® the RD and the WR outputs when high and enables them when low. Also used to synchronize the phase of the TCU clock signals, when two or more TCUs are used. Section 1.5.

Crystal or External Clock Source (XIN): Input from a crystal or an external clock source. Section 1.3.

Continuous Wait (CWAIT): Active low. Initiates a continuous wait if sampled low in the middle of T2 during a Fast cycle, or in the middle of TD2, during a peripheral cycle. If CWAIT is low at the end of T1, it initiates a Cycle Hold. Section 1.7.1.

Four-Bit Wait State Inputs (WAIT1, WAIT2, WAIT4 and WAIT8): Active low. These inputs, (collectively called WAITn), allow from zero to fifteen wait states to be specified. They are binary weighted. Section 1.7.1.

Peripheral Cycle (PER): Active low. If active, causes the TCU to insert five wait states into a normal bus cycle. It also causes the Read and Write signals to be re-shaped to meet the setup and hold timing requirement of slower MOS peripherals. Section 1.7.2.

### 2.1.3 Output Signals

Reset Output (RSTO): Active low. This signal becomes active when RSTI is low, initiating a system reset. RSTO goes high on the first rising edge of PHI1 after RSTI goes high. Section 1.4.

**Read Strobe (RD):** (TRI-STATE) Active low. Identifies a Read cycle. It is decoded from DDIN and TRI-STATE by RWEN/SYNC. Section 1.6.

Write Strobe (WR): (TRI-STATE) Active low. Identifies a Write cycle. It is decoded from DDIN and TRI-STATE by RWEN/SYNC. Section 1.6.

Note: RD and WR are mutually exclusive in any cycle. Hence they are never low at the same time.

Data Buffer Enable (DBE): Active low. This signal is used to control the data bus buffers. It is low when the data buffers are to be enabled. Section 1.6.

Timing State Output (TSO): Active low. The falling edge of TSO signals the beginning of state T2 of a bus cycle. The rising edge of TSO signals the beginning of state T4. Section 1.6.

Ready (RDY): Active high. This signal will go low and remain low as long as wait states are to be inserted in a bus cycle. It is normally connected to the RDY input of the CPU. Section 1.7.

Fast Clock (FCLK): This is a clock running at the same frequency as the crystal or the external source. Its frequency is twice that of the CPU clocks. Section 1.3.

CPU Clocks (PHI1 and PHI2): These outputs provide the Series 32000 CPU with two phase, non-overlapping clock signals. Their frequency is half that of the crystal or external source. Section 1.3.

System Clock (CTTL): This is a system version of the PHI1 clock. Hence, it operates at the CPU clock frequency. Section 1.3.

Crystal Output (XOUT): This line is used as the return path for the crystal (if used). It must be left open when an external clock source is used to drive XIN. Section 1.2.

Supply Voltage

## 2.0 Device Specifications (Continued)

2.2 ABSOLUTE MAXIMUM RATINGS (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Input Voltages -0.5V to  $V_{CC}$  + 0.5V **Output Voltages** -0.5V to  $V_{CC} + 0.5V$

-65°C to +150°C Storage Temperature

Lead Temperature (Soldering, 10 sec.) 300°C 1W

Continous Power Dissipation

Note: Absolute maximum ratings indicate limits beyond which permament damage may occur. Continuous operation at these limits is not intended; operation should be limited to those conditions specified under Electrical Character-

2.3 ELECTRICAL CHARACTERISTICS  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ ,  $V_{CC} = 5\text{V} \pm 5\%$ , GND = 0V

| Symbol           | Parameter                     | Conditions                                                    | Min                  | Тур | Max                  | Units |

|------------------|-------------------------------|---------------------------------------------------------------|----------------------|-----|----------------------|-------|

| V <sub>IL</sub>  | Input Low Voltage             | All Inputs Except RSTI & XIN                                  |                      |     | 0.8                  | ٧     |

| V <sub>IH</sub>  | Input High Voltage            | All Inputs Except RSTI & XIN                                  | 2.0                  |     |                      | ٧     |

| V <sub>T+</sub>  | RSTI Rising Threshold Voltage | V <sub>CC</sub> = 5.0V                                        | 2.5                  |     | 3.5                  | ٧     |

| V <sub>HYS</sub> | RSTI Hysteresis Voltage       | V <sub>CC</sub> = 5.0V                                        | 0.8                  |     | 1.9                  | ٧_    |

| V <sub>XL</sub>  | XIN Input Low Voltage         |                                                               |                      |     | 0.20 V <sub>CC</sub> | ٧     |

| V <sub>XH</sub>  | XIN Input High Voltage        |                                                               | 0.80 V <sub>CC</sub> |     |                      | V     |

| IIL              | Input Low Current             | V <sub>IN</sub> = 0V                                          |                      |     | -10                  | μΑ    |

| I <sub>IH</sub>  | Input High Current            | V <sub>IN</sub> = V <sub>CC</sub>                             |                      |     | 10                   | μΑ    |

| V <sub>OL</sub>  | Output Low Voltage            | PHI1 & PHI2, I = 1 mA All Other Outputs Except XOUT, I = 2 mA |                      |     | 0.10 V <sub>CC</sub> | ٧     |

| V <sub>OH</sub>  | Output High Voltage           | All Outputs Except XOUT, I = -1 mA                            | 0.90 V <sub>CC</sub> |     |                      | v     |

| IL.              | Leakage Current on RD/WR      | 0.4V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                      | -20                  |     | + 20                 | μΑ    |

| lcc              | Supply Current                | f <sub>xin</sub> = 20 MHz                                     |                      | 100 | 120                  | mA    |

Note 1: All typical values are for  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$ .

# **Connection Diagram**

Order Number NS32C201D or NS32C201N See NS Package Number D24C or N24A

FIGURE 2.1

# 2.0 Device Specifications (Continued)

## 2.4 SWITCHING CHARACTERISTICS

#### 2.4.1 Definitions

All the timing specifications given in this section refer to 2.0V on the rising or falling edges of the clock phases PHI1 and PHI2; to 15% or 85% of  $V_{\rm CC}$  on all the CMOS output signals, and to 0.8V or 2.0V on all the TTL input signals, unless specifically stated otherwise.

## 2.4.2 Output Loading

| Capacitive loading on output pins for the NS32C201. |

|-----------------------------------------------------|

| RDY, DBE, TSO50 pF                                  |

| RD, WR75 pF                                         |

| CTTL50 ÷ 100 pF                                     |

| FCLK100 pF                                          |

| PHI1, PHI2170 pF                                    |

#### **ABBREVIATIONS**

L.E.—Leading Edge

T.E.—Trailing Edge

R.E.—Rising Edge

F.E.—Falling Edge

## 2.4.3 Timing Tables

| Symbol                  | Figure | Description                                                              | Reference/Conditions                            | NS32C201-10                   |                                | NS32C201-15                    |                                | Units |

|-------------------------|--------|--------------------------------------------------------------------------|-------------------------------------------------|-------------------------------|--------------------------------|--------------------------------|--------------------------------|-------|

|                         |        |                                                                          |                                                 | Min                           | Max                            | Min                            | Max                            |       |

|                         |        | N, FCLK, PHI1 & PHI2) TIMIN                                              | G                                               |                               |                                |                                |                                |       |

| t <sub>Cp</sub>         | 2.2    | Clock Period                                                             | PHI1 R.E. to Next<br>PHI1 R.E.                  | 100                           |                                | 66                             |                                | ns    |

| t <sub>CLh</sub>        | 2.2    | Clock High Time                                                          | At 90% V <sub>CC</sub> on PHI1<br>(Both Edges)  | 0.5 t <sub>Cp</sub><br>15 ns  | 0.5 t <sub>Cp</sub><br>-7 ns   | 0.5 t <sub>Cp</sub><br>- 10 ns | 0.5 t <sub>Cp</sub><br>-3 ns   |       |

| t <sub>CLI</sub>        | 2.2    | Clock Low Time                                                           | At 15% V <sub>CC</sub> on PHI1                  | 0.5 t <sub>Cp</sub><br>-5 ns  | 0.5 t <sub>Cp</sub><br>+ 10 ns | 0.5 t <sub>Cp</sub><br>-5 ns   | 0.5t <sub>CP</sub><br>+6 ns    |       |

| t <sub>CLw(1,2)</sub>   | 2.2    | Clock Pulse Width                                                        | At 2.0V on PHI1, PHI2<br>(Both Edges)           | 0.5 t <sub>CP</sub><br>-10 ns | 0.5 t <sub>CP</sub><br>-4 ns   | 0.5 t <sub>CP</sub><br>-6 ns   | 0.5 t <sub>CP</sub><br>-4 ns   |       |

| t <sub>CLwas</sub>      |        | PHI1, PHI2 Asymmetry (t <sub>CLw</sub> (1) - t <sub>CLw</sub> (2))       | At 2.0V on PHI1,<br>PHI2                        | -5                            | 5                              | -3                             | 3                              | ns    |

| tCLR                    | 2.2    | Clock Rise Time                                                          | 15% to 90% V <sub>CC</sub><br>on PHI1 R.E.      |                               | 8                              |                                | 6                              | ns    |

| tolf                    | 2.2    | Clock Fall Time                                                          | 90% to 15% V <sub>CC</sub><br>on PHI1 F.E.      |                               | 8                              |                                | 6                              | ns    |

| t <sub>nOVL</sub> (1,2) | 2.2    | Clock Non-Overlap Time                                                   | At 15% V <sub>CC</sub> on PHI1,<br>PHI2         | -2                            | +2                             | -2                             | +2                             | ns    |

| t <sub>nOVLas</sub>     |        | Non-Overlap Asymmetry<br>(t <sub>nOVL</sub> (1) - t <sub>nOVL</sub> (2)) | At 15% V <sub>CC</sub> on PHI1,<br>PHI2         | -4                            | 4                              | -3                             | 3                              | ns    |

| <sup>t</sup> Xh         | 2.2    | XIN High Time<br>(External Input)                                        | At 80% V <sub>CC</sub> on XIN<br>(Both Edges)   | 16                            |                                | 10                             |                                | ns    |

| t <sub>XI</sub>         | 2.2    | XIN Low Time<br>(External Input)                                         | At 15% V <sub>CC</sub> on XIN<br>(Both Edges)   | 16                            |                                | 10                             |                                | ns    |

| <sup>t</sup> XFr        | 2.2    | XIN to FCLK R.E. Delay                                                   | 80% V <sub>CC</sub> on XIN R.E.<br>to FCLK R.E. | 6                             | 29                             | 6                              | 25                             | ns    |

| <sup>t</sup> XFf        | 2.2    | XIN to FCLK F.E. Delay                                                   | 15% V <sub>CC</sub> on XIN F.E. to FCLK F.E.    | 6                             | 29                             | 6                              | 25                             | ns    |

| txcr                    | 2.2    | XIN to CTTL R.E. Delay                                                   | 80% V <sub>CC</sub> on XIN R.E.<br>to CTTL R.E. | 6                             | 34                             | 6                              | 25                             | ns    |

| t <sub>XPr</sub>        | 2.2    | XIN to PHI1 R.E. Delay                                                   | 80% V <sub>CC</sub> on XIN R.E.<br>to PHI1 R.E. | 6                             | 32                             | 6                              | 25                             | ns    |

| t <sub>FCr</sub>        | 2.2    | FCLK to CTTL R.E. Delay                                                  | FCLK R.E. to CTTL R.E.                          | 0                             | 6                              | 0                              | 6                              | ПB    |

| tFCI                    | 2.2    | FCLK to CTTL F.E. Delay                                                  | FCLK R.E. to CTTL F.E.                          | -3                            | 4                              | -3                             | 4                              | ns    |

| t <sub>FPr</sub>        | 2.3    | FCLK to PHI1 R.E. Delay                                                  | FCLK R.E. to PHI1 R.E.                          | -3                            | 4                              | -3                             | 4                              | ns    |

| t <sub>FPf</sub>        | 2.3    | FCLK to PHI1 F.E. Delay                                                  | FCLK R.E. to PHI1 F.E.                          | -5                            | 2                              | -5                             | 2                              | ns    |

| t <sub>Fw</sub>         | 2.3    | FCLK Pulse Width with Crystal                                            | At 50% V <sub>CC</sub> on FCLK<br>(Both Edges)  | 0.25 t <sub>Cp</sub><br>-5 ns | 0.25 t <sub>Cp</sub><br>+ 5 ns | 0.25 t <sub>Cp</sub><br>-5 ns  | 0.25 t <sub>Cp</sub><br>+ 5 ns | ,,,,  |

| t <sub>PCf</sub>        | 2.3    | PHI2 R.E.to CTTL<br>F.E. Delay                                           | PHI2 R.E. to CTTL F.E.                          | -3                            | 4                              | -3                             | 3                              | ns    |

| <sup>t</sup> CTw        | 2.3    | CTTL Pulse Width                                                         | At 50% V <sub>CC</sub> on CTTL<br>(Both Edges)  | 0.5 t <sub>Cp</sub><br>-7 ns  | 0.5 t <sub>Cp</sub><br>+ 1 ns  | 0.5 t <sub>Cp</sub><br>-5 ns   | 0.5 t <sub>Cp</sub><br>+ 1 ns  |       |

Note 1: txcr. tFcr. tFcr. tpcr. tcTh are measured with 100 pF load on CTTL.

Note 2: PHI1 and PHI2 are interchangeable for the following parameters: top, total, to

# 2.0 Device Specifications (Continued)

2.4.3 Timing Tables (Continued)

| Symbol              | Figure      | Description                            | Reference/Conditions                       | NS32C201-10 |         | NS32C201-15 |         | Unit         |

|---------------------|-------------|----------------------------------------|--------------------------------------------|-------------|---------|-------------|---------|--------------|

|                     |             |                                        |                                            | Min         | Max     | Min         | Max     | <u> </u>     |

| CTTL TIM            | ING (CL = 5 | 0 pF)                                  |                                            |             |         | Г           |         | 1            |

| t <sub>PCr</sub>    | 2.3         | PHI1 to CTTL R.E. Delay                | PHI1 R.E. to CTTL R.E.                     | -2          | 5       | -2          | 3       | ns           |

| <sup>t</sup> CTR    | 2.3         | CTTL Rise Time                         | 10% to 90% V <sub>CC</sub><br>on CTTL R.E. |             | 7       |             | 6       | ns           |

| <sup>t</sup> CTF    | 2.3         | CTTL Fall Time                         | 90% to 10% V <sub>CC</sub><br>on CTTL F.E. |             | 7       |             | 6       | ns           |

| CTTL TIM            | ING (CL = 1 | 00 pF)                                 |                                            |             |         |             |         |              |

| t <sub>PCr</sub>    | 2.3         | PHI1 to CTTL R.E. Delay                | PHI1 R.E. to CTTL R.E.                     | -2          | 6       | -2          | 4       | ns           |

| <sup>t</sup> CTR    | 2.3         | CTTL Rise Time                         | 10% to 90% V <sub>CC</sub><br>on CTTL R.E. |             | 8       |             | 7       | ns           |

| <sup>t</sup> CTF    | 2.3         | CTTL Fall Time                         | 90% to 10% V <sub>CC</sub><br>on CTTL F.E. |             | 8       |             | 7       | ns           |

| CONTRO              | L INPUTS (R | ST1, ADS, DDIN) TIMING                 |                                            |             |         |             |         |              |

| t <sub>RSTs</sub>   | 2.4         | RSTI Setup Time                        | Before PHI1 R.E.                           | 20          |         | 15          |         | $oxed{oxed}$ |

| t <sub>ADs</sub>    | 2.4         | ADS Setup Time                         | Before PHI1 R.E.                           | 25          |         | 20          |         | ns           |

| t <sub>ADw</sub>    | 2.4         | ADS Pulse Width                        | ADS L.E. to ADS T.E.                       | 25          |         | 20          |         | n            |

| t <sub>DDs</sub>    | 2.4         | DDIN Setup Time                        | Before PHI1 R.E.                           | 15          |         | 13          | <u></u> | ns           |

| CONTRO              | L OUTPUTS   | RSTO, TSO, RD, WR, DBE & RWEN          | /SYNC) TIMING                              |             |         |             |         |              |

| tastr               | 2.4         | RSTO R.E. Delay                        | After PHI1 R.E.                            |             | 21      |             | 10      | n            |

| t <sub>Tf</sub>     | 2.5         | TSO L.E. Delay                         | After PHI1 R.E.                            |             | 12      |             | 8       | n            |

| t <sub>Tr</sub>     | 2.5         | TSO T.E. Delay                         | After PHI1 R.E.                            | 3           | 18      | 3           | 10      | n            |

| t <sub>RWf(F)</sub> | 2.5         | RD/WR L.E. Delay (Fast Cycle)          | After PHI1 R.E.                            |             | 30      |             | 21      | n            |

| t <sub>RWf(S)</sub> | 2.6         | RD/WR L.E. Delay<br>(Peripheral Cycle) | After PHI1 R.E.                            |             | 25      |             | 15      | n            |

| t <sub>RWr</sub>    | 2.5/6       | RD/WR T.E. Delay                       | After PHI1 R.E.                            | 3           | 20      | 3           | 15      | n            |

| t <sub>DBf(W)</sub> | 2.5/6       | DBE L.E. Delay (Write Cycle)           | After PHI1 R.E.                            |             | 25      |             | 15      | n            |

| t <sub>DBf(R)</sub> | 2.5/6       | DBE L.E. Delay (Read Cycle)            | After PHI2 R.E.                            |             | 20      |             | 11      | n            |

| t <sub>DBr</sub>    | 2.5/6       | DBE T.E. Delay                         | After PHI2 R.E.                            |             | 20      |             | 15      | n            |

| t <sub>pLZ</sub>    | 2.7         | RD,WR Low Level to TRI-STATE           | After RWEN/SYNC R.E.                       |             | 25      |             | 20      | n            |

| t <sub>pHZ</sub>    | 2.7         | RD,WR High Level to TRI-STATE          | After RWEN/SYNC R.E.                       |             | 20      |             | 15      | n            |

| t <sub>pŽL</sub>    | 2.7         | RD,WR TRI-STATE to Low Level           | After RWEN/SYNC F.E.                       |             | 25      |             | 18      | n            |

| t <sub>pZH</sub>    | 2.7         | RD,WR TRI-STATE to High Level          | After RWEN/SYNC F.E.                       |             | 25      |             | 18      | n            |

| WAIT ST             | ATES & CYC  | LE HOLD (CWAIT, WAITn, PER & R         | DY) TIMING                                 |             |         |             |         |              |

| t <sub>CWs(H)</sub> | 2.8         | CWAIT Setup Time (Cycle Hold)          | Before PHI1 R.E.                           | 30          | <u></u> | 20          |         | l n          |

| t <sub>CWh(H)</sub> | 2.8         | CWAIT Hold Time (Cycle Hold)           | After PHI1 R.E.                            | 0           |         | 0           |         | n            |

| t <sub>CWs(W)</sub> | 2.8/9       | CWAIT Setup Time (Wait States)         | Before PHI2 R.E.                           | 10          |         | 6           |         | n            |

| t <sub>CWh(W)</sub> | 2.9         | CWAIT Hold Time (Wait States)          | After PHI2 R.E.                            | 20          |         | 10          |         | n            |

| t <sub>Ws</sub>     | 2.9         | WAITn Setup Time                       | Before PHI2 R.E.                           | 7           |         | 6           |         | п            |

| t <sub>Wh</sub>     | 2.9         | WAITn Hold Time                        | After PHI2 R.E.                            | 15          |         | 10          |         | n            |

| tps                 | 2.10        | PER Setup Time                         | Before PHI1 R.E.                           | 7           |         | 5           |         | n            |

| t <sub>Ph</sub>     | 2.10        | PER Hold Time                          | After PHI1 R.E.                            | 30          |         | 20          |         | n            |

| t <sub>Rd</sub>     | 2.8/9/10    | RDY Delay                              | After PHI2 R.E.                            |             | 25      |             | 12      | n            |

| SYNCHR              | ONIZATION   | (SYNC) TIMING                          |                                            |             |         |             |         |              |

| t <sub>Sys</sub>    | 2.11        | SYNC Setup Time                        | Before XIN R.E.                            | 6           | ļ       | 6           |         | r            |

| t <sub>Syh</sub>    | 2.11        | SYNC Hold Time                         | After XIN R.E.                             | 5           | 1       | 5           |         | n            |

| tcs                 | 2.11        | CTTL/SYNC Inversion Delay              | CTTL (master) to<br>RWEN/SYNC (slave)      |             | 10      |             | 7       | n            |