# NS405-Series Display/Terminal Management Processor (TMP)

# **General Description**

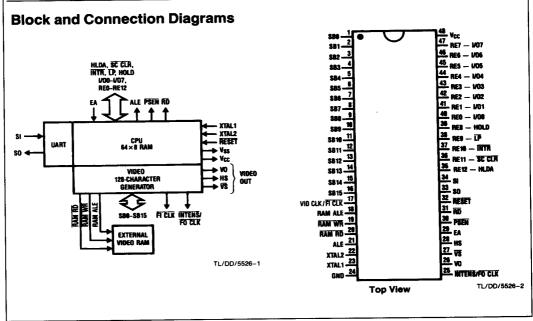

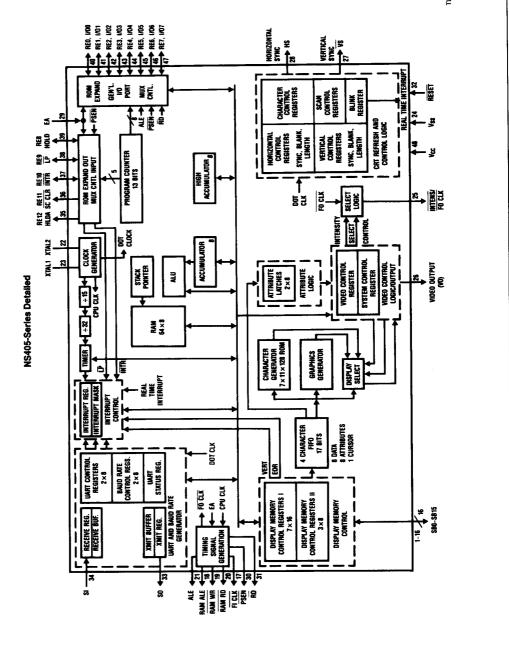

The NS405 is a CRT terminal controller on a chip. It is a microcomputer system which replaces the following LSI circuits commonly found in a CRT data terminal:

- Microcomputer

- Baud Rate Generator

- CRT Controller

DMA Controller

- Interrupt Controller

- Character Generator

- Parallel I/O Controller

- Character Gener

- Timer

• UART

In addition the NS405 includes powerful attribute logic, two graphics display modes, and fast video output circuits.

The NS405 is primarily intended for use in low-cost terminals, but contains many features which make it a superior building block for "smart" terminals and word processing systems.

The NS405 interfaces easily to the display monitor, keyboard, display memory, and I/O ports. The architecture and instruction set are derived from the 8048-series microcontrollers. The instruction set has been enhanced and the architecture tailored to allow the NS405 CPU to efficiently manage a large display memory and an extensive interrupt environment.

The TMP can be used to easily and inexpensively add a display to many systems where it was previously impractical, it is not limited to terminal applications.

# **Features**

- Enhanced 8048 instruction set and architecture

- Up to 8k x 8 ROM external with ROM expand bus

- On-board RAM 64 x 8

- Programmable display format

- On-board video memory management unit

- 16-bit bidirectional display memory bus (direct video and attribute RAM interface)

- Built-in timer

- Real-time clock (may be programmed for 1 Hz)

- Video control signals

- Eight independent attributes

- Pixel and block graphics display modes

- Programmable cursor characteristics

- m Programmable CRT refresh rate

- Light pen feature

- UART, programmable baud rate up to 19.2k baud

- Character generator (128 characters 7 x 11 max)

- Single 5-volt supply @ 110 mA (typ)

- Up to 18 MHz video dot rate (12 MHz CPU clock)

- 48-pin package

- 8-bit parallel I/O port (multiplexed with external ROM)

- Extensive I/O expansion capabilities

- Up to 64k by 8 or 16 video RAM

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Temperature Under Bias

0°C to +70°C

Storage Temperature

All Input or Output Voltages

with Respect to V<sub>SS</sub>\*

-65°C to +150°C -0.5V to +7.0V Power Dissipation ESD

\*EA, SI and VSYNC may be subjected to V<sub>SS</sub> + 15V.

2000V

1.5W

Note: Absolute maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended; operations should be limited to those conditions specified under DC Electrical Character-

# **DC Electrical Characteristics**

$T_A = 0$ °C to +70°C,  $V_{CC} = +5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise specified

| Symbol           | Parameter                                                        | Test Conditions                                            | Min  | Max  | Units |

|------------------|------------------------------------------------------------------|------------------------------------------------------------|------|------|-------|

| V <sub>IL1</sub> | Input Low Voltage (All Except XTAL1, XTAL2, RESET)               | -                                                          | -0.5 | 0.8  | v     |

| V <sub>IH1</sub> | Input High Voltage (All Except XTAL1, XTAL2, RESET)              |                                                            | 2.0  | Vcc  | V     |

| V <sub>IL2</sub> | Input Low Voltage (XTAL1, XTAL2, RESET)                          |                                                            | -0.5 | 0.6  | V     |

| V <sub>IH2</sub> | Input High Voltage (XTAL1, XTAL2, RESET)                         |                                                            | 3.8  | Vcc  | v     |

| V <sub>OL</sub>  | Output Low Voltage (All Except INTENS, VO)                       | I <sub>OL</sub> = 2.0 mA                                   |      | 0.4  | V     |

| V <sub>OH</sub>  | Output High Voltage (All Except INTENS, VO)                      | l <sub>OH</sub> = -125 μA                                  | 2.4  | Vcc  | v     |

| VoL              | Output Low Voltage (INTENS, VO)                                  | I <sub>OI</sub> = 5.0 mA                                   | i    | 0.4  | v     |

| V <sub>OH</sub>  | Output High Voltage (INTENS, VO)                                 | l <sub>OH</sub> = -500 μA                                  | 2.4  |      | v     |

| I <sub>IL</sub>  | Input Leakage Current (EA, INT, SI)                              | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>        |      | ±10  | μА    |

| loL              | Output Leakage Current<br>(ROM Expand Bus, High Impedance State) | V <sub>CC</sub> ≥ V <sub>IN</sub> ≥ V <sub>SS</sub> + 0.45 |      | ±10  | μΑ    |

| l <sub>OL</sub>  | Output Leakage Current<br>(System Bus, High Impedance State)     | $V_{CC} \ge V_{IN} \ge V_{SS} + 0.45$                      |      | ±100 | μА    |

| Icc              | Total Supply Current                                             | T <sub>A</sub> = 25°C                                      |      | 150  | mA    |

# **AC Electrical Characteristics**

$T_A = 0$ °C to +70°C,  $V_{CC} = +5V \pm 10$ %,  $V_{SS} = 0$ V, unless otherwise specified

| Symbol           | Parameter                                             | Min  | Max   | Units |

|------------------|-------------------------------------------------------|------|-------|-------|

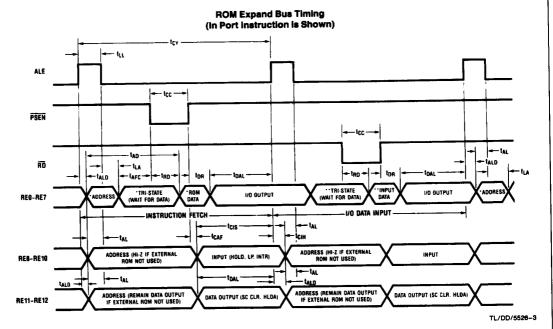

| AND ROM EX       | (PAND BUS TIMING                                      |      |       |       |

| FXTAL            | Crystal Frequency                                     | 3    | 18    | MHz   |

| F <sub>CPU</sub> | CPU Frequency                                         | 3    | 12    | MHz   |

| tcy              | CPU Cycle Time                                        | 1.25 | 7.5   | μs    |

| t <sub>DF</sub>  | Video Dot Time                                        | 55.5 | 333.3 | ns    |

| t <sub>LL</sub>  | ALE Pulse Width (Note 1)                              | 125  |       | ns    |

| t <sub>AL</sub>  | Address Setup to ALE (Note 1)                         | 55   |       | ns    |

| tLA              | Address Hold from ALE (Note 1)                        | 40   |       | ns    |

| tcc              | Control Pulse Width PSEN, RD (Note 1)                 | 250  |       | ns    |

| t <sub>DR</sub>  | Data Hold (Notes 1, 4)                                | 0    | 100   | ns    |

| t <sub>RD</sub>  | PSEN, RD to Data In (Note 1)                          |      | 220   | ns    |

| t <sub>AD</sub>  | Address Setup to Data In (Note 1)                     |      | 360   | ns    |

| t <sub>AFC</sub> | Address Float to RD, PSEN (Notes 1, 5)                | 0    |       | ns    |

| t <sub>CAF</sub> | PSEN to Address Float (Notes 1, 5)                    | -10  | + 10  | ns    |

| t <sub>DAL</sub> | Data Setup to ALE (RE0-7, 11, 12) (Note 1)            | 55   |       | ns    |

| t <sub>ALD</sub> | Data Hold from ALE (RE0-7, 11, 12) (Note 1)           | 40   |       | ns    |

| t <sub>CIS</sub> | Control Input Setup to ALE (RE8, 9, 10) (Note 1)      | 240  |       | ns    |

| t <sub>CIH</sub> | Control Input Hold from ALE (RE8, 9, 10) (Notes 1, 4) | 75   | 125   | ns    |

# **AC Electrical Characteristics**

$T_A = 0$ °C to +70°C,  $V_{CC} = +5V \pm 10$ %,  $V_{SS} = 0$ V, unless otherwise specified (Continued)

| Symbol           | Parameter                                  | Min | Max | Units |

|------------------|--------------------------------------------|-----|-----|-------|

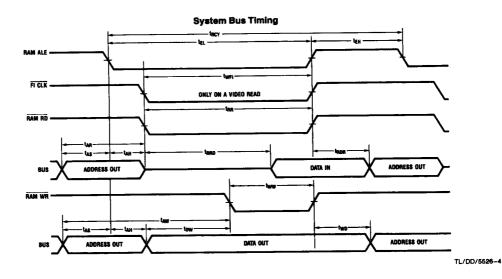

| EM BUS TIMIN     | G                                          |     |     |       |

| t <sub>EL</sub>  | RAM ALE Low Time (Note 1)                  | 250 |     | ns    |

| t <sub>EH</sub>  | RAM ALE High Time (Note 1)                 | 100 |     | ns    |

| tas              | Address Setup to RAM ALE (Note 1)          | 20  |     | ns    |

| t <sub>AH</sub>  | Address Hold from RAM ALE (Note 1)         | 10  |     | ns    |

| t <sub>RR</sub>  | RAM RD Width (Note 1)                      | 210 |     | ns    |

| t <sub>AR</sub>  | Address Setup to RAM RD (Note 1)           | 80  |     | ns    |

| tard             | Data Access from RAM RD (Note 1)           |     | 140 | ns    |

| t <sub>RDR</sub> | Data Hold from RAM RD (Notes 1, 4)         | 0   | 60  | ns    |

| twFl             | FIFO In Clock Width (Note 1)               | 210 |     | ns    |

| tww              | RAM WR Strobe Width (Note 1)               | 130 |     | ns    |

| t <sub>AW</sub>  | Address Setup to RAM WR (Note 1)           | 120 |     | ns    |

| t <sub>DW</sub>  | Data Setup to RAM WR (Note 1)              | 10  |     | ns    |

| t <sub>WD</sub>  | Data Hold from RAM WR (Note 1)             | 20  |     | ns    |

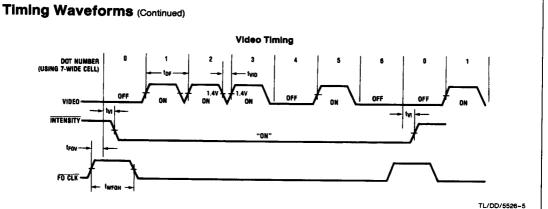

| O TIMING         |                                            |     |     |       |

| t <sub>DF</sub>  | Dot Period = $\frac{1}{f_c}$ (Note 1)      | 55  |     | ns    |

| t <sub>VID</sub> | Video Blank Time (Note 1)                  | 5   | 15  | ns    |

| t <sub>VI</sub>  | Skew, Intensity to Dot 0 (Note 1)          | -15 | 15  | ns    |

| t <sub>FOV</sub> | FIFO Out Clock to Dot 0 (Note 1)           |     | 15  | ns    |

| twfoh            | FIFO Out Clock Width High (Note 1, Note 2) | 55  | 165 | ns    |

<sup>\*1/3</sup> CPU cycle.

Note 1: Control outputs  $C_L = 80$  pF; ROM Expand Bus outputs  $C_L = 150$  pF; System Bus outputs  $C_L = 100$  pF;  $V_{OUT}$  & INTENS outputs  $C_L = 50$  pF;  $V_{CAL} = 18$  MHz;  $V_{CAL} = 100$  pF;  $V_{OUT} = 12$  MHz. XTAL1 & XTAL2 driven externally per Figure 12b with 50% duty cycle.

Note 2: FO CLK duty cycle is shown above.

Note 3: Hold request is latched. It is honored at the start of the next vertical retrace.

Note 4: Max spec. listed for user information only, to prevent bus contention. Maximum value not tested.

Note 5: Not tested.

| Character<br>Cell Width | FIFO Out<br>HIGH | FIFO Out<br>LOW |

|-------------------------|------------------|-----------------|

| 6                       | 1 dot            | 5 dots          |

| 7                       | 2 dots           | 5 dots          |

| 8                       | 2 dots           | 6 dots          |

| 9                       | 3 dots           | 6 dots          |

| 10                      | 3 dots           | 7 dots          |

# **Input Hold Times**

$T_A = 25^{\circ}C$ ,  $V_{CC} = +5V \pm 10\%$ ,  $V_{SS} = 0V$

| Input              | Min Active Time                                   |

|--------------------|---------------------------------------------------|

| Reset              | 50 ms (power up)<br>5 CPU Cycles (after power up) |

| External Interrupt | 2 CPU Cycle                                       |

| Light Pen          | 1 CPU Cycle                                       |

| I/O Input          | 1 CPU Cycle                                       |

| Hold Request       | 1 CPU Cycle (Note 3)                              |

# **FIFO**

Fall through should not be greater than 4 character times (character time =  $1/f_{XTAL} \times #dots/cell$ ).

Throughput rate must be at least the character rate (character rate = 1/character time).

<sup>\*\*1</sup> Dot time is 55 ns.

| Capacit | Capacitance TA = 25°C, VCC = VSS = 0V |                 |

|---------|---------------------------------------|-----------------|

| Symbol  | Parameter                             | Test Conditions |

| _       |                                       |                 |

| Symbol | Parameter         | Test Conditions                                      | Min | Max | Units |

|--------|-------------------|------------------------------------------------------|-----|-----|-------|

| CIN    | Input Capacitance | F <sub>C</sub> = 1 MHz (Note 5)                      |     | 10  | pF    |

| Cout   | Output and Reset  | Unmeasured Pins Returned to V <sub>SS</sub> (Note 5) |     | 20  | ρF    |

# **AC Electrical Characteristics in CPU Cycle Time**

CPU AND ROM EXPAND BUS TIMING (FOR REFERENCE ONLY)

| Symbol           | Paramete                 | r                          | Тур                                                                           |

|------------------|--------------------------|----------------------------|-------------------------------------------------------------------------------|

| tLL              | ALE Pulse Width          |                            | 14 t <sub>CY/60</sub>                                                         |

| t <sub>AL</sub>  | Address Setup to ALE     |                            | 8 t <sub>CY/60</sub>                                                          |

| t <sub>LA</sub>  | Address Hold from ALE    |                            | 6 t <sub>CY/60</sub>                                                          |

| tcc              | Control Pulse Width      | PSEN<br>RD                 | 24 t <sub>CY/60</sub><br>36 t <sub>CY/60</sub>                                |

| tcy              | CPU Cycle Time           |                            | $60 t_{CY/60} = 15/f_{CPU} = \frac{15}{f_{XTAL} \div 1 \text{ or } \div 1.5}$ |

| t <sub>DR</sub>  | Data Hold                |                            | -2 t <sub>CY/60</sub>                                                         |

| t <sub>RD</sub>  | Control Pulse to Data In | PSEN<br>RD                 | 18 t <sub>CY/60</sub><br>30 t <sub>CY/60</sub>                                |

| t <sub>AD</sub>  | Address Setup to Data I  | n                          | 32 t <sub>CY/60</sub>                                                         |

| t <sub>AFC</sub> | Address Float to         | PSEN<br>RD                 | 2 t <sub>CY/80</sub><br>2 t <sub>CY/60</sub>                                  |

| t <sub>CAF</sub> | PSEN to Address Float    |                            | 0 t <sub>CY/60</sub>                                                          |

| <sup>t</sup> DAL | Data Setup to ALE        | RE0-7<br>RE8-10<br>RE11-12 | 6 t <sub>CY/60</sub><br>- 2 t <sub>CY/60</sub><br>16 t <sub>CY/60</sub>       |

| t <sub>ALD</sub> | Data Hold from ALE       | RE0-7<br>RE8-12            | 2 tCY/60<br>6 tCY/60                                                          |

# SYSTEM BUS TIMING (FOR REFERENCE ONLY)

| Symbol           | Parameter                 | Tic                           | ks                                     |

|------------------|---------------------------|-------------------------------|----------------------------------------|

|                  |                           | Min                           | Max                                    |

| t <sub>EL</sub>  | RAM ALE Low Time          | 14 t <sub>CY/60</sub> - 42 ns |                                        |

| t <sub>EH</sub>  | RAM ALE High Time         | 6 t <sub>CY/60</sub> - 25 ns  |                                        |

| tas              | Address Setup to RAM ALE  | 4 t <sub>CY/60</sub> - 60 ns  | ******                                 |

| t <sub>AH</sub>  | Address Hold from RAM ALE | 2 t <sub>CY/60</sub> - 40 ns  | ······································ |

| tRCY             | Read or Write Cycle Time  |                               |                                        |

| t <sub>RR</sub>  | RAM RD Width              | 12 t <sub>CY/60</sub> - 40 ns | -                                      |

| t <sub>AR</sub>  | Address Setup to RAM RD   | 6 t <sub>CY/60</sub> - 45 ns  |                                        |

| t <sub>RRD</sub> | Data Access from RAM RD   |                               | 10 t <sub>CY/60</sub> - 70 ns          |

| t <sub>RDR</sub> | Data Hold from RAM RD     |                               | 01700                                  |

| twFi             | FIFO In Clock Width       | 12 t <sub>CY/60</sub> - 40 ns |                                        |

| tww              | RAM WR Strobe Width       | 8 t <sub>CY/60</sub> - 27 ns  | ·                                      |

| t <sub>AW</sub>  | Address Setup to RAM WR   | 10 t <sub>CY/60</sub> - 90 ns |                                        |

| t <sub>DW</sub>  | Data Setup to RAM WR      | 2 t <sub>CY/60</sub> - 30 ns  |                                        |

| t <sub>WD</sub>  | Data Hold from RAM WR     | 2 t <sub>CY/60</sub> - 20 ns  | · · · · · · · · · · · · · · · · · · ·  |

\*Remain I/O OUTPUT if External ROM not used.

\*\*I/O Data input or 2nd ROM byte of 2 byte instruction. Otherwise remain I/O OUTPUT.

TL/DD/5526-6

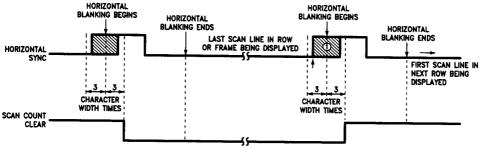

Scan Count Clear Timing

For external character generation this edge is used to clock CLEAR into scan line counter. The edge must come before Scan Count Clear goes away, but not before the video controller has brought in all necessary display information for the last scan line.

| 1.0 I        | Functional Pin Descriptions                            |                                                                                                                                                   |

|--------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|              | PPLIES                                                 |                                                                                                                                                   |

| Pin          | Name                                                   | Function                                                                                                                                          |

| 48           | V <sub>CC</sub> — Power                                | 5V ± 10%                                                                                                                                          |

| 24           | V <sub>SS</sub> — Ground Reference                     |                                                                                                                                                   |

| 1.2 IN       | PUT SIGNALS                                            |                                                                                                                                                   |

| 23, 22<br>29 | XTAL1, XTAL2 — Crystal 1, 2:<br>EA — External Access:  | Crystal connections for clock oscillator (3–18 MHz). Pull HIGH $(V_{IH_2})$                                                                       |

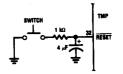

| 32           | RESET                                                  | An active low input that initializes the processor. The RESET input is also used for internal ROM verification.                                   |

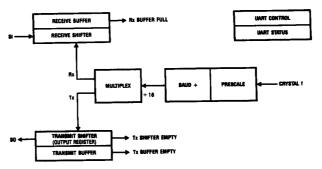

| 34           | SI — Serial Input:                                     | Drives receiver section of UART (true data).                                                                                                      |

|              | TPUT SIGNALS                                           | brives receiver section of OART (true data).                                                                                                      |

| 33           | SO — Serial Output:                                    | Driven by transmitter section of UART (true data).                                                                                                |

| 21           | ALE — Address Latch Enable:                            | ROM address is available on the ROM Expand Bus and may be latched                                                                                 |

|              |                                                        | on the falling edge of ALE. Port output data may be latched on the rising edge of ALE. ALE pulses are always present, even if EA is tied low.     |

| 30           | PSEN — Program Store Enable:                           | Enable external ROM output drivers when low. PSEN is idle (high) when                                                                             |

| 31           | RD — Read Port Data:                                   | the CPU fetches from internal ROM.                                                                                                                |

| 31           | nd — Read Port Data:                                   | Accept Port input data on ROM Expand Bus RE0-RE7 while low. ROM Expand Bus is in high impedance state while RD is low.                            |

| 28           | HS — Horizontal Sync                                   | The rising edge of HS is controlled by the Horizontal Sync Begin Register                                                                         |

|              |                                                        | and the falling edge is controlled by the Horizontal Sync End Register. HS is disabled (low) if bit 5 of the Video Control Register = 0.          |

| 27           | VS — Vertical Sync Output:                             | The falling edge of VS is controlled by the Vertical Sync Begin Register                                                                          |

|              |                                                        | and the rising edge is controlled by the Vertical Sync End Register. $\overline{VS}$ is at TRI-STATE if bit 5 of the Video Control Register = 0.  |

| 26           | VO — Video Output:                                     | High = beam on, low = beam off. VO is disabled (low) if bit 5 of the                                                                              |

| 25           | INTENS/FO CLK                                          | Video Control Register = 0. (Shared pin) INTENS Signal under attribute control may be used to switch                                              |

|              |                                                        | the bistable brightness of display characters.                                                                                                    |

|              |                                                        | FIFO Out Clock may be used to clock data from an external FIFO in<br>synchronism with data from the internal FIFO.                                |

|              |                                                        | Both CANNOT be used simultaneously.                                                                                                               |

| 17           | VID CLK/FI CLK — Video Dot Clock Out/<br>FIFO IN CLOCK | (Shared pin) The rising edge of the Video Dot Clock may be used to clock the data out of the video output pin. FIFO In Clock may be used to clock |

|              |                                                        | data from an extended attribute RAM into an external FIFO in                                                                                      |

|              |                                                        | synchronism with the data loaded into the internal FIFO.                                                                                          |

|              |                                                        | Both CANNOT be used simultaneously.                                                                                                               |

| 18           | RAM ALE — RAM Address Latch Enable:                    | RAM address is available on the System Bus and may be latched on the                                                                              |

|              |                                                        | falling edge of RAM ALE. Only operational when Display RAM accesses                                                                               |

|              |                                                        | being performed. Otherwise high.                                                                                                                  |

| 20           | RAM RD — RAM Read:                                     | Enable display RAM data onto the System Bus when RAM RD is low.                                                                                   |

| 19           | RAM WR — RAM Write:                                    | Data to RAM is available on the System Bus and may be written at the                                                                              |

| 1.4 BUS      | s—1/0                                                  | rising edge of RAM WR.                                                                                                                            |

| 1-8          | SB0-SB7 — System Bus 0-7:                              | Display PAM address is subsubushile DAMA ALE in bight and and                                                                                     |

|              | oso osi oyalam busu-1.                                 | Display RAM address is output while RAM ALE is high and may be latched on the falling edge of RAM ALE. System Bus accepts data input              |

| 9-16         | SB8-SB15 — System Bus 8-15:                            | while RAM RD is low and outputs data while RAM WR is low.  Normally, Display RAM address is output and held on these pins for the                 |

|              |                                                        | full read or write cycle. However, if bit 4 of the System Control Register is                                                                     |

|              |                                                        | set, these pins function bidirectionally like SB0-SB7 to allow 16-bit data words for attribute operation.                                         |

| 35-47        | RE0-12 — ROM Expand Bus 0-12:                          | Used for program ROM expansion as described below. Time multiplexed                                                                               |

|              |                                                        | with I/O port and system control signals. I/O port and system control signals only if no external ROM used.                                       |

| 40-47        | RE0-RE7                                                | Low order ROM address is output and may be latched on the falling edge                                                                            |

|              |                                                        | of ALE. Enable ROM data to this Bus when PSEN is low. Enable I/O port                                                                             |

|              |                                                        | input data to the Bus when $\overline{\text{RD}}$ is low. Use the rising edge of ALE to latch port output data.                                   |

|              |                                                        |                                                                                                                                                   |

| Pin   | Name                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39-35 | RE8-RE12                        | Five most significant bits of the ROM address are output during ALE and remain stable until data is read in during PSEN. These pins are multiplexed with the HLDA, INTR, LP, SC CLR, and HOLD signals.                                                                                                                                                                                                                                                                 |

| 37    | INTR — Interrupt: RE10          | An active low input that interrupts the processor if the external interrupt is enabled. Because it shares a pin with RE10, INTR may be driven directly only if no external ROM is used (EA is low). Otherwise must be driven through a 3.9k resistor.*                                                                                                                                                                                                                 |

| 38    | □P — Light Pen Interrupt: RE9   | An active low input that interrupts the processor if internal interrupts are enabled and bit 5 in the Interrupt Mask Register is set. Because it shares a pin with RE9, LP may be driven directly only if EA is low. Otherwise, must be driven through a 3.9k resistor.*                                                                                                                                                                                               |

| 39    | HOLD — HOLD request: RE8        | When high, requests that the NS405 enter the Hold mode. When in the Hold mode the System Bus will be in a high impedance state. The Hold mode is granted at the beginning of the next vertical retrace. Because it shares a pin with RE8, HOLD may be driven directly only if EA is low. Otherwise, must be driven through a 3.9k resistor.*                                                                                                                           |

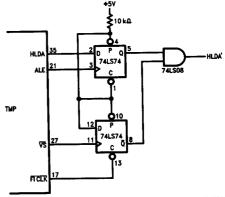

| 35    | HLDA — Hold Acknowledge: RE12   | This output is asserted in response to Hold and provides handshake capability with another processor (active high). For more detailed information see Section 3.0 Slave Processing. Because HLDA shares a pin with RE12, the HLDA state is preset only during the interval preceding the rising edge of ALE. However, if no external ROM is used, HLDA is a steady state output and need not be latched externally.                                                    |

| 36    | SC CLR — Scan Count Clear: RE11 | This output clears an external scan counter when used with an external character generator. It is a low going pulse which occurs during the horizontal retrace preceding the first scan line of each character row. Because SC CLR shares a pin with the RE11, the correct SC CLR state is present only during the interval preceding the rising edge of ALE. However, if no external ROM is used, SC CLR is a steady state output and need not be latched externally. |

<sup>\*</sup>Unused control inputs must be terminated

# 2.0 Functional Description

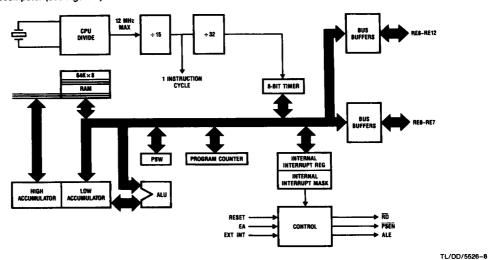

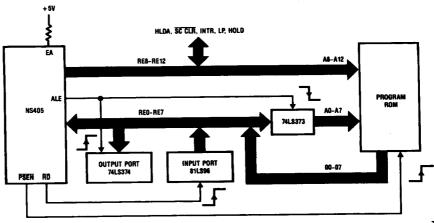

The CPU of the NS405 is patterned after the 8048 single chip microcomputer (see *Figure 1*).

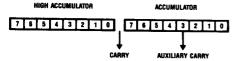

### 2.1.1 Accumulator — High Accumulator

In addition to the regular 8-bit Accumulator, there is an 8-bit High Accumulator extension to facilitate the 16-bit operations required for display memory management. The HACC/ACC pair is usually used in conjunction with the 16-bit RAM pointer registers (RA, R0 and RB, R1, CURSOR, HOME, BEGD and ENDD) to effect video data transfers. In addition, external attribute memory is loaded in a 16-bit transfer operation. Any instruction which causes a carry or borrow out of the low accumulator will affect the high accumulator (see Figure 2).

Auxiliary carry is used only when converting the accumulator contents from binary to BCD (binary coded decimal) using the DA A instruction. The auxiliary carry flag can be cleared by moving a zero into bit 6 of the program status word.

TL/DD/5526~9

FIGURE 2. CPU Accumulator

# 2.1.2 Program Counter (PC)

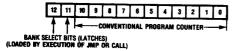

The Program Counter is a 13-bit wide register which provides program addressing for the CPU. The lower 11 bits operate like a conventional program counter while the upper 2 bits are actually latches. These 2 latches are automatically loaded from the bank select flip-flops (PSW bits 3, 4) whenever a JMP or CALL instruction is executed. The bank select flip-flops in turn are only modified upon the execution of a Select Memory Bank Instruction or modification of the PSW (see Figure 3).

TL/DD/5526-10

# FIGURE 3. TMP Program Counter

# 2.1.3 Program Memory

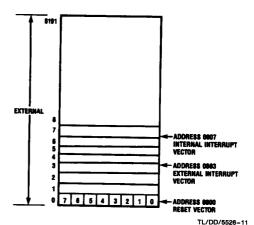

Memory is subdivided into 2k banks with accesses limited to the currently selected bank unless a Bank Change sequence has been executed. Upon reaching the end of a memory bank, the program counter will wrap around and point to the beginning of the current bank.

Each bank is further subdivided into pages of 256 bytes each, with 8 pages in every bank. The conditional JUMP instructions are restricted to operate within the memory page that they reside in.

Because of the sequence which the CALL instruction executes when pushing and loading the PC, it is possible to easily call and return from subroutines located in different memory banks (see *Figure 4*).

Upon executing an RET or RETR instruction for a call from one memory bank into another, a SEL MBx instruction should be excuted to restore the memory bank select flipflops to their original bank. However, no SEL MBx is needed after an interrupt since the flip-flops were never modified.

FIGURE 4. Program Memory Map

# 2.1.4 Program Status Word Bit Assignments

| Bit<br>Position | Contents                                                                                                                        |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| 0               | Stack Pointer Bit, S0                                                                                                           |

| 1               | Stack Pointer Bit, S1                                                                                                           |

| 2               | Stack Pointer Bit, S2                                                                                                           |

| 3*              | Memory Bank Select Bit 0                                                                                                        |

| 4*              | Memory Bank Select Bit 1                                                                                                        |

| 5*              | Register Bank Select Bit (0 = Bank 0, 1 = Bank 1)                                                                               |

| 6*              | Auxiliary Carry. A carry from Bit 3 to Bit 4 generated by an add operation. Used only by the decimal adjust (DA A) instruction. |

| 7*              | Carry. A bit indicating the preceding operation resulted in an overflow or an underflow from the 8-bit accumulator.             |

\*Note 1: Bits 3 through 7 are saved on the stack by subroutine calls or interrupts. Bits 3 and 4 are restored upon execution of an RET instruction, whereas all 5 bits are restored by RETR.

Note 2: F0 is not saved on the stack (as in an 8048).

Note 3: Bits 0-5 cleared on a RESET.

### 2.1.5 Stack Pointer (SP)

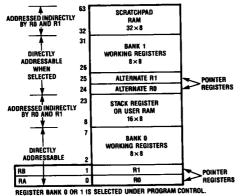

The stack pointer is an independent 3-bit counter which points to designated locations in the internal RAM that holds subroutine return parameters. The stack itself is located in RAM locations 8-23 (see *Figure 5*).

Each entry in the stack takes up two bytes and contains both the PC and status bits. When reset to zero, the stack pointer actually points to locations 8 and 9 in RAM. Since the stack pointer is a simple up/down counter, an overflow will cause the deepest stack entry to be lost (the counter overflows from 111 to 000 and underflows from 000 to 111).

overflows from 111 to 000 and underflows from 000 to 111).

Note: If the level of subroutine nesting is less than eight (8), the unneeded stack locations may be used as RAM.

| POINTER      | LOCATION |   |     |     |   |   |     |    |     |   |   |

|--------------|----------|---|-----|-----|---|---|-----|----|-----|---|---|

|              | 9        |   | 2   | C8- | ı |   |     | -7 | 5W3 | P |   |

| 000          | 8        |   | 1-3 | PC  |   |   | 4-7 | PC |     |   |   |

| TL (DD (550) |          | 0 | 1   | 2   | 3 | 4 | 5   | 6  | 7   | 8 | 9 |

Note: The odd numbered RAM bytes in the stack area have two (2) extra bits to allow for storage of the bank select switch bits. This feature allows interrupt routines and subroutines to be located outside the current 2k program memory bank.

FIGURE 5. Typical Stack Composition

### 2.1.6 Data Memory (On-Chip RAM)

The data memory nominally consists of 64 8-bit locations and is utilized for working registers, the subroutine stack, pointer registers and scratch pad. There are two sets of working/pointer registers (R0-R7) which are selected by the Select RAM Bank instruction. The stack area is located in locations 8-23. Locations 32-63 contain the scratch pad memory. To facilitate 16-bit Video Memory Management there are two 8-bit extension registers (RA and RB) which are associated with the R0 and R1 registers respectively of whichever RAM bank is currently selected (see *Figure* 6). i.e., There is only one RA register and only one RB register.

TL/DD/5526-13

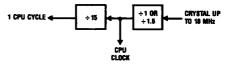

### 2.1.7 Timer

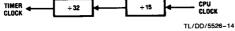

The On-Board Timer is an 8-bit up counter which sets the Timer Overflow Flag and generates an internal interrupt (if enabled) whenever it overflows from FF to zero. The Timer may be stopped, started, loaded and read from by the CPU. The Timer clock is derived from the CPU clock as shown in Figure 7. Whenever a Start Timer instruction is executed the  $\div$  32 is initialized to its zero state to insure a full count measurement. After overflow the timer keeps counting until the next FF to zero overflow at which time the overflow flag will be set and another interrupt generated. The overflow flag can only be reset through the JTF and JNTF instructions.

FIGURE 7. Timer Clock Generation

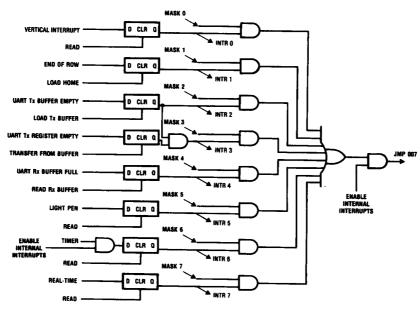

### 2.1.8 Interrupts

The interrupt circuitry handles two generic classes of interrupt conditions called Internal and External. Either class has its own master control which can be activated through software enable and disable instructions. On an interrupt service the currently executing instruction is completed, then two CPU cycles are used as the program counter and bits 3–7 of the PSW are pushed onto the stack and stack pointer is incremented.

Then the interrupt vector address (3 or 7) is loaded into the PC and service started. Whenever an interrupt condition is being serviced all other interrupts of either class are locked out until a RETR instruction is executed to conclude interrupt service. If both an external and internal interrupt arrive at the same time, the external interrupt is recognized first.

### 2.1.8.1 External Interrupt

The External Interrupt consists solely of the shared INTR/RE10 pin. External interrupts on this pin will be detected if the setup and hold times as shown in the timing diagrams are met. This pin is a level sampled interrupt which means that as long as the pin is low during the sampling window an interrupt will be generated. In addition, the INTR pin is the only external pin whose logic state can be directly tested through software.

### 2.1.8.2 Internal Interrupts

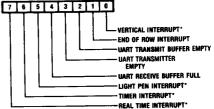

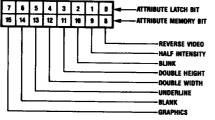

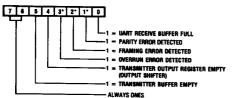

The Internal Interrupts consist of seven internal operational conditions plus the light pen arranged in an 8-bit wide register as shown in Figure 8. Activation of an internal interrupt condition causes a corresponding register bit to be set, Figure 9. Each internal interrupt may be individually masked out through the Interrupt Mask register which has the same bit assignments as the Interrupt register and can be loaded from the accumulator. A zero in the Interrupt Mask register inhibits the interrupt and a one enables it. Further interrupt processing is as shown. To determine which of the eight internal conditions caused the interrupt the CPU must read the Interrupt register into the accumulator. To acknowledge receipt of the interrupt certain bits are automatically cleared on a read while others are reset upon service of the particular interrupt.

The conditions under which each of the interrupts are generated and cleared are as follows:

TI /DD/5526-16

Note: The interrupt flags indicated by an asterisk (\*) are cleared when the Interrupt Register is read.

### FIGURE 8. Internal Interrupt Register

### Bit

O Vertical Interrupt—Generates an interrupt at the end of the display row designated by the Vertical Interrupt Register. Interrupt bit cleared on a CPU read of the interrupt register. If VIR > Vertical Length Register no interrupt will be generated.

FIGURE 9. internal interrupt Processing

TL/DD/5526-15

### Bit

- 1 End of Row Interrupt—Generates an interrupt at the end of each display row when the Current Row Start Register is updated for the next row. Used in conjunction with the Row Sequencing Control Bit (5) in the System Control Register to implement Row Pointer Look-Up Tables and Horizontally Split Screens. Interrupt bit cleared on a CPU write to the Home Register. Does not generate interrupts for those rows blanked during vertical blanking.

- 2 UART Transmit Buffer Empty—Generates an interrupt when the Transmit Buffer empties out after dumping a character into the Transmit Shift Register. Interrupt bit cleared on a CPU write to the Transmit Buffer.

- 3 Transmitter Empty—Generates an interrupt when BOTH the Transmit Buffer and Transmit Shift Register are empty. The interrupt bit is cleared when the CPU loads the transmit buffer.

- 4 UART Receiver Buffer Full—Generates an interrupt when the Receiver Buffer fills up with a character from the Receive Shift Register. Interrupt bit cleared on a CPU read of the Receiver Buffer.

- 5 Light Pen Interrupt—Generates an interrupt on each falling edge detected on the shared LP/RE9 pin. Since only falling edges generate interrupts and the input is sampled each CPU Cycle, a high level must be sampled between falling edges in order to be considered a new interrupt. This interrupt is used to latch the light pen position registers. For further information see Light Pen Description. Interrupt bit cleared on a CPU read of the interrupt register.

### Bit

- 6 Timer Interrupt—Generates an interrupt when the internal 8-bit Timer overflows from FF to 00. Interrupt bit cleared on a CPU read of the interrupt register.

- 7 Real-Time Interrupt—Generates interrupts at a software programmable frequency that is generally in the Hertz range. (See CPU Clock Generation.) Thus permitting the implementation of a real-time clock or timer. Interrupt bit cleared on a CPU read of the interrupt register.

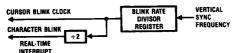

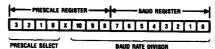

### 2.1.9 Clock Generation

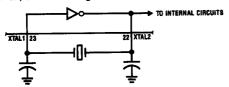

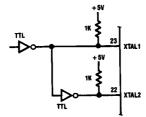

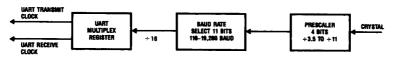

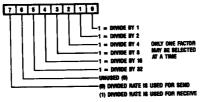

All chip clocks are derived from the one external crystal connected between pins 22 and 23. This master clock also doubles as the video dot clock. The crystal frequency is constrained to lie within the range of 3 to 18 MHz. The CPU clock is derived from the crystal clock by either using it directly or by dividing down by a factor of 1.5 (Figure 10).

TL/DD/5526-17

# FIGURE 10. CPU Clock Generation

The choice is software programmable through bit 0 in the System Control Register. The exact selection is made in consideration of the fact that the CPU clock must lie within the range of 3 to 12 MHz. In addition, the choice of divide by modes will also impact the display character cell width due to the nature of the video controller. Specifically with  $\div 1.5$

the cell width must be  $\geq 8$  dots wide whereas with  $\div 1$  the cell width must be  $\geq 6$  dots wide.

The low clock rates necessary to implement Cursor Blinking, Character Blinking and the Real-Time Interrupt are derived by passing the vertical sync frequency through a 5-bit Blink Rate Divisor Register, (Figure 11). The resultant frequency is used as the Cursor Blink Clock. This clock is then further divided by 2 to yield the Character Blink and Real-Time Interrupt Clocks. For example, to get a 1 Hz real time interrupt, with a 60 Hz system, set the 5 bit Divisor Register to 30 in order to yield a 2 Hz signal which is then divided by

TL/DD/5526-18

FIGURE 11. Blink Clock Generation

# 2.1.10 Oscillator Operation

The on-board oscillator circuit consists of a phase inverter which, when used with an external parallel resonant tank, (Figure 12a), will yield the required oscillator clock. Crystals should be specified for AT cut and parallel resonant operation with the desired load capacitance (typically 20 pF). If one desires to externally generate the clock and input it to the chip, he may do so by driving XTAL1 (pin 23) and XTAL2 (pin 22) as shown in Figure 12b.

TL/DD/5526-19

FIGURE 12a. TMP Oscillator

TI /DD/5526-20

Note: Use AS TTL devices if faster than 12 MHz.

# FIGURE 12b. External Oscillator Mode

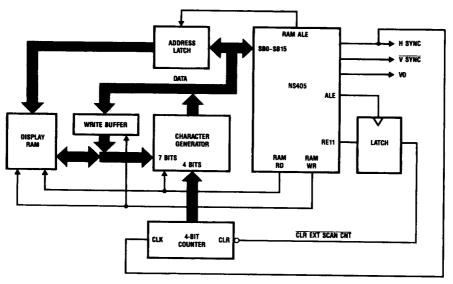

### 2.2 DISPLAY MEMORY CONTROLLER

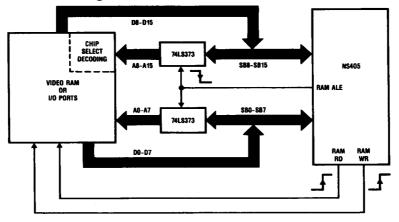

The video display data resides in the external Video Memory which is managed by the Display Memory Controller (DMC) through the System Bus. Either the CPU or the Video Controller may access the display memory by presenting its requests to the DMC. A maximum of three Video Memory accesses (Reads or Writes) can be performed by the DMC during each CPU instruction execution cycle. Because the CPU can access the Video Memory, one may expand CPU I/O or data memory by memory mapping into the Video

Memory space. Up to 64k locations may be addressed over the 16-bit System Bus. Data word widths may be 8 or 16 bits depending upon whether external character attribute selection is used. The actual bus multiplexing mode is controlled by bit 4 in the System Control register. The Video Controller has the highest priority in obtaining Video Memory accesses with the CPU getting in on a space available basis. If all memory accesses are being taken by the Video Controller (rarely), the CPU is put into a wait state should it try to access video memory. To ease accessing requirements and boost throughput the Video Controller utilizes a 4-level data FIFO which is normally kept full of display data.

# 2.2.1 Display Memory Control Registers

In order to facilitate the management of video data for such features as a Screen scroll, memory paging and row lookup the DMC utilizes a number of registers which address the video RAM space. Each of these pointers is 16 bits wide and writable or readable from the 16-bit HACC/ACC pair as the case may be. There are 2 video data accessing modes as determined by bit 5 in the SCR, Sequential and Table Lookup. The functions of the pointer registers vary depending upon the accessing mode selected. Their designators are:

HOME = Home address register. Read and write.

BEGD = Beginning of diplay RAM. Write only.

ENDD = End of display RAM. Write only.

CURS = Cursor address register. Read, Write, Increment, Decrement.

SROW = Status section register. Write only.

CRSR = Current row start register. Not directly accessed.

### 2.2.2 Sequential Access Mode

In this mode display data is accessed from sequential address locations in the video memory until the data requirements for the current screen field are fulfilled. The location from which the first display character is taken is the one pointed to by the HOME register. By modifying the contents of HOME one may implement a row scroll or paging operation. The BEGD and ENDD are used to control the wraparound condition when HOME gets near the end of available display RAM as determined by ENDD. In this instance, when sequential accessing brings us to the end of memory as pointed to by ENDD, the controller wraps around by jumping back to the beginning of display memory as pointed to by BEGD. The value in ENDD should be the last location in display memory + 1. Also the size of the display memory between BEGD and ENDD (ENDD - BEGD) must be an integral number of display rows. The CURS in both accessing modes merely identifies the current cursor position in display memory so that the cursor characteristics can be inserted into the video at the appropriate character position. In addition to the display of normal video data one may elect to have a special status section displayed using data from a separate section of video memory. The status section would consist of an integral number of display rows on the bottom of the screen. This feature operates by reloading the video RAM pointer with the contents of SROW when the desired row position at which to start the status section comes up. The particular row at which the status display starts is defined in the Timing Chain. Once the video RAM pointer is jumped to SROW, data accessing again proceeds sequentially from there until the data requirements for the current field are satisfied.

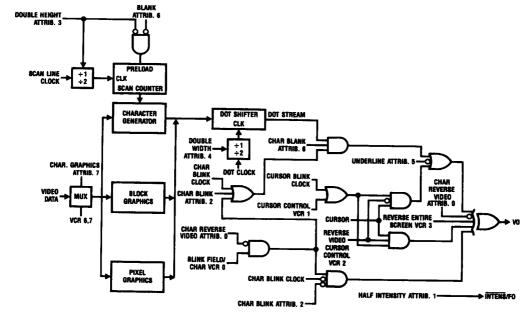

# PEM LIGHT PEN DETECTION CHARACTER GENERATOR CHARACTER GENERATOR CHARACTER GENERATOR ATTRIBUTE VIDEO OUTPUT GRAPHICS CONTROLLER VIDEO OUTPUT PIXEL GRAPHICS

TL/DD/5526-21

Whether a status section is used or not, upon accessing all of the data necessary to display a field, the video RAM pointer is reset to HOME in preparation for the display of a new field.

### 2.2.3 Table Lookup Mode

The CRSR (transparent to the user) is a pointer to the address of the first character in a display row. It is required because each time a scan line is displayed, all display characters in the row must be accessed anew. Since a row is made up of a number of scan lines, we must recover the address of the first character in the row for each scan in the row. After a row is done, the CRSR is normally advanced to point to the first character in the next row.

In table look-up mode the starting memory location of the next row is loaded into the CRSR from the HOME register at the end of each row. The HOME register was presumably updated by the CPU since the last end of row.

A CRSR load also generates the internal End of Row interrupt which the CPU will use as a signal to reload HOME. Finally, reloading HOME will clear out the End of Row interrupt. If the status section feature is used, upon reaching the begin status row location the CRSR will be loaded with SROW instead of HOME for that row. After which CRSR will revert back to load from HOME for the remaining rows on the screen.

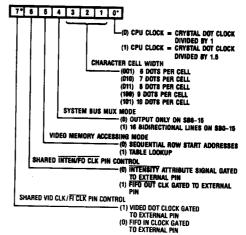

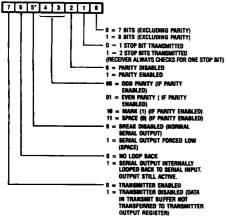

### 2.3 SYSTEM CONTROL REGISTER

Through the System Control Register (SCR) the user specifies several important chip operational conditions. It is an 8-bit write only register which is loaded from the CPU accumulator.

TL/DD/5526-22

\*Bit 0 is set to 1 by RESET and bit 7 is set to 0 by RESET.

# FIGURE 13. System Control Register

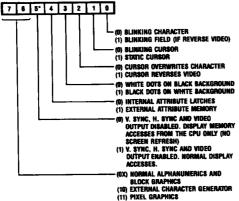

# 2.4 VIDEO CONTROL REGISTER

Through the Video Control Register (VCR) the user specifies several video display features to the chip. It is an 8-bit write only register which is loaded from the CPU accumulator.

7

TL/DD/5526-23

\_ .\_\_ .\_\_

\*Bit 5 is set to 0 by RESET.

FIGURE 14. Video Control Register

# 2.5 CRT REFRESH LOGIC

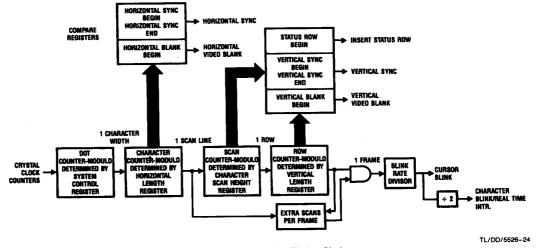

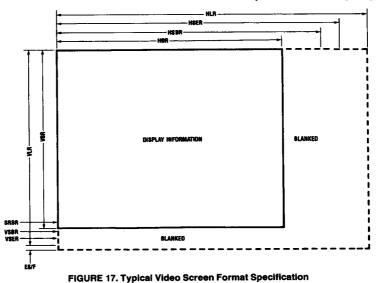

All video timing and clocking signals are derived from a series of counters and comparators called the Video Timing Chain. The chain is driven by the dot/crystal clock and ultimately divides down to the very slow blink clock, (Figure 15). By having the program initialize the registers in the chain a user may specify all aspects of video generation.

The chain also controls the size and placement of the cursor and underline attribute within a character cell as well as the cell partitioning for block graphics display. All totaled, the chain consists of 14 wire only registers. They are loaded indirectly by using the Timing Chain Pointer (TCP), a 4-bit pointer to registers in the chain, and the MOV @TCP, A instruction.

FIGURE 15. TMP Video Timing Chain

### 2.5.1 TMP Timing Chain Registers

### TCP

### **Horizontal Timing**

- 0 Horizontal Length Register HLR 7 bits

- Total number of character cells in a horizontal scan and retrace.

- Enter desired count 1

- Horizontal Blank Begin Register HBR 7 bits (Characters/Row)

- Character position in horizontal scan after which horizontal blanking begins.

- Enter desired number of displayed characters/row 1.

- 2 Horizontal Sync Begin Register HSBR 7 bits

- Character position in horizontal scan after which horizontal sync begins (rising edge), HSBR ≤ HLR.

- Enter desired count + 2.

# 2.5.1 TMP Timing Chain Registers (Continued)

| 2.5.1 TN        | IP Timing Chain Registers (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCP             | Horizontal Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3               | Horizontal Sync End Register — HSER 7 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 | — Character position in horizontal scan after which horizontal sync ends (falling edge), HSER ≤ HLR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                 | — Enter desired count + 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Note: The       | polarity of the horizontal sync signal can be inverted by switching the values in the two horizontal sync registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TCP             | Character Height Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

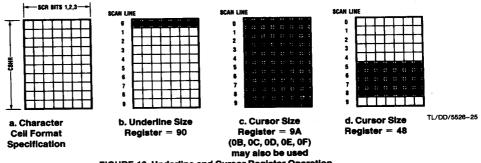

| 4               | Character Scan Height Register — CSHR 4 bits (see Figure 16a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| High            | — Scan line height of a character cell.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Nibble          | Enter desired number of scan lines 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| . 4             | Extra Scans/Frame — ES/F 4 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Low             | Number of extra scans to be added to a frame if desired.    The desired are the second of the s |