# H1853 H1853C

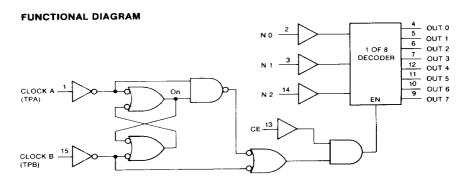

1800 CMOS Microprocessor Family N-Bit 1 of 8 Decoder

#### MICROELECTRONICS CENTER

#### DESCRIPTION

Hughes 1853 allows decoding of the 1802A microprocessor generated I/O lines (N0-N2) to provide direct control for up to seven input and seven output devices. The TPA and TPB clock inputs provide control signal output timing while the Chip Enable (CE) input allows multi-level I/O expansion for decoding. The 1853 can also be used as a general 1 of 8 decoder for memory system applications.

The 1853 operates over a 4-10.5 voltage range while the 1853C operates over a 4-6.5 voltage range. The 1853 is available in a 16 lead hermetic dual-in-line ceramic package (D suffix), plastic package (P suffix), or cerdip (Y suffix). Devices in chip form (H suffix) are available upon request. form (H suffix) are available upon request.

#### **FEATURES**

- Static Silicon Gate CMOS Circuitry

- Interfaces Directly with 1802A Microprocessor without Additional Components

- Provides Control for up to 7 Input and 7 Output Devices

- · Low Power Dissipation

- Easy Expansion for Multi-Level I/O Systems through Chip Enable.

- · Buffered Inputs and Outputs

- · Strobed Outputs for Spike-Free Decoding

#### PIN CONFIGURATION

# **ABSOLUTE MAXIMUM RATINGS**

| Operating Temperature Range (TA)                |                    |

|-------------------------------------------------|--------------------|

| Ceramic Package                                 | -55 to + 125°C     |

| Plastic Package                                 | -40 to + 85°C      |

| DC Supply-Voltage Range (VDD)                   |                    |

| (All voltage values referenced to VSS terminal) |                    |

| 1853                                            | -0.5 to + 13 Volts |

| 1853C                                           | -0.5 to + 7 Volts  |

| Input Voltage Range                             | Vss -0.3V to       |

|                                                 | $V_{DD} + 0.3V$    |

| Storage Temperature Range (Tstg)                | -65 to + 150°C     |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### OPERATING CONDITIONS at $T_A = -55$ to +125°C, $V_{DD} = \pm 5\%$

| T ZIMI MIG COMBANICATION I                          |          |         | · •, • •  |           |          |            |       |      | CONTRACTOR ROSS |     |

|-----------------------------------------------------|----------|---------|-----------|-----------|----------|------------|-------|------|-----------------|-----|

|                                                     |          |         |           |           |          |            |       |      |                 | 47  |

|                                                     |          |         | Hansi.    |           |          |            |       |      | 1. 4            | 611 |

| Supply-Voltage Range                                | _        | _       |           | 4         | _        | 10.5       | 4     | _    | 6.5             | v   |

| Recommended Input Voltage Range                     | _        | _       | _         | vss       | _        | VDD        | vss   | _    | VDD             | ٧   |

| Static Electrical Characteristics at TA =           | 55°C to  | 125°C L | Inless Of | herwise : | Specifie | d          | -     |      |                 |     |

| Quiescent Device Current, IL4                       |          |         | 5         | _         | 1        | 10         | - T   | 5    | 50              |     |

|                                                     |          | _       | 10        | _         | 10       | 100        | -     | _    | _               | μА  |

| Output Low Drive (Sink) Current, IOL                | 0.4      | 0,5     | 5         | 1.6       | 3.2      | <u> </u>   | 1.6   | 3.2  | _               | 4   |

|                                                     | 0.5      | 0,10    | 10        | 2.6       | 5.2      | _          | _     | _    | _               | mA  |

| Ouput High Drive (Source Current), IOH              | 4.6      | 0,5     | 5         | -1.15     | -2.3     | <u> </u>   | -1.15 | -2.3 | _               | A   |

|                                                     | 9.5      | 0,10    | 10        | -2.6      | -5.2     |            |       | _    | _               | mA  |

| Output Voltage Low-Level, VOL 1,3                   | _        | 0,5     | 5         | _         | 0        | 0.1        | _     | 0    | 0.1             |     |

|                                                     | -        | 0,10    | 10        | _         | 0        | 0.1        | _     | _    | _               |     |

| Output Voltage High Level, VOH 3                    | -        | 0,5     | 5         | 4.9       | 5        | -          | 4.9   | 5    |                 | ٧   |

|                                                     | _        | 0,10    | 10        | 9.9       | 10       | -          | -     | _    | _               |     |

| Input Low Voltage, VIL                              | 0.5, 4.5 | _       | 5         | _         | -        | 1.5        | -     | _    | 1.5             |     |

|                                                     | 1,9      | _       | 10        | _         |          | 3          | _     | _    |                 |     |

| Input High Voltage, V <sub>IH</sub>                 | 0.5, 4.5 | _       | 5         | 3.5       | _        | _          | 3.5   | _    | _               | \ \ |

|                                                     | 1,9      | _       | 10        | 7         | -        | _          | _     | -    | _               |     |

| Input Leakage Current, I <sub>IN</sub> <sup>4</sup> | Any      | 0,5     | 5         | _         | -        | ±1         | -     | _    | <u>±</u> 1      | _   |

|                                                     | Input    | 0,10    | 10        |           |          | <u>±</u> 1 | -     | -    |                 | μА  |

| 3-State Ouput Leakage Current, IOUT 4               | 0,5      | 0,5     | 5         | _         |          | ±1         | _     | -    | ±1              |     |

|                                                     | 0,10     | 0,10    | 10        | _         | -        | ±1         | _     | 1    | _               | μA  |

| Operating Current I <sub>DD1</sub> <sup>2,4</sup>   | 0,5      | 0,5     | 5         | _         | 50       | 500        |       | 50   | 100             |     |

|                                                     | 0,10     | 0,10    | 10        | _         | 150      | 1000       | _     | _    | _               | μΑ  |

| Input Capacitance, C <sub>IN</sub> <sup>3</sup>     | -        | _       |           | -         | 5        | 7.5        | _     | 5    | 7.5             | ρF  |

| Output Capacitance, COUT∞                           | _        |         | =         | _         | 10       | 15         | _     | 10   | 15              | рF  |

<sup>\*</sup>Typical values are for  $T_A = +25$ °C and nominal voltage.

NOTE 1: IOL = IOH = 1 uA

NOTE 2: Operating current measured in a 1802A system at 2MHz with outputs floating.

NOTE 3: Design assured but not tested.

NOTE 4: Parameters guaranteed by other tests at -55°C.

#### OPERATING CONDITIONS, cont

#### H 1853/1853C

| Silve to tenspies "                               |                                                  |          |        | Hit     |     |          |        |          | iai ka |     |

|---------------------------------------------------|--------------------------------------------------|----------|--------|---------|-----|----------|--------|----------|--------|-----|

| A CHARLET PHO                                     |                                                  | <b>L</b> |        |         |     |          |        |          | Ž., 28 |     |

| Dynamic Electrical Characteristics                | at $T_A = -55$                                   | to +125° | C, CL= | 50pF, V |     | %, VIH = | VDD, V | IL = VSS | ·      |     |

| Propogation Delay Time:                           | -                                                |          | 5      | _       | 175 | 275      |        | 175      | 275    | ns  |

| CE to Output, tFOH, tEOL                          |                                                  | _        | 10     |         | 90  | 150      |        | _        |        |     |

| N to Outputs, t <sub>NOH</sub> , t <sub>NOL</sub> |                                                  | _        | 5      |         | 225 | 350      | _      | 225      | 350    | ns  |

|                                                   |                                                  |          | 10     |         | 120 | 200      |        | -        | _      |     |

| Clock A to Output, t <sub>AO</sub>                | _                                                | _        | 5      |         | 200 | 300      |        | 200      | 300    | n   |

|                                                   | _                                                |          | 10     | _       | 100 | 150      |        | _        | _      |     |

|                                                   | <del>                                     </del> | _        | 5      | _       | 175 | 275      |        | 175      | 275    | ns  |

| Clock B to Output, t <sub>BO</sub>                |                                                  | _        | 10     |         | 90  | 150      | _      | _        | . –    | ]   |

| Minimum Pulse Widths:                             |                                                  |          | 5      | _       | 50  | 75       |        | 50       | 75     |     |

| Clock A, t <sub>CACA</sub>                        | -                                                | _        | 10     | _       | 25  | 50       | _      |          | _      | ] , |

| Clock B, t <sub>CBCB</sub> C8                     |                                                  | <u> </u> | 5      |         | 50  | 75       |        | 50       | 75     | ]   |

|                                                   | =                                                |          | 10     |         | 25  | 50       | _      |          | _      | 1   |

<sup>\*</sup>Typical values are for TA = 25°C and nominal voltage

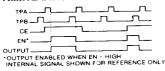

#### TIMING DIAGRAMS

# PROPOGATION DELAY TIMING:

# APPLICATIONS EXAMPLES

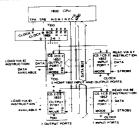

The Figure shows two 1853 used to decode 4K address into 16 groups of 256 address each.

MA 8 represents the 8th binary address bit.

(i.e. 28 = 256)

M 0 will address 0-255

M 1 will address 256-511

M 15 will address 3840-4095

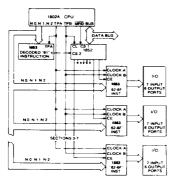

In the 1802A microprocessor systems, when more than three I/O ports are required, the N lines can be decoded to specify up to 7 different input and 7 different output channels as shown.

By executing Input instruction 69 (N lines = 001) for instance, the port 1 input register is enabled to the bus since MRD is high during the memory write cycle. The 1853 decode line 1 will also be active high during an output instruction, 61 (N lines = 001) but MRD is low during the memory read cycle disabling the memory read cycle disabling the port 1 input register from the bus. At TPB, the valid byte from memory is strobed into the port 1 output register.

### **ADDRESS DECODER:**

# ONE LEVEL I/O SYSTEMS:

#### TWO LEVEL I/O SYSTEMS

In the 1802A microprocessor systems, when more than 7 input or 7 output ports are required, a two level I/O system can be designed as shown in the figure.

A 61 (N lines = 001) output instruction is first executed to place an 8-bit device selection code in the I/O device-select register, 1852. Subsequent execution of one of the 6 remaining output instructions (62-67) selects one of 48 output ports, or subsequent execution of one of the 7 input instructions (69-6F) selects one of the 56 input ports.

With additional decoding the total number of input and output ports can be further expanded.

#### SIGNAL DESCRIPTION

Clock A, Clock B: The selected outputs stay true from the trailing edge of the Clock A (TPA) input to the trailing edge of Clock B (TPB) input, if the chip is enabled. The transition of both the clock inputs at the trailing edge should be the high-to-low.

CE: The Chip Enable input enables the chip when high. All outputs will be low when CE = 0.

N 0, N 1, N 2: These three inputs select one of eight decoded outputs when the chip is enabled. N 0 is the least significant input, N 2 is the most significant input.

Output 0 - Output 7: One output can be selected at a time. The truth table is shown below.

#### **TRUTH TABLE**

| CE | CLK A | CLK 8 | EN    |

|----|-------|-------|-------|

| 1  | 0     | 0     | Qn-1* |

| 1  | 0     | 1     | 1     |

| 1  | 1     | 0     | 0     |

| 1  | 1     | 1     | 1     |

| 0  | X     | х     | 0     |

<sup>1 =</sup> High Level

|   |   |     | _   |   |   |   |   |   |   |   |   |

|---|---|-----|-----|---|---|---|---|---|---|---|---|

| 2 | X | N O | 200 | • | 1 |   | 3 |   | 9 |   | 2 |

| 0 | 0 | 0   | 1   | 1 | 0 | 0 | 0 | 0 | 0 | 0 | a |

| 0 | 0 | 1   | 1   | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0   | 1   | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1   | 1   | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0   | 1   | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1   | 1   | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0   | 1   | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1   | 1   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| х | Х | X   | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Information furnished by Hughes is believed to be accurate and reliable. However, no responsibility is assumed by Hughes for its use; nor for any infringements or patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Hughes.

Hughes Microelectronics Center 500 Superior Avenue, Box H Newport Beach, CA 92658-8903 Tele: (714) 759-2727 FAX: (714) 759-2720

12/88 Printed in U.S.A.

<sup>0 =</sup> Low Level

X = Don't Care

<sup>\*</sup>Qn-1 = Enable remains in previous state.