# Built-In Prescaler PLL Frequency Synthesizer IC for Use in Analog Cellular Systems

#### **■ DESCRIPTION**

The HD155001T is a PLL frequency synthesizer IC that was developed for use in analog cellular systems. The HD155001T includes a built-in prescaler for analog cellular frequencies, and thus can form a PLL system by attaching an external loop filter and VCO.

#### **■ FUNCTIONS**

- Dual-Modules Pulse Swallow Type PLL Frequency Synthesizer

- Power Saving Mode

- Lock Detection Function (Selectable Hysteresis Characteristics)

- Optional Mode

- · Divisors Can Be Set By Serial Interface Commands

- Built-In Crystal Oscillator Circuit

- Built-In Charge Pump Circuit

- Built-In Analog Switch for High Speed Lock-Up

## **■ FEATURES**

- High Speed Prescaler (FINmax = 1.1 GHz) for Analog Cellular Systems

- Low Current Consumption

Operational: 7.5 mA (typ), 11 mA (max)

PS Mode: 200 μA (typ), 400 μA (max)

- High Charge Pump Current Drive Ability

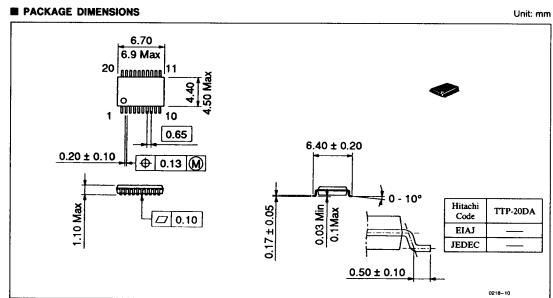

- TSOP-20 (thin small outline package) Miniature Package

- Can Be Used With Either Single Or Dual Voltage Power Supplies

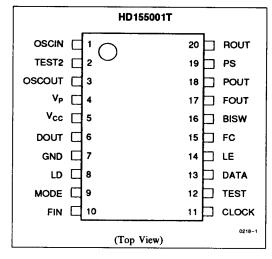

#### PIN OUT

## **■ PIN DESCRIPTION**

| No. | Pin              | 1/0    | Function                                                                                                 |            |

|-----|------------------|--------|----------------------------------------------------------------------------------------------------------|------------|

| 1   | OSCIN            | Input  | Reference Oscillator Input Pin. (A crystal can be connected between this pin and OSCOUT.)                | Oscillator |

| 2   | TEST2            | Output | Test Pin (normally left open)                                                                            | CMOS       |

| 3   | OSCOUT           | Output | The Reverse Phase Output Pin for the OSCIN Pin. (A crystal can be connected between this pin and OSCIN.) | Oscillator |

| 4   | V <sub>P</sub>   |        | Dout Pin Power Supply Connection Pin                                                                     |            |

| 5   | v <sub>cc</sub>  |        | Power Supply Connection Pin                                                                              |            |

| 6   | D <sub>out</sub> | Output | Charge Pump Output                                                                                       | Analog     |

| 7   | GND              |        | Ground Pin                                                                                               |            |

| 8   | LD               | Outut  | Lock Detection Output Pin                                                                                | CMOS       |

| 9   | MODE             | Input  | Normal/Optional Setting Pin                                                                              | Pull-Up    |

| 10  | FIN              | Input  | VCO Connection Pin                                                                                       | Analog     |

| 11  | CLOCK            | Input  | Command Input Synchronous Clock Input Pin                                                                | CMOS       |

| 12  | TEST             | Input  | Test Pin (normally left open)                                                                            | Pull-Up    |

| 13  | DATA             | Input  | Command Input Data Pin                                                                                   | CMOS       |

| 14  | LE               | Input  | Command Input Enable Pin                                                                                 | Pull-Up    |

| 15  | FC               | Input  | Phase Comparator Polarity Setting Pin                                                                    | Pull-Up    |

| 16  | BISW             | Output | High Speed Lock-Up Analog Switch Output Pin                                                              | Analog     |

| 17  | FOUT             | Output | Internal Counter Monitor Pin                                                                             | CMOS       |

| 18  | POUT             | Output | Phase Comparator Output Pin 1                                                                            | Analog     |

| 19  | PS               | Input  | Power Save Mode Setting Pin                                                                              | Pull-Up    |

| 20  | ROUT             | Output | Phase Comparator Output Pin 2                                                                            | CMOS       |

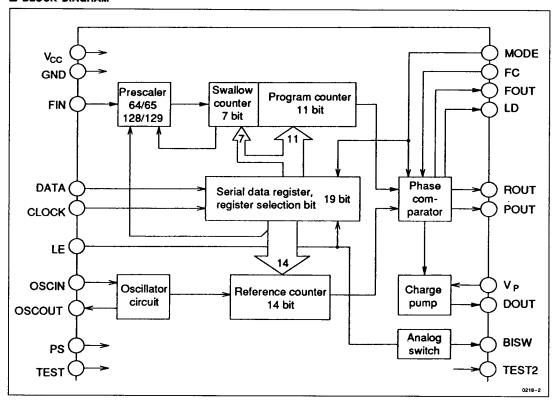

## **■ BLOCK DIAGRAM**

#### **■ FUNCTIONAL DESCRIPTION**

To operate the HD155001T, the mode must be set from the mode pins, and the registers must be set by the control microcomputer.

Setting the Operating Mode: The HD155001T provides the operating modes shown in Table 1. These operating modes are described in "Operating Modes".

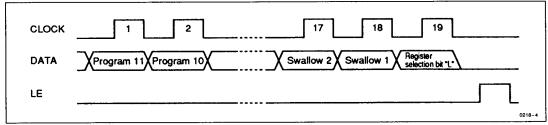

Setting the Registers: The HD155001T has four internal registers, and they are used to set the reference counter, the program counter, the swallow counter, and the prescaler divisors. These registers are set by the control microcomputer from the CLOCK, DATA, and LE pins. Figures 1 and 2 show the timing charts for these operations.

When setting these registers, the prescaler and the reference counter, and the program counter and the swallow

counter, are set together as register pairs. These register pins are selected by appending a register selection bit to the end of the setup data.

The register selection bit selects the prescaler and reference counter register, when this bit is high, and selects the program counter and swallow counter register when low.

The prescaler register (1 bit) sets the prescaler divisor, which is 64/65 when this bit is high, and 128/129 when low.

Note that the counter registers execute divide operations based on the set value as the divisor, i.e., they function as auto reload counters.

The value of the reference counter register must be between 16 and 16383, the value of the program counter register must be between 16 and 2047, and that of the swallow counter register, between 0 and 127.

#### • Table 1. Setting the HD155001T Operating Mode

|                        | MODE = H                    | MODE = L                                        |  |  |

|------------------------|-----------------------------|-------------------------------------------------|--|--|

| PS = H                 | Normal Active Mode          | Optional Active Mode Optional Power Saving Mode |  |  |

| PS = L                 | Normal Power Saving Mode    |                                                 |  |  |

| CLOCK 1  DATA Prescale | Pr Reference 14 Reference 2 | Reference 1 Register selection bit "H"          |  |  |

Figure 1. Setting the Prescaler and the Reference Counter Registers (Optional Mode)

Figure 2. Setting the Program Counter and the Swallow Counter Registers (Optional Mode)

Other Settings: The only other HD155001T setting is the FC pin, which determines the phase comparator's input polarity. When FC is high, if the reference counter output is delayed relative to the outputs of the program counter and the swallow counter (i.e., the VCO oscillator frequency is too high), then the charge pump output is set to low. When FC is low, the charge pump will be set to high in that case.

Operating Modes: The HD155001T provides four operating modes, which are selected by the MODE and PS pins. The MODE pin switches the HD155001T between the normal and optional modes. These modes differ in the register data loading timing from the LE pin, and in the LD pin lock detection conditions. The PS pin switches the HD155001T between the active and power saving modes.

#### 1. Normal Mode

Data loading controlled by the LE pin is based on the pin level: the register data is loaded when the LE pin is high.

The LD pin uses the phase comparator output without modification, and outputs that data. More accurately, when the charge pump is high impedance, LD will output a high level.

#### 2. Optional Mode

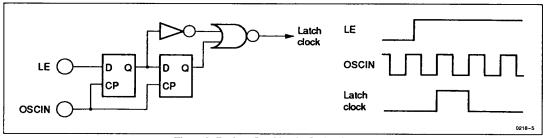

In optional mode, data loading by the LE pin is performed on signal edges. The OSCIN pin clock is used, and data is latched into the registers on the rising edge of the LE pin signal. A length of at least 3 OSCIN clock pulses is required by the LE pin. (See Figure 3.)

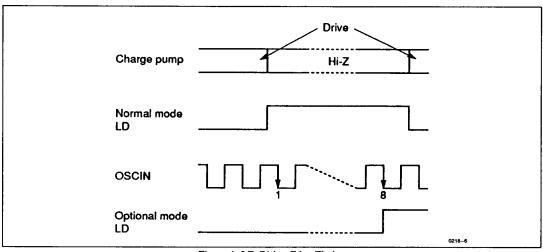

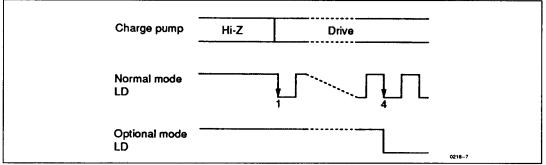

The LD pin outputs the phase comparator output with hysteresis generated by counting the phase comparator output with a counter. (See Figures 4 and 5.)

## 3. Power Saving Mode

A major portion of the current consumption by the HD155001T is used by the ECL prescaler. In power saving mode, the ECL circuits are stopped to reduce this power consumption.

Since the CMOS logic blocks consume essentially no power when there is no clock input, clock input to the CMOS blocks is stopped in power saving mode.

Furthermore, the charge pump output goes to the high impedance state, and the loop filter holds the immediately preceding value. A point that requires attention when using power saving mode, is that although the CMOS blocks, for which only the clock is stopped, retain their prior states, the ECL circuits do not retain their states. Thus there will be a slight phase difference created on return to active mode after exiting power saving mode.

Figure 3. Register Latching in Optional Mode

Figure 4. LD Rising Edge Timing

Figure 5. LD Falling Edge Timing

Register Setting Values: The HD155001T is a dual-modules pulse swallow-type PLL synthesizer, Therefore, the register settings can be derived from the following formulas.

- When the prescaler divisor is 128/129:

f<sub>VCO</sub> = fX'tal × (PRG × 128 + SWL) ÷ REF

- 2. When the prescaler divisor is 64/65:  $f_{VCO} = fX'tal \times (PRG \times 64 + SWL) \div REF$

f<sub>VCO</sub> and fX'tal indicate the VCO and oscillator frequencies respectively, and PRG, SWL, and REF are the program, swallow, and reference counter division ratios. Note that PRG must be larger than SWL, and when the prescaler divisor is 64, SWL must be less than 64.

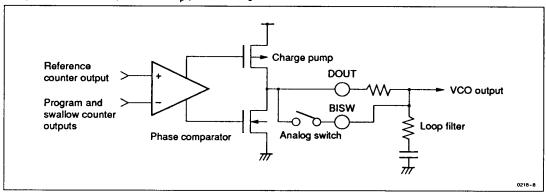

Use of the BISW Pin: The HD155001T provides a built-in analog switch for changing the loop filter time constants to shorten the lock-up time. By connecting the BISW pin to the loop filter capacitor, either directly or through an appropriate resistance, the charge pump output can charge the loop filter capacity rapidly. This shortens the lock-up time. (See Figure 6.)

To turn the analog switch on, the LE pin must be high.

**Use of the V<sub>p</sub> Pin:** There are cases where, due to the characteristics of the VCO used, it is necessary to have the dynamic range of the charge pump output exceed the V<sub>CC</sub> voltage. The HD155001T provides the V<sub>p</sub> pin as a charge

pump drive power supply, separate from the power supply for the prescaler and logic blocks. This pin is not connected to the V<sub>CC</sub> pin, and therefore can be set to a different voltage.

Note that it is possible to adjust the PLL system loop gain by changing the  $V_D$  pin voltage.

**Internal State Monitoring:** The HD155001T provides three monitor pins.

#### 1. FOUT

The FOUT pin is the monitor pin for the reference and program counters. Since these counters are auto-reload counters, the FOUT pin monitors the overflow signals. The FC pin determines which counter is monitored: the reference counter is monitored when FC is high, and the program counter when FC is low.

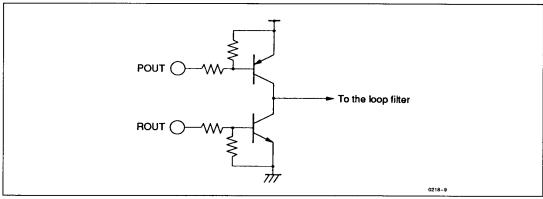

#### 2. ROUT and POUT

The ROUT and POUT pins monitor the charge pump drive signals. The ROUT pin is the current sink side monitor (NMOS internally), and the POUT pin is the current source monitor (PMOS internally).

**Use of the Monitor Pins:** Of the monitor pins described above, the ROUT and POUT pins can be used as shown in the circuit in Figure 7.

Figure 6. Analog Switch Usage Example

Figure 7. ROUT and POUT Pin Application Example

## ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                               | Symbol           | Value                                      | Unit |  |

|-----------------------------------------|------------------|--------------------------------------------|------|--|

| Power Supply Voltage (V <sub>CC</sub> ) | v <sub>cc</sub>  | - 0.3 to 7.0                               | v    |  |

| Power Supply Voltage (V <sub>P</sub> )  | V <sub>P</sub>   | V <sub>CC</sub> to 7.0                     | v    |  |

| Pin Voltage                             | V <sub>T</sub>   | -0.3 to V <sub>CC</sub> + 0.3<br>(7.0 max) | v    |  |

| Pin Voltage (Open Drain)                | V <sub>td</sub>  | -0.3 to V <sub>CC</sub> + 0.3<br>(7.0 max) | v    |  |

| Operating Temperature                   | Topr             | - 40 to + 85                               | °C   |  |

| Storage Temperature                     | T <sub>stg</sub> | - 55 to + 125                              | °C   |  |

## ■ ELECTRICAL CHARACTERISTICS

• DC Electrical Characteristics ( $T_A = 0 \text{ to } +70^{\circ}\text{C}, V_{CC} = 5\text{V} \pm 10\%, V_{SS} = 0\text{V}$ )

| Parameter                   | Symbol             | Min                 | Тур | Max                 | Unit            | Test Conditions                       | Applicable<br>Pins       |

|-----------------------------|--------------------|---------------------|-----|---------------------|-----------------|---------------------------------------|--------------------------|

| Power Supply Voltage        | $v_{cc}$           | 2.7                 | 3.0 | 3.3                 | v               |                                       | 5                        |

| Power Supply Current        | I <sub>CC</sub>    | _                   | 7.5 | 11                  | mA              |                                       | 5                        |

| Power Saving Mode Current   | I <sub>PS</sub>    |                     | 200 | 400                 | μA              |                                       | 5                        |

| FIN Operating Frequency     | f <sub>FIN</sub>   | 10                  | _   | 1100                | MHz             | $V_{FIN} = 0  dBm$                    | 10                       |

| OSCIN Operating Frequency   | foscin             | 0.01                | _   | 20                  | MHz             | $V_{OSCIN} = 2 V_{PP}$                | 1                        |

| FIN Input Voltage           | V <sub>FIN</sub>   | - 10                | _   | 6                   | dBm             | $f_{FIN} = 500  MHz$                  | 10                       |

| OSCIN Input Voltage         | V <sub>OSCIN</sub> | 0.5                 | _   | V <sub>CC</sub>     | V <sub>PP</sub> | f <sub>OSCIN</sub> = 10 MHz           | 1                        |

|                             | v <sub>IH</sub>    | 0.7 V <sub>CC</sub> |     | _                   | v               |                                       | 9, 11, 13,<br>14, 15, 19 |

| Input Voltage               | V <sub>IL</sub>    | _                   | T = | 0.3 V <sub>CC</sub> | v               |                                       |                          |

| Input Leakage Current       | $I_{L}$            | <b>–</b> 1          |     | 1                   | μΑ              | 0 < V <sub>IL</sub> < V <sub>CC</sub> | 11, 13                   |

| Pull-up Resistance          | R <sub>PU</sub>    | _                   | 50  | _                   | kΩ              |                                       | 9, 14, 15, 19            |

| 0                           | V <sub>OH</sub>    | $V_{\rm CC} - 0.4$  | _   | _                   | v               | $-I_{OH} = 0.4 \mathrm{mA}$           | 8, 17, 20                |

| Output Voltage              | V <sub>OL</sub>    | _                   | _   | 0.4                 | v               | $I_{OL} = 0.4 \text{ mA}$             |                          |

| D 0 :                       | V <sub>DOH</sub>   | $V_{CC} - 0.4$      | _   | _                   | v               | $-I_{DOH} = 2.0 \mathrm{mA}$          | 6                        |

| Dout Output Voltage         | V <sub>DOL</sub>   | _                   | _   | 0.4                 | v               | $I_{DOL} = 2.0  \text{mA}$            |                          |

| Analog Switch on Resistance | R <sub>SW</sub>    | _                   | 50  | _                   | Ω               |                                       | 16                       |

| Open Drain Output Voltage   | V <sub>ODL</sub>   | _                   | _   | 0.4                 | v               | $I_{ODL} = 0.4 \text{ mA}$            | 18                       |