# Description

The HD404508, HD4074509 is a CMOS 4-bit single-chip HMCS400 series microcomputer providing high program productivity. It is suitable for a digital tuning system by virtue of its PLL frequency synthesizer with 160 MHz prescaler, IF counter, A/D converter, and LCD driver incorporated in addition to ROM, RAM, I/O, timer, and serial interface. The HD4074509 is a ZTAT microcomputer incorporating PROM. It can dramatically shorten system development period and provide a smooth transition debugging to mass production.

### **Features**

- 4-bit CPU (HMCS400)

- 8192 words × 10 bits ROM (HD404508)

- 16384 words × 10 bits programmable ROM (HD4074509) (Program specification is compatible with 27256 type.)

- 512 digits × 4 bits RAM

- I/O ports

- —I/O ports: 29

- -Input ports: 2

- Output ports: 16 (multiplexed with the LCD segment pins)

- PLL with prescaler (max. 160 MHz)

- -12 programmable reference frequency

- -2-modulus prescaler (1/32, 1/33)

- —Phase comparator

- -PLL lock detection circuit

- LCD driver

- —Display duty: static, 1/2, 1/3

- —Segment signal output pins: 28 (including 16 multiplexed pins with R ports)

- -Common signal output pins: 3

- IF counter

- —Gate time: 1 ms. 4 ms. 8 ms.  $\infty$  ms

- -Maximum input frequency: 15 MHz

- Two clock synchronous SCIs

- A/D converter (8 bits × 2 channels)

- Three timer/counters

- —8-bit timer (multiplexed with reload, event, PWM)

- —8-bit timer (multiplexed with reload, event)

- —20-bit timer (free-running, 125 ms interrupt)

- Instruction cycle time: 1.8 µs

- Subroutine stack: 16 levels including interrupts

- Five external and six internal interrupts

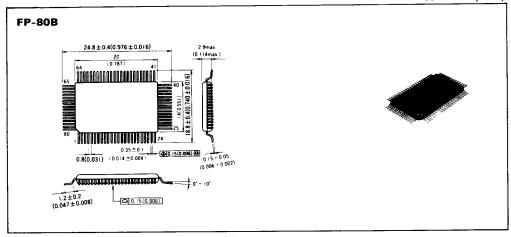

- Package: 80-pin flat plastic package (FP-80B)

# **Program Development Support Tools**

- Cross assembler and simulator software for use with IBM PCs and compatibles

- In circuit emulator for use with IBM PC

- Programming socket adapter for programming the EPROM-on-chip device

## **Ordering Information**

| Part No.    | ROM (Words)        | Package |

|-------------|--------------------|---------|

| HD404508FS  | 8192<br>(Mask ROM) | FP-80B  |

| HD4074509FS | 16384<br>(PROM)    |         |

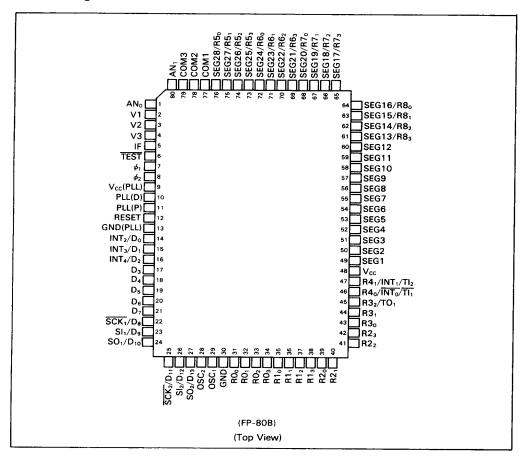

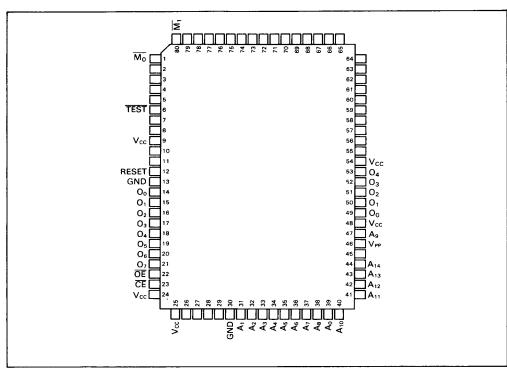

# Pin Arrangement

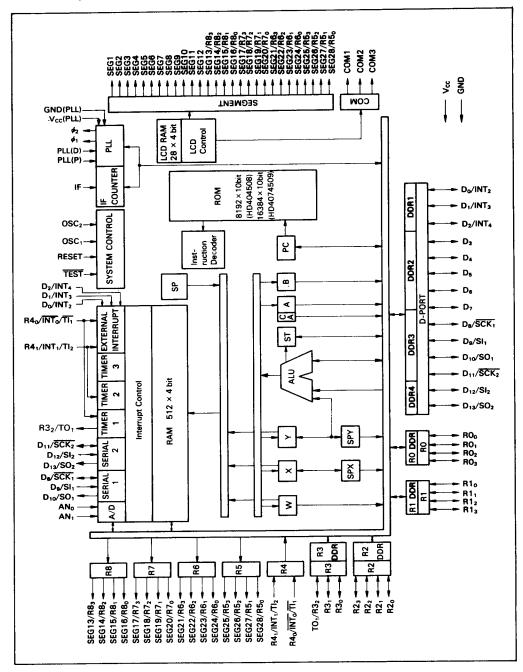

# **Block Diagram**

#### Pin Function

## Power supply

$\mathbf{V}_{CC}$ : Power supply voltage (+5 V) is applied to  $\mathbf{V}_{CC}$ .

**GND:** Connected to the ground (0 V). **Vcc(PLL):** Connected to power supply for

PLL (+5 V). **GND(PLL):** Connected to the ground for PLL (0V).

#### Test

**TEST:** Input for a factory test mode. Connected to the V<sub>CC</sub> for normal operation.

#### Reset

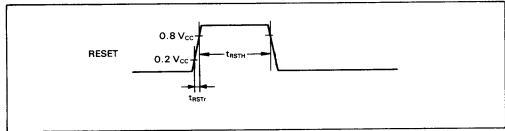

RESET: RESET resets the MCU.

#### Oscillation

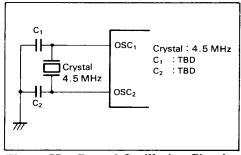

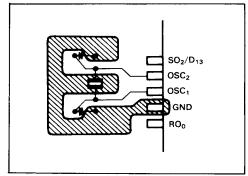

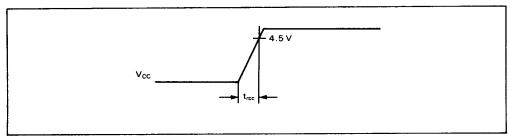

**OSC1, OSC2:** Input pins for the crystal oscillator circuits. Connected to the 4.5 MHz crystal resonator.

#### Ports

**D port (D<sub>0</sub>-D<sub>13</sub>):** The D port is an input/output port accessed on a bit basis. All D<sub>0</sub>-D<sub>13</sub> are input/output pins. D<sub>0</sub>, D<sub>1</sub> and D<sub>2</sub> are multiplexed with INT<sub>2</sub>, INT<sub>3</sub> and INT<sub>4</sub>, respectively. D<sub>8</sub> to D<sub>13</sub> are multiplexed with  $\overline{SCK_1}$ , SI<sub>1</sub>, SO<sub>1</sub>,  $\overline{SCK_2}$ , SI<sub>2</sub>, and SO<sub>2</sub>, respectively.

R ports (R0-R8): The R ports are input/output ports accessed in 4-bit units.

However, R3 is a 3-bit port and R4 a 2-bit port. R0 to R3 are I/O ports; R5 to R8 output ports; and R4 an input port. The pins R3<sub>2</sub>, R5<sub>0</sub>,-R8<sub>3</sub>, R4<sub>0</sub>, and R4<sub>1</sub> are multiplexed with TO<sub>1</sub>, SEG28-SEG13,  $\overline{\text{INT}_0}/\overline{\text{TI}_1}$ , and  $\overline{\text{INT}_1}/\text{TI}_2$ , respectively.

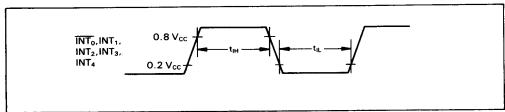

### Interrupt

$\overline{\text{INT_0}}$ ,  $\overline{\text{INT_1}}$ ,  $\overline{\text{INT_2}}$ ,  $\overline{\text{INT_3}}$ ,  $\overline{\text{INT_4}}$ : External interrupts for the MCU. These five pins are multiplexed with R4<sub>0</sub>/ $\overline{\text{TI_1}}$ , R4<sub>1</sub>/ $\overline{\text{TI_2}}$ , D<sub>0</sub>, D<sub>1</sub> and D<sub>2</sub>, respectively.

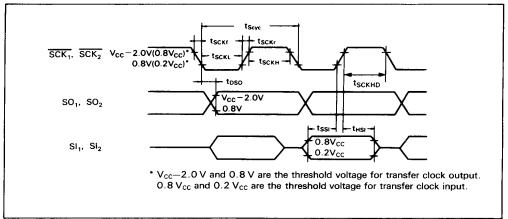

### Serial communication interface

$\overline{SCK_1}$ ,  $SI_1$ ,  $SO_1$ ,  $\overline{SCK_2}$ ,  $SI_2$ ,  $SO_2$ : These are transmit clock input/output pins ( $\overline{SCK_1}$ ,  $\overline{SCK_2}$ ), serial data input pins ( $SI_1$ ,  $SI_2$ ), and serial data output pins ( $SO_1$ ,  $SO_2$ ) used for serial interface.  $\overline{SCK_1}$ ,  $\overline{SCK_2}$ ,  $SI_1$ ,  $SI_2$ ,  $SO_1$ , and  $SO_2$  are

multiplexed with  $D_8$ ,  $D_{11}$ ,  $D_9$ ,  $D_{12}$ ,  $D_{10}$ , and  $D_{13}$ , respectively.

#### Timer

$\overline{\textbf{TI_1}}$ ,  $\overline{\textbf{TI_2}}$ ,  $\overline{\textbf{TO_1}}$ : These are external clock input pins  $(\overline{\textbf{TI}_1}, \, \textbf{TI}_2)$  and timer output pin  $(\textbf{TO_1})$  used for the timer.  $\overline{\textbf{TI}_1}$ ,  $\overline{\textbf{TI}_2}$ , and  $\overline{\textbf{TO}_1}$  are multiplexed with  $R4_0/\overline{\textbf{INT}_0}$ ,  $R4_1/\overline{\textbf{INT}_1}$ , and  $R3_2$ , respectively.

## Liquid crystal display

COM1, COM2, COM3, SEG1-SEG28: Thes are the common signal output pins (COM1-COM3) and segment signal output pins (SEG1-SEG28) used for the LCD driver. The sixteen pins from SEG13 to SEG28 are multiplexed with R8<sub>3</sub>-R8<sub>0</sub>, R7<sub>3</sub>-R7<sub>0</sub>, R6<sub>3</sub>-R6<sub>0</sub>, and R5<sub>3</sub>-R5<sub>0</sub>, respectively.

V1, V2, V3: Power supply pins for the LCD.

# PLL

PLL (P): An input pin for 160 MHz max. of local oscillation output (VCO output). This pin becomes active when pulse swallow mode is selected during PLL enable. Since an alternating current amplifier is incorporated, local oscillation output should be latched after being filtered through a capacitor.

**PLL (D):** An input pin for 20 MHz max. of local oscillation output (VCO output). This pin becomes active when direct dividing mode is selected during PLL enable. Since an alternating current amplifier is incorporated, local oscillation output should be latched after being filtered through a capacitor.

$\phi$ 1,  $\phi$ 2: These pins are outputs of a phase comparator used by the PLL function. The same signal is output from  $\phi$ 1 and  $\phi$ 2.

#### IF counter

IF: An input pin for intermediate frequency measurement. Since an alternating current amplifier is incorporated, local oscillation output must be latched after being filtered through a capacitor.

#### AD converter

$AN_0$ ,  $AN_1$ : These pins are the AD converter input pins.

# **OHITACHI**

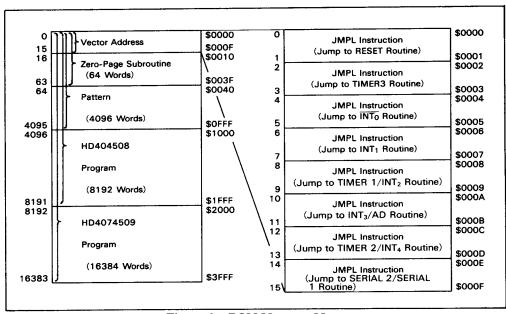

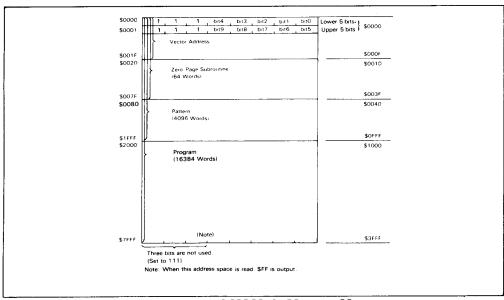

# Memory Map

# **ROM Memory MAP**

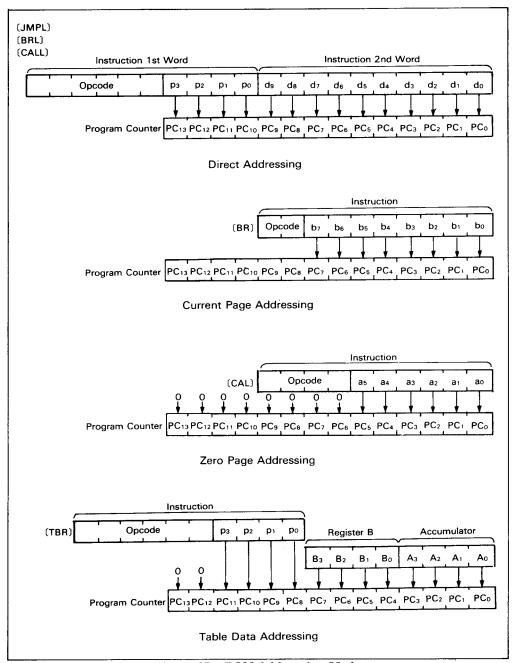

ROM memory map is shown in figure 1 and is explained below.

Vector address area (\$0000 to \$000F): Locations \$0000 through \$000F are reserved for JMPL instruction to branch to the start addresses of the reset routine and the interrupt service routine. After reset or interrupt routine is serviced, the program is executed from the vector address.

Zero page subroutine area (\$0000 to \$003F): Locations \$0000 through \$003F are

reserved for subroutines. The program branches to the subroutine in \$0000-\$003F by the CAL instruction.

Pattern area (\$0000 to \$0FFF): The ROM data in locations \$0000 through \$0FFF can be referred to by the P instruction.

#### Program area

(\$0000 to \$1FFF: HD404508, \$0000 to \$3FFF: HD4074509,):

Locations \$0000 through \$1FFF, \$3FFF can be used for program code.

Figure 1. ROM Memory Map

### RAM Memory MAP

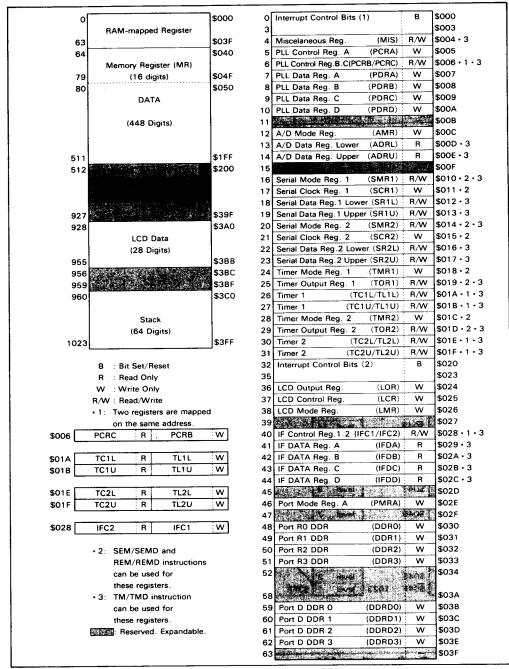

The MCU contains 512 digits  $\times$  4 bits RAM comprising data area and stack area. In addition to these areas, interrupt control bits, special registers, and display data RAM are mapped to the same RAM memory space. RAM memory map (figure 2) is described in the following paragraphs.

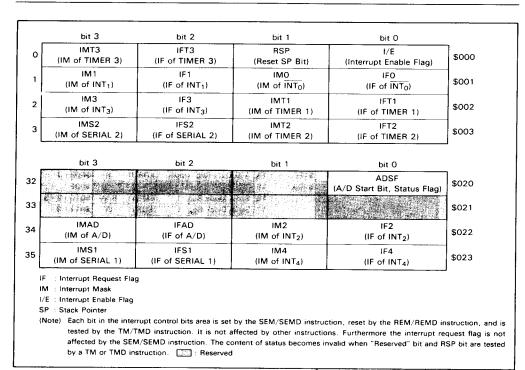

Interrupt control bit area (\$000 to \$003, \$020 to \$023): The interrupt control bit area (figure3) is used to control interrupt. It can be accessed only by the RAM bit manipulation instruction. However, the interrupt request flag cannot be set by software. The RSP bit is used only to reset the stack pointer.

**Special registers area (\$004 to \$01F, \$024 to \$03F):** The special registers are the mode registers for external interrupt, serial interface, and timer, data direction and data registers for I/O ports. As shown in figure 2, these registers can be classified into three

types: write-only, read-only, and read/write registers.

Note that some of these registers cannot be accessed by the RAM bit manipulation instruction.

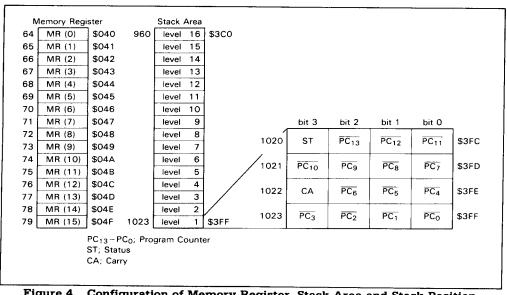

Data area (\$040 to \$01FF): The memory register (MR), 16 addresses deep (\$040-\$04F), can be accessed by the LAMR and XMRA instructions (figure 4).

Stack area (\$03C0 to \$03FF): The stack area is used for saving the contents of the program counter (PC), status (ST), and carry (CA). This area can be used as a 16-nesting-level subroutine stack in which one level requires 4 digits. The data to be saved and save conditions are shown in figure 4. The program counter is restored by the RTN and RTNI instructions. Status and carry are restored by the RTNI instruction only. Any space not used is available data storage.

Figure 2. RAM Memory Map

## **҈®HITACHI**

Figure 3. Configuration of Interrupt Control Bit Area (RAM Space)

Configuration of Memory Register, Stack Area and Stack Position

# **Functional Description**

## Registers and Flags

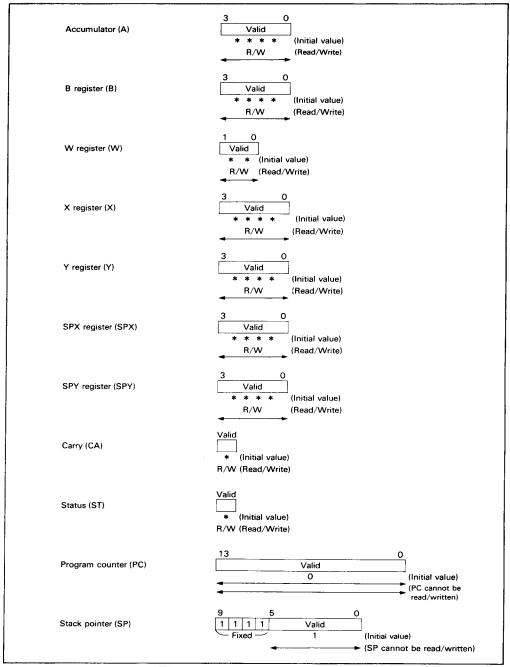

The MCU has nine registers and two flags for the CPU operations. They are illustrated in figure 5 and described in the following paragraphs.

Accumulator (A), B register (B): The 4-bit register accumulator and B resgister are used to hold the results from the arithmetic logic unit (ALU), and to transfer data to/from memories, I/O, and other registers.

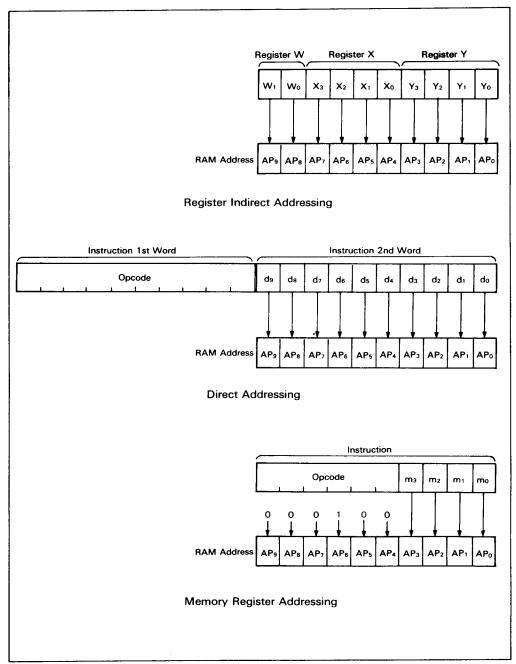

W register (W), X register (X), Y register (Y): W register is a 2-bit, and X and Y registers are 4-bit registers used for register indirect RAM addressing. Y register is also used for D-port addressing.

SPX register (SPX), SPY register (SPY): The 4-bit registers SPX and SPY are used to assist the X and Y registers, respectively.

Carry (CA): Carry (CA) stores ALU overflow generated by the arithmetic operation. It is affected by the SEC, REC, ROTL, and ROTR instructions. Carry is pushed onto the stack during interrupt servicing, and popped from the stack by the RTNI instruction, but not by the RTN instruction. Status (ST): Status (ST) latches ALU overflow generated by the arithmetic and compare instructions, Not Zero from ALU, and results of bit tests. It is a branch condition of the BR, BRL, CAL, and CALL instructions. The contents of the status remain unchanged until the next arithmetic, compare, or bit test instruction is executed. ST becomes 1 after the BR, BRL, CAL, or CALL instruction is executed irrespective of whether it is executed or skipped. The contents of the status are pushed onto the stack during interrupt servicing, and popped from the stack by the RTNI instruction, but not by the RTN instruction.

**Program counter (PC):** The 14-bit program counter is a binary counter which holds a ROM address.

Stack pointer (SP): The 10-bit stack pointer contains the address of the next stack area. SP is initialized to \$3FF by MCU reset. It is decremented by 4 when data is pushed onto the stack, and is incremented by 4 when data is popped from the stack.

Since the upper 4 bits of SP are fixed to 1111, the stack can be used for up to 16 levels. SP is initialized to \$3FF in two ways; MCU reset and RSP bit reset with the REM or REMD instruction.

Figure 5. Registers and Flags

# **@HITACHI**

Hitachi America Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

1276

#### Reset

#### Power-on reset:

At power-on, the MCU automatically enters reset state for approximately 60 to 65 ms to assure oscillation stabilization time, and then the MCU recovers from that state.

# Reset by RESET pin (reset from active mode, standby mode):

The MCU is reset at the rising edge of the reset signal. This signal should be asserted high for at least 3.6  $\mu$ s. The MCU is then reset for one instruction cycle time, after which reset is cancelled.

# Reset by RESET pin (reset from stop mode):

The MCU is reset at the rising edge of the reset signal. This signal should be asserted high for at least 20 ms. At the beginning of oscillation, the MCU automatically enters reset state for 60 to 65 ms to assure oscillation stabilization time, and then reset is cancelled.

#### Read function:

The accessible RESET pin is mapped to the bit 0 (\$004, 0) of the miscellaneous register (MLS).

Note that from power-on to the begining of normal oscillation, the I/O pins are undefined since the I/O data direction registers are not initialized. Values initialized by MCU reset are shown in table 1 and table 2.

Table 1. Initial Value by MCU Reset

| items                |                                                                | Initial Value<br>by MCU Reset | Contents                                              |

|----------------------|----------------------------------------------------------------|-------------------------------|-------------------------------------------------------|

| Program Counter (PC) |                                                                | \$0000                        | Execute program from the top of ROM address           |

| Status (ST)          |                                                                | 1                             | Enable to branch with conditional branch instruction  |

| Stack Pointer        | (SP)                                                           | \$3FF                         | Stack level is 0                                      |

| Interrupt            | Interrupt Enable Flag (I/E)                                    | 0                             |                                                       |

| Flag/Mask            | Interrupt Request Flag (IF)                                    | 0                             |                                                       |

|                      | Interrupt Mask (IM)                                            | 1                             |                                                       |

| PLL                  | PLL Control Register A, B, C<br>(PCRA, PCRB, PCRC)             | 0000                          |                                                       |

| A/D                  | A/D Mode Register (AMR)                                        | 0000                          |                                                       |

| Serial<br>Interface  | Serial Mode Register 1, 2 (SMR1, SMR2)                         | 0000                          |                                                       |

|                      | Serial Clock Register 1, 2 (SCR1, SCR2)                        | 0000                          |                                                       |

| Timer/<br>Counter    | Timer Mode Register 1, 2 (TMR1, TMR2)                          | 0000                          |                                                       |

|                      | Timer Output Register 1, 2 (TOR1, TOR2)                        | 0000                          |                                                       |

|                      | Timer/Event Counter 1, 2 Lower, Upper (TC1L, TC1U, TC2L, TC2U) | 0000                          |                                                       |

|                      | Timer 3                                                        | Note 1                        |                                                       |

| LCD                  | LCD Output Register (LOR)                                      | Note 2                        |                                                       |

|                      | LCD Control Register (LCR)                                     | 0000                          |                                                       |

|                      | LCD Mode Register (LMR)                                        | 0000                          | After reset is cancelled, duty must be set by program |

| IF                   | IF Control Register 1, 2 (IFC1, IFC2)                          | 0000                          |                                                       |

|                      | IF Counter Data Register A, B, C, D (IFDA, IFDB, IFDC, IFDD)   | 0000                          |                                                       |

| 1/0                  | Port D Data Register                                           | 1                             |                                                       |

|                      | Port R0-R3 Data Register                                       | Note 3                        |                                                       |

|                      | Port RO-R3 DDR (DDRO, DDR1,<br>DDR2, DDR3)                     | Note 4                        |                                                       |

|                      | Port D DDR (DDRD0, DDRD1,<br>DDRD2, DDRD3)                     | 0000                          |                                                       |

|                      | Port Mode Register A (PMRA)                                    | 0000                          |                                                       |

Note 1: Initial value of timer 3 by MCU reset

The initial value of depends on the value of the data retention bit (MIS $_3$ : \$004, 3).

# **@HITACHI**

| Item    | Reset when power-on reset or data retention bit is 0 | Reset when data retention bit is 1 |

|---------|------------------------------------------------------|------------------------------------|

| Timer 3 | All bits become 0 and are initialized                | Not initialized                    |

Note 2: Initial value of the LCD output register by MCU reset

The initial value of the LCD output register depends on the value of the data retention bit (MIS<sub>3</sub>: \$004, 3).

| Item                | Reset when power-on reset or data retention bit is 0               | Reset when data retention bit is 1   |  |

|---------------------|--------------------------------------------------------------------|--------------------------------------|--|

| LCD output register | LCD output register becomes 0000 and SEG/R-port pins become R port | Retained (SEG/R port is not changed) |  |

Note 3: Initial value of the port RO-R3 data register by MCU reset

The initial value of the port RO-R3 data register depends on the value of the data retention bit

(MIS<sub>3</sub>: \$004, 3).

| Item                     | Reset when power-on reset or data retention bit is 0 | Reset when data retention bit is 1 |

|--------------------------|------------------------------------------------------|------------------------------------|

| Port RO-R3 data register | 1                                                    | Retained                           |

Note 4: Initial value of the R port data direction register by MCU reset

Initial value of the R port data direction register depends on the value of the data retention bit (MIS<sub>3</sub>: \$004, 3).

| Item                           | Reset when power-on reset or data retention bit is 0                          | Reset when data retention bit is 1          |  |  |

|--------------------------------|-------------------------------------------------------------------------------|---------------------------------------------|--|--|

| R port data direction register | The R port data direction register becomes 0000 and R port becomes input port | Retained (I/O of the R port is not changed) |  |  |

1279

Table 2. Values of the Registers except for Table 1 after the Reset

| Items                                                                    | Initial Value by<br>MCU Reset from<br>Active Mode                     | Initial Value by<br>MCU Reset from<br>Standby Mode | Initial Value by<br>MCU Reset from<br>Oscillation Stop<br>Mode | Initial Value by<br>MCU Reset from<br>Power-on |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------|------------------------------------------------|

| Carry (CA)                                                               | The contents of the                                                   |                                                    |                                                                |                                                |

| Accumulator (A)                                                          | items just before MCU reset are not                                   |                                                    |                                                                |                                                |

| B Register (B)                                                           | assured. It is necessary to                                           |                                                    |                                                                |                                                |

| W Register (W)                                                           | initialize them by software again.                                    |                                                    |                                                                |                                                |

| X/SPX Register<br>(X/SPX)                                                | Software again.                                                       |                                                    |                                                                |                                                |

| Y/SPY Register<br>(Y/SPY)                                                |                                                                       |                                                    |                                                                |                                                |

| PLL Data Register<br>(PDRA, PDRB,<br>PDRC, PDRD)                         |                                                                       |                                                    |                                                                |                                                |

| A/D Data Register<br>Lower, Upper<br>(ADRL, ADRU)                        |                                                                       |                                                    |                                                                |                                                |

| Serial Data Register 1,<br>2 Lower, Upper<br>(SR1L, SR1U, SR2L,<br>SR2U) |                                                                       |                                                    |                                                                |                                                |

| RAM                                                                      | The contents of RAM                                                   | just before MCU rese                               | et are retained                                                | Same as above                                  |

| Miscellaneous MIS <sub>3</sub>                                           | The contents of MIS <sub>3</sub> just before MCU reset are retained 0 |                                                    |                                                                | 0                                              |

| Register (MIS) MIS <sub>0</sub>                                          | MISo reads RESET pin level at read operation                          |                                                    |                                                                |                                                |

## Interrupt

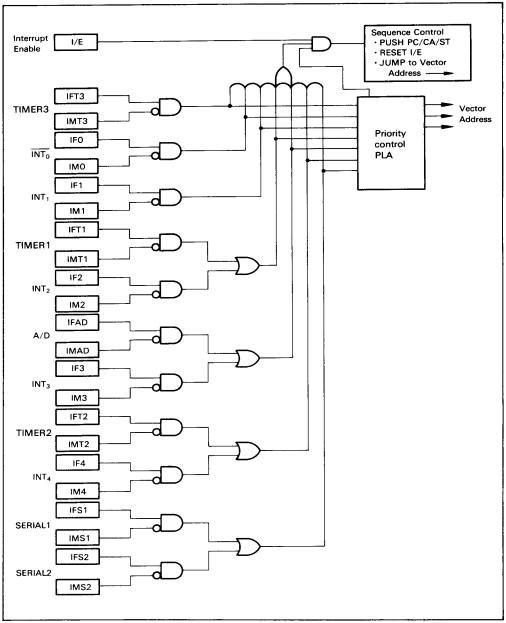

Eleven interrupt sources are available on the MCU: external requests ( INT<sub>0</sub>, INT<sub>1</sub>, INT<sub>2</sub>, INT<sub>3</sub>, INT<sub>4</sub>), timers (TIMER 1, TIMER 2, TIMER 3), A/D converter, and serial interfaces (SERIAL 1, SERIAL 2). For each source, an interrupt request flag (IF) and interrupt mask (IM) are provided to control and maintain the interrupt requests. To control the entire interrupt process, the interrupt enable flag (I/E) is provided.

Since the vector addresses are shared between timer 1 and  $INT_2$ , between A/D and  $INT_3$ , between timer 2 and  $INT_4$ , and between serial 1 and serial 2, determining which request occurs must be done by software.

Interrupt control bits and interrupt processing: The interrupt control bits are mapped to addresses \$000 through \$003, and \$020 through \$023 of RAM space and are accessed by the RAM bit manipulation instruction.

However, interrupt request flag IF cannot be set by software.

The interrupt enable flag (I/E) and interrupt request flag (IF) are set to 0, and the interrupt mask (IM) is initialized to 1 by MCU reset.

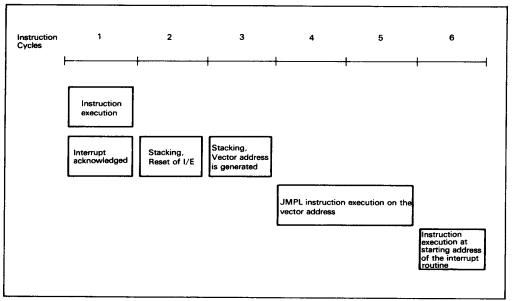

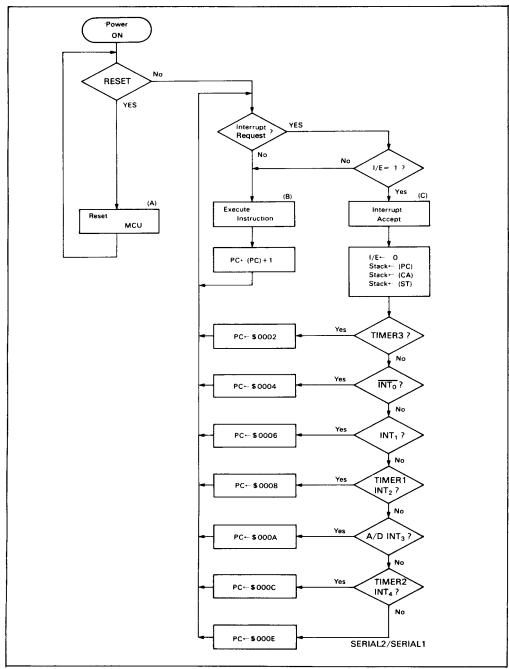

An interrupt control circuit block diagram is shown in figure 6. Interrupt priority and vector addresses are shown in table 3, and the interrupt processing conditions for 11 different interrupt types in table 4.

When interrupt request flag is 1 and interrupt mask is 0, an interrupt request is generated. If the interrupt enable flag is 1 at that time, interrupt processing activates. Then a vector address corresponding to the interrupt request is generated from priority PLA.

An interrupt processing sequence and flow-chart are shown in figures 7 and 8 respectively. When an interrupt is received, the current instruction execution finishes at the first cycle, I/E is reset at the second cycle, then the contents of the carry, status, and program counter are pushed onto the stack in the second and third cycles, and the program jumps to the vector address to restart instruction execution in the third cycle. For each vector address area, the JMPL instruction must be programmed to branch the starting address of interrupt routine. The interrupt request flag which causes interrupt

processing must be reset by software in an interrupt routine.

Interrupt enable flag (I/E: \$000, 0): The interrupt enable flag controls enable/disable of all interrupt requests. It is reset by interrupt processing and set by the RTNI instruction. (See table 5.)

External interrupts (INT<sub>0</sub>, INT<sub>1</sub>, INT<sub>2</sub>, INT<sub>3</sub>, INT<sub>4</sub>): Five external interrupt pins are provided for the MCU. The external interrupt request flag is set at the falling edge of the INT<sub>0</sub> input. It is set at the rising edge of the INT<sub>1</sub>, INT<sub>2</sub>, INT<sub>3</sub>, and INT<sub>4</sub> inputs. When using INT<sub>0</sub> and INT<sub>1</sub>, interrupt input should be enabled by setting the external interrupt enable bit of the timer output register (TOR1: \$019, TOR2: \$01D). If the interrupt enable bit is reset, the external interrupt request flag is not set and interrupt processing is not performed since input signal itself is maskes. (See section "Timer".)

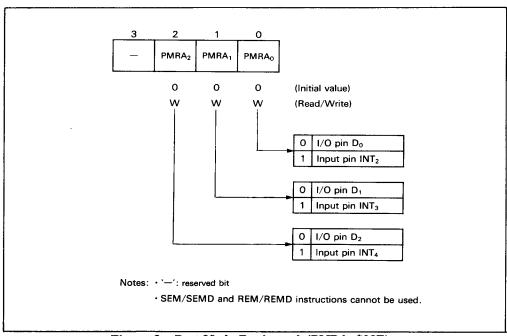

When using INT<sub>2</sub>, INT<sub>3</sub>, and INT<sub>4</sub>, the corresponding bits of port mode register A (PMRA: \$02E) select external interrupt input. If port mode register A is set, the corresponding data direction register bit is reset automatically to input. If port mode register A is reset, external interrupt request flag is not set in spite of external interrupt signal input and interrupt processing is not performed since the external interrupt input signal is masked.

External interrupt requrst flags (IF0: \$001, 0 IF1: \$001, 2 IF2: \$022, 0 IF3: 002, 2 IF4: \$023, 0): External interrupt request flag IF0 is set at the falling edge of the  $\overline{\text{INT}}_0$  input. IF1-IF4 are set at the rising edge of INT<sub>1</sub>-INT<sub>4</sub>. (See table 6.)

External interrupt masks (IM0: \$001, 1 IM1: \$001, 3 IM2: \$022, 1 IM3: \$022, 3 IM4: \$023,1): The external interrupt request masks mask the interrupt request from the external interrupt request flag. (See table 7.)

Port mode register A (PMRA: \$02E): Port mode register A is a 3-bit write-only register which controls the  $D_0/INT_2$ ,  $D_1/INT_3$ , and  $D_2/INT_4$  pins as shown in figure 9.

Port mode register A is initialized to \$0 by MCU reset, so that these pins are all set to D port I/O pins after reset.

Table 3. Vector Addresses and Interrupt Priority

| address | Vector | Priority | Reset, interrupt                        |

|---------|--------|----------|-----------------------------------------|

|         | \$0000 | _        | RESET                                   |

|         | \$0002 | 1        | TIMER3                                  |

|         | \$0004 | 2        | ĪNT <sub>0</sub>                        |

|         | \$0006 | 3        | INT <sub>1</sub>                        |

|         | \$0008 | 4        | TIMER1/INT <sub>2</sub>                 |

|         | \$000A | 5        | INT <sub>3</sub> /A/D                   |

|         | \$000C | 6        | TIMER2/INT <sub>4</sub>                 |

| _       | \$000E | 7        | SERIAL2/SERIAL1                         |

|         |        |          | TIMER2/INT <sub>4</sub> SERIAL2/SERIAL1 |

Table 4. Interrupt Servicing Conditions

Interrupt Source

| Interrupt<br>Control Bit | TIMER3 | INTo | INT <sub>1</sub> | TIMER1<br>/INT <sub>2</sub> | INT <sub>3</sub><br>/A/D | TIMER2<br>/INT4 | SERIAL1<br>/SERIAL2 |

|--------------------------|--------|------|------------------|-----------------------------|--------------------------|-----------------|---------------------|

| I/E                      | 1      | 1    | 1                | 1                           | 1                        | 1               | 1                   |

| IFT3·IMT3                | 1      | 0    | 0                | 0                           | 0                        | 0               | 0                   |

| IFO·IMO                  | *      | 1    | 0                | 0                           | 0                        | 0               | 0                   |

| IF1 · IM1                | *      | *    | 1                | 0                           | 0                        | 0               | 0                   |

| IFT1·IMT1 + IF2 · IM2    | *      | *    | *                | 1                           | 0                        | 0               | 0                   |

| IF3·IM3+IFAD·IMAD        | *      | *    | *                | *                           | 1                        | 0               | 0                   |

| IFT2·IMT2+IF4·IM4        | *      | *    | *                | *                           | *                        | 1               | 0                   |

| IFS2·IMS2+IFS1·IMS1      | *      | *    | *                | *                           | *                        | *               | 1                   |

|                          |        |      |                  |                             |                          |                 |                     |

<sup>\* :</sup> Both 0 and 1 do not affect operation

Figure 6. Interrupt Control Circuit Block Diagram

Figure 7. Interrupt Servicing Sequence

Figure 8. Interrupt Servicing Flowchart

Table 5. Interrupt Enable Flag (\$000,0)

| Interrupt Enable<br>Flag (I/E) | Interrupt Enable<br>/Disable |

|--------------------------------|------------------------------|

| 0                              | Disable                      |

| 1                              | Enable                       |

|                                |                              |

Initial value 0, R/W

Table 6. External Interrupt Request Flag (\$001,0, \$001,2, \$002,2, \$022,0, \$023,0)

| External Interrupt<br>Request Flag<br>(IF0, IF1, IF2, IF3, IF4) | Interrupt Requests  |

|-----------------------------------------------------------------|---------------------|

| 0                                                               | No                  |

| 1                                                               | Yes                 |

| Initial value 0, R/W (d                                         | cannot be set to 1) |

Table 7. External Interrupt Mask (\$001, 1, \$001,3, \$002,3, \$022,1, \$023,1)

# External Interrupt Mask (IMO, IM1, IM2, IM3, IM4) Interrupt Requests

| 0 | Enable          |

|---|-----------------|

| 1 | Disable (masks) |

|   |                 |

Initial value 1, R/W

Figure 9. Port Mode Register A (PMRA: \$02E)

## Low Power Dissipation Mode

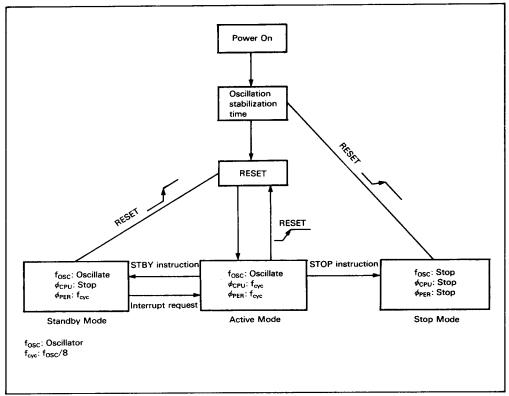

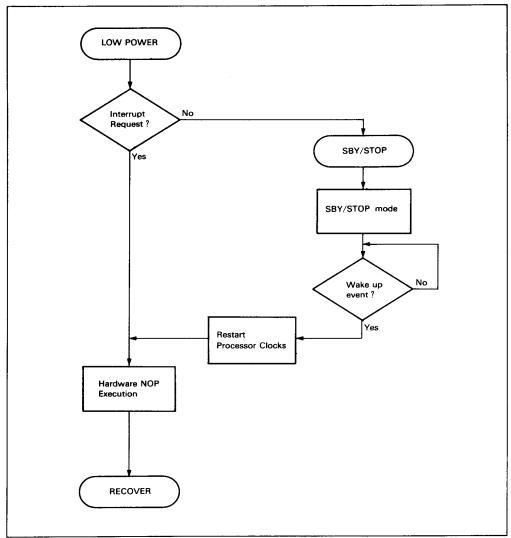

The MCU has two low power dissipation modes, standby mode, stop mode. The function of the low power dissipation mode is shown in table 8. CPU state transition between low power dissipation modes is shown in figure 10.

Table 8. Low Power Dissipation Mode

| Low<br>Power<br>Dissipation<br>Mode |                     | Conditions            |      |        |          |                   |                                                     |                                                                                               |

|-------------------------------------|---------------------|-----------------------|------|--------|----------|-------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------|

|                                     | Instruc-<br>tion    | Oscillator<br>circuit |      | •      | RAM      | Register,<br>Flag | Input/<br>Output<br>Pin                             | Timer 1,2,3<br>Serial<br>Interface 1,<br>2, A/D,<br>IF counter,<br>LCD,PLL<br>( $\phi$ PER*3) |

| Standby<br>Mode                     | SBY instruction     | Active                | Stop | Active | Retained | Retained          | Retained                                            | Active                                                                                        |

| Stop<br>Mode                        | Stop<br>instruction | Stop                  | Stop | Stop   | Retained | Reset *1          | R port:<br>retained<br>D port:<br>high<br>impedance | Stop                                                                                          |

<sup>\*1)</sup> The MCU recovers from STOP mode by Reset input. Refer to table 1 of section "Reset" for the contents of the flags and registers.

<sup>\*2)</sup>  $\phi$ CPU: System clock

<sup>\*3) \$\</sup>phi\$PER: Interrupt, peripheral function clock

Figure 10. CPU State Transition

**Active Mode:** In active mode, the MCU operates depending on the clock generated from the OSC1 and OSC2 oscillator circuits.

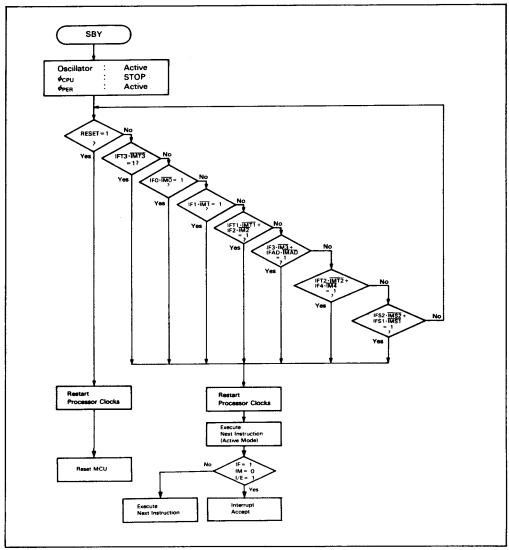

**Standby Mode:** The MCU enters standby mode when a SBY instruction is excuted. In this mode, an oscillator, interrupt, timer, serial interface, A/D, LCD, PLL, and IF counter continue to operate, but all instruction-related clocks stop.

This in turn stops the CPU, retains all RAM and register contents, and maintains current I/O pin status.

The standby mode is terminated by a RESET or interrupt request. After an interrupt request, the MCU resumes by executing the next instruction following the SBY instruction. Then, if the interrupt enable flag is 1, the interrupt is processed. If the interrupt enable flag is 0, the interrupt request is left pending and normal instruction execution continues.

MCU operating flowchart in standby mode is

shown in figure 11.

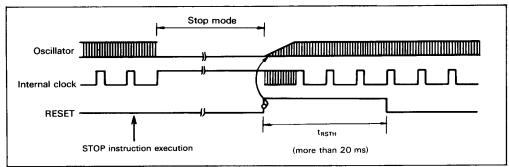

**Stop Mode:** The MCU enters stop mode when a stop instruction is executed. In this mode, the oscillator stops, causing all MCU functions to also stop.

The stop mode is terminated by a RESET input as shown in figure 12. Reset must be High for at least 20 ms to stabilize oscillation. During stop mode, all RAM contents are retained.

When the MCU resumes after stop mode, the accuracy of the contents of the accumulator, B register, W register, X/SPX register, Y/SPY register, carry, and serial data register cannot be guaranteed.

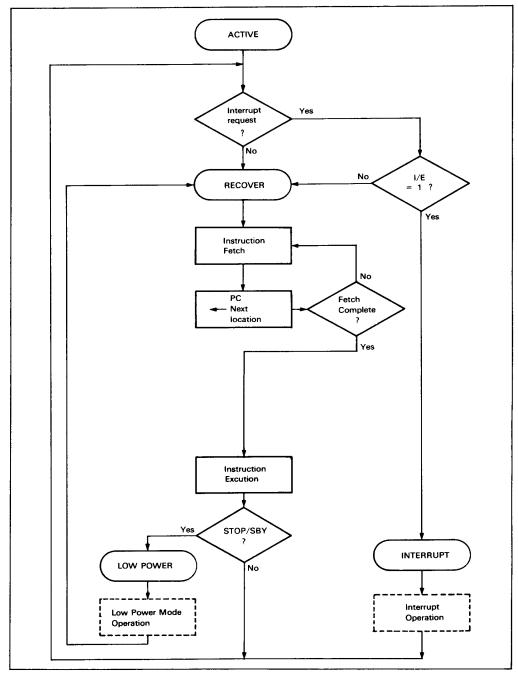

MCU Operation Sequence: The MCU operates according to the flowcharts shown in figures 13 and 14. The RESET is an asynchronous input, which resets the MCU regardless of the MCU state.

Figure 11. A Standby Mode Flowchart

Figure 12. Timing Diagram When Canceling Stop Mode

Figure 13. MCU Operation Sequence (MCU Operation Cycle)

(C) HITACHI

Figure 14. MCU Operation Sequence (Low Power Mode Operation)

#### PLL Function

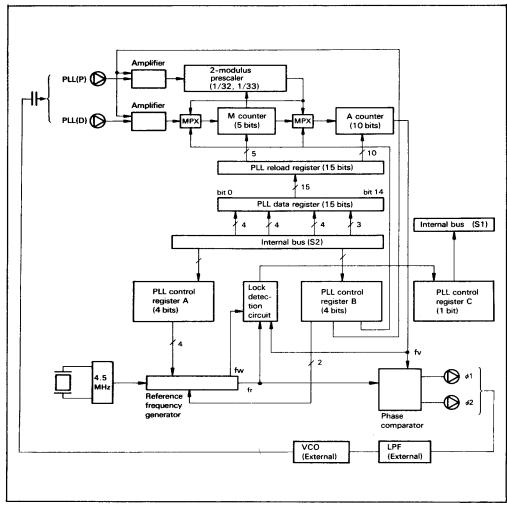

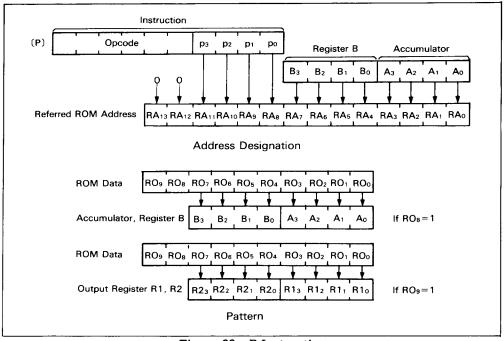

The PLL function performs phase comparison between an external input signal and an internal reference signal, and outputs a comparison result signal. Block diagram is shown in figure 15.

#### PLL Features:

- 12 programmable reference frequencies (1, 2, 5, 6.25, 9, 10, 12.5, 18, 20, 25, 50, 100 kHz)

- · Two dividing modes

- —Pulse swallow mode divide ratio: 1024 to (2<sup>15</sup> - 1)

- -Direct mode

- divide ratio: 4 to  $(2^{15} 1)$

- Two independent comparison output signal pins

- · PLL lock detection function

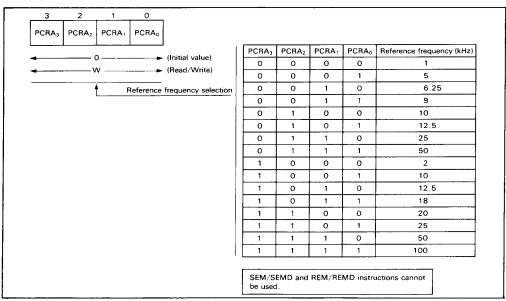

Reference frequency generator: The reference frequency generator divides source oscillation (4.5 MHz) to generate twelve different reference frequencies  $f_r$ : 1, 2, 5, 6.25, 9, 10, 12.5, 18, 20, 25, 50, and 100 kHz. Any of them can be selected by programming bit 0 to bit 3 of PLL control register A (PCRA<sub>0</sub>-PCRA<sub>3</sub>).

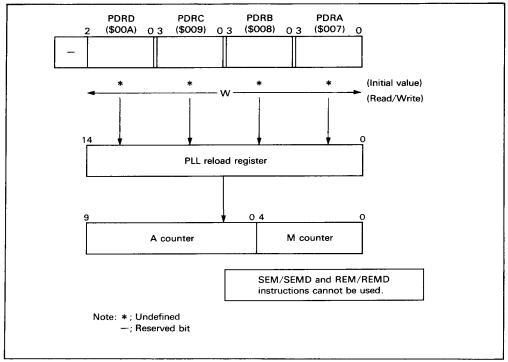

**Variable divider:** The variable divider is a down-counter composed of a 5-bit M counter and a 10-bit A counter. In direct dividing

mode, the variable divider functions as a 15bit down-counter with connected M and A counters to perform the auto-reload function. In pulse swallow dividing mode, both M and A counters function as down-counters which input 2-modulus prescaler (mode 1/33) output. When the M counter reaches 0, 2modulus prescaler mode changes from 1/33 to 1/32, and the A counter continues to count. When the A counter reaches 0, the M and A counters are auto-reloaded and start counting again. The dividing mode (direct or pulse swallow) can be selected by programming bit 2 of PLL control register B (PCRB2). Divide value should be set in the PLL data register. The value is set in the PLL reload register via the PLL data register. The contents of the PLL data register (15 bits) are loaded in the PLL reload register automatically by the write instruction to the lower four bits of the PLL data register (PDRA register). Therefore, data must be written in the registers in the following order: PDRD, PDRC, PDRB, and PDRA.

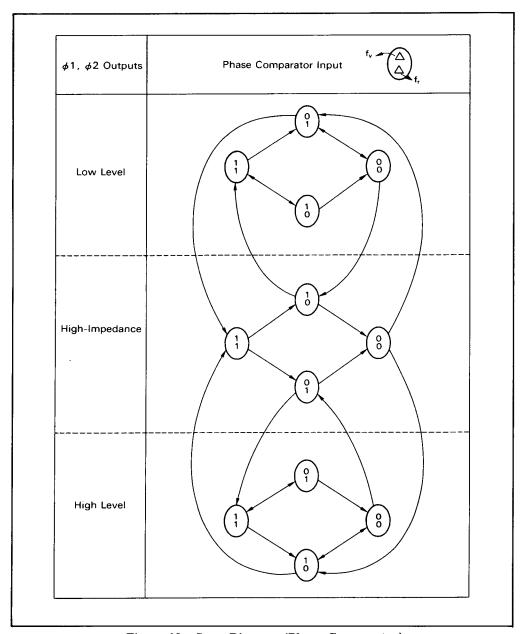

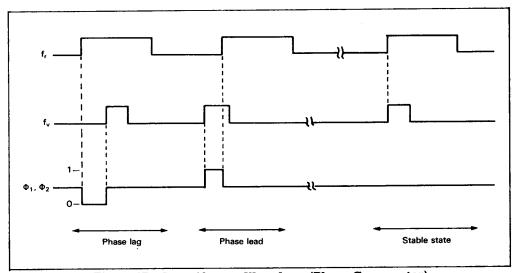

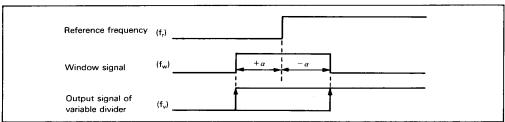

**Phase comparator:** The phase comparator detects phase difference between the reference frequency  $(f_r)$  and the output signal  $(f_v)$  from the variable divider. The result is output from the  $\phi 1$  and  $\phi 2$  pins, as shown in figure 16, figure 17.

Figure 15. PLL Function Block Diagram

Figure 16. State Diagram (Phase Comparator)

Figure 17. Input/Output Waveform (Phase Comparator)

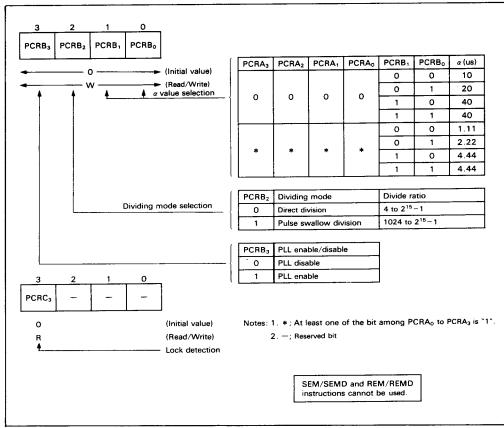

**Lock detection circuit:** If the phase difference between the reference frequency  $(f_r)$  and a signal  $(f_v)$  generated by dividing an external input signal through the variable divider is less than a specified value  $\pm \alpha$ , PLL is assumed to be locked and bit 3 of the PLL control register C (PCRC<sub>3</sub>) is set. The set condition of PCRC<sub>3</sub> is shown in figure 18. PCRC<sub>3</sub> is reset automatically after being read. Note: Value  $\alpha$  varies with programming bit 0 and bit 1 of PLL control register B (PCRB<sub>0</sub>, PCRB<sub>1</sub>).

When entering the stop mode, set PCRB<sub>3</sub> to 0 and PLL is disabled. PLL (P) and PLL (D) are pulled down to the GND so that current is not consumed by the alternate amplifier.

PLL control register A (PCRA: \$005): PLL control register A is a 4-bit write-only register (figure 19).

PLL control registers B, C (PCRB: \$006, PCRC: \$006): PLL control register B is a 4-bit write-only register. PLL control register C is a 1-bit read-only register(figure 20).

PLL data register A (PDRA: \$007)

PLL data register B (PDRB: \$008)

PLL data register C (PDRC: \$009)

PLL data register D (PDRD: \$00A): PLL

data registers A, B and C are 4-bit write-only

registers, and PLL data register D is a 3-bit

write-only register (figure 21).

Figure 18. PCRC<sub>3</sub> SET Condition

Figure 19. PLL Control Register A (PCRA: \$005)

**@HITACHI**

Figure 20. PLL Control Register B, C (PCRB: \$006, PCRC: \$006)

Figure 21. PLL Data Register and PLL Reload Register

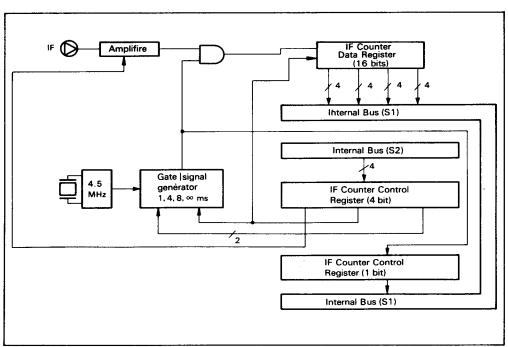

#### **IF** Counter

### IF Counter Features:

· Resolution: 16 bits

· Gate time: 1, 4, 8, ∞ ms

· Input signal: 15 MHz max.

IF Counter Function: The IF counter is a 16-bit binary counter whose data can be read. It is used to detect a stop signal during autosearch tuning; if a desired IF frequency range is found by counting the input frequency of the IF pin during auto-search tuning, it can be assumed that a radio station exists on the received frequency. The block diagram of the IF counter is shown in figure 22.

Count time (gate signal) of the IF counter can be selected from among 1, 4, 8 and  $\infty$  ms by the IF counter control register. After all, the frequency input to the IF pin can be measured by counting the number of pulses input to the IF counter within the selected count time.

The IF counter is reset by clearing the IF clear start bit of the IF counter control register, and initiates counting by setting the IF clear start bit. When the IF clear start bit is set, the busy bit is set, and when counting is terminated, it is cleared. Accordingly, whether or not counting is being performed can be acknowledged by software. Note that when entering into the stop mode, IFC13 must be set to 0 and the IF counter must be disabled. The IF pin is pulled down to the GND, so that current is not consumed by the alternate amplifier.

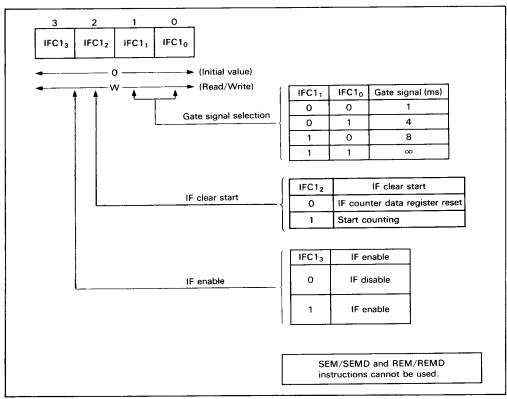

IF conter control register 1 (IFC1: \$028): IF counter control register 1 is a 4-bit write-only register (figure 23).

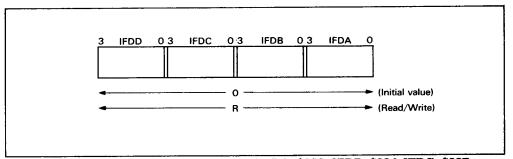

IF counter data register A (IFDA: \$029) IF counter data register B (IFDB: \$02A) IF counter data register C (IFDC: \$02B) IF counter data register D (IFDD: \$02C): IF counter data registers A to D are 4-bit read-only registers. The most significant digit is IFDD, the other bits are, in order: IFDC, IFDB, and IFDA (figure 24).

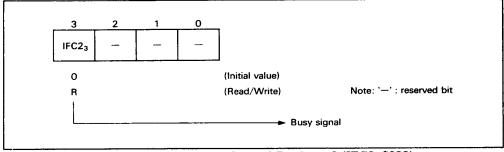

**IF** counter control register 2 (**IFC2**: \$028): IF counter control register 2 is a 1-bit read-only register (figure 25).

Figure 22. IF Counter Block Diagram

**@HITACHI**

**Gate Signal:** The IF counter's gate signal time is specified by the IF counter control register 1. The basic clock timing is a 1 ms pulse generated asynchronously with an instruction. Dividing this clock produces a 1, 4, or 8 ms gate signal. (Gate signal is selected among 1, 4, 8,  $\infty$  ms.) Accordingly, even if the IF clear start bit of the IF counter control register 1 is set to initiate counting, the IF counter does not start counting until the first basic clock is generated after executing the current instruction. Time difference between the busy bit and the actual gate signal is max. 1 ms, independent of the specified gate time, since basic clock timing is 1 ms.

Note: Precautions when gate signal  $\infty$  is selected.

When gate signal  $\infty$  is selected, the counter always operates by the IF input signal. Consequently, if data is read at counter update wrong data may be read. Thus, a gate must

be closed once before data is read. To close a gate in the  $\infty$  mode, a value other than  $\infty$  should be set in the gate signal selection bits (bit 1, 0) during setting of the IF enable bit (bit 3) and IF clear start bit (bit 2) of the IF counter control register 1 to 1.

To continue counting after data read, the  $\infty$  mode should be set again. Make certain that the counter does not operate while the gate is being closed.

Accordingly, gate closure time should be considered when counting continues after data read.

When gate signal  $\infty$  is selected, the IF counter does not start counting until the first basic clock is generated after executing the current instruction (max. 1 ms) even if the IF clear start bit of the IF counter control register is set to initiate counting.

Busy signal is invalid for the gate signal  $\infty$  mode

Figure 23. IF Counter Control Register 1 (IFC1: \$028)

**(D)** HITACHI

# HD404508, HD4074509

Figure 24. IF Counter Data Register (IFDA: \$029, IFDB: \$02A,IFDC: \$02B, IFDD: \$02C)

Figure 25. IF Counter Control Register 2 (IFC2: \$028)

#### Serial Interface

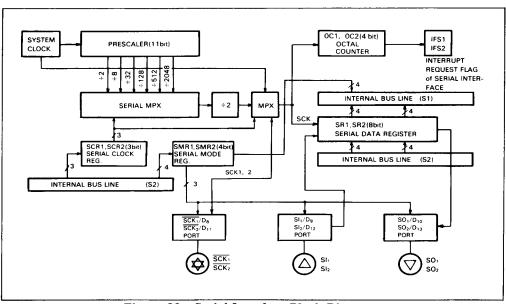

The serial interface is used to transmit/receive 8-bit data serially. The MCU has two serial interfaces, serial 1 and serial 2. The serial interfaces consist of the serial data registers (SR1, SR2), the serial mode registers (SMR1, SMR2), the serial clock registers (SCR1, SCR2), the octal counter, and the multiplexer as illustrated in figure 26.

Pins  $D_8/\overline{SCK_1}$ ,  $D_{11}/\overline{SCK_2}$ ,  $D_9/\overline{SI_1}$ ,  $D_{12}/\overline{SI_2}$ ,  $D_{10}/\overline{SO_1}$ ,  $D_{13}/\overline{SO_2}$ , and STS instruction are controlled by the serial mode register. The serial clock register controls the transfer clock. The contents of the serial data register can be written into or read out by software. The data in the serial data register can be shifted synchronously with the transfer clock signal.

Serial interface operation is initiated by the STS instruction while the enable bit of the target serial interface (bit 3 of the serial mode register of each serial interface) is set. The octal counter is reset to \$0 by the STS instruction. The counter starts to count at the

$\frac{falling}{SCK_2} \ \text{and increments by one at the rising edge of the signals}.$

When the octal counter is reset to \$0 after eight transfer clock signals, or when a transmit/receive operation is discontinued by resetting the octal counter, the serial interrupt request flag will be set.

To control two serial interfaces by executing the STS instruction once, an enable bit (bit 3) of the serial mode register is provided for each serial interface. When the STS instruction is executed, the serial interface of which an enable bit is set starts to operate. If both enable bits are reset, the serial interface does not operate even if the STS instruction is executed. If both enable bits are set, two serial interfaces can be operated by executing the STS instruction once.

The enable bit is reset after the STS instruction execution automatically.

Consequently, to operate the serial interface, the STS instruction should be executed after setting an enable bit.

Figure 26. Serial Interface Block Diagram

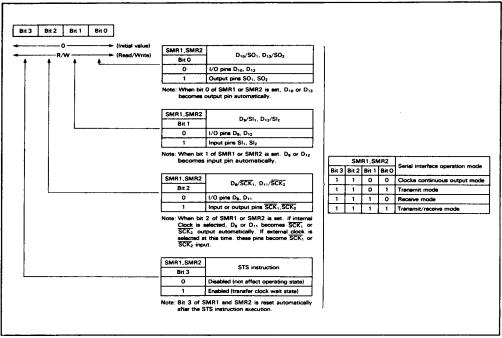

Serial Mode Registers (SMR1: \$010, SMR2: \$014): The 4-bit write-only serial mode registers control the serial interface operation and the pins  $\overline{SCK_1}$ ,  $\overline{SCK_2}$ ,  $SI_1$ ,  $SI_2$ ,  $SO_1$ , and  $SO_2$  as shown in figure 27.

The write signal to the serial mode register initializes the operating state of the serial interface.

The write signal to the serial mode register stops the serial data register and octal counter from applying transfer clock, and it also resets the octal counter to \$0 simultaneously. Therefore, when the serial interface is in the "Transfer State", the write signal causes the serial mode register to cease the data transfer and to set the serial interrupt request flag.

The contents of the serial mode register is invalid until the second instruction is executed after a write instruction. Therefore, it will be necessary to execute the STS instruction after the data in the serial mode register has been changed completely. The serial mode register will be reset to \$0 by MCU reset.

Bit 3 of the serial mode register is an enable bit for the serial interface. To operate the serial interface, this bit should be set before executing the STS instruction.

If the STS instruction is executed while the enable bit is set, the serial interface starts to operate. If the STS instruction is executed while the enable bits of both serial interfaces are set, two serial interfaces start to operate. The internal clocks of SERIAL 1 and SERIAL 2 are asynchronous each other.

The enable bit is automatically reset after the STS instruction execution.

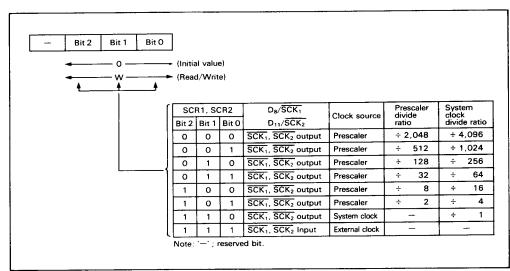

Serial Clock Registers (SCR1: \$011, SCR2: \$015): The serial clock register is a 3-bit write-only register which controls the transfer clock source and prescaler divide ratio as shown in figure 28. A write signal to the serial clock register initializes internal state of the serial interface. A write signal to the serial clock register stops the serial data register and octal counter from applying transfer clock, and it resets the octal counter. Therefore, when the serial interface is in the transfer state, the write signal to the serial clock register stops the data transfer and sets the serial interrupt request flag.

Serial Data Registers (SR1L: \$012, SR1U: \$013, SR2L: \$016, SR2U: \$017): The 8-bit read/write serial data register consists of a lower digit (SR1L: \$012, SR2L: \$016) and a higher digit (SR1U: \$013, SR2U: \$017).

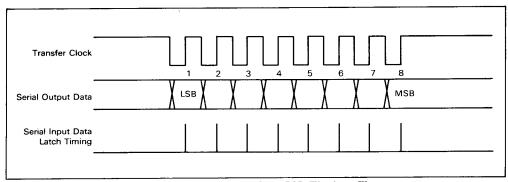

The data in the serial data register will be output from the  $SO_1$  and  $SO_2$  pins, from LSB to MSB, synchronously with the falling edge of the transfer clock. At the same time, external data will be input from the  $SI_1$  and  $SI_2$  pins to the serial data register, to LSB first, synchronously with the rising edge of the transfer clock. Figure 29 shows the I/O timing chart for the transfer clock signal and the data. The read/write operations of the serial data register should be performed after the completion of data transmit/receive.

Otherwise the data may not be guaranteed.

Figure 27. Serial Mode Register (SMR1: \$010, SMR2: \$014) and Operation Mode Selection

Table 9. Serial Interrupt Request Flag (IFS2: \$003,2, IFS1: \$023,2)

| Interrupt Requests |  |  |

|--------------------|--|--|

|                    |  |  |

|                    |  |  |

| -                  |  |  |

Reset by the REM and REMD instruc-Note: tions. 1 cannot be set by software. Tested by the TM and TMD instructions.

Table 10. Serial Interrupt Mask (IMS2: \$003, 3, IMS1: \$023, 3)

| Interrupt Requests |  |  |

|--------------------|--|--|

| Enabled            |  |  |

| Masked (held)      |  |  |

|                    |  |  |

Initial value: 1, R/W

REM, REMD, SEM, SEMD, TM, and Note: TMD instructions can be used.

Figure 28. Serial Clock Register (SCR1: \$011, SCR2: \$015)

Figure 29. Serial Interface I/O Timing Chart

## HD404508, HD4074509

Serial Interrupt Request Flag (IFS1: \$023 bit 2, IFS2: \$003 bit 2): The serial interrupt request flag is set when the octal counter counts eight transfer clock signals, or when data transfer is discontinued by resetting the octal counter. See table 9.

Serial Interrupt Mask (IMS1: \$023 bit 3, IMS2: \$003 bit 3): The serial interrupt mask masks the interrupt request. See table 10.

Selection and Change of the Operation Mode: The serial interface operation modes which are determined by a combination of the value in the serial mode register are shown in figure 27.

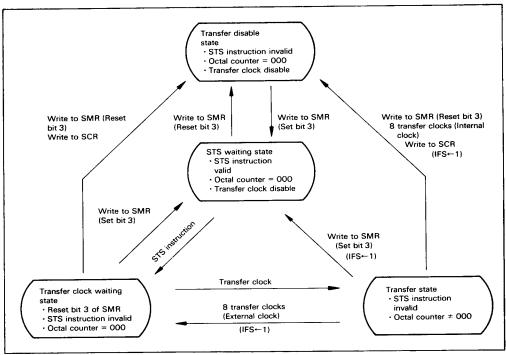

Operating State of Serial Interface: The serial interface has four operating states, transfer disable state, STS waiting state, transfer clock waiting state, and transfer state, as shown in figure 30.

The transfer disable state is the initialization state of the serial interface. In this state, the serial interface does not operate even if the STS instruction is executed or the transfer clock is applied. Setting the enable bit of the desired serial interface enters it into STS waiting state.

When the STS instruction is executed in this state, the serial interface becomes transfer clock waiting state and serial transfer is enabled. When both enable bits of the serial interface 1 and 2 are set before executing the STS instruction, two serial interfaces start to

operate. If the transfer clock is applied during the transfer clock waiting state, the serial interface changes to transfer state, while the octal counter counts up and the serial data register changes simultaneously. However, if the consecutive clock output mode is selected, only transfer clock is output consecutively without transfer.

In the transfer state, the octal counter becomes 000 by 8 transfer clocks and the serial interrupt flag is set. At this time, if internal clock is selected, the serial interface changes to the transfer disable state, and if external clock is selected, it changes to the transfer clock waiting state. A write signal to the serial mode register during the transfer state resets the octal counter to 000 to stop transfer and sets the interrupt request flag simultaneously.

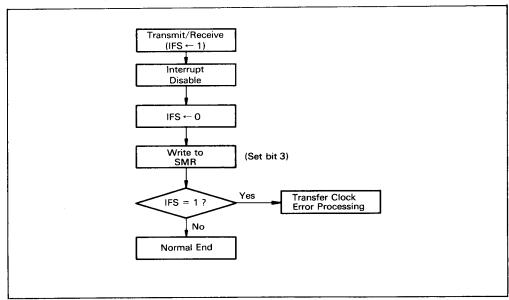

Example of Transfer Clock Error Detection: The serial interface malfunctions when the transfer clock is disturbed by external noises. In this case, transfer clock error can be detected by the procedure shown in figure 31. If more than 8 transfer clocks are applied in the transfer clock waiting state, the state of the serial interface changes as the following sequence: first, transfer state, second, transfer clock waiting state, and third, transfer state again. The serial interrupt flag should be reset before entering into the STS waiting state by writing data to the serial mode register. This procedure causes the serial interrupt request flag to be set again.

Figure 30. Operating State of Serial Interface

Figure 31. Example of Transfer Clock Error Detection

(C) HITACHI

#### Timer

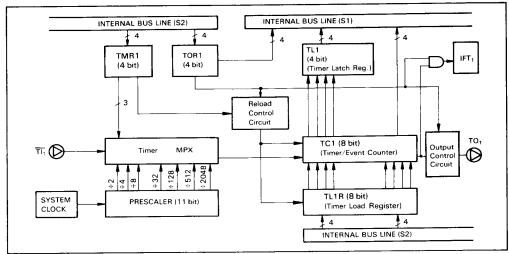

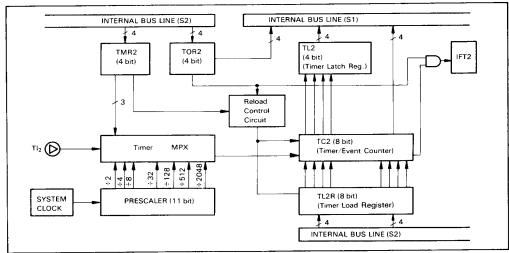

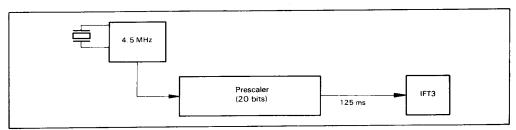

The MCU contains a prescaler, two timer/counters (timer-1, 2) and time-base prescaler (timer 3). Figures 32, 33 and 34 show the block diagrams of the timers.

Prescaler: The input to the prescaler is a system clock signal. The prescaler is initialized to \$000 by MCU reset before dividing the system clock. The prescaler keeps counting up except in MCU reset and stop mode. Timer input clock and serial transfer clock are selected by the timer mode registers (TMR1, TMR2) and serial clock registers (SCR1, SCR2) among prescaler outputs.

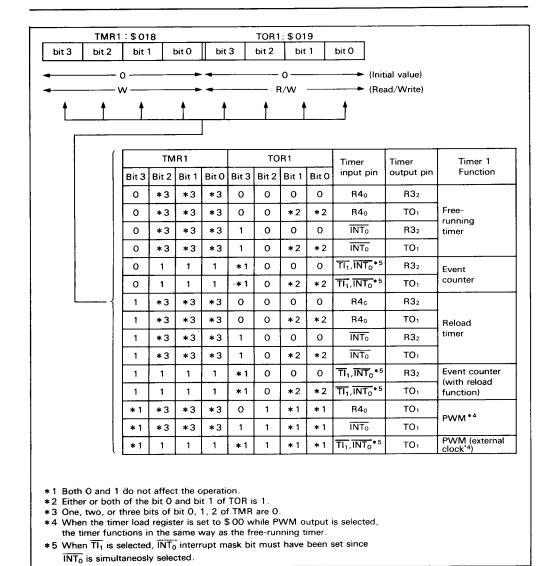

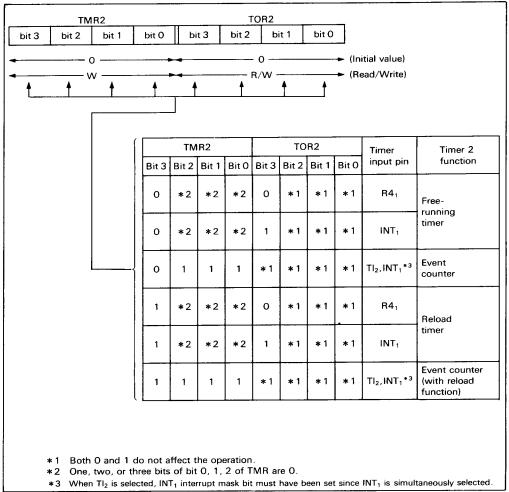

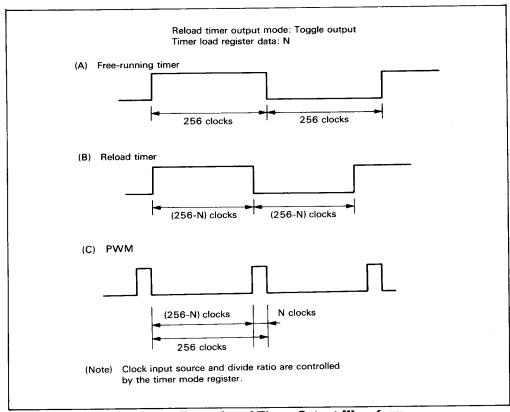

Operation of Timer 1, Timer 2: Timer 1 and 2 are multifunctional timers. They can be used as a free-running timer, event counter, reload timer, or PWM circuit (Timer 2 does not have a PWM function). Each function is selected by the timer mode register (TMR1, TMR2) and timer output register (TOR1, TOR2).

The timer/counter (TC1, TC2) is initialized to \$00 by MCU reset, and it starts to count up every input signal. As an input clock, the clock divided by the prescaler and an external clock can be used. When an external clock input is selected, external interrupt must be inhibited by setting the external interrupt mask bit (IM0 or IM1) since the external clock input pin is multiplexed with the external interrupt pin. (External interrupt cannot be inhibited by setting the interrupt enable bit of the timer output register.) If an input clock is applied after the timer counter reaches \$FF, the timer interrupt request flag (IFT1, IFT2) is set. If an auto-reload function is not selected, timer 1 and 2 function as free-running timer/event counter and continue to count up after returning to \$00. If the autoreload function is selected, they are reload timers.

The timers initiate counting up from the timer load register (TLR1, TLR2) value loaded in the timer counter for each clock input after the timer counter reaches \$FF.

Timer 1 has a timer output circuit. This circuit changes output level when a clock is input after the timer counter reaches \$FF. An optional cycle clock signal can be output by combining this circuit and the reload timer. Also this output circuit becomes PWM output circuit if PWM function is specified by the timer output register. One cycle of the PWM output is 256 input clocks. The output becomes 1 during the time for the number of clocks set in the timer load register, and becomes 0 during the other time.

To obtaine the voltage level in proportion to the value set in the timer load register, PWM output should be combined with low-pass filter.

**Timer 3 Operation:** Timer 3 is a prescaler which sets interrupt request flag (IFT3) every 125 ms.

- Timer interrupt request flag (IFT3: \$000 bit 2)

- · Timer interrupt mask (IMT3: \$000 bit 3)

The timer interrupt mask masks the timer 3 interrupt request.

Timer 3 is initialized in the following condition

- · Power-on Reset

- · MCU Reset when the data retention bit (MIS<sub>3</sub>: \$004,3) is 0.

Figure 32. Timer 1 Block Diagram

Figure 33. Timer 2 Block Diagram

Figure 34. Timer 3 Block Diagram

**@HITACHI**

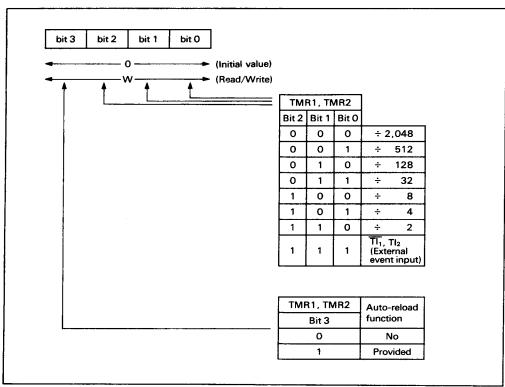

Timer Mode Register 1, 2 (TMR1: \$018, TMR2: \$01C): The timer mode register is a 4-bit write-only register which selects the autoreload function, input clock, and prescaler divide ratio as shown in figure 35.

The timer mode register is initialized to \$0 by MCU reset.

The operation mode of the timer mode register is changed at the second instruction cycle after the timer mode register is written to. Initialization of the timer by a write to the timer mode register should be performed after the operation mode is completely changed.

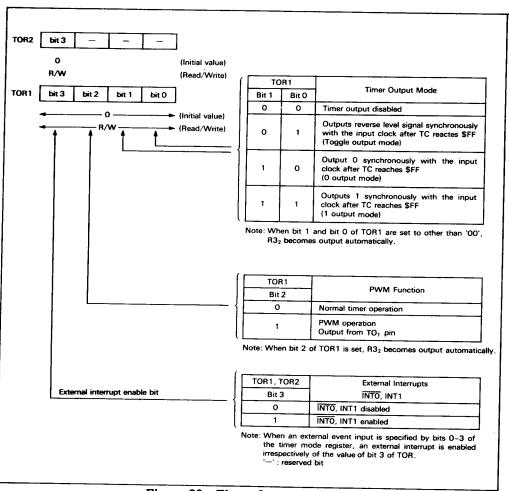

Timer Output Register (TOR1: \$019, TOR2: \$01D): The timer output register is a 4-bit read/write register which controls the

timer output mode, PWM output, and external interrupts as shown in figure 36.

If bit 0 and 1 of the timer output register are set in the mode except for timer output disable mode, the pin becomes timer output pin automatically.

Combination of these modes and each mode of the timer 1 to 3 can produce optional frequency and optional duty clock signal. When PWM output is set, the timer output pin becomes PWM output pin independently of the timer output mode.

The timer output register is initialized to \$0 by MCU reset.

The operation mode of the timer output register is changed at the second instruction cycle after the timer output register is written to.

Figure 35. Timer Mode Register 1, 2 (TMR1; \$018, TMR2; \$019)

Timer 1, 2 (TC1L: \$01A, TC1U: \$01B, TL1L: \$01A, TL1U: \$01B, TC2L: \$01E, TC2U: \$01F, TL2L: \$01E, TL2U: \$01F): Timer 1 and 2 consist of write-only timer load register (8 bits) and read-only timer/event counter (8 bits) respectively. Each of them has a lower digit (TC1L: \$01A, TC2L: \$01E) and a higher digit (TC1U: \$01B, TC2U: \$01F).

The timer/event counter can be initialized by writing data into the timer load register. In this case, write the lower digit first, and then the higher digit. The timer load register is initialized to \$00 by the MCU reset.

The counter value of the timer can be obtained by reading the timer/event counter. In this case, read the higher digit first, and then the lower digit. The count value of the

lower digit is latched at the time when the higher digit is read.

Timer Interrupt Request Flag (IFT1: \$002 bit 0, IFT2: \$003 bit 0): The timer interrupt request flag is set by the overflow output of timer 1 or timer 2. If the PWM function is selected, the timer interrupt request flag is not set even if the overflow output generates.

See table 11.

Timer Interrupt Mask (IMT1: \$002 bit1, IMT2: \$003 bit 1): The timer interrupt mask masks an interrupt request from timer 1 or timer 2.

See table 12.

Table 11. Timer Interrupt Request Flag

Timer Interrupt

Request Flag Interrupt Request

| nequest riag | Interrupt Request |  |  |

|--------------|-------------------|--|--|

| 0            | No                |  |  |

| 1            | Yes               |  |  |

Initial value: 0, R/W

## Table 12. Timer Interrupt Mask

| Interrupt Request |

|-------------------|

| Enabled           |

| Disabled (masks)  |

|                   |

Initial value: 1, R/W

Figure 36. Timer Output Register

Operating Mode of Timer 1, Timer 2: Since timer 1 and timer 2 can select several functions as free-running, reload, PWM (timer 1 only), and can control clock input and timer output, various operating states can be specified by combination of these functions as shown in figure 37, 38. Required data should

be set in the timer mode register and timer output register for the selected operating state.

Example of the timer output waveform is shown in figure 39. The waveform depends on the operation mode.

Figure 37. Combination of Timer 1 Operation Modes

**@HITACHI**

Figure 38. Combination of Timer 2 Operation Modes

Figure 39. Examples of Timer Output Waveform

#### A/D Converter

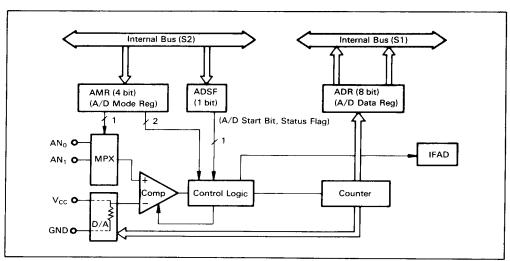

The MCU incorporates an A/D converter operating in the sequential comparison method with a resistor ladder. It can measure two analog inputs with 8-bit resolution. A block diagram of the A/D converter is shown in figure 40.

The A/D converter is composed of the following registers and bit.

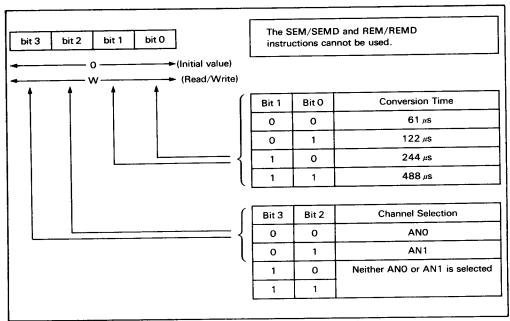

**A/D mode register (AMR: \$00C):** The A/D mode register is a write-only register. Bits 0 and 1 select an A/D conversion period, and bits 2 and 3 select a channel (figure 41).

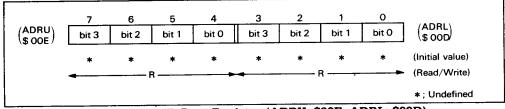

A/D data register (ADRU: \$00E, ADRL: \$00D): The A/D data register is a read-only register.

Data read during A/D conversion is not guaranteed. After completion of a conversion,

resulting data is maintained until the following conversion starts (figure 42).

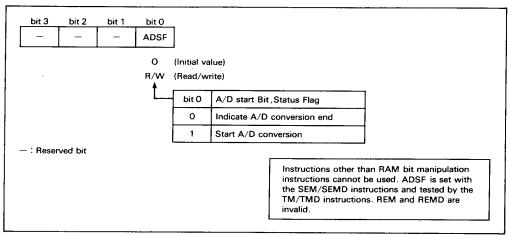

A/D start bit, status flag (ADSF: \$020, 0): Writing 1 into the A/D start bit initiates A/D conversion. On completion of A/D conversion, the converted data is stored in the A/D data register simultaneously with setting the A/D interrupt flag, and the A/D start flag is cleared.

Note that writing into ADSF should be parformed by bit manipulation instruction SEM or SEMD. It is invalid with the REM/REMD instructions. ADSF must not be written to during A/D conversion. The configuration of ADSF is shown in figure 43.

#### Precautions on A/D converter use:

Port output instructions should not be executed during A/D conversion to allow the A/D converter to operate stably.

Figure 40. A/D Converter Block Diagram

Figure 41. A/D Mode Register (AMR: \$00C)

Figure 42. A/D Data Register (ADRU: \$00E, ADRL: \$00D)

1319

# HD404508, HD4074509

Figure 43 A/D Start Bit, Status Flag (ADSF: \$020,0)

## Liquid Crystal Display Circuit

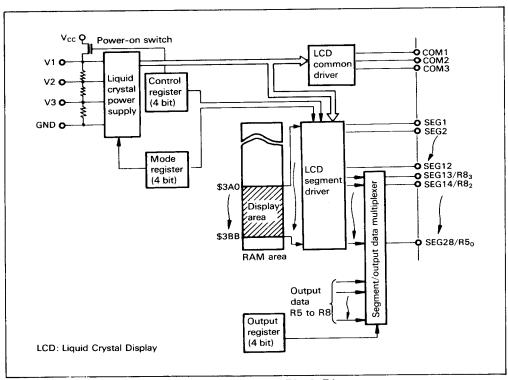

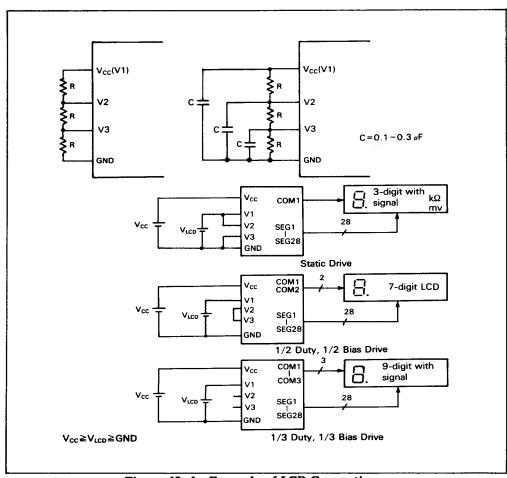

A LCD circuit can directly drive a liquid crystal in three drive systems, static, 1/2 duty, and 1/3 duty with its three common signal pins and 28 segment signal pins. The LCD circuit is comprised of RAM, controller, and driver as shown in figure 44.

RAM (\$3A0-\$3BB): RAM in the LCD circuit is dual-port RAM which sends display data to the segment signal pin without software. Relation between display RAM area and segment signal is shown in figure 45. By writing data in RAM area, the corresponding

segment pin automatically outputs it as display data. 1 means light on, and 0 means light off

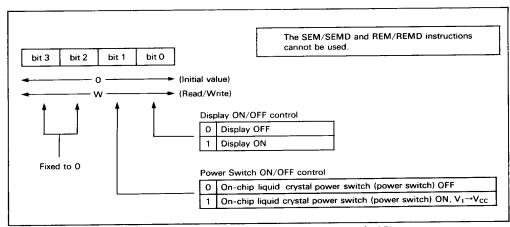

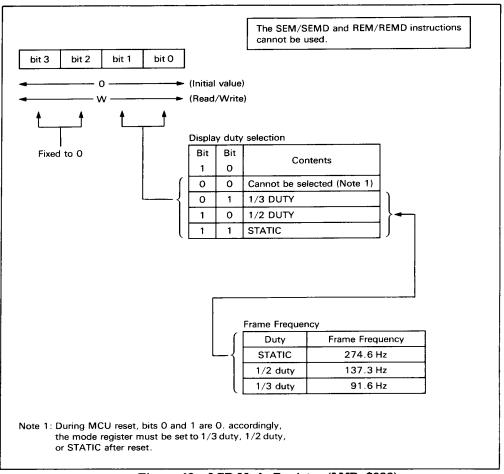

**Control Section:** The control section consists of the following three registers:

- $\cdot$  LCD output register (LOR: \$024) (figure 46)

- · LCD control register (LCR: \$025) (figure 47)

- · LCD mode register (LMR: \$026) (figure 48)

**LCD Driver:** The LCD driver has three common signal pins and 28 segment signal pins. 16 segment pins SEG13 to SEG28 are multiplexed with output ports R8, R7, R6, and R5.

Figure 44. LCD Circuit Block Diagram

|       |        |        |        | Address       |

|-------|--------|--------|--------|---------------|

| BIT 3 | BIT 2  | BIT 1  | BIT O  | (Hexadecimal) |

|       | SEG 1  | SEG 1  | SEG 1  | \$3A0         |

|       | SEG 2  | SEG 2  | SEG 2  | \$3A1         |

|       | SEG 3  | SEG 3  | SEG 3  | \$3A2         |

|       | SEG 4  | SEG 4  | SEG 4  | \$3A3         |

|       | SEG 5  | SEG 5  | SEG 5  | \$3A4         |

|       | SEG 6  | SEG 6  | SEG 6  | \$3A5         |

|       | SEG 7  | SEG 7  | SEG 7  | \$3A6         |

|       | SEG 8  | SEG 8  | SEG 8  | \$3A7         |

|       | SEG 9  | SEG 9  | SEG 9  | \$3A8         |

|       | SEG 10 | SEG 10 | SEG 10 | \$3A9         |

|       | SEG 11 | SEG 11 | SEG 11 | \$3AA         |

|       | SEG 12 | SEG 12 | SEG 12 | \$3AB         |

|       | SEG 13 | SEG 13 | SEG 13 | \$3AC         |

|       | SEG 14 | SEG 14 | SEG 14 | \$3AD         |

|       | SEG 15 | SEG 15 | SEG 15 | \$3AE         |

|       | SEG 16 | SEG 16 | SEG 16 | \$3AF         |

|       | SEG 17 | SEG 17 | SEG 17 | \$3BO         |

|       | SEG 18 | SEG 18 | SEG 18 | \$3B1         |

|       | SEG 19 | SEG 19 | SEG 19 | \$3B2         |

|       | SEG 20 | SEG 20 | SEG 20 | \$3B3         |

|       | SEG 21 | SEG 21 | SEG 21 | \$3B4         |

|       | SEG 22 | SEG 22 | SEG 22 | \$3B5         |

|       | SEG 23 | SEG 23 | SEG 23 | \$3B6         |

|       | SEG 24 | SEG 24 | SEG 24 | \$3B7         |

|       | SEG 25 | SEG 25 | SEG 25 | \$3B8         |

|       | SEG 26 | SEG 26 | SEG 26 | \$3B9         |

|       | SEG 27 | SEG 27 | SEG 27 | \$3BA         |

|       | SEG 28 | SEG 28 | SEG 28 | \$3BB         |

|       | сомз   | COM2   | COM1   |               |

Note: Some areas do not correspond to a segment signal. They can be read/written to.

Figure 45. LCD RAM Area and Segment Signals

Figue 46. LCD Output Register (LOR: \$024)

Figure 47. LCD Control Register (LCR: \$025)

Figure 48. LCD Mode Register (LMR: \$026)

Large LCD Panel Driving and Driving Voltage (VLCD): When using the large LCD panel, lower the dividing resistance by implementing the external resistors parallel to the internal dividing resistors as shown in figure 49.

Since the liquid crystal display board is of matrix configuration, the path of the charge/discharge current through the load capacitors is very complicated. Moreover, as it varies depending on display condition, a value of resistance cannot be simply determined by referring to the load capacitance of liquid

crystal display. A value of resistance must be experimentally determined according to the demand for power consumption of the equipment in which the liquid crystal display is implemented. (A capacitor, C=0.1 to 0.3  $\mu$ F can be used if necessary.) In general, R is 1 k $\Omega$  to 10 k $\Omega$ .

The following figure shows a connection when changing the liquid crystal driving voltage ( $V_{LCD}$ ). In this case, power supply switch for dividing resistor (power switch) should be turned OFF. (Bit 1 of the LCR register is 0).

Figure 49. An Example of LCD Connection

## Input/Output Port

The MCU has 47 I/O pins comprising 29 I/O pins, 2 input pins, and 16 output pins (multiplexed with SEG pins). The I/O ports (D, R0-R3) have individual data direction registers so that data direction (I/O) can be selected for each bit.Port R4 is an input port. All ports are standard ports. The registers which control the I/O ports of each module are shown in figure 52.

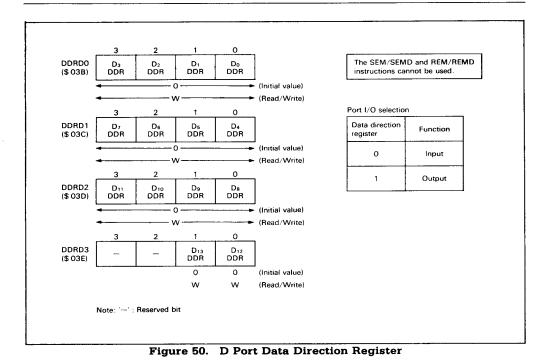

**Port D** ( $D_0$ - $D_{13}$ ): The D port is an I/O port composed of 14 I/O pins accessed on a bit basis. All bits of the port D data register are set to 1 by MCU reset. Data direction (input/output) of each pin can be selected by the data direction register provided for each bit (0: input, 1: output). The data direction register is cleared by reset, so that the D port becomes an input port by reset. (See figure 50.) The D port can be set and reset by the SED/RED and SEDD/REDD instructions, and can be tested by the TD/TDD instructions. Pins  $D_0$ - $D_2$  and  $D_8$ - $D_{13}$  are multiplexed with INT<sub>2</sub>, INT<sub>3</sub>, INT<sub>4</sub>,  $\overline{SCK_1}$ , SI<sub>1</sub>, SO<sub>1</sub>,  $\overline{SCK_2}$ , SI<sub>2</sub>, and SO<sub>2</sub>, respectively.

Ports R0-R3: These are the I/O ports accessed in 4-bit units. The initial value of the port R data register by MCU reset depends on the value of the data retention bit. When it is 0, register value is 1, when it is 1, the register value before reset is retained. Data direction (input/output) of each bit of port R can be controlled by the port R data direction register (DDR0-DDR3) (0: input, 1: output). Since the data direction register is cleared by reset, the R port becomes an input port by reset. However, when the data retention bit is 1, I/O direction of the R port remains unchanged since the previous data is maintained without being cleared. (See figure 51.)

Data is input as well as output through ports R0-R3 by the LAR and LBR instruction.

Pin R3 $_2$  of port R3 is multiplexed with timer output pin TO $_1$ . TO $_1$  is an output pin of timer 1, which can output optional frequency clock and PWM output signal utilizing reload function. For details, see section "Timer".

Circuit types of I/O pins are shown in table 13.

Port R4: Port R4 is an input port accessed in 2-bit units. Pin R40 is multiplexed with external interrupt input  $\overline{INT_0}$  and timer input  $\overline{TI_1}$ , and R41 is multiplexed with external interrupt input INT1 and timer input TI2. Operation mode of each pin is selected by the timer mode register and timer output regis-

ter. (for details, see section "Timer".)

Data is input through port R4 by the LAR and

LBR instructions.

Circuit types of the R4 port pins are shown in table 13.

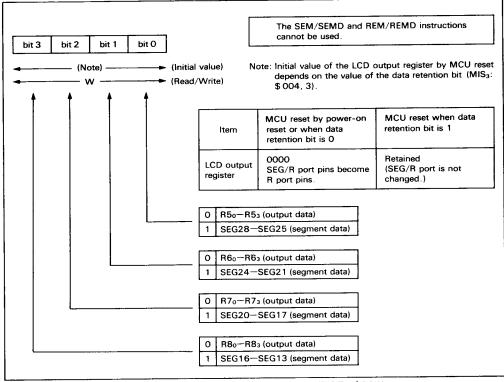

Ports R5-R8: These ports are output ports accessed in 4-bit units. Pins R5<sub>0</sub>-R5<sub>3</sub> are multiplexed with SEG28-SEG25; R6<sub>0</sub>-R6<sub>3</sub>, with SEG24-SEG21; R7<sub>0</sub>-R7<sub>3</sub> with SEG20-SEG17; and R8<sub>0</sub>-R8<sub>3</sub>, with SEG16-SEG13, respectively. Operation mode of each pin is selected by the LCD output register (for details, see section "LCD Circuit").

During reset, these ports are used as R ports and 1 is output. However, when the data retention bit is 1, these pins are not switched to R ports and 1 is not set in the data register, so that the previous data is maintained. Circuit types of the R5-R8 pins are shown in table 13.

Data Direction Register (\$030-\$033, \$03B-\$03E): The data direction register (DDR) is a 4-bit write-only register which controls input and output of the I/O ports. Each I/O port bit has a DDR and data direction can be selected on a bit basis. Data is input from each pin when a port is an input port. For an output port, data is accessed from the data register.

The I/O ports become input ports when DDR is cleared by reset. However, the R port data direction register is not cleared by reset when the data retention bit is 1, so that the previous data is retained.

D port data direction register (DDRD0: \$03B, DDRD1: \$03C, DDRD2: \$03D, DDRD3: \$03E): This register can select D port data direction on a bit basis. RAM bit manipulation instruction cannot be used. The D port becomes an input port by reset (figure 50).

R port data direction register (DDR0: \$030, DDR1: \$031, DDR2: \$032, DDR3: \$033): This register can select data direction for ports R0-R3 on a bit basis. RAM bit manipulation instruction cannot be used. When the R port data direction register is cleared by MCU reset, the R ports become input ports. However, if the data retention bit is 1, this register is not cleared by reset and the previous data is retained (figure 51). Note: I/O pins unused on the user system. If unused I/O pins are left floating, the LSI may malfunction because of noise. To prevent this, unused pins should be pulled up to  $V_{\rm CC}$  through a resistor of approximately 100 k $\Omega$ .

3 0 Port I/O selection Data direction DDRO RO<sub>3</sub> RO<sub>2</sub> RO<sub>1</sub> R<sub>0</sub>o Function (\$ 030) DDR DDR DDR DDR register \* \* (Initial value) 0 Input (Read/Write) 2 O Output DDR1 R11 R1o (\$ 031) DDR DDR DDR DDR Note 1: \*; The initial value of the \* (Initial value) R port data direction register by MCU reset (Read/Write) depends on the value 0 of the data retention DDR2 R23 R21 R<sub>2</sub>o bit (MIS<sub>3</sub>: \$004,3). (\$032)DDR DDR DDR \* (Initial value) Reset when Reset when power on reset data retention (Read/Write) Item and when data bit is 1 2 1 0 retention bit is 0 DDR3 R3<sub>2</sub> R3<sub>1</sub> R<sub>30</sub> R port 0000 Retained (\$033)DDR DDR DDR data R port becomes (R port function direction does not change (Initial value) input port register (Read/Write) Note 2: -; Reserved bit The SEM/SEMD and REM/REMD instructions cannot be used

Figure 51. R Port Data Direction Register

Table 13. Circuit Type of I/O Pins

| I/O Pins       | Circuit Type                            | Applied Pins                                                                                                                                                           |

|----------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O common pin | Input Signal Input data                 | D <sub>0</sub> -D <sub>13</sub>                                                                                                                                        |

|                | STOP DDR Output data                    |                                                                                                                                                                        |

| -              | Input signal Input data                 | R0-R3                                                                                                                                                                  |

|                | Output data                             |                                                                                                                                                                        |

|                | <i>th</i>                               | SCK <sub>1</sub> , SCK <sub>2</sub>                                                                                                                                    |

|                | STOP  I/O Select signal  SCK (internal) |                                                                                                                                                                        |

| Output pin     | SEG/R select signal                     | R5-R8                                                                                                                                                                  |

|                | Output data                             |                                                                                                                                                                        |

|                | V <sub>cc</sub> STOP                    | SO <sub>1</sub> , SO <sub>2</sub> ,<br>TO <sub>1</sub> (STOP = "1")                                                                                                    |

|                | Output data                             |                                                                                                                                                                        |

| Input pin      | Input signal Input data                 | R4                                                                                                                                                                     |

|                | <b>○</b>                                | INT <sub>0</sub> , INT <sub>1</sub> , INT <sub>2</sub><br>INT <sub>3</sub> , INT <sub>4</sub> , SI <sub>1</sub><br>SI <sub>2</sub> , TI <sub>1</sub> , TI <sub>2</sub> |

(1) HITACHI

Figure 52. I/O Mode Selection Registers

## HD404508, HD4074509

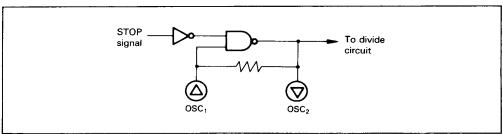

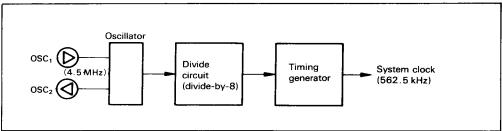

#### Oscillation Circuit

The oscillation circuit configuration is shown in figure 53.

Figure 54 shows an internal oscillation circuit block diagram. 4.5 MHz crystal should be attached.

Figure 55 is an example of a crystal oscillation circuit, and its layout example is shown in figure 56.

Notes: 1. The circuit parameters are changed by crystal resonator and the floating capacitance in the board. In employing a resonator, please consult with the engineers of the crystal maker to determine the actual

circuit parameter.

2. Wiring between OSC1, OSC2, and elements should be as short as possible, and never cross other wires. (See figure 56.)

Figure 53. Oscillator

Figure 54. Internal Oscillation Circuit

Figure 55. Crystal Oscillation Circuit

Figure 56. Crystal Oscillation Circuit Layout

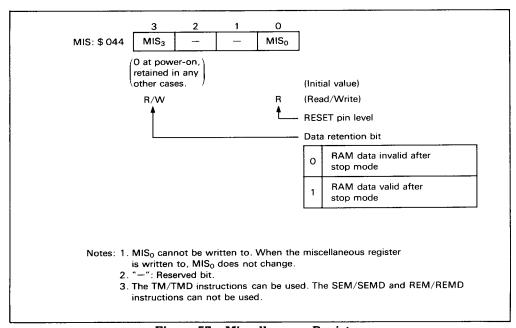

## Miscellaneous Register

The function of the miscellaneous register, shown in figure 57, is described below.

**RESET:** The RESET pin level can be read by reading the  $MIS_0$  bit.

Data retention bit: This bit is cleared if  $V_{\rm CC}$  voltage supply stops. This bit is set before the MCU enters into stop mode. Then, if this bit is set when the MCU recovers from stop mode by MCU reset,  $V_{\rm CC}$  voltage is applied during stop mode and RAM data is retained.

Figure 57. Miscellaneous Register

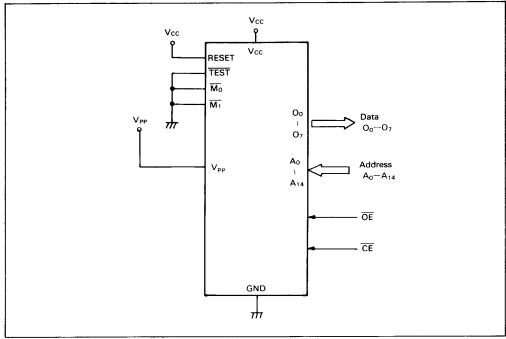

## **PROM Mode Pin Description**

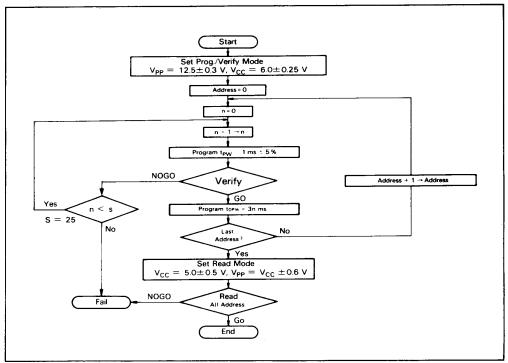

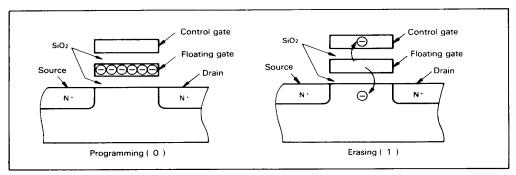

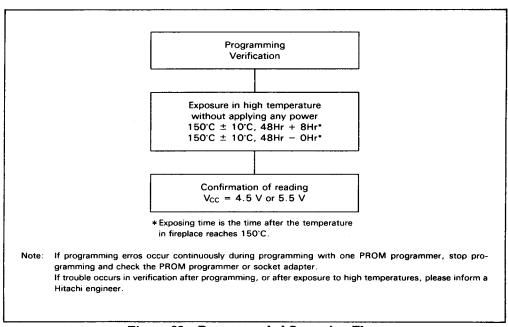

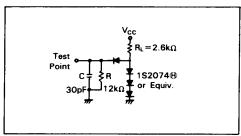

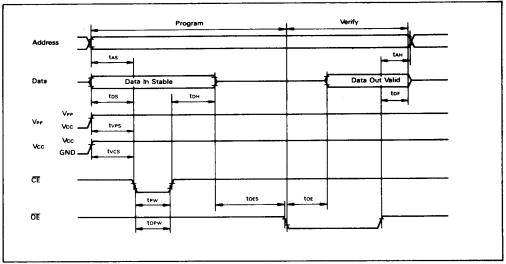

The HD4074509 is a ZTAT microcomputer incorporating PROM. When the MCU enters PROM mode, the MCU stops to program the