# HMCS42C(HD44700),-HMCS42CL(HD44708)

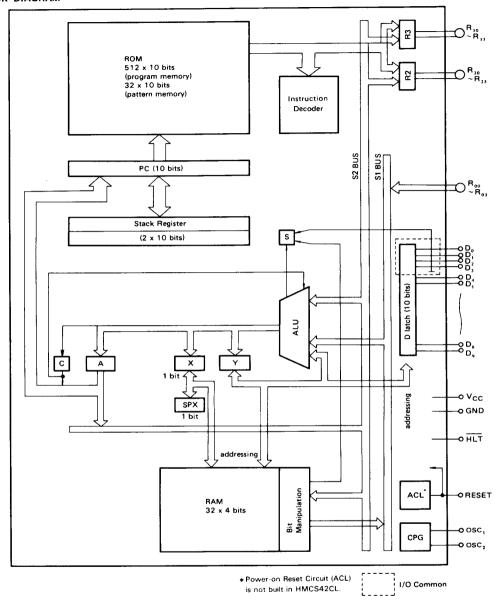

The HMCS42C is the CMOS 4-bit single chip microcomputer which contains ROM, RAM, and I/O on single chip. The HMCS42C is designed to perform efficient controller function as well as arithmetic function for both binary and BCD data. The CMOS technology of the HMCS42C provides the flexibility of microcomputers for battery powered and battery back-up applications.

### ■ FEATURES

- 4-bit Architecture

- 512 Words of Program ROM (10 bits/Word)

32 Words of Pattern ROM (10 bits/Word)

- 32 Digits of Data RAM (4 bits/Digit)

- 22 I/O Lines

- Instruction Cycle Time: HMCS42C; 10 μs HMCS42CL; 20 μs

- All Instructions except One Instruction; Single Word and Single Cycle

- BCD Arithmetic Instructions

- Pattern Generation Instruction

- Table Look Up Capability -

- Bit Manipulation Instructions for Both RAM and I/O

- Option of I/O Configuration Selectable on Each Pin; Pull Up MOS or CMOS or Open Drain

- Built-in Oscillator

- Built-in Power-on Reset Circuit (HMCS42C only)

- Low Operating Power Dissipation; 1.5mW typ.

- Stand-by Mode (Halt Mode); 50 μW max.

- CMOS Technology

- Single Power Supply: HMCS42C; 5V±10%

HMCS42Cl = 2.5V ± 5.5

HMCS42CL; 2.5V to 5.5V

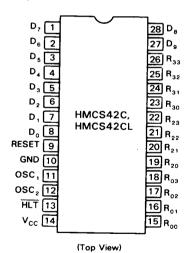

### **■ PIN ARRANGEMENT**

**₾HITACHI**

### ■ BLOCK DIAGRAM

(1) HITACHI

### ■ HMCS42C ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>=5V±10%)

### ABSOLUTE MAXIMUM RATINGS

| Item                             | Symbol            | Value                        | Unit | Remarks                                                                |

|----------------------------------|-------------------|------------------------------|------|------------------------------------------------------------------------|

| Supply Voltage                   | V <sub>cc</sub>   | -0.3 to +7.0                 | V    |                                                                        |

| Pin Voltage (1)                  | V <sub>T1</sub>   | -0.3 to V <sub>CC</sub> +0.3 | V    | Except for pins specified by V <sub>T2</sub>                           |

| Pin Voltage (2)                  | V <sub>T2</sub>   | -0.3 to +10.0                | V    | Applied to only open-drain output pins and open-drain I/O common pins. |

| Maximum Total Output Current (1) | -ΣI <sub>01</sub> | 45                           | mA   | [NOTE 3]                                                               |

| Maximum Total Output Current (2) | Σl <sub>o2</sub>  | 45                           | mA   | [NOTE 3]                                                               |

| Operating Temperature            | Topr              | -20 to +75                   | °C   |                                                                        |

| Storage Temperature              | T <sub>stg</sub>  | -55 to +125                  | °C   |                                                                        |

[NOTE 1] Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under the conditions of "ELECTRICAL CHARACTERISTICS-1, -2". If these conditions are exceeded, it could affect reliability of LSI.

[NOTE 2] All voltages are with respect to GND.

[NOTE 3] Maximum Total Output Current is total sum of output currents which can flow out (or flow in) simultaneously.

### • ELECTRICAL CHARACTERISTICS-1 (V<sub>CC</sub>=5V±10%, Ta=-20 to +75°C)

|                                        |                   | T                                                                               |                                                 |                      | Value |      | Unit | Note |

|----------------------------------------|-------------------|---------------------------------------------------------------------------------|-------------------------------------------------|----------------------|-------|------|------|------|

| Item                                   | Symbol            | rest Co                                                                         | onditions                                       | min                  | typ   | max  | Unit | Note |

| Input "Low" Voltage                    | V <sub>IL</sub>   |                                                                                 |                                                 | -                    | _     | 1.0  | ٧    |      |

| Input "High" Voltage (1)               | V <sub>IH1</sub>  |                                                                                 |                                                 | V <sub>CC</sub> -1.0 | _     | Vcc  | ٧    | 2    |

| Input "High" Voltage (2)               | V <sub>IH2</sub>  |                                                                                 |                                                 | V <sub>CC</sub> -1.0 | _     | 10   | ٧    | 3    |

| Output "Low" Voltage                   | VoL               | I <sub>OL</sub> = 1.6mA                                                         |                                                 | _                    | _     | 0.8  | V    |      |

| Output "High" Voltage (1)              | V <sub>OH1</sub>  | - I <sub>OH</sub> = 1.0m                                                        | nA                                              | 2.4                  | -     |      | ٧    | 4    |

| Output "High" Voltage (2)              | V <sub>OH2</sub>  | -I <sub>OH</sub> = 0.01                                                         | mA                                              | V <sub>CC</sub> -0.3 | _     | _    | V    | 5    |

| Output "High" Current                  | ГОН               | V <sub>OH</sub> = 10V                                                           |                                                 | _                    | -     | 3    | μΑ   | 6    |

|                                        |                   | V <sub>in</sub> =0 to V <sub>0</sub>                                            | cc                                              |                      |       | 1.0  |      | 2, 7 |

| Input Leakage Current                  | I <sub>IL</sub>   | V <sub>in</sub> =0 to 10                                                        | ov                                              |                      | _     | 3    | μΑ   | 7    |

| Pull up MOS Current                    | - I <sub>P</sub>  | V <sub>cc</sub> =5V                                                             |                                                 | 60                   |       | 250  | μΑ   |      |

| Supply Current (1)                     | l <sub>CC1</sub>  | V <sub>in</sub> =V <sub>CC</sub> ,<br>Ceramic Filter Oscillation                |                                                 | -                    | _     | 1.6  | mA   |      |

| Supply Current (2)                     | I <sub>CC2</sub>  | V <sub>in</sub> =V <sub>CC</sub> ,<br>R <sub>f</sub> Oscillatio<br>External Clo | n<br>ck Operation                               | -                    | -     | 0.8  | mA   |      |

|                                        |                   |                                                                                 | V <sub>in</sub> =0 to V <sub>CC</sub>           | _                    | _     | 1    | μΑ   | 2, 7 |

| Standby I/O Leakage Current            | ILS               | HLT=1.0V                                                                        | $V_{in} = 0$ to $V_{CC}$<br>$V_{in} = 0$ to 10V | 1                    |       | 3    | μΑ   | 8    |

| Standby Supply Current                 | lccs              | V <sub>in</sub> =V <sub>CC</sub> , H                                            |                                                 | _                    | _     | 10   | μΑ   | 9    |

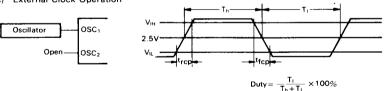

| External Clock Operation               |                   |                                                                                 |                                                 |                      |       |      |      |      |

| External Clock Frequency               | f <sub>cp</sub>   |                                                                                 |                                                 | 200                  | 400   | 440  | kHz  |      |

| External Clock Duty                    | Duty              |                                                                                 |                                                 | 45                   | 50    | 55   | %    |      |

| External Clock Rise Time               | t <sub>rcp</sub>  |                                                                                 |                                                 | 0                    | -     | 0.2  | μs   |      |

| External Clock Fall Time               | t <sub>fcp</sub>  |                                                                                 |                                                 | 0                    | -     | 0.2  | μs   |      |

| Instruction Cycle Time                 | T <sub>inst</sub> | T <sub>inst</sub> =4/f <sub>cp</sub>                                            |                                                 | 9.1                  | 10    | 20   | μs   |      |

| Internal Clock Operation (Rf Oscillati | on)               |                                                                                 |                                                 |                      |       |      |      | ·    |

| Clock Oscillation Frequency            | fosc              | R <sub>f</sub> =91kΩ±                                                           |                                                 | 300                  |       | 500  | kHz  |      |

| Instruction Cycle Time                 | T <sub>inst</sub> | T <sub>inst</sub> =4/f <sub>OS</sub>                                            | sc .                                            | 8.0                  | _     | 13.3 | μs   |      |

| Internal Clock Operation (Ceramic Fi   | ter Oscillation)  |                                                                                 |                                                 |                      |       |      |      |      |

| Clock Oscillation Frequency            | fosc              | Ceramic Filt                                                                    | er                                              | 392                  | _     | 408  | kHz  |      |

| Instruction Cycle Time                 | T <sub>inst</sub> | T <sub>inst</sub> =4/f <sub>OS</sub>                                            | ic                                              | 9.8                  | _     | 10.2 | μs   | 1    |

[NOTE 1] All voltages are with respect to GND. [NOTE 2] This is applied to RESET,  $\overline{\text{HLT}}$ , OSC, INT, and the With Pull up MOS or CMOS type of I/O pins. [NOTE 3] This is applied to the Open Drain type of I/O pins.

### (2) HITACHI

Hitachi America Ltd. • 2210 O'Toole Ave. • San Jose, CA 95131 • (408) 435-8300

[NOTE 4] This is applied to the CMOS type of I/O or Output pins.

[NOTE 5] This is applied to the With Pull up MOS or CMOS type of I/O or Output pins.

[NOTE 6] This is applied to the Open Drain type of I/O or Output pins.

[NOTE 7] I/O current is excluded.

[NOTE 8] The Standby I/O Leakage Current is the I/O feakage current in the Halt and Disable State.

[NOTE 9] I/O current is excluded.

The Standby Supply Current is the supply current at V<sub>CC</sub>=5V±10% in the Halt State. The supply current in the case where the supply voltage falls to the Halt Duration Voltage is called the Halt Current (I<sub>DM</sub>), and it is shown in "ELECTRICAL CHARACTERISTICS-2."

### • ELECTRICAL CHARACTERISTICS-2 (Ta=-20 to +75°C)

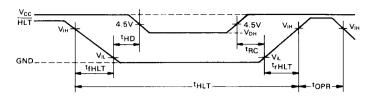

Reset and Halt

| Item                    | Symbol            | Test Conditions                                                                                                           | l                   | Unit |      |     |

|-------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------|------|------|-----|

| iterii                  | Symbol            | Test Conditions                                                                                                           | min                 | typ  | max  | Uni |

| Halt Duration Voltage   | V <sub>DH</sub>   | HLT=0.2V                                                                                                                  | 2.3                 | _    | _    | ٧   |

| Halt Current            | 1 <sub>DH</sub>   | V <sub>in</sub> =V <sub>CC</sub> , HLT=0.2V,<br>V <sub>DH</sub> =2.3V                                                     | _                   | _    | 10   | μΑ  |

| Halt Delay Time         | t <sub>MD</sub>   |                                                                                                                           | 100                 | _    |      | μs  |

| Operation Recovery Time | t <sub>RC</sub>   |                                                                                                                           | 100                 | _    | _    | μs  |

| HLT Fall Time           | t <sub>fHLT</sub> |                                                                                                                           | -                   | _    | 1000 | μs  |

| HLT Rise Time           | t <sub>rHLT</sub> |                                                                                                                           | _                   | _    | 1000 | με  |

| HLT "Low" Hold Time     | t <sub>HLT</sub>  |                                                                                                                           | 400                 | _    |      | μ   |

| HLT "High" Hold Time    | topa              | R <sub>f</sub> Oscillation,<br>External Clock Operation                                                                   | 0.1                 | -    | -    | m   |

| •                       | ••••              | Ceramic Filter Oscillation                                                                                                | 4                   | _    |      | 1   |

| Power Supply Rise Time  | t <sub>roc</sub>  | Built-in Reset,<br>HLT=V <sub>CC</sub>                                                                                    | 0.1                 | _    | 10   | m   |

| Power Supply OFF Time   | t <sub>OFF</sub>  | Built-in Reset,<br>HLT=V <sub>CC</sub>                                                                                    | 1                   | _    | -    | m   |

| RESET Pulse Width (1)   |                   | External Reset,  V <sub>CC</sub> =4.5 to 5.5V, HLT=V <sub>CC</sub> (R <sub>f</sub> Oscillation, External Clock Operation) | 1                   | -    | _    |     |

| neser ruise with (1)    | t <sub>RST1</sub> | External Reset V <sub>CC</sub> =4.5 to 5.5V, HLT=V <sub>CC</sub> (Ceramic Filter Oscillation)                             | 4                   |      |      | m:  |

| RESET Pulse Width (2)   | t <sub>RST2</sub> | External Reset V <sub>CC</sub> =4.5 to 5.5V, HLT=V <sub>CC</sub>                                                          | 2·T <sub>inst</sub> | -    | -    | μ:  |

| RESET Rise Time         | t <sub>rRST</sub> | External Reset V <sub>CC</sub> =4.5 to 5.5V, HLT=V <sub>CC</sub>                                                          |                     | -    | 20   | m   |

| RESET Fall Time         | t <sub>fRST</sub> | External Reset V <sub>CC</sub> =4.5 to 5.5V, HLT=V <sub>CC</sub>                                                          | _                   | _    | 20   | m   |

[NOTE] All voltages are with respect to GND.

### ■ HMCS42CL ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>=2.5V to 5.5V)

### ABSOLUTE MAXIMUM RATINGS

| ltem                             | Symbol              | Value                        | Unit | Remarks                                                           |

|----------------------------------|---------------------|------------------------------|------|-------------------------------------------------------------------|

| Supply Voltage                   | V <sub>cc</sub>     | -0.3 to +7.0                 | ٧    |                                                                   |

| Pin Voltage (1)                  | V <sub>T1</sub>     | -0.3 to V <sub>CC</sub> +0.3 | V    | Except for pins specified by V <sub>T2</sub>                      |

| Pin Voltage (2)                  | V <sub>T2</sub>     | -0.3 to +10.0                | V    | Applied to open-drain output pins and open-drain I/O common pins. |

| Maximum Total Output Current (1) | - ΣI <sub>o</sub> , | 45                           | mA   | [NOTE 3]                                                          |

| Maximum Total Output Current (2) | Σl <sub>o2</sub>    | 45                           | mA   | [NOTE 3]                                                          |

| Operating Temperature            | Topr                | -20 to +75                   | °C   |                                                                   |

| Storage Temperature              | T <sub>stg</sub>    | -55 to +125                  | °C   |                                                                   |

[NOTE 1] Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under the conditions of "ELECTRICAL CHARACTERISTICS-1, -2." If these conditions are exceeded, it could affect reliability of LSI.

[NOTE 2] All voltages are with respect to GND.

[NOTE 3] Maximum Total Output Current is total sum of output currents which can flow out (or flow in) simultaneously.

### • ELECTRICAL CHARACTERISTICS-1 (V<sub>CC</sub>=2.5 to 5.5V, Ta=-20 to +75°C)

|                             |                  | Ŧ1.                                                                                                                                                              | 2 distant                             |                      | Value |                      | Unit | Note     |

|-----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|-------|----------------------|------|----------|

| Item                        | Symbol           | l est (                                                                                                                                                          | Test Conditions                       |                      | typ   | max                  | Oint | 140.0    |

| Input "Low" Voltage         | VIL              |                                                                                                                                                                  |                                       | -                    |       | 0.15·V <sub>CC</sub> | V    |          |

| Input "High" Voltage (1)    | V <sub>IH1</sub> |                                                                                                                                                                  |                                       | 0.85·V <sub>CC</sub> | _     | V <sub>cc</sub>      | V    | 2        |

| Input "High" Voltage (2)    | V <sub>IH2</sub> |                                                                                                                                                                  |                                       | 0.85·V <sub>CC</sub> |       | 10                   | V    | 3_       |

| Output "Low" Voltage        | Vol              | I <sub>OL</sub> =0.4mA                                                                                                                                           |                                       | _                    | -     | 0.4                  | V    |          |

| Output "High" Voltage       | V <sub>OH</sub>  | -1 <sub>OH</sub> =0.08r                                                                                                                                          | -1 <sub>OH</sub> =0.08mA              |                      | _     |                      | ٧    | 4        |

| Output "High" Current       | Гон              | V <sub>OH</sub> = 10V                                                                                                                                            |                                       | _                    | _     | 3                    | μΑ   | 5        |

|                             |                  | V <sub>in</sub> =0 to V <sub>CC</sub>                                                                                                                            |                                       | _                    |       | 1.0                  |      | 2, 6     |

| Input Leakage Current       | I <sub>IL</sub>  | V <sub>in</sub> =0 to 10                                                                                                                                         | V                                     | _                    |       | 3                    | μΑ   | 6        |

| Pull up MOS Current         | -I <sub>P</sub>  | v <sub>cc</sub> =3v                                                                                                                                              |                                       | 10                   |       | 80                   | μΑ   | <u> </u> |

| Supply Current              | lcc              | V <sub>in</sub> =V <sub>CC</sub> , V <sub>CC</sub> =3V<br>(f <sub>OSC</sub> /f <sub>cp</sub> =200kHz)<br>R <sub>f</sub> Oscillation,<br>External Clock Operation |                                       | _                    | _     | 100                  | μΑ   |          |

|                             |                  | <b></b>                                                                                                                                                          | V <sub>in</sub> =0 to V <sub>CC</sub> | -                    | _     | 1                    | μΑ   | 2, 6     |

| Standby I/O Leakage Current | lLS              | HLT=0.5V                                                                                                                                                         | V <sub>in</sub> =0 to 10V             | -                    | _     | 3                    | μΑ   | 7        |

|                             | +                | V <sub>in</sub> =V <sub>CC</sub> ,                                                                                                                               | V <sub>CC</sub> =2.5 to 3.5V          |                      |       | 6                    | μΑ   | 8        |

| Standby Supply Current      | lccs             | HLT=0.1V                                                                                                                                                         | V <sub>CC</sub> = 2.5 to 5.5V         | _                    | _     | 10                   | μΑ   | 7 °      |

(to be continued)

|                                             |                   | Tank Candinian                                                            |      | Value |      | Unit    | Note |

|---------------------------------------------|-------------------|---------------------------------------------------------------------------|------|-------|------|---------|------|

| Item                                        | Symbol            | Test Conditions                                                           | min  | typ   | max  | Unit    | Note |

| External Clock Operation                    |                   |                                                                           |      |       |      |         |      |

| External Clock Frequency                    | f <sub>cp</sub>   |                                                                           | 130  | 200   | 240  | kHz     |      |

| External Clock Duty                         | Duty              |                                                                           | 45   | 50    | 55   | %       |      |

| External Clock Rise Time                    | t <sub>rcp</sub>  |                                                                           | 0    | _     | 0.2  | μs      |      |

| External Clock Fall Time                    | t <sub>fcp</sub>  |                                                                           | 0    | _     | 0.2  | μs      |      |

| Instruction Cycle Time                      | T <sub>inst</sub> | T <sub>inst</sub> =4/f <sub>cp</sub>                                      | 16.8 | 20    | 30.8 | μs      |      |

| Internal Clock Operation (Rf Osci           | llation)          |                                                                           |      |       |      |         | ]    |

| 0. 10 % 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 |                   | $R_f = 180 k\Omega \pm 2\%,$<br>$V_{CC} = 2.5 \text{ to } 3.5 \text{V}$   | 130  | -     | 250  | 250 kHz |      |

| Clock Oscillation Frequency                 | fosc              | $R_f = 180 k\Omega \pm 2\%$<br>$V_{CC} = 2.5 \text{ to } 5.5 \text{V}$    | 130  | _     | 350  | Kriz    |      |

| Landardian Corola Time                      |                   | T <sub>inst</sub> = 4/f <sub>OSC</sub> ,<br>V <sub>CC</sub> = 2.5 to 3.5V | 16   | -     | 30.8 | μs      |      |

| Instruction Cycle Time                      | T <sub>inst</sub> | T <sub>inst</sub> =4/f <sub>OSC</sub> ,<br>V <sub>CC</sub> =2.5 to 5.5V   | 11.4 | _     | 30.8 | μ3      |      |

[NOTE 1] All voltages are with respect to GND.

[NOTE 2] This is applied to RESET, HLT, OSC, INT, and the With Pull up MOS or CMOS type of I/O pins. [NOTE 4] This is applied to the Open Drain type of I/O pins. [NOTE 4] This is applied to the CMOS type of I/O or Output pins.

[NOTE 5] This is applied to the Open Drain type of I/O or Output pins.

[NOTE 6] I/O current is excluded.

[NOTE 7] The Standby I/O Leakage Current is the I/O leakage current in the Halt and Disable State.

[NOTE 8] I/O current is excluded.

The Standby Supply Current is the supply current at  $V_{CC} = 2.5$  to 5.5V in the Halt State. The supply current in the case where the supply voltage falls to the Halt Duration Voltage is called the Halt Current ( $I_{DH}$ ), and it is shown in "ELECTRICAL CHARACTERISTICS-2."

### • ELECTRICAL CHARACTERISTICS-2 (Ta=-20 to +75°C)

Reset and Halt

| •                       |                   | Total Constitution                                                                                       | Va                  | lue  | Unit |

|-------------------------|-------------------|----------------------------------------------------------------------------------------------------------|---------------------|------|------|

| Item                    | Symbol            | Test Conditions                                                                                          | min                 | max  | Uni  |

| Halt Duration Voltage   | V <sub>DH</sub>   | HLT=0.2V                                                                                                 | 2.0                 |      | V    |

| Halt Current            | I <sub>DH</sub>   | V <sub>in</sub> =V <sub>CC</sub> , <del>HLT</del> =0.1V<br>V <sub>DH</sub> =2.0V                         | -                   | 10   | μΑ   |

| Halt Delay Time         | t <sub>HD</sub>   |                                                                                                          | 200                 | -    | μs   |

| Operation Recovery Time | t <sub>RC</sub>   |                                                                                                          | 200                 | _    | μs   |

| HLT Fall Time           | t <sub>fHLT</sub> |                                                                                                          | _                   | 1000 | μs   |

| HLT Rise Time           | t <sub>rHLT</sub> |                                                                                                          | -                   | 1000 | με   |

| HLT "Low" Hold Time     | t <sub>HLT</sub>  |                                                                                                          | 800                 | -    | μs   |

| HLT "High" Hold Time    | <sup>t</sup> OPR  | R <sub>f</sub> Oscillation,<br>External Clock Operation<br>V <sub>CC</sub> = 2.5 to 5.5V                 | 0.2                 | _    | ms   |

| RESET Pulse Width (1)   | t <sub>RST1</sub> | V <sub>CC</sub> =2.5 to 5.5V, HLT=V <sub>CC</sub> (R <sub>f</sub> Oscillation, External Clock Operation) | 2                   | -    | ms   |

| RESET Pulse Width (2)   | t <sub>RST2</sub> | V <sub>CC</sub> = 2.5 to 5.5V<br>HLT=V <sub>CC</sub>                                                     | 2·T <sub>inst</sub> | _    | μs   |

| RESET Fall Time         | t <sub>fRST</sub> | HLT=V <sub>CC</sub>                                                                                      |                     | 20   | ms   |

| RESET Rise Time         | t <sub>rRST</sub> | HET=V <sub>CC</sub>                                                                                      | _                   | 20   | ms   |

[NOTE] All voltages are with respect to GND.

144

### ■ SIGNAL DESCRIPTION

The input and output signals for the HMCS42C, shown in PIN ARRANGEMENT, are described in the following para-

### V<sub>CC</sub> and GND

Power is supplied to the HMCS42C using these two pins. V<sub>CC</sub> is power and GND is the ground connection.

### RESET and HLT

The status of the Halt and Reset depends on the following truth table.

| RESET | HLT | Operation       |

|-------|-----|-----------------|

| 0     | 1   | Operating State |

| 1     | 1   | Reset State     |

| 0     | 0   | Halt State      |

| 1     | 0   | Not Allowable   |

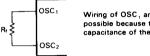

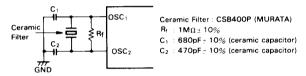

### OSC, and OSC2

These pins provide control input for the built-in oscillator circuit. A resistor, ceramic filter circuit, or an external oscillator can be connected to these pins to provide a system clock with various degrees of stability/cost tradeoffs. Lead length and stray capacitance on these two pins should be minimized.

Refer to OSCILLATOR for recommendations about these pins.

### R<sub>oo</sub> to R<sub>os</sub>

These 4 lines are arranged into one 4-bit Data Input Channel. It is directly addressed by the operand of input instruction. Refer to INPUT/OUTPUT for additional information.

R<sub>20</sub> to R<sub>23</sub>, R<sub>30</sub> to R<sub>33</sub>

These 8 lines are arranged into two 4-bit Data Output Channels. The 4-bit registers (Data I/O Register) are attached to these channels. Each channel is directly addressed by the operand of output instruction.

Refer to INPUT/OUTPUT for additional information.

### D<sub>0</sub> to D<sub>3</sub>

These lines are four 1-bit Discrete Input/Output Common pins. The 1-bit latches are attached to these pins. Each pin is addressed by the Y register. It is also addressed directly by the operand of input/output instruction.

Refer to INPUT/OUTPUT for additional information.

#### D<sub>4</sub> to D<sub>9</sub>

These lines are six 1-bit Discrete Output pins. The 1-bit latches are attached to these pins. Each pin is addressed by the Y register.

Refer to INPUT/OUTPUT for additional information.

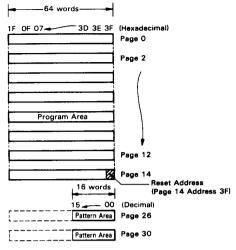

### ■ ROM

### **ROM Address Space**

ROM is used as a memory for the instructions and the patterns (constants). The instruction used in the HMCS42C consists of 10 bits. These 10 bits are called "a word", which is a unit for writing into ROM.

The ROM address is composed of the program area (page 0 to page 14) and the pattern area (pages 26, 30). (64 words/page.)

The ROM capacity is 544 words (1 word = 10 bits) in all.

Only the program area can contain both the instructions and the patterns (constants).

The ROM address space is shown in Figure 1.

Figure 1 ROM Address Space

### Program Counter (PC)

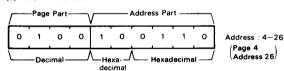

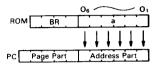

The program counter is used for addressing the program area. It consists of the page part and the address part as shown in Figure 2.

Figure 2 Configuration of Program Counter

Once a certain value is loaded into a page part, it is unchanged until other value is loaded by the program. Any number among 0 to 14 can be set in the page part.

The address part is a 6-bit polynomial counter and counts up for each instruction cycle time. The sequence in the decimal and hexadecimal system is shown in Table 1. This sequence forms a loop and has neither the starting nor ending point. It doesn't generate an overflow carry. Consequently, the program on a same page is executed in order unless the value of the page part is changed.

Table 1 Program Counter Address Part Sequence

| Decimal | Hexadecimal | Decimal | Hexadecimal | Decimal | Hexadecimal |

|---------|-------------|---------|-------------|---------|-------------|

| 63      | 3F          | 5       | 05          | 9       | 09          |

| 62      | 3E          | 11      | ОВ          | 19      | 13          |

| 61      | 3D          | 23      | 17          | 38      | 26          |

| 59      | 38          | 46      | 2E          | 12      | oc          |

| 55      | 37          | 28      | 1C          | 25      | 19          |

| 47      | 2F          | 56      | 38          | 50      | 32          |

| 30      | 1E          | 49      | 31          | 37      | 25          |

| 60      | 3C          | 35      | 23          | 10      | 0A          |

| 57      | 39          | 6       | 06          | 21      | 15          |

| 51      | 33          | 13      | OD          | 42      | 2A          |

| 39      | 27          | 27      | 1B          | 20      | 14          |

| 14      | OE          | 54      | 36          | 40      | 28          |

| 29      | 1D          | 45      | 2D          | 16      | 10          |

| 58      | 3A          | 26      | 1A          | 32      | 20          |

| 53      | 35          | 52      | 34          | 0       | 00          |

| 43      | 2B          | 41      | 29          | 1       | 01          |

| 22      | 16          | 18      | 12          | 3       | 03          |

| 44      | 2C          | 36      | 24          | 7       | 07          |

| 24      | 18          | 8       | 08          | 15      | OF          |

| 48      | 30          | 17      | 11          | 31      | 1F          |

| 33      | 21          | 34      | 22          |         |             |

| 2       | 02          | 4       | 04          |         |             |

### Designation of ROM Address and ROM Code

The page part is represented by decimal and the address part is divided into 2 parts (2 bits and 4 bits) and represented by hexadecimal.

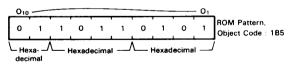

One word (10 bits) is divided into three parts (2 bits, 4 bits and 4 bits from the most significant bit O<sub>10</sub>) and represented by hexadecimal. The examples are shown in Figure 3.

### (a) ROM Address

### (b) ROM Code

Figure 3 Designation of ROM Address and ROM Code

### **■ PATTERN GENERATION**

The pattern (constants) can be accessed by the pattern instruction (P). The pattern can be written in any address of the ROM address space.

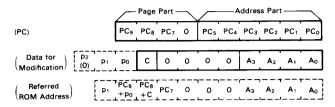

#### Reference

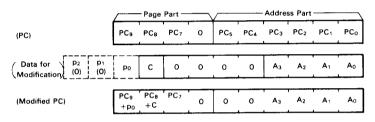

ROM addressing for the pattern reference is performed by modifying the program counter with the accumulator, the carry F/F and the operand p. Figure 4 shows how to modify the program counter. The address part is replaced with the accumulator and 0s, while the page part is logically ORed with 0s, C (F/F) and the lower bit of the operand p (po). The upper bit (p1) of the operand is for referring to the pattern area.

Non-existing ROM area can not be referred.

The contents of PC is only modified apparently and is not changed. Then the address is counted up after the execution of the pattern instruction and next instruction but one is executed. Therefore, the instruction just after the pattern instruction (P) should be NOP.

The pattern instruction is executed in 2 cycles.

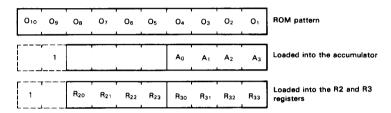

#### Generation

The bit pattern of referred ROM address is generated by the following two ways.

(i) The pattern is loaded into Accumulator.

(ii) The pattern is loaded into the data I/O registers R2 and R3. The command bits (O<sub>9</sub>, O<sub>10</sub>) in the pattern determine which way is taken.

Mode (i) is performed when  $O_9$  is "1" and mode (ii) is performed when  $O_{10}$  is "1".

Mode (i) and mode (ii) are simultaneously performed when both  $O_9$  and  $O_{10}$  are "1".

The correspondence of each bit of the pattern is shown in Figure 5.

### (1) HITACHI

#### CAUTION

In the program execution, the pattern can not be distinguished from the instruction. When the program is running at the address written as a pattern, the instruction corresponding to the pattern bit is executed. Take care not to execute a pattern as an instruction.

Figure 4 ROM Addressing for Pattern Generation

Figure 5 Correspondence of Each Bit of Pattern

Table 2 Example of how to use Pattern Instruction

Referred After Execution

| Before Execution |   |     |   |   | Referred<br>ROM | B-44    | After Execution |   |          | Remarks |               |  |

|------------------|---|-----|---|---|-----------------|---------|-----------------|---|----------|---------|---------------|--|

| PC Value         | р | С   | В | Α | Address         | Pattern | В               | A | R2       | R3      | nemarks       |  |

| 0-3F             | 1 | 0   |   | 0 | 8-00            | 131     |                 | 8 | <b>-</b> | -       |               |  |

| 2-3F             | 3 | 1   |   | 8 | 30-08           | 231     |                 | _ | С        | 8       |               |  |

| 14-00            | 2 | 0/1 |   | 9 | 30-09           | 331     |                 | 8 | С        | 8       |               |  |

| 10-01            | 2 | 0   |   | 5 | 26-05           | 331     |                 | 8 | С        | 8       |               |  |

| 8-00             | 2 | 1   |   | 5 | 28-05           |         |                 |   |          |         | Not allowable |  |

- "-" means that the value does not change after execution of the instruction.

- \*\* "0/1" means that either "0" or "1" may be selected.

- ••• The value of PC and the ROM address are divided into the page and the address parts. The page part is represented by decimal and the address part by hexadecimal.

#### ■ BRANCH

ROM is accessed according to the program counter sequence and the program is executed. In order to jump to an optional address out of the sequence, there are four ways.

They are explained in the following paragraphs.

### • BR

By BR instruction, the program branches to an address in the current page.

The lower 6 bits of ROM output (operand a, O<sub>6</sub> to O<sub>1</sub>) are transferred to the lower 6 bits of the program counter. This instruction is a conditional instruction and executed only when the Status is "1". If it is "0", the instruction is skipped and it becomes "1". The operation is shown in Figure 6.

### • LPU

By LPU instruction, a jump between pages is performed.

The lower 4 bits of ROM output are transferred to the page part of the program counter with delay by one-cycle time. Therefore, the cycle just after the issuing of this instruction is on the same page and the page jump is performed at the next cycle.

This instruction is conditional, and is executed only when the Status is "1". But the Status is unchanged (remains "0") even if it is skipped.

LPU instruction is used in combination with BR instruction or CAL instruction as the macro instruction of BRL or CALL instruction.

The LPU operation is shown in Figure 7.

#### • BRL

By BRL instruction, the program branches to an address in

### **@HITACHI**

Hitachi America Ltd. • 2210 O'Toole Ave. • San Jose, CA 95131 • (408) 435-8300

any page.

This is a macro instruction composed of LPU and BR and divided into two steps as follows.

BRL

$$a - b \rightarrow LPU$$

a < Jump to address b on page  $a > BR$  b

BRL instruction is a conditional instruction because of its characteristics of LPU and BR instructions, and is executed only when the Status is "1". When the Status is "0", this instruction is skipped and the Status becomes "1".

Figure 6 BR Operation

### TBR (Table Branch)

By TBR instruction, the program branches referring to the table.

The program counter is modified by Accumulator, the Carry F/F, and the operand p. Accumulator and 0s are assigned into the address part of the program counter. The 0s, Carry F/F, and the operand p<sub>1</sub>, p<sub>0</sub> are logically ORed with the page part of the program counter.

TBR modifies the PC in the same way as the pattern instruction (P) does. The method for modification is shown in Figure 8.

Figure 7 LPU Operation

Figure 8 Modification of Program Counter by TBR Instruction

### ■ SUBROUTINE JUMP

There are two types of subroutine jumps. They are explained in the following paragraphs.

### • CAL

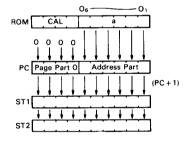

By CAL instruction, subroutine jump to the Subroutine Space is performed.

The program counter is saved in the following order.

$PC+1 \rightarrow ST1 \rightarrow ST2$ The page part of PC is 0. The lower 6 bits of ROM output (operand a,  $O_6$  to  $O_1$ ) are transferred to the lower 6 bits of the program counter.

CAL instruction is a conditional instruction and executed only when the Status is "1". If it is "0", the instruction is skipped and it becomes "1".

The save condition of the program counter when CAL instruction is executed is shown in Figure 9.

### • CALL

By CALL instruction, subroutine jump to an address in any page is performed.

This is a macro instruction of LPU and CAL. The subroutine jump to the page specified by LPU enables the subroutine jump to an optional address.

CALL

$$a - b \rightarrow LPU$$

a < Subroutine jump to address b on page a > CAL b

CALL instruction is conditional because of its characteristics of LPU and CAL instructions and is executed when the Status is "1". If the Status is "0", this instruction is skipped and the Status becomes "1".

Figure 9 Subroutine Jump Stacking Order

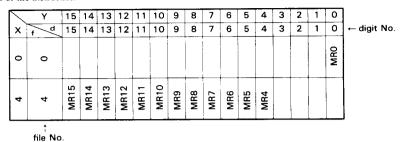

### RAM

RAM is a memory used for storing data and saving the contents of the registers. Its capacity is 32 digits (128 bits) where one digit consists of 4 bits.

Addressing of RAM is performed by the matrix of the file No. and the digit No.

The file No. is set in the X register and the digit No. in the Y register for reading, writing or testing. Specific digits in RAM can be addressed not via the X register and Y register. These digits, 13 digits (MR0, MR4 to MR15), are called "Memory Register (MR)". The memory register can be exchanged with the accumulator by XAMR instruction.

The RAM address space is shown in Figure 10.

If an instruction consists of a simultaneous read/write operation of RAM (exchange between the contents of RAM and those

of the register), the writing data doesn't affect the reading data because read operation precedes write operation.

The RAM bit manipulation instruction enables any addressed RAM bit to be set, reset, or tested. The bit assignment is specified by the operand n of the instruction.

The bit test makes the Status "1" when the assigned bit is "1" and makes it "0" when the assigned bit is "0".

Correspondence between the RAM bit and the operand n is shown in Figure 11.

Figure 10 RAM Address Space

•

Figure 11 RAM Bit and Operand n

### - REGISTER

The HMCS42C has four registers and two latches available to the programmer. The latches are the Carry F/F and the Status F/F. They are explained in the following paragraphs.

### • Status F/F (S)

The Status F/F latches the result of logical or arithmetic operations (Not Zero, Overflow) and bit test operations. The Status F/F affects conditional instructions (LPU, BR and CAL instructions). These instructions are executed only when the Status F/F is "1". If it is "0", these instructions are skipped and the Status F/F becomes "1".

### Accumulator (A; A Register) and Carry F/F (C)

The result of the Arithmetic Logic Unit (ALU) operation (4 bits) and the overflow of the ALU are loaded into the accumulator and the Carry F/F respectively. The Carry F/F can be set, reset or tested. Combination of the accumulator and the Carry F/F can be right or left rotated. The accumulator is the main register for ALU operation and the Carry F/F is used to store the overflow generated by ALU operation when the calculation of two or more digits (4 bits/digit) is performed.

### X Register (X)

The result of ALU operation (1 bit) is loaded into this register. The X register is exchangeable with the SPX register. The X register addresses the RAM file and composed of 1-bit (0 or 4) register.

### SPX Register (SPX)

The SPX register is exchangeable with the X register. The SPX register is used to stack the contents of the X regis-

ter and expand the addressing system of RAM in combination with the X register. It is composed of 1-bit (0 or 4) register.

#### Y Register (Y)

The result of ALU operation (4 bits) is loaded into this register. The Y register can calculate itself simultaneously with transferring data by the bus lines, which is usable for the calculation of two or more digits (4 bits/digit). The Y register addresses the RAM digit and 1-bit Discrete I/O.

### ■ INPUT/OUTPUT

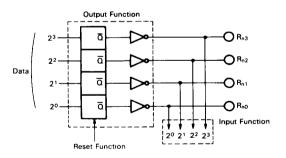

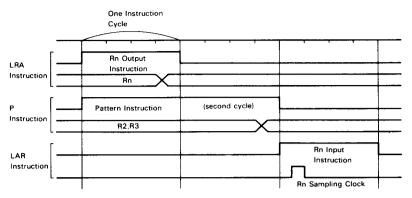

### • 4-bit Data Input/Output Channel (R)

The HMCS42C has one 4-bit Data Input Channel (R0) and two Data Output Channels (R2, R3).

The 4-bit register is attached to R2 and R3 channels. Channel addressing is performed by the program. The input

Channel addressing is performed by the program. The input instruction inputs 4-bit data into the accumulator (A register) through R0 channel.

The data is transferred from the accumulator to the Data I/O Registers R2 and R3 via the bus lines. ROM bit patterns are loaded into the Data I/O Registers R2 and R3 by the pattern instruction.

The block diagram is shown in Figure 12. The I/O timing is shown in Figure 13.

Figure 12 4-bit Data I/O Block Diagram

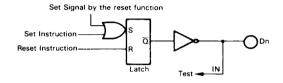

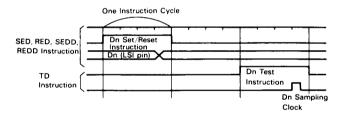

### • 1-bit Discrete Input/Output Pin (D)

The HMCS42C has ten 1-bit Discrete Pins. The  $D_0$  to  $D_3$  are 1-bit Discrete 1/O Common Pins and the  $D_4$  to  $D_9$  are 1-bit Dis-

## **OHITACHI**

Hitachi America Ltd. • 2210 O'Toole Ave. • San Jose, CA 95131 • (408) 435-8300

Figure 13 4-bit Data I/O Timing

Figure 14 1-bit Discrete I/O Block Diagram

Figure 15 1-bit Discrete I/O Timing

crete Output Pins.

The 1-bit Discrete I/O is addressed by the Y register. The addressed latch can be set or reset by output instruction and level ("0" or "1") of the addressed pin can be tested by an input instruction.

Note that, since the latch output is directly connected to the pin even during execution of input instruction, the input data is wired logic of the latch output and the pin input. Therefore, the latch should be set to "1" not to affect the pin input before execution of input instruction.

The  $D_0$  to  $D_3$  pins are also addressed directly by the operand n of input/output instruction and can be set or reset.

The block diagram is shown in Figure 14 and the I/O timing is in Figure 15.

### • I/O Configuration

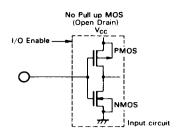

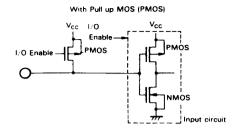

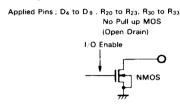

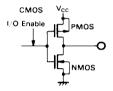

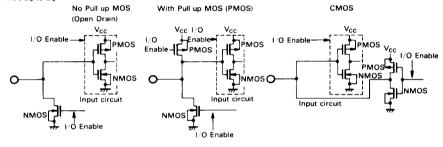

The I/O configuration of each pin can be specified among Open Drain and With Pull up MOS using a mask option as shown in Figure 16.

### (a) Configuration of Input Pin Applied Pins; Roo to Ros

### (b) Configuration of Output Pin

### (c) Configuration of I/O Pin

Applied Pins; Do to Da

\*When "Disable" is specified for the I/O State at the Halt State, the I/O Enable signal shown in the figure turns off the input circuit, Pull up MOS and NMOS output and sets CMOS output to high impedance (PMOS, NMOS; OFF).

Figure 16 I/O Configuration

### ■ RESET FUNCTION

The status of the Reset depends on the following truth table. Moreover, the HMCS42C has the automatic reset function (ACL; Built-in Reset Circuit). The Built-in Reset Circuit restricts the rise condition of the power supply; Refer to Figure 18. When the Built-in Reset Circuit is used, RESET should be connected to Vec.

V<sub>SS</sub>.

HMCS42CL doesn't have the Built-in Reset Circuit.

Internal state of the HMCS42C are specified as follows by the reset function.

- Program Counter (PC) is set to address 3F on page 14 (14-3F)

- · I/O latch and Registers (D<sub>0</sub> to D<sub>9</sub>, R2, R3) are set to "1".

Note that other blocks (Status, Register, RAM, etc.) are not cleared.

| RESET | HLT | Operation       |

|-------|-----|-----------------|

| 0     | 1   | Operating State |

| 1     | 1   | Reset State     |

| 0     | 0   | Halt State      |

| 1     | 0   | Not Allowable   |

[NOTE] RESET and  $\overline{\text{HLT}}$  pins should not be changed simultaneously not to malfunction.

### @ HITACHI

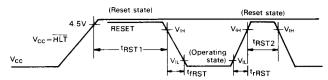

- $\cdot\,t_{RST\,1}$  includes the time required from the power ON until the operation gets into the constant state.

- · tRST2 is applied when the operation is in the constant state.

Figure 17 RESET Timing

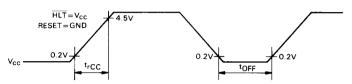

t<sub>OFF</sub> specifies the period when the power supply is OFF, when a short break of the power supply occurs and the power supply ON/OFF is repeated.

Figure 18 Power Supply Timing for Built-in Reset Circuit

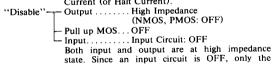

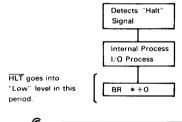

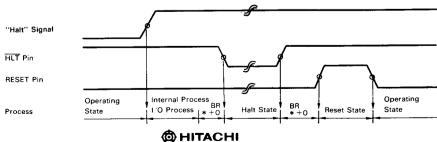

### **■ HALT FUNCTION**

When the HLT pin is set to "0" ("Low" level) and the RE-SET pin is set to "0" ("Low" level), the internal clock stops and all the internal statuses (RAM, the Registers, the Carry F/F, the Status F/F, the Program Counter, etc.) are held. Refer to the truth table in RESET FUNCTION. Because all internal logic operations stop in this state, power consumption is reduced. There are two input/output statuses in the Halt State. The user should specify either "Enable" or "Disable" using a mask option at ROM ordering.

"Enable"

Output ...... The Status before the Halt State is held.

Pull up MOS ... ON

Input ...... No relation to "Halt"

Since Pull up MOS is ON, Pull up MOS current flows when output is "0" ("Low" level) in the Halt State (NMOS; ON). When an input signal changes, transmission current flows into an input circuit. Also, current flows into Pull up MOS. These currents are added to the Stand-by Supply Current (or Halt Current).

Stand-by Supply Current (or Halt Current) flows even if an input signal changes.

even if an input signal changes.

When the HLT pin is set to "1" ("High" level), the HMCS42C gets into operation from the status just before the Halt State.

The halt timing is shown in Figure 19.

#### CAUTION

If, during the Halt State, the external reset input is applied (RESET = "1" ("High" level)), the internal status is not held.

### (NOTE)

Release "Halt" according to the following sequence for Ceramic Filter Oscillation. Though abnormal oscillation occurs after releasing "Halt" in the case of Ceramic Filter Oscillation, the system does not malfunction because of executing BR \*+0. Reset and restart after that operation.

Hitachi America Ltd. • 2210 O'Toole Ave. • San Jose, CA 95131 • (408) 435-8300

Figure 19 Halt Timing

### ■ OSCILLATOR

The HMCS42C contains its own oscillator and frequency divider (CPG). The user can obtain the desired timing for operation of the LSI by merely connecting an resistor R<sub>f</sub> or ceramic filter circuit (Internal Clock Operation).

The  ${\rm OSC}_1$  clock frequency is internally divided by four to produce the internal system clocks.

The user may exchange the external parts for the same LSI to select either of these two operational modes as shown in Figure 20. There is no need of specifying it by using the mask option.

### (a) Internal Clock Operation Using Resistor Rf

Wiring of OSC, and OSC, pins should be as short as possible because the oscillation frequency is modified by capacitance of these pins.

### (b) Internal Clock Operation Using Ceramic Filter Circuit (This is not applied to HMCS42CL)

When halt function is applied, keep the "NOTE" in "HALT FUNCTION". This circuit is the example of the typical use. As the oscillation characteristics is not guaranteed, please consider and examine the circuit constants carefully on your application.

### (c) External Clock Operation

Figure 20 Clock Operation Mode

### ■ INSTRUCTION LIST

The instructions of the HMCS42C are listed according to their functions, as shown in Table 3.

Table 3 Instruction List

| Group                  | Mnemonic  | Function                                                     | Status  |

|------------------------|-----------|--------------------------------------------------------------|---------|

| Di-4 Di-4              | LAY       | Y → A                                                        |         |

| Register · Register    | LASPX     | SPX → A                                                      |         |

| Instruction            | XAMR m    | A ↔ MR (m)                                                   |         |

|                        | LXA       | $A \rightarrow X$                                            |         |

|                        | LYA       | $A \rightarrow Y$                                            |         |

|                        | LXI i     | $i \rightarrow X$                                            |         |

| AM Address Register    | LYI i     | $i \rightarrow Y$                                            |         |

| Instruction            | IY        | Y+1 → Y                                                      | NZ      |

| nstruction             | DY        | Y-1 → Y                                                      | NB      |

|                        | AYY       | $Y+A \rightarrow Y$                                          | С       |

|                        | SYY       | Y-A → Y                                                      | NB      |

|                        | XSPX      | X → SPX                                                      |         |

|                        | LAM (X)   | $M \rightarrow A (X \leftrightarrow SPX)$                    |         |

| RAM · Register         | XMA (X)   | M ↔ A (X ↔ SPX)                                              |         |

| nstruction             | LMAIY (X) | $A \rightarrow M, Y+1 \rightarrow Y (X \leftrightarrow SPX)$ | NZ      |

|                        | LMADY (X) | $A \rightarrow M, Y-1 \rightarrow Y (X \leftrightarrow SPX)$ | NB      |

| mmediate Transfer      | LMIIY i   | $i \rightarrow M, Y+1 \rightarrow Y$                         | NZ      |

| nstruction             | LAI i     | i → A                                                        |         |

|                        | Ali       | $A+i \rightarrow A$                                          | С       |

|                        | AMC       | $M+A+C$ (F/F) $\rightarrow A$                                | С       |

|                        | SMC       | $M-A-\widetilde{C}$ (F/F) $\rightarrow A$                    | NB      |

|                        | AM        | M+A → A                                                      | С С     |

|                        | DAA       | Decimal Adjustment (Addition)                                | ļ       |

| Arithmetic Instruction | DAS       | Decimal Adjustment (Subtraction)                             |         |

| Antinmetic instruction | NEGA      | Ā+1 → A                                                      |         |

|                        | SEC       | "1" → C (F/F)                                                |         |

|                        | REC       | "O" → C (F/F)                                                |         |

|                        | TC        | Test C (F/F)                                                 | C (F/F) |

|                        | ROTL      | Rotation Left                                                |         |

|                        | ROTR      | Rotation Right                                               |         |

|                        | MNEI i    | M ≠ i                                                        | NZ      |

|                        | YNELI     | Y ≠ i                                                        | NZ      |

| Compare Instruction    | ANEM      | A ≠ M                                                        | NZ      |

|                        | ALEI i    | A ≦ i                                                        | NB      |

|                        | ALEM      | A ≤ M                                                        | NB      |

| 0.444.0%.44            | SEM n     | "1" → M (n)                                                  |         |

| RAM Bit Manipulation   | REM n     | "O" → M (n)                                                  |         |

| Instruction            | TM n      | Test M (n)                                                   | M (n)   |

(to be continued)

| Group                       | Mnemonic | Function                               | Status |

|-----------------------------|----------|----------------------------------------|--------|

| ROM Address<br>Instruction  | BR a     | Branch on Status 1                     | 1      |

|                             | CAL a    | Subroutine Jump on Status 1            | 1      |

|                             | LPU u    | Load Program Counter Upper on Status 1 | ļ      |

|                             | TBR p    | Table Branch                           | i      |

|                             | RTN      | Return from Subroutine                 |        |

|                             | SED      | "1" → D (Y)                            |        |

|                             | RED      | "O" → D (Y)                            | Ì      |

|                             | TD       | Test D (Y)                             | D (Y)  |

| Input/Output<br>Instruction | SEDD n   | "1" → D (n)                            |        |

|                             | REDD n   | "O" → D (n)                            |        |

|                             | LAR p    | R (p) → A                              |        |

|                             | LRA p    | $A \rightarrow R (p)$                  |        |

|                             | Рр       | Pattern Generation                     |        |

|                             | NOP      | No Operation                           |        |

[NOTE] 1. (XY) after a mnemonic code has two meanings as follows.

Mnemonic only

Instruction execution only

After instruction execution, X ↔ SPX

Mnemonic with X [Example] LAM

M -- A

LAMX

$M \rightarrow A$  $M \rightarrow A, X \rightarrow SPX$

2. Status column shows the factor which brings the Status F/F "1" under judgement instruction or instruction accompanying the judgement.

NZ . . . . . . ALU Not Zero

C . . . . . ALU Overflow in Addition, that is, Carry

NB . . . . . . ALU Overflow in Subtraction, that is, No Borrow

Except above........ Contents of the status column affects the Status F/F directly.

3. The Carry F/F (C(F/F)) is not always affected by executing the instruction which affects the Status F/F.

Instructions which affect the Carry F/F are eight as follows.

AMC SEC SMC REC DAA ROTL DAS ROTR

4. All instructions except the pattern instruction (P) are executed in 1 cycle. The pattern instruction (P) is executed in 2 cycles.

HMCS42C Mask Option List

□ 5V Operation : HMCS42C

□ 3V Operation : HMCS42CL

★ Mark "\square" in "\square" for the selected spec.

| Date                                  |  |

|---------------------------------------|--|

| Customer                              |  |

| Dept.                                 |  |

| Name                                  |  |

| ROM CODE ID                           |  |

| LSI Type Name<br>(entered by Hitachi) |  |

(1) I/O Option

| Pin            |             |          | I/O Option  |      | Pin             | Pin | I/O Option |  |   |  |

|----------------|-------------|----------|-------------|------|-----------------|-----|------------|--|---|--|

| Name           | I/O Remarks | Name I/O | 1/0         | Α    | В               | С   | Remarks    |  |   |  |

| Do             | 1/0         |          |             |      | Roo             | ı   |            |  |   |  |

| D,             | 1/0         |          |             |      | R <sub>o1</sub> | l . |            |  |   |  |

| D <sub>2</sub> | 1/0         |          |             |      | R <sub>o2</sub> | 1   |            |  |   |  |

| D <sub>3</sub> | 1/0         |          |             |      | R <sub>o3</sub> | I . |            |  |   |  |

| D <sub>4</sub> | 0           |          |             |      | R <sub>20</sub> | 0   |            |  |   |  |

| D <sub>5</sub> | 0           | -        |             |      | R <sub>21</sub> | 0   |            |  |   |  |

| D <sub>6</sub> | 0           |          |             |      | R <sub>22</sub> | 0   |            |  |   |  |

| D <sub>7</sub> | 0           |          |             |      | R <sub>23</sub> | 0   |            |  |   |  |

| D <sub>e</sub> | 0           |          |             |      | R <sub>30</sub> | 0   |            |  |   |  |

| D <sub>9</sub> | 0           |          |             |      | R <sub>31</sub> | 0   |            |  |   |  |

| _ •            |             |          |             |      | R <sub>32</sub> | 0   |            |  |   |  |

|                |             |          | <b>†</b> ~~ | <br> | R <sub>33</sub> | 0   |            |  | 1 |  |

☆ Specify the I/O composition with a mark of "○" in the applicable composition column.

A: No pull up MOS

B: With pull up MOS

C: CMOS Output

C: CMOS O

(2) I/O State at "Halt" mode

| I/O State |         |  |  |  |

|-----------|---------|--|--|--|

|           | Enable  |  |  |  |

|           | Disable |  |  |  |

★ Mark "V" in "□" for the selected t/O state.

(3) Package

| Package |        |  |  |  |

|---------|--------|--|--|--|

|         | DP-28  |  |  |  |

|         | DP-28S |  |  |  |

★ Mark "✓" in "□" for the selected package.

Check List of Application

[A] Oscillator (CPG option)

| CPG 5V Operation |                                                | 3V Operation                      |  |  |

|------------------|------------------------------------------------|-----------------------------------|--|--|

| Resistor         | $\square$ R <sub>f</sub> =91k $\Omega \pm 2\%$ | $\Box R_f = 180k\Omega \pm 2\%$   |  |  |

|                  | ☐ MURATA: CSB400P                              |                                   |  |  |

| Ceramic Filter   | ☐ TDK: FCR400K                                 |                                   |  |  |

|                  | ☐ Kyocera: KBR-400B                            |                                   |  |  |

| External Clock   | ☐ f <sub>cp</sub> =200k to 440kHz              | ☐ f <sub>cp</sub> =130k to 240kHz |  |  |

★ Mark "\square" in "\square" for the selected oscillator.

[B] Halt function (Only when Ceramic Filter is selected in [A].)

|           | Using Ceramic Filter         |  |

|-----------|------------------------------|--|

|           | ☐ Not used                   |  |

| Halt Mode | ☐ Used (Recovery with Reset) |  |

★ Mark "V" in "□" for the selected spec.

**OHITACHI**

156