# HD63185, HD63187

# Document Image Compression and Expansion Processor Enhanced (DICEP-E)

DICEP-E is an LSI that performs compression (encoding) and expansion (decoding) of 2value data used to represent a document image. It is positioned at the high end of the DICEP (HD63085) and DICEP-A (HD63183), and has been designed for application in such electronic office devices as facsimiles apparatus (G3, G4), intelligent copiers, image workstations, terminals, and filing systems. DICEP-E adopts the MH (Modified Huffman), MR (Modified Relative Element Address Designate) and M2R (Modified MR) coding scheme, which are the G3 and G4 standards recommended by CCITT (International Telegraph and Telephone Consultative Committee).

#### **Features**

- The features of HD63185 and shoron as follows. The differences detween HD63185 and HD63187 and show as notes.

- Compatible with the CCITT recommendations for G3 and G4 facsimile apparatus

- Bit unit page processing using simple MPU instructions

- The number of picture elements in each line and the line length can be specified in bit units. Encoding (compression) and decoding (expansion) of 2-value data for multiple scan lines can also be performed.

- On-chip line memory for high-speed encoding and decoding

- An on-chip line memory (6,144 bits/line) for reference and code lines provides high-speed encoding and decoding.

- —Transfer of data to the on-chip line memory is performed by accessing 1 word (8-bit/16-bit) in 5 machine cycles (312.5ns minimum) for 1-line continuous access.

- —On-chip line memory also allows reference line access during 2-dimensional encoding to be performed by accessing 1 word in 3 cycles, and parallel processing is also possible.

- —An on-chip changed picture element detector and decoded picture element generator perform changed picture element detection and image data generation for 1 word of data per cycle.

- Specification of split processing memory

area for encoding/decoding

Byte-by-byte split processing of code data and image data can be performed in any memory area, and processing can be restarted from any address. This allows split processing in memory block units, rather than line units.

- Flexible system configuration

- —Connectable with either 68 Series or 80 Series MPU.

- —Two bus interfaces: system bus interface and image bus interface. Both the system bus and image bus sizes are selectable between 8-bit and 16-bit.

- —The port for code data and image data write to and read from DICEP-E can be selected as desired for connection to the system bus interface. (Note 1)

- Line-by-line alternate encode/decode

Line-by-line alternate encoding and

decoding, or time sharing simultaneous

processing of inter-bus transfers and

decoding can be performed. (Note 2)

- High-speed DMA transfer

- —2-channel simultaneous DMA transfer can be performed for transfer between the I/O device on the image bus and image memory, and between two image memories. Maximum transfer speed is 6.4M bytes/second. (Note 3)

- —Including a DMA controller on the system bus of the DICEP-E allows 4-channel (write to/read from FIFO and line memory) independent DMA transfer.

- Code-code conversion

Code data can be converted to different code data without using external memory. (Note 4)

- A selection of coded data configurations

The configuration of code generated during the encode procedure can be specified as MSB first or LSB first.

- Conversion of memory data configuration on the image bus

During DMA transfer between memories, memory data on the image bus can be converted to four different configurations in 8-bit or 16-bit unis. (Note 5)

- Read-modify-write

During decoding, logical operations can

be performed using the decoded data in

the on-chip line memory and the image

data stored in external memory. Up to 16

logical operations, including AND, OR,

and EOR are available, and operations

can be performed line by line. (Note 6)

## HD63185,HD63187

- DRAM control signal

- Memory ROW and COLUMN switching signals (RAS, CAS, MUX) are output for image memory DRAM on the image bus.

- A host of programmable parameters

On-chip programmable registers provide flexibility for application in a wide variety of systems.

- —Parameters can be changed before issuance of each instruction.

- —Scan line length is programmable in 1bit units, ranging from the image memory word size (8-bit/16-bit) up to 6,144 bits. (Note 7)

- —Encoding, decoding, and data transfer can be selected individually or in any combination. (Note 8)

- -MH, MR or  $M^2R$  coding scheme can be selected.

- —The minimum number of code bits per line is programmable within the range of  $0-2^{16}-1$ .

- —The number EOLs (end of line) is programmable within the range of  $0-2^{16}$ -1.

- —The number RTCs (return to control) is programmable within the range of 0—2<sup>16</sup>-1. (Note 9)

- —The number lines that must be processed is programmable within the range of  $1-2^{16}-1$ .

- —The number lines that must be transferred during DMA transfer is programmable within the range of  $1-2^{16}$ -1.

- —The number lines that are 2-dimension encoded following 1-dimension encoding during MR encoding is programmable within the range of  $0-2^{16}$ -1.

- —The area for document image data area which is read and the area for the code data which is written during encoding can be specified within the range of 1—2<sup>16</sup>-1 bytes.

- —The area for document image data area which is generated and the area for the code data which is read during decoding can be specified within the range of  $1-2^{16}-1$  bytes.

- Data transfer between buses

Data can be transferred between the system bus and image bus via the on-chip

- line memory, without encoding/decoding. Burst DMA transfer is performed in line units, also, access from the system bus is performed using write to and read from the control register line memory, allowing access from the MPU.

- Desired part of a document Specific portions of the original can be specified in bit units for cut and encoding/decoding. Also, data can be cut out during DMA transfer on the image bus in units that are the same size as the bus width of the I/O device. (Note 10)

- Octet mode

Each line or the total number of code bits

per page can be set in 8-bit or 16-bit units,

depending on the bus size.

- High-speed operation

- —Minimum instruction cycle time of 62.5ns

- --Maximum input clock frequency of 16HMz

- Output of 1-line processing end signal In the multi-line processing mode, a line processing end signal is output from the LEND pin after completion of processing for 1 line. During encoding, this signal is output following generation of 1 line's code (when it is set in the register immediately before E-FIFO), and during decoding it is output following writing from internal line memory to external memory.

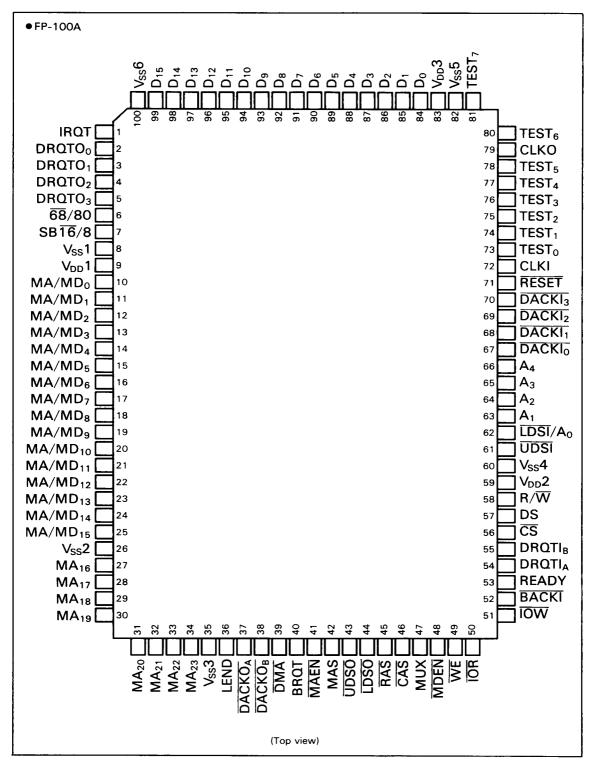

- 100-pin plastic QFP (FP-100A)

Note 1: When using HD63187 the image data canbe accessed only thsoush the image bus, if the number of a line processing bit is over 6, 144 bits during MR and M<sup>2</sup>R coding. The coded data can be accessed iheough either the system bus I/O pat or the image bus I/O poit.

Note 3, 9: HD63187 does not have the DMA transfer on the image bus.

Note 7: For HD63187, the scan line length is programmable in 1-bit unit, ranging from the image memory word siqe (8-bit/16-bit) up to 61.423 bits.

Note 2, 4, 5, 6, 8, 10: HD63187 does not have this function.

#### Pin Arrangement

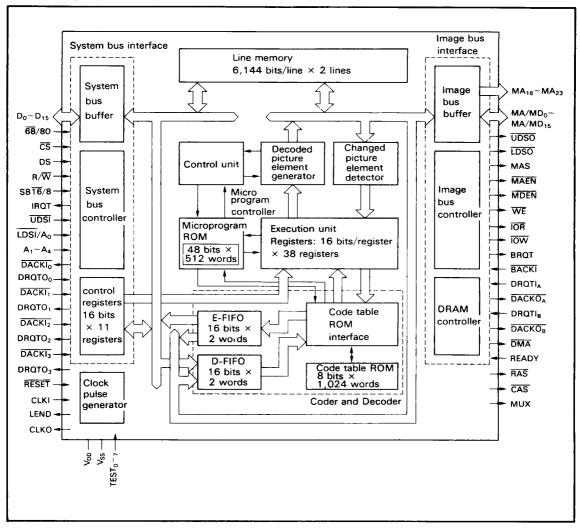

#### **Block Diagrams**

#### System Bus Interface

The system bus interface allows interfacing with 16-bit MPUs such as 68000 Series, and with 8-bit MPUs such as the 6800 Series, H8 Series, and 64180 Series. This block includes control registers that the MPU can directly access, and can also accommodate a 4-channel DMA for data transfer to FIFO and line memory during encoding/decoding.

#### Microprogram Controller

The microprogram controller stores the encoded/decoded program in microprogram ROM and controls all of the other blocks.

This block consists of a 48-bit  $\times$  512-word microprogram ROM, a sequence controller and pipeline registers.

#### **Execution Unit**

The execution unit generates image memory addresses, and calculates run lengths, the position of the changed picture elements and the relative distance between changed picture elements on the code line and those on the reference line.

This block consists of 38 16-bit registers, and arithmetic unit (AU), and an adder. Registers can contain any value sent from the MPU, via the system bus interface control registers.

#### Coder and Decoder

The coder generates code table ROM addresses in accordance with the input run lengths and relative distances, and references the code table ROM to generate an appropriate code. The decoder, on the other hand, generates a code table ROM address based on the input code, and references the code table ROM to generate references or relative distances.

This block consists of 8-bit  $\times$  1024-word code table ROM, a code table ROM interface, 16-bit  $\times$  2-word or 8-bit  $\times$  4-word (optional) encode FIFO (E-FIFO) and decode FIFO (D-FIFO). The code table ROM stores data for reference during encoding and decoding, while the

code table ROM interface generates code table ROM addresses. E-FIFO is used for temporary storage of code during encoding, while D-FIFO is used for temporary storage of code during decoding.

#### **Changed Picture Element Detector**

The changed picture element detector detects picture elements whose color (black/white) is different from the immediately preceding picture element on the same scan line. This circuit can detect changed picture elements for 1 word (16 bits) of image memory per instruction cycle.

This block consists of two changed picture element detectors — a reference line detector and an encoded line detector.

#### Decoded Picture Element Generator

The decoded picture element generator can generate 1 word (16 bits) per instruction cycle of restored picture element data, based on changed picture element position data.

#### Line Memory

Line memory can be used for accumulation of 2-lines of image data during encoding/ decoding, or as buffer memory during data transfer between the system bus and image bus.

This memory is consists of static RAM, in the capacity of 6,144 bits per line. One line of line memory is used as the encode/decode reference line, while another line is used to store data during encoding and data transfer between buses.

#### **Document Image Bus Interface**

The document image bus interface provides an interface between DICEP-E and the image bus, with a multiplexed 16 bits for addresses and data, and 8 bits for the upper 8 bits of the address. In addition to a bus arbitration function, this block outputs signals for controls of such image bus functions as 2-channel DMA control.

#### **Block Diagram**

## HD63185,HD63187

#### **Functional Summary**

|                                                              | Function                                                       |                                                      |  |  |  |  |

|--------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|--|--|--|--|

| Item                                                         | HD63185                                                        | HD63187                                              |  |  |  |  |

| Coding scheme                                                | MH, N                                                          | IR, M <sup>2</sup> R                                 |  |  |  |  |

| Maximum scan-line length                                     | 6,144 picture elements/line                                    | 61,423 picture elements/line                         |  |  |  |  |

| Number of processing lines                                   | 64k line                                                       | s (2 <sup>16</sup> -1)                               |  |  |  |  |

| Image memory address space                                   | 8M words                                                       | (16M bytes)                                          |  |  |  |  |

| Picture element processing units                             | Bit units (number of processing picture elements, line length) |                                                      |  |  |  |  |

| Maximum DMA transfer rate                                    | 6.4M bytes/second                                              | not avairable                                        |  |  |  |  |

| Internal line memory maximum access speed                    | 6.4M byt                                                       | es/second                                            |  |  |  |  |

| Maximum split processing memory area (image data, code data) | 64k bytes (byte unit)                                          |                                                      |  |  |  |  |

| Generated code configuration                                 | LSB/MSB first                                                  |                                                      |  |  |  |  |

| Read-modify-write                                            | Operation processing – 16 types (AND, OR, EOR, etc.)           | not avairable                                        |  |  |  |  |

| Coding speed                                                 |                                                                | 20 to 30 rercent longer than HD63185 processing time |  |  |  |  |

#### **Internal Registers**

DICEP-E registers can be classified into two groups: control registers that are directly accessible by the MPU, and parameter registers that can be accessed via the parameter buffer registers (PBR). The following details the access methods used for each type of register.

# Registers directly accessible from the MPU

The control registers (CR), data buffer register (DBR), and FIFO can be accessed directly from the MPU, in accordance with A1—A4, when CS is L-level.

Teble 1 shows the directly accessible registers.

# Registers accessible via the parameter buffer registers (PBR)

The parameter registers can be accessed via the parameter buffer registers (PBR). The MPU specifies a parameter register using the address register (AR), and a parameter written to the parameter buffer registers is written to the corresponding parameter register. The MPU writes parameters to parameter registers in the following sequence:

- The PBR ready flag of the status register (SR) is checked to see if it is 1.

- The desired parameter register is specified using the address register (AR).

- The parameter is written to the parameter buffer registers (PBR).

- When the parameter is written to PBR, DICEP-E judges whether address and parameter preparation are complete, and then writes the parameter to the specified register.

Table 2 shows the parameter registers.

#### **Parameter Registers**

|     | Address (AR) |     |     |     |     | Oper   | ration N | Node     |        | Register Name                           |

|-----|--------------|-----|-----|-----|-----|--------|----------|----------|--------|-----------------------------------------|

| AR5 | AR4          | AR3 | AR2 | AR1 | ARO | Encode | Decode   | Transfer | Symbol | Name                                    |

| 0   | 0            | 0   | 0   | 0   | 0   | 0      |          |          | ERSARH | Encode reference line start address (H) |

| 0   | 0            | 0   | 0   | 0   | 1   | 0      |          |          | ERSARL | Encode reference line start address (L) |

| 0   | 0            | 0   | 0   | 1   | 0   | 0      | 0        | 0        | EESARH | Encode code line start address (H)      |

| 0   | 0            | 0   | 0   | 1   | 1   | 0      | 0        | 0        | EESARL | Encode code line start address (L)      |

| 0   | 0            | 0   | 1   | 0   | 0   | 0      |          | 0        | ESBAR  | Encode start bit address register       |

| 0   | 0            | 0   | 1   | 0   | 1   | 0      |          | 0        | EPNR   | Number of encode bits register          |

| 0   | 0            | 0   | 1   | 1   | 0   | 0      |          | 0        | EHWR   | Encode scan-line length register        |

| 0   | 0            | 0   | 1   | 1   | 1   | 0      |          | 0        | ELNR   | Number of encode lines register         |

| 0   | 0            | 1   | 0   | 0   | 0   | 0      |          |          | EEOLR  | Encode EOL register                     |

| 0   | 0            | 1   | 0   | 0   | 1   | 0      |          |          | EMCLR  | Minimum number of encode bits register  |

| 0   | 0            | 1   | 0   | 1   | 0   | 0      |          |          | EKPR   | Encode K parameter register             |

| 0   | 0            | 1   | 0   | 1   | 1   | 0      |          |          | EKCNTR | Encode K counter register               |

| 0   | 0            | 1   | 1   | 0   | 0   | 0      |          |          | ECSARH | Encode code area start address (H)      |

| 0   | 0            | 1   | 1   | 0   | 1   | 0      |          |          | ECSARL | Encode code area start address (L)      |

| 0   | 0            | 1   | 1   | 1   | 0   | 0      |          |          | ECBLKR | Encode code area size register          |

| 0   | 0            | 1   | 1   | 1   | 1   |        | 0        |          | DRSARH | Decode reference line start address (H) |

| 0   | 1            | 0   | 0   | 0   | 0   |        | 0        |          | DRSARL | Decode reference line start address (L) |

| 0   | 1            | 0   | 0   | 0   | 1   |        | 0        |          | DDSARH | Decode code line start address (H)      |

| 0   | 1            | 0   | 0   | 1   | 0   |        | 0        |          | DDSARL | Decode code line start address (L)      |

| 0   | 1            | 0   | 0   | 1   | 1   |        | 0        |          | DSBAR  | Decode start bit address register       |

| 0   | 1            | 0   | 1   | 0   | 0   |        | 0        |          | DPNR   | Number of decode bits register          |

| 0   | 1            | 0   | 1   | 0   | 1   |        | 0        |          | DHWR   | Decode scan-line length register        |

| 0   | 1            | 0   | 1   | 1   | 0   |        | 0        |          | DLNR   | Number of decode lines register         |

| 0   | 1            | 0   | 1   | 1   | 1   |        | 0        |          | DRTCR  | Decode RTC register                     |

| 0   | 1            | 1   | 0   | 0   | 0   |        | 0        |          | DCSARH | Decode code area start address (H)      |

| 0   | 1            | 1   | 0   | 0   | 1   |        | 0        |          | DCSARL | Decode code area start address (L)      |

| 0   | 1            | 1   | 0   | 1   | 0   |        | 0        |          | DCBLKR | Decode code area size register          |

| 0   | 1            | 1   | 0   | 1   | 1   | 0      | 0        | 0        | MBLKR  | Image memory block register             |

| 0   | 1            | 1   | 1   | 0   | 0   | (0)    | (0)      | (0)      | DMASAH | DMAA channel start address register (H) |

| 0   | 1            | 1   | 1   | 0   | 1   | (0)    | (0)      | (0)      | DMASAL | DMAA channel start address register (L) |

| 0   | 1            | 1   | 1   | 1   | 0   | (0)    | (0)      | (0)      | DMABSR | DMAA channel block size register        |

| 0   | 1            | 1   | 1   | 1   | 1   | (0)    | (0)      | (()      | DMAHWR | DMAA channel scan-line length register  |

(to be continued)

# HD63185,HD63187

## (continued)

|     | Ade | dres | s ( <i>f</i> | AR) |     | Ope    | ration N | Pode     | Register Name |                                                  |  |

|-----|-----|------|--------------|-----|-----|--------|----------|----------|---------------|--------------------------------------------------|--|

| AR5 | AR4 | AR3  | AR2          | AR1 | AR0 | Encode | Decode   | Transfer | Symbol        | Name                                             |  |

| 1   | 0   | 0    | 0            | 0   | 0   | (()    | (0)      | (0)      | DMALNR        | Number of DMAA channel processing lines register |  |

| 1   | 0   | 0    | 0            | 0   | 1   | (()    | (0)      | (0)      | DMBSAH        | DMAB channel start address register (H)          |  |

| 1   | 0   | 0    | 0            | 1   | 0   | (0)    | (0)      | (0)      | DMBSAL        | DMAB channel start address register (L)          |  |

| 1   | 0   | 0    | 0            | 1   | 1   | (0)    | (0)      | (0)      | DMBBSR        | DMAB channel block size register                 |  |

| 1   | 0   | 0    | 1            | 0   | 0   | (()    | (()      | (0)      | DMBHWR        | DMAB channel scan-line length register           |  |

| 1   | 0   | 0    | 1            | 0   | 1   | (()    | (0)      | (0)      | DMBLNR        | Number of DMAB channel processing lines register |  |

#### **Absolute Maximum Ratings**

| item                  | Symbol           | Value                    | Unit |

|-----------------------|------------------|--------------------------|------|

| Supply Voltage*1      | V <sub>DD</sub>  | -0.3 ∼ +7.0              | V    |

| Input Voltage*1       | Vin              | $-0.3 \sim V_{DD} + 0.3$ | V    |

| Operating Temperature | T <sub>OPR</sub> | 0 ~ 70                   | .c   |

| Storage Temperature   | T <sub>STG</sub> | −55 ~ +125               | °C   |

| Power Dissipation*2   | Pc               | 500                      | mW   |

<sup>\*1</sup> Value based on  $V_{SS} = 0V$

## **Recommended Operating Conditions**

| Item                  | Symbol           | min  | typ | max                  | Unit |

|-----------------------|------------------|------|-----|----------------------|------|

| Supply Voltage*       | V <sub>DD</sub>  | 4.75 | 5   | 5.25                 | V    |

| Input Voltage*1       | V <sub>IL</sub>  | -0.3 | _   | 0.8                  | V    |

|                       | V <sub>IH</sub>  | 2.2  | _   | V <sub>DD</sub> +0.3 | V    |

| Operating Temperature | T <sub>OPR</sub> | 0    | 25  | 70                   | ·C   |

<sup>\*</sup> Value based on Vss=0V

<sup>\*2</sup> Tolerance at T<sub>a</sub>=25°C