# **Hard Disk Controller (HDC)**

#### DESCRIPTION

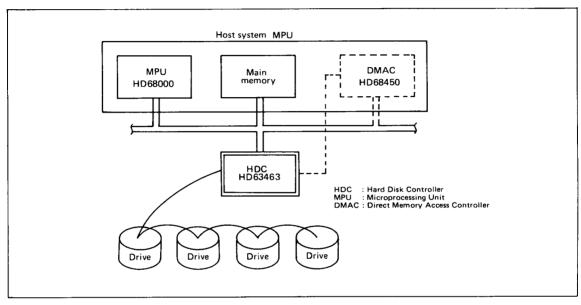

The HD63463 (HDC: Hard Disk Controller) is a CMOS device developed for use as a peripheral LSI for the 16-bit microprocessor HD68000 (MPU: Microprocessing Unit). The HDC connects the host system and the Winchester type hard disk device with or without HD68450 (DMAC: Direct Memory Access Controller).

#### **FEATURES**

- Two types of disk interface, ST506/ST412/ST412HP and SMD

- Choice of data bus width 16 or 8 bits

- Serial data transfer rate max 20 Mbit/s [NRZ], max 10 Mbit/s [MFM]

- Step rate max 1.1 MHz

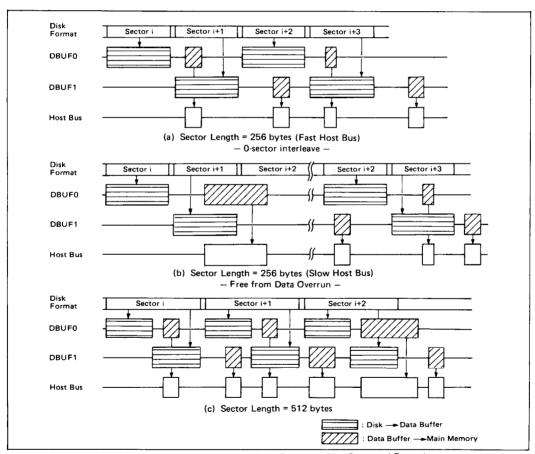

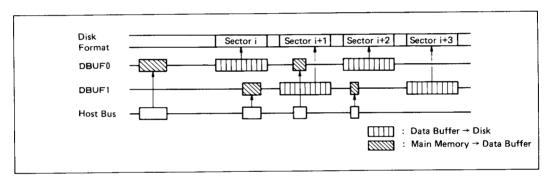

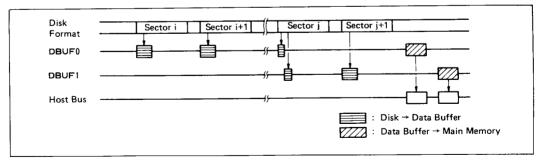

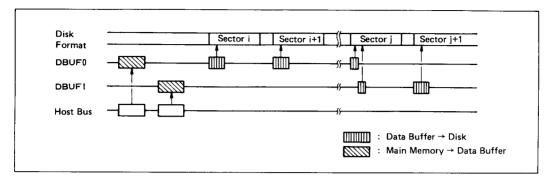

- Internal data buffer (256 bytes x 2)

- Zero-sector interleave access

- Programmed I/O access

- Automatic error correction

- Zero pattern detector/generator, address mark detector/ generator, write precompensation logic, etc internally provided

- 22 high-level function commands

- 25 error codes

- External circuit diagnosis command

- Low power dissipation typ 250 mW

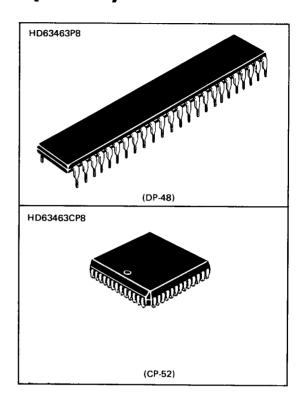

#### TYPE OF PRODUCTS

| Type No.   | Package | Clock Frequency (MHz) |       |  |

|------------|---------|-----------------------|-------|--|

| туре но.   | Fackage | Host                  | Drive |  |

| HD63463P8  | DP-48   | 8.0                   | 20.0  |  |

| HD63463CP8 | CP-52   | 8.0                   | 20.0  |  |

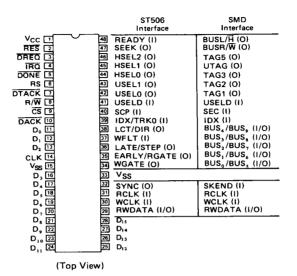

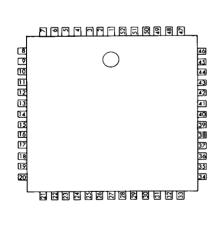

#### PIN ARRANGEMENT

DP-48

CP-52

(Top View)

| Pin      | ST506<br>Inter-    | SMD I | Pin | ST506               | SMD                                      |  |  |  |

|----------|--------------------|-------|-----|---------------------|------------------------------------------|--|--|--|

| No.      | face               | face  | No. | Interface Interface |                                          |  |  |  |

| 1        | vcc                |       | 27  | Vcc                 |                                          |  |  |  |

| 2        | Vcc                |       | 28  | D <sub>12</sub>     | 1/0)                                     |  |  |  |

| 3        | RES (              | 1)    | 29  | D <sub>1</sub> ,    | 1/0)                                     |  |  |  |

| 4        | DREC               | (0)   | 30  | D <sub>14</sub>     | (1/0)                                    |  |  |  |

| 5        | IRQ (              | 0)    | 31  | Dis                 | (1/0)                                    |  |  |  |

| 6        | DONE               | (1)   | 32  | RWDATA (I/O)        | RWDATA (I/O)                             |  |  |  |

| 7        | RS (I)             |       | 33  | WCLK (I)            | WCLK (I)                                 |  |  |  |

| 8        | DTAC               | K (0) | 34  | RCLK (I)            | RCLK (I)                                 |  |  |  |

| 9        | R/₩ (              | 1)    | 35  | SYNC (O)            | SKEND (I)                                |  |  |  |

| 10       | CS (I)             |       | 36  | V <sub>SS</sub>     |                                          |  |  |  |

| 11       | DACK               | (1)   | 37  | v <sub>SS</sub> _   |                                          |  |  |  |

| 12       | D <sub>0</sub> (1/ | O)    | 38  | WGATE (O)           | BUS <sub>o</sub> /BUS <sub>s</sub> (I/O) |  |  |  |

| 13       | D, (I/             | O)    | 39  | EARLY/RGATE (O)     | BUS, /BUS, (I/O)                         |  |  |  |

| 14       | D <sub>2</sub> (1/ | O)    | 40  | LATE/STEP (O)       | BUS, /BUS, (I/O)                         |  |  |  |

| 15       | CLK (              | 1)    | 41  | WFLT (I)            | BUS <sub>3</sub> /BUS <sub>8</sub> (I/O) |  |  |  |

| 16       | VSS                |       | 42  | LCT/DIR (O)         | BUS. /BUS. (1/O)                         |  |  |  |

| <u> </u> | VSS                |       | 43  | IDX/TRKO (I)        | IDX (I)                                  |  |  |  |

| 18       | D, (I/             | (0)   | 44  | SCP (I)             | SEC (1)                                  |  |  |  |

| 19       | D <sub>4</sub> (I/ | O)    | 45  | USELD (I)           | USELD (I)                                |  |  |  |

| 20       | D, (I/             | O)    | 46  | USELO (O)           | TAG1 (0)                                 |  |  |  |

| 21       | D, (1/             | O)    | 47  | USEL1 (O)           | TAG2 (O)                                 |  |  |  |

| 22       | D, (I/             | (O)   | 48  | HSELO (O)           | TAG3 (O)                                 |  |  |  |

| 23       | D <sub>8</sub> (1/ | (0)   | 49  | HSEL1 (O)           | UTAG (O)                                 |  |  |  |

| 24       | D, (1/             | (0)   | 50  | HSEL2 (O)           | TAG5 (O)                                 |  |  |  |

| 25       | D10 (              | 1/0)  | 51  | SEEK (O)            | BUSR/W (O)                               |  |  |  |

| 26       | D <sub>11</sub> (  | 1/0)  | 52  | READY (I)           | BUSL/H (O)                               |  |  |  |

### SIGNAL LINES

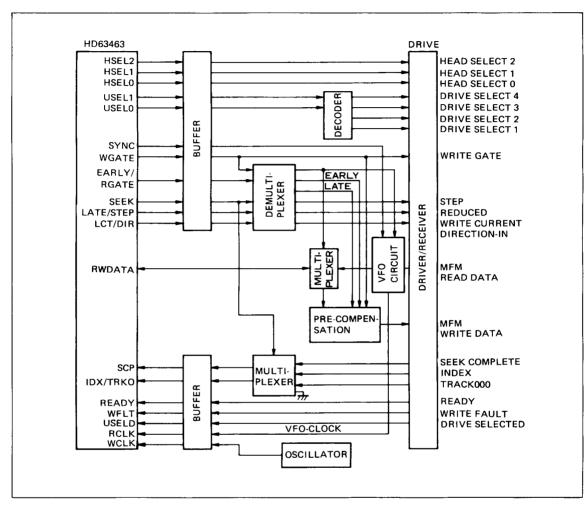

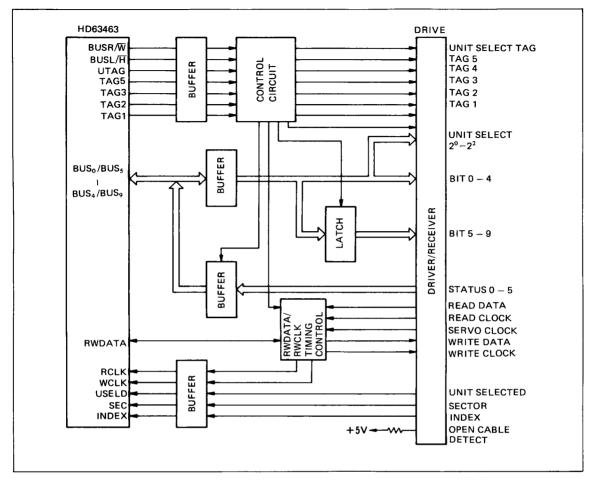

Figure 1 Input/Output Signals

# MAJOR FUNCTIONS OF HDC

| Drive Interface     | ST506*                      | Number of Heads                                            | Max 8                             |  |  |  |

|---------------------|-----------------------------|------------------------------------------------------------|-----------------------------------|--|--|--|

|                     |                             | Number of Drives                                           | Max 4                             |  |  |  |

|                     |                             | Write Precompensation                                      | Controlled                        |  |  |  |

|                     |                             | High-Speed Seek                                            | Step rate min 875 ns (CLK: 8 MHz) |  |  |  |

|                     | Storage Module Drive (SMD)  | Number of Heads                                            | Max 32                            |  |  |  |

|                     |                             | Number of Drives                                           | Max 8                             |  |  |  |

|                     |                             | Track Offset                                               | Controlled                        |  |  |  |

|                     |                             | Data Strobe                                                | Controlled                        |  |  |  |

|                     | Serial Data Format          | NRZ or MFM (selectable)                                    |                                   |  |  |  |

|                     | Serial Data Transfer Rate   | Max 20 Mbps (NRZ), max 10 Mbps (MFM)                       |                                   |  |  |  |

|                     | Multiple Sector Access      | Multiple sector, multiple track                            |                                   |  |  |  |

|                     | Parallel Seek               | Possible                                                   |                                   |  |  |  |

|                     | Diagnosis                   | External circuit diagnosis                                 |                                   |  |  |  |

| Disk Format         | Data Length                 | 256, 512, 1024, 2048, or 4096 bytes (selectable)           |                                   |  |  |  |

|                     | Number of Sectors           | Max 255 (hard sector), max 128 (soft sector)               |                                   |  |  |  |

|                     | Number of Cylinders         | Max 1024                                                   |                                   |  |  |  |

|                     | Sector Format               | Hard sector or soft sector (selectable)                    |                                   |  |  |  |

| Error Processing    | Processing Code             | 16-bit CRC (error detection), 2 types                      |                                   |  |  |  |

|                     |                             | 32-bit ECC (error detection or correction)                 |                                   |  |  |  |

|                     | Error Correction Capability | Automatic correction of single burst error (up to 11 bits) |                                   |  |  |  |

| On-Chip Data Buffer | Capacity                    | 256 bytes × 2                                              |                                   |  |  |  |

|                     | Data Transfer               | Simultaneous transfer on host side and drive side          |                                   |  |  |  |

|                     | Addressing                  | Stack type (pointer can be upda                            | ted)                              |  |  |  |

| Host Interface      | Operation Cycle Time        | Max 8 MHz                                                  |                                   |  |  |  |

|                     | Data Bus Width              | 16 or 8 bits (selectable)                                  |                                   |  |  |  |

|                     | DMA Transfer                | Burst or cycle steal mode (selec                           | table)                            |  |  |  |

|                     | Programmed I/O              | Possible                                                   |                                   |  |  |  |

| Commands            | Seek                        | 2 commands                                                 |                                   |  |  |  |

|                     | Disk Read/Write             | 8 commands                                                 |                                   |  |  |  |

|                     | Data Buffer                 | 4 commands                                                 |                                   |  |  |  |

|                     | Drive Check                 | 2 commands                                                 |                                   |  |  |  |

|                     | Others                      | 6 commands                                                 |                                   |  |  |  |

<sup>\*</sup>ST506/ST412/ST412HP is referred to as "ST506" in this document.

#### HARDWARE DESCRIPTION

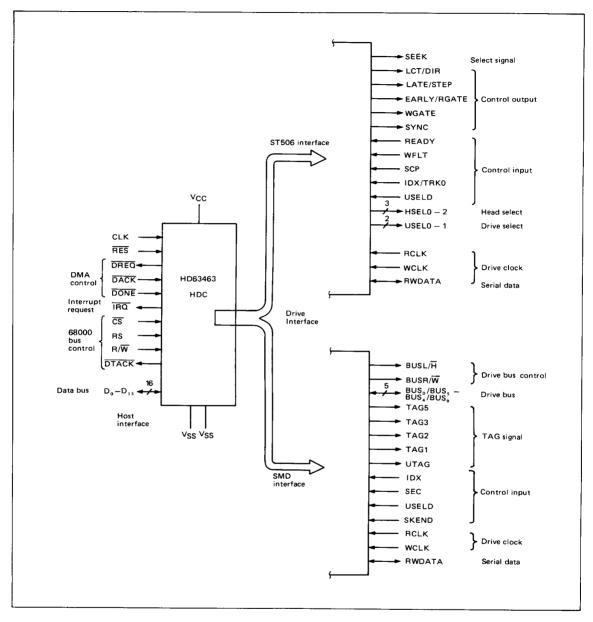

#### SYSTEM CONFIGURATION

An HDC-based system configuration is illustrated in figure 2. The HDC is used to connect more than one hard disk drives (also called "drive" in this manual) to the host system. The host system consists of the MPU (Microprocessing Unit), the main memory and the DMAC (Direct Memory Access Controller). The HDC requires minimum number of external circuits that

are connected to the host system including the HD68000 (MPU) and the HD68450 (DMAC).

If the host system does not require a high throughput, then the DMAC is not necessary. A few additional external circuits allow the HDC to be connected to another host system other than the HD68000.

The HDC may control either up to four ST506 drives or up to eight SMD drives.

Figure 2 System Configuration Example

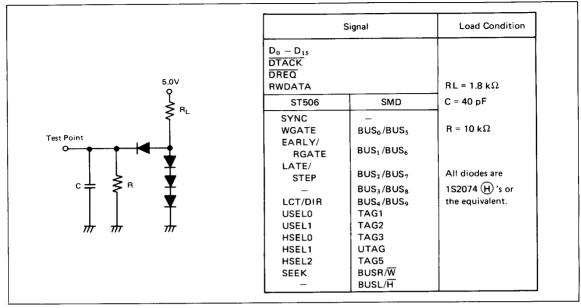

#### SIGNAL LINES

The input/output signal lines of the HDC are shown in figure 1 which covers both ST506 and SMD drive interface.

Each signal is described in the following tables and descriptions.

#### Host Interface

| Category                         | Signal         | 1/0 |

|----------------------------------|----------------|-----|

| Clock, Reset                     | CLK            | 1   |

|                                  | RES            | 1   |

| DMA Control                      | DREQ           | 0   |

| (HD68450                         | DACK           | 1   |

| Compatible)                      | DONE           | l l |

| Interrupt Request                | ĪRΩ            | 0   |

|                                  | CS             | 1   |

| Bus Control<br>(HD68000          | RS             | t   |

| Compatible)                      | R/W            | ı   |

|                                  | DTACK          | 0   |

| Data Bus (HD68000<br>Compatible) | $D_0 - D_{15}$ | I/O |

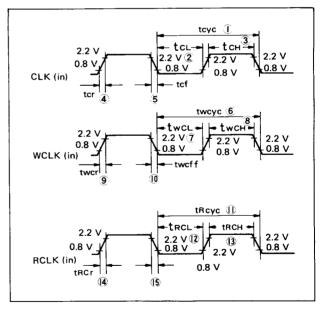

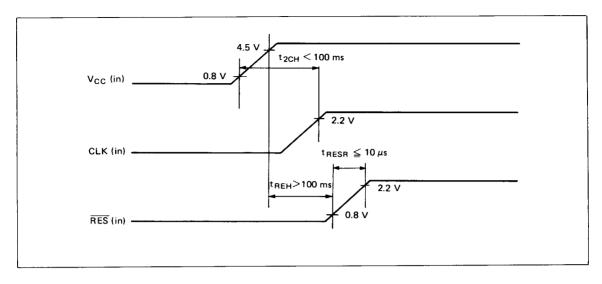

CLK - Clock signal from the host system.

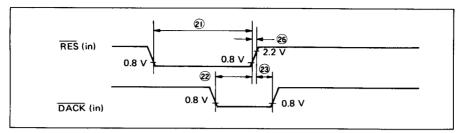

**RES** - Reset signal from the host system.

DREQ — Asserted when a DMA data transfer is requested to the DMAC. Receiving this signal, the DMAC obtains the bus mastership from the MPU.

$\overline{\text{DACK}}$  – Transfer acknowledge signal from the DMAC. Receiving this signal, the HDC transfers data through the host bus in the DMA mode. When  $\overline{\text{RES}}$  signal is at "0", HDC data bus configuration change from 16 bits to 8 bits when  $\overline{\text{DACK}}$  = 0.

**DONE** — Receiving this signal from the DMAC, the DMA data transfer through the host bus stops immediately.

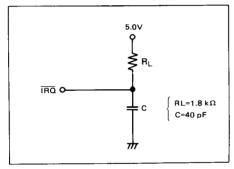

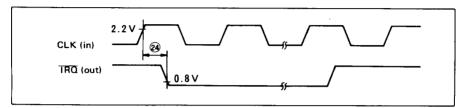

$\overline{IRQ}$  — Interrupt request signal sent to the MPU (open drain output).

**CS** – Chip select signal generated by decoding address, address strobe, and data strobe of the host.

RS - Register select signal of the HDC. It selects registers when set to "0", data buffers when set to "1".

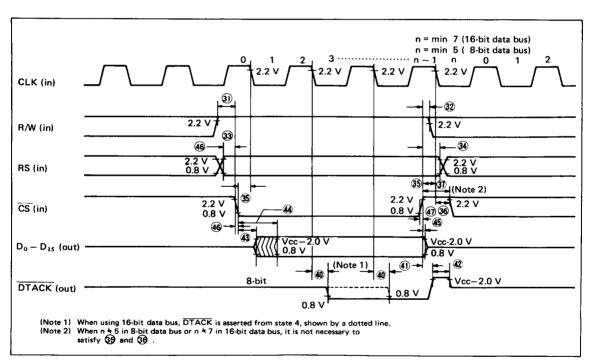

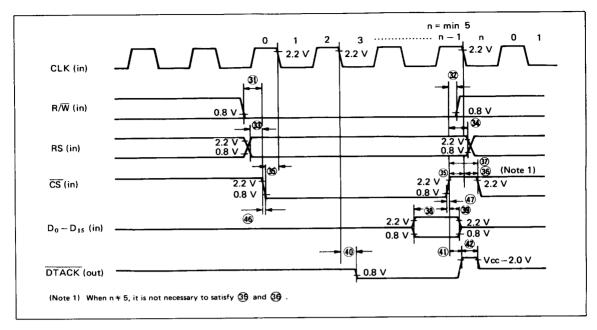

R/W - Signal that indicates the data transfer direction.

**DTACK** — Acknowledge signal that indicates the end of data transfer in the host bus. The host waits until the HDC asserts this signal to terminate the transfer.

$D_0-D_{15}=16\text{-bit}$  bi-directional data bus. When used as an 8-bit data bus,  $D_8-D_{15}$  must be open.

#### ST506 Interface

| Category       | Signal      | 1/0 |

|----------------|-------------|-----|

| Select Signal  | SEEK        | 0   |

| Control Output | LCT/DIR     | 0   |

|                | LATE/STEP   | 0   |

|                | EARLY/RGATE | 0   |

|                | WGATE       | 0   |

|                | SYNC        | 0   |

|                | HSEL0-HSEL2 | 0   |

|                | USEL0-USEL1 | 0   |

| Control Input  | READY       | l l |

|                | WFLT        | 1   |

|                | SCP         | 1   |

|                | IDX/TRK0    | 1   |

|                | USELD       | 1   |

| Drive Clock    | RCLK        | ı   |

|                | WCLK        | ı   |

| Drive Data     | RWDATA      | 1/0 |

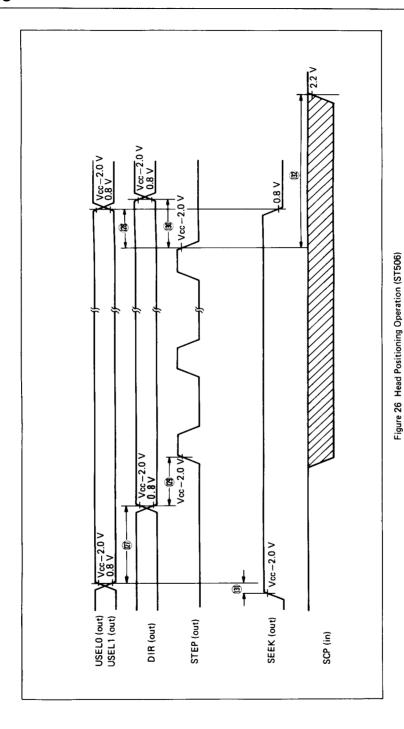

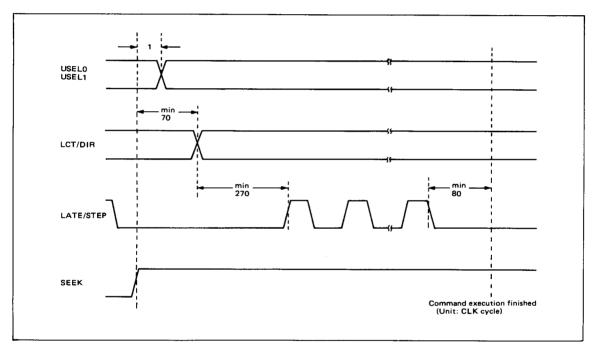

**SEEK** — Used to decode multiplexed signals. SEEK signal remains high during the head positioning operation of the HDC.

LCT/DIR — When SEEK is at "1", this signal indicates the head direction: the head moves toward the spindle if the LCT/DIR signal is at "1". When SEEK is at "0", write current is reduced if this signal is at "1".

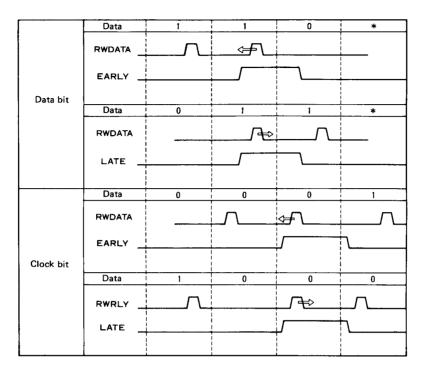

**LATE/STEP** — When SEEK is at "1", this signal serves as step pulses output for head positioning. When SEEK is at "0", this signal requests write precompensation (LATE).

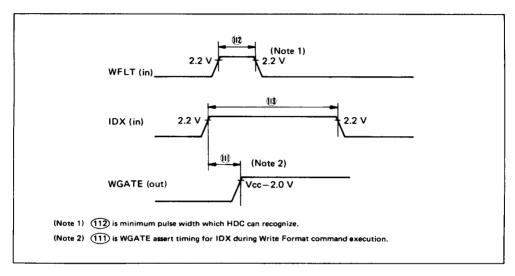

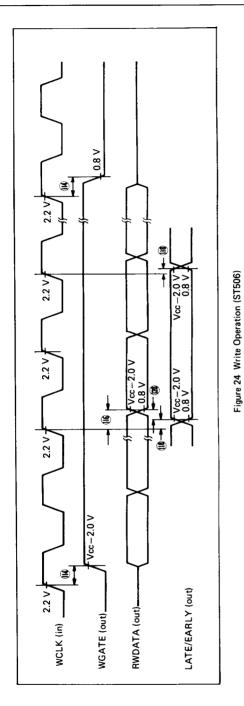

**EARLY/RGATE** — When the WGATE signal is at "1", this signal requires write precompensation (EARLY). Otherwise, it serves as a read gate signal that requests reading data from the drive.

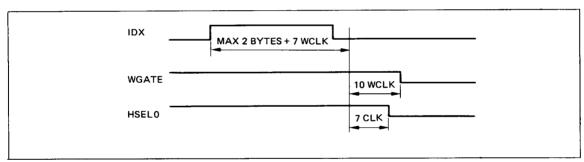

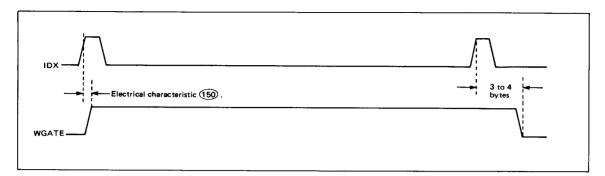

WGATE — Write gate signal that requests writing data to the

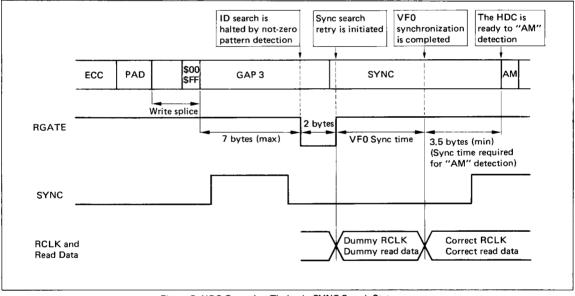

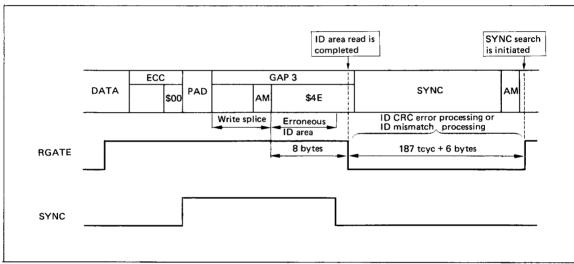

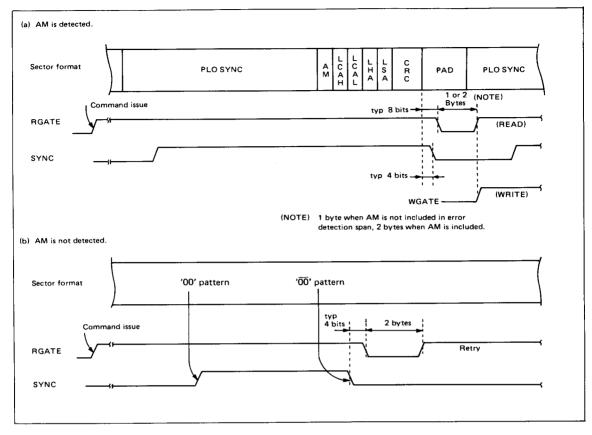

SYNC — Signal to select the loop gain of the external data separator. SYNC is at "1" when RGATE is at "1" and one byte of \$00 is detected in the disk data. SYNC is at "0" when RGATE is at "0".

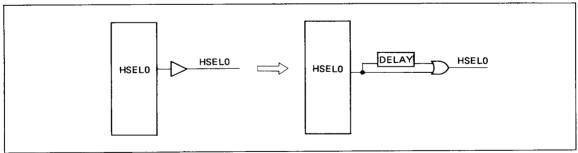

${\sf HSEL0-HSEL2}-3$ -bit signal that selects up to eight heads in the drive.

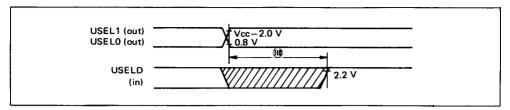

USELO-USEL1 - 2-bit signal that selects one of four drives.

**READY** - Signal indicating that the selected drive is ready.

**WFLT** - Signal indicating that the drive has detected a fault which may cause a write error.

${f SCP}-{f Signal}$  indicating that head positioning (seek operation) has been completed in the drive.

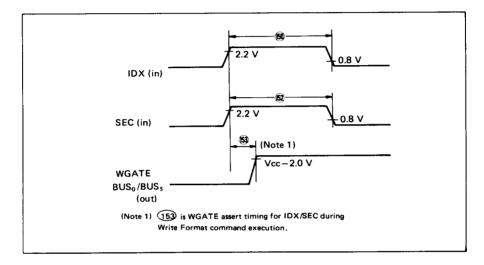

IDX/TRKO — When SEEK is at "1", this signal indicates that the head in the drive is positioned at the outermost track (track 0). When SEEK is at "0", this signal serves as an index signal that indicates the beginning of a track.

**USELD** - Response signal from the drive indicating that the drive is selected.

**RCLK** — Disk read clock from the external data separator. Its frequency is twice the serial transfer rate.

**WCLK** — Disk write clock from the external oscillator. Its frequency is twice the serial transfer rate.

RWDATA — Disk read/write serial data is input/output as modified frequency modulation code. This pin is normally in read state.

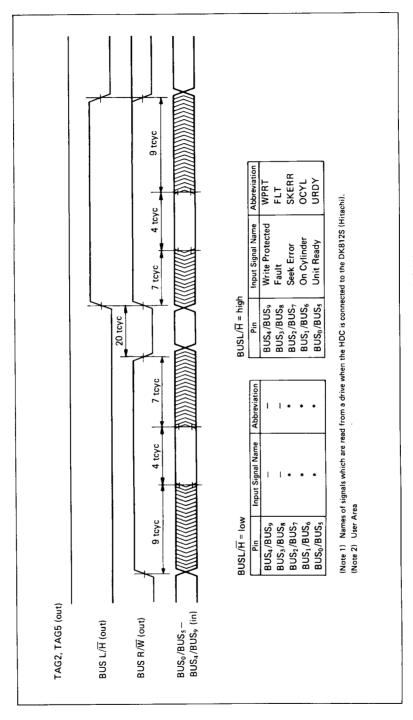

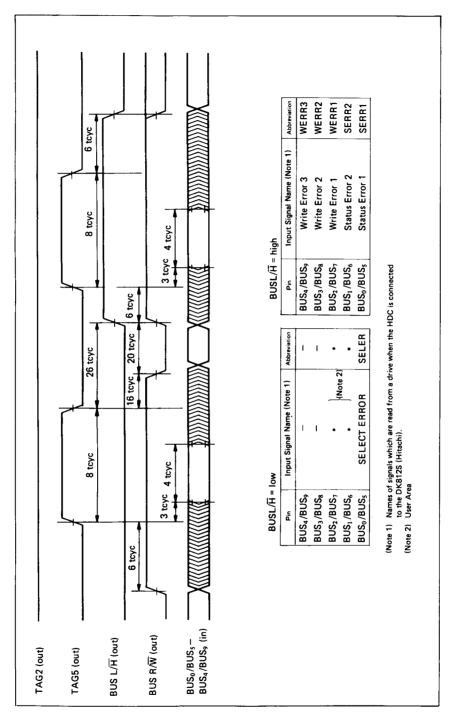

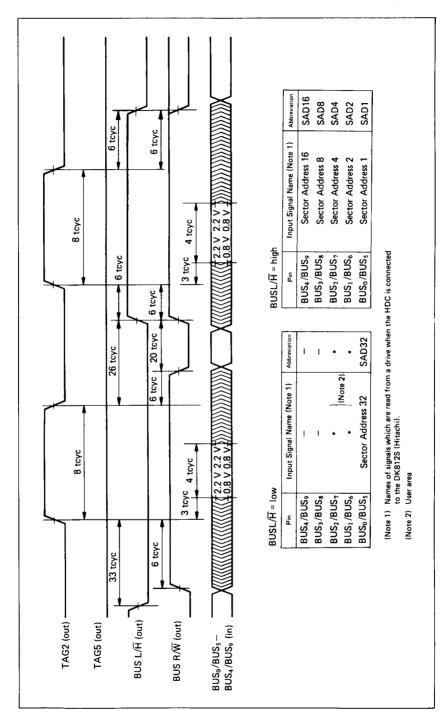

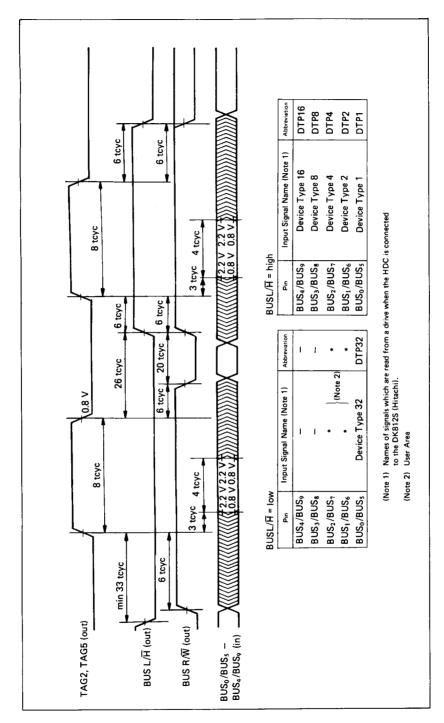

#### SMD Interface

| Category          | Signal                                                                     | 1/0 |

|-------------------|----------------------------------------------------------------------------|-----|

| Drive Bus Control | BUSL/H                                                                     | 0   |

|                   | BUSR/W                                                                     | 0   |

| Drive Bus         | BUS <sub>0</sub> /BUS <sub>5</sub> –<br>BUS <sub>4</sub> /BUS <sub>9</sub> | I/O |

| Tag               | TAG5                                                                       | 0   |

|                   | TAG3                                                                       | 0   |

|                   | TAG2                                                                       | 0   |

|                   | TAG1                                                                       | 0   |

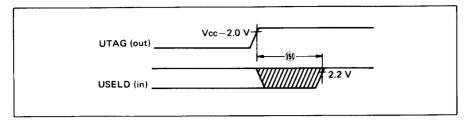

|                   | UTAG                                                                       | 0   |

| Control Input     | IDX                                                                        | 1   |

|                   | SEC                                                                        | I   |

|                   | USELD                                                                      | 1   |

|                   | SKEND                                                                      | 1   |

| Drive Clock       | RCLK                                                                       | 1   |

|                   | WCLK                                                                       | I   |

| Drive Data        | RWDATA                                                                     | I/O |

$BUSL/\overline{H}$  — When this signal is at high, lower 5 bits of 10-bit drive bus are being transferred.

$BUSR/\overline{W}$  — When this signal is at high,  $BUS_0/BUS_5-BUS_4/BUS_9$  are in input state.

BUS<sub>0</sub>/BUS<sub>5</sub> - BUS<sub>4</sub>/BUS<sub>9</sub> - 5-bit bi-directional bus that is used to control the drive. When the data is output from 10-bit drive bus, the high-order 5 bits are output first and then the low-order 5 bits. When the data is input to the bus, higher 3 bits of the 8-bit status are fetched first, then the lower 5 bits.

TAG5 - Together with TAG2, used as a status input select signal.

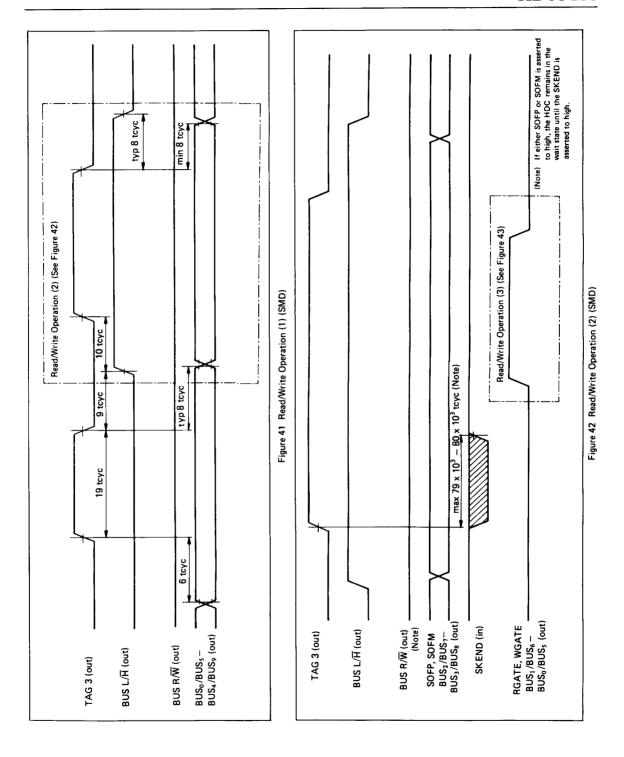

**TAG3** – Tag signal indicating that the drive bus contains information such as disk read/write instruction.

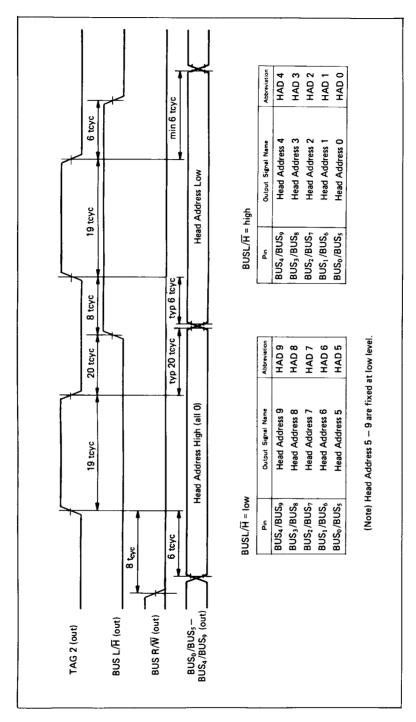

TAG2 — Tag signal indicating that the drive bus contains the address for head selection. When drive status is read from the drive bus, TAG2 and TAG5 are decoded to select the status.

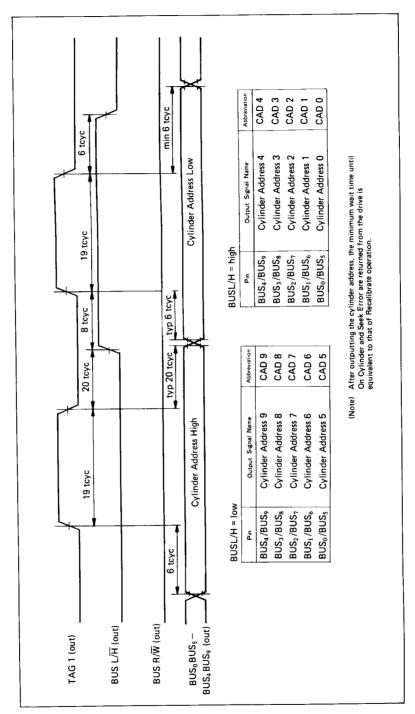

TAG1 - Tag signal indicating that the drive bus contains the destination cylinder address.

UTAG — Tag signal indicating that the drive bus contains a 3-bit drive number.

IDX - Index signal indicating the beginning of a track.

**SEC** – Signal indicating the beginning of a sector.

**USELD** — Response signal from the drive indicating that the drive is selected.

**SKEND** — Signal that is generated when the servo circuit in the disk drive terminates seek operation and the head is placed on the track.

**RCLK** – Disk read clock from the drive. Its frequency is the same as the serial data transfer rate.

**WCLK** – Disk write clock from the drive. Its frequency is the same as the serial data transfer rate.

$\mbox{\bf RWDATA}-\mbox{\bf Disk read/write serial data that is input/output as Non-Return to Zero code.}$

#### HOST INTERFACE

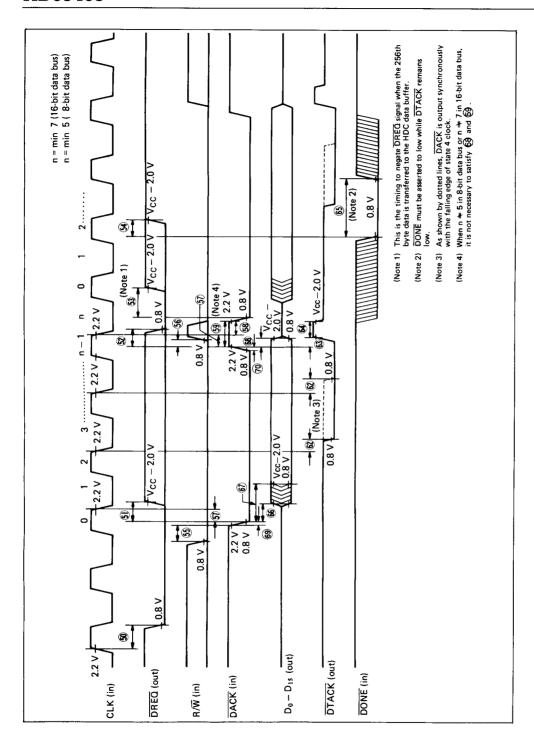

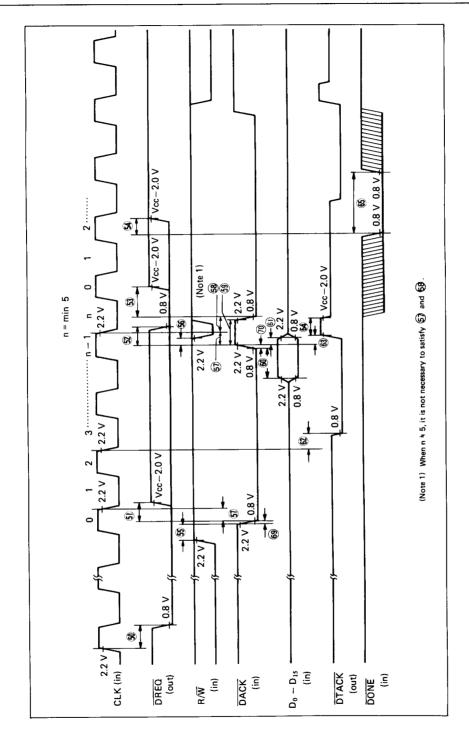

The HDC can be directly connected to the HD68000 (MPU) and the HD68450 (DMAC), so that the HDC data is transferred asynchronously with the host system. The HDC data bus is 16-bit wide, in addition, an 8-bit configuration is available by asserting the  $\overline{DACK}$  signal externally during reset. The minimum access time that is required for communication between the HDC and the MPU, or between the HDC and the DMAC is listed in Table 1 (wait cycles are not included).

Table 1 Host Interface Minimum Access Time

| Data Bus Transfer Direction  | 8-Bit Data Bus<br>(cycles) | 16-Bit Data Bus<br>(cycles) |

|------------------------------|----------------------------|-----------------------------|

| MPU read<br>(HDC to MPU)     | 3                          | 4                           |

| MPU write<br>(MPU to HDC)    | 3                          | 3                           |

| DMA write<br>(memory to HDC) | 3                          | 3                           |

| DMA read<br>(HDC to memory)  | 3                          | 4                           |

#### DRIVE INTERFACE

The HDC can interface with two different types of drives. DIF mode of the Operation Mode register 0 (OM0) selects the drive interface. ST506 interface is selected when DIF is at "0", and

SMD interface when DIF is at "1". The external circuits required for HDC drive interface vary according to which interface is used. Figures 3 and 4 show the interface circuits which connect ST506 device and SMD device respectively.

Figure 3 ST506 Interface Circuit

Figure 4 SMD Interface Circuit

#### SOFTWARE INTERFACE

The HDC is furnished with 22 commands, which are classified into 6 categories; specification, head positioning, disk access, data transfer, drive check, and others.

Table 2 List of Commands

| Category       | Command                    | Mnemonic |

|----------------|----------------------------|----------|

| Specifications | Specify                    | SPC      |

| Head Positiong | Recalibrate                | RCLB     |

|                | Seek                       | SEK      |

| Disk Access    | Read Data                  | RD       |

|                | Read Erroneous Data        | RED      |

|                | Read ID                    | RID      |

|                | Read ID Skew<br>(Note 1)   | RIS      |

|                | Find ID                    | FID      |

|                | Check Data                 | CKD      |

|                | Compare Data               | CMPD     |

|                | Write Data                 | WD       |

|                | Write Format               | WFM      |

|                | Write Format Skew (Note 1) | WFS      |

| Data Transfer  | Memory to Buffer           | МТВ      |

|                | Buffer to Memory           | втм      |

|                | Open Buffer Write          | OPBW     |

|                | Open Buffer Read           | OPBR     |

| Drive Check    | Polling                    | POL      |

|                | Check Drive                | СКУ      |

| Others         | Abort                      | ABT      |

|                | Check ECC                  | CKE      |

|                | Polling Disable            | POD      |

|                | Recall                     | RCAL     |

|                | Test                       | TST      |

(Note 1) Valid only for the hard sector. Disabled for the soft sector.

Specify - Specifies the HDC's operation mode, data transfer mode, etc.

Recalibrate — Moves the drive head to the outermost track (track 0).

Seek — Moves the drive head onto a track specified by the Next Cylinder Address.

Read Data — Reads the data of specified sectors and stores it in the data buffer.

Read Erroneous Data — Reads disk data and stores it in the data buffer no matter a CRC error occurs or not in ID area.

Read ID - Reads ID areas from specified number of sectors.

Read ID Skew - Reads ID area of a sector formatted by Write Format Skew command.

Find ID - Reads ID areas and stores the data in data buffers. ID area containing a CRC error is skipped reading, and the subsequent ID area without any CRC error is searched for.

Check Data — Checks if there is any ECC or CRC error in DATA area of specified sectors. No data is transferred to data buffers or to the main memory while checking.

Compare Data — Compares the data in data buffers and the data read from specified sectors.

Write Data — Writes the data stored in data buffers into DATA area of specified sectors.

Write Format – For the hard sector, formats a specified number of sectors starting with a specified physical sector address. For the soft sector, formats a track.

Write Format Skew — Formats a sector specified by a physical sector address by skewing ID area by 64 bytes.

**Memory to Buffer** – Transfers data from the main memory to the data buffer by DMA transfer.

**Buffer to Memory** — Transfers data stored in the data buffer to the main memory by DMA transfer.

Open Buffer Write — Provides initialization of pointer to write data into the data buffer starting from an address specified by Pointer Offset. The data buffer is written in the PIO mode after the command execution ends.

Open Buffer Read — Provides initialization to read the data stored in the data buffer from an address specified by Pointer Offset. The data buffer is read in the PIO mode after the command execution ends.

Polling - Monitors drive status including seek end.

Check Drive — Sets result parameters indicating status of a specified drive to Parameter Block.

Abort – Stops all operations being executed by the HDC.

**Check ECC** — For ECC errors occurred during RD and RED command execution, reports result parameters indicating addresses and patterns of erroneous data.

Polling Disable - Stops Polling command execution.

Recall — Clears all bits of the status register and sets a buffer pointer to the start address of parameter block so that command parameters can be accepted.

Test — Makes the output pins of the HDC's drive interface three-stated.

Table 3 Command Code, Interrupt Request, and DMA Data Transfer

| Command Name        | Command   | Code  | Interrupt Factor Bits                 |               |             | DMA Transfer   |         |

|---------------------|-----------|-------|---------------------------------------|---------------|-------------|----------------|---------|

| Command Name        | Binary    | HEX   | CED                                   | SED           | DER         | DTM = 0        | DTM = 1 |

| Specify             | 1110 1000 | E8    |                                       |               | l. <u>-</u> |                |         |

| Recalibrate         | 1100 1000 | C8    | 0                                     | 0             | 0           |                |         |

| Seek                | 1100 0000 | CO    | 0                                     | 0             | 0           |                |         |

| Read Data           | 0100 0000 | 40    | 0                                     | 0             | 0           |                | 0       |

| Read Erroneous Data | 0111 0000 | 70    | 0                                     | 0             | 0           |                | 0       |

| Read ID             | 0110 0000 | 60    |                                       |               |             |                |         |

| Read ID Skew        | 0110 1000 | 68    | 0                                     | 0             | 0           |                | 0       |

| Find ID             | 0110 0001 | 61    | 0                                     | 0             | 0           |                | 0       |

| Check Data          | 0100 1000 | 48    | 0                                     | 0             | 0           |                |         |

| Compare Data        | 1000 1000 | 88    | 0                                     | 0             | 0           |                | 0       |

| Write Data          | 1000 0111 | 87    | 0                                     | 0             | 0           |                | 0       |

| Write Format        | 1010 0011 | А3    |                                       |               |             |                |         |

| Write Format Skew   | 1010 1011 | АВ    | 0                                     | 0             | 0           |                | 0       |

| Memory to Buffer    | 1001 0000 | 90    | 0                                     |               |             | 0              | 0       |

| Buffer to Memory    | 0101 0000 | 50    | 0                                     |               |             | 0              | 0       |

| Open Buffer Read    | 0011 0000 | 30    |                                       |               |             |                |         |

| Open Buffer Write   | 0011 1000 | 38    |                                       |               |             |                |         |

| Polling             | 0001 0000 | 10    |                                       | 0             | 0           |                |         |

| Check Drive         | 0010 1000 | 28    |                                       |               | 0           |                |         |

| Abort               | 1111 **** | FO-FF | 0                                     |               |             |                |         |

| Check ECC           | 0010 0000 | 20    | · · · · · · · · · · · · · · · · · · · |               |             |                |         |

| Test                | 1110 0000 | E0    |                                       |               |             |                |         |

| Polling Disable     | 0001 1000 | 18    |                                       | 0             | 0           |                |         |

| Recall              | 0000 1000 | 08    |                                       |               |             |                |         |

| Inhibited           | 1101 **** | D0-DF |                                       | end of commar |             | o: DMA transfe |         |

execution.

DMA: Direct Memory Access DTM: Data Transfer Mode

\*: don't care

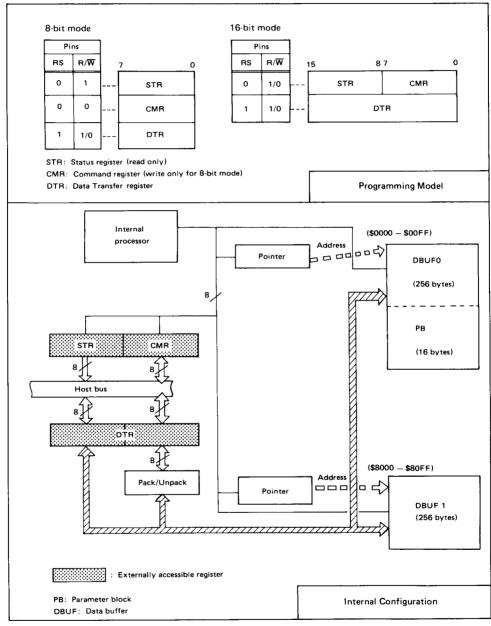

#### PROGRAMMING MODEL

Figure 5 shows the internal configuration of the HDC and a programming model. The HDC internally provides an 8-bit STR (Status register), an 8-bit CMR (Command register), a 16-byte PB (Parameter Block) and two 256-byte data buffers (DBUF0 and DBUF1). The data can be written to/read from PB, DBUF0 and DBUF1 by externally accessing DTR (Data Transfer register). Their address are specified by a pointer, and is incremented for each access. Internal processors set pointer value, or select one of PB, DBUF0 and DBUF1 to be connected to DTR. These internal processors are initialized by writing a command from the MPU to CMR. The result of command execution is reflected in the STR.

At the beginning of the command execution, internal processors read command parameters in PB written by the MPU and determine the command operation mode. At the end of the command execution, the MPU reads result parameters in PB written by internal processors.

When the HDC writes data to a disk, the host system sends disk write data to DBUF, then internal processors write the contents of DBUF into the disk. When the HDC reads data from a disk, internal processors read the contents of the disk and stores them into DBUF, then the host system reads data from DBUF. The MPU can access STR, CMR, and DTR while the DMAC can access only DTR in the single addressing mode.

When used in 8-bit mode, the HDC requires 2-byte address space. One byte (RS (Resister Select signal) = 0) is an 8-bit read only STR or an 8-bit write only CMR. Another byte (RS = 1) is an 8-bit DTR.

When used in a 16-bit mode, the HDC requires 2-word address space. One word (RS = 0) consists of an 8-bit CMR and an 8-bit read only STR. Another word (RS = 1) serves as a 16-bit DTR.

Figure 5 Internal Configuration and Programming Model

When the HDC is either in idle state or command execution end state, the MPU can access PB by accessing DTR. While the HDC is executing a command (during data transfer), DBUF0 or DBUF1 can be accessed by accessing DTR. Before accessing DBUF0 or DBUF1, the MPU must issue a command to open the buffer.

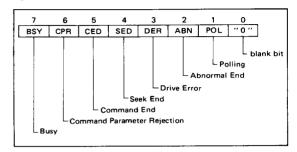

#### STATUS REGISTER

The bit configuration of the Status register is shown in the figure below, and each bit is described in Table 4.

Table 4 Status Register Bit Description

| Bit | Abbr. | Bit Name                          | Set "1"<br>Condition       | Reset "0"<br>Condition                                                              | Interrupt<br>Source Bit | Description                                                                                                                                                                   |

|-----|-------|-----------------------------------|----------------------------|-------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BSY   | Busy                              | Command<br>acknowledged    | Command execu-<br>tion end (except<br>for POL command)                              |                         | While HDC is executing a command, BSY bit is set to "1".                                                                                                                      |

| 6   | CPR   | Command<br>Parameter<br>Rejection | Command<br>execution       | RCAL<br>command<br>received                                                         |                         | With this bit reset to "0", command parameters can be written.                                                                                                                |

| 5   | CED   | Command<br>End                    | Command execution end      | RCAL<br>command<br>received                                                         | 0                       | Set to "1" when command shown in table 3 ends. When this bit is set, HDC asserts IRQ signal.                                                                                  |

| 4   | SED   | Seek End                          | Drive seek end<br>detected | RCAL<br>command<br>received                                                         | 0                       | If detecting drive seek end during execution of command shown in table 3, HDC sets "1" in this bit at the end of command execution.                                           |

| 3   | DER   | Drive Error                       | Drive error<br>detected    | RCAL<br>command<br>received                                                         | 0                       | If detecting drive error during execution of command shown in table 3, HDC sets "1" in this bit at the end of command execution.                                              |

| 2   | ABN   | Abnormal End                      | Error detected             | RCAL<br>command<br>received                                                         |                         | If acknowledging errors such as illegal command, drive faults, data over/under run, the HDC sets "1" to ABN at the end of command execution. The SSB contains the error code. |

| 1   | POL   | Polling                           | POL command received       | POD command<br>received, seek<br>operation end<br>detected, drive<br>error detected |                         | Set to "1" during execution of POL command.                                                                                                                                   |

| 0   |       |                                   |                            |                                                                                     |                         | Blank bit, always set to "0".                                                                                                                                                 |

O: An interrupt is generated when this bit is set.

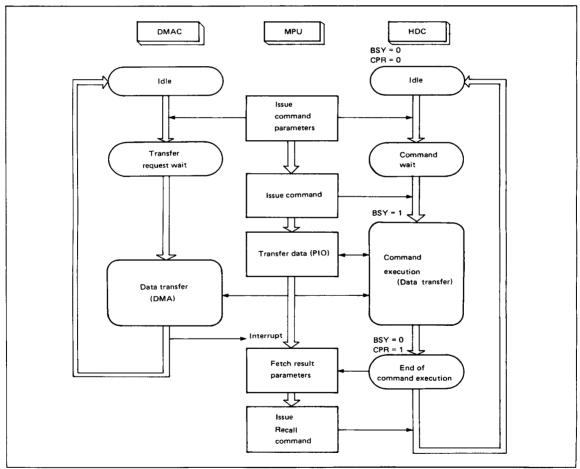

#### HDC CONTROL PROCEDURE

The MPU's procedure to control the HDC is shown in figure 6. To control the HDC, the MPU must read STR of the HDC. The MPU may issue command parameters to PB in the HDC only when both BSY and CPR bits are cleared.

This enables the HDC to change its status from idle state to command wait state. Although a data buffer pointer does not indicate the start address of PB under command wait state, STR has the same contents as in the idle state. It is impossible to distinguish these two internal HDC states externally.

After this, the MPU issues a command. The HDC executes a command after setting BSY bit to "1". At the end of command execution, result parameters are stored in PB, the CPR bit is set to "1", and BSY bit is cleared. Under this condition, the MPU reads result parameters from PB. Issuing Recall command after this enables the HDC state to change from command execution end state to idle state.

Some commands do not require either or both of the command parameter and result parameter. For some commands, the CED bit, SED bit, or DER bit is set to "1", which enables the HDC to generate an interrupt request to the MPU.

In the DMA (direct memory access) mode, data transfer takes place between the main memory and the HDC when a disk access command is received. For this reason, the MPU must initialize the DMAC before issuing a disk access command to the HDC. Data such as system memory address and number of transfer words are written into the DMAC register.

When the MPU writes data into internal control register in the DMAC, the DMAC state changes from the idle state to transfer request wait state. Upon reception of a transfer request signal (DREQ) from the HDC, the DMAC transfers data to/from the HDC and system memory until specified number of words are transferred. The DMAC may generate an interrupt request to the MPU when the transfer is completed.

Figure 6 HDC Control Procedure

#### **COMMAND PARAMETERS**

Command parameters are listed in Table 5. Command parameters used by the HDC to control ST506 type hard disk drive

are listed in the upper row of each command, and those for the SMD type in the lower row.

Table 5 Command Parameter (byte organization)

| Commands                                   | Parameters (Upper row: ST506 Lower row: SMD)                                                                                           |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Specify                                    | OMO OM1 OM2 CUL TO/NCH NCL NH NS SH/RL GPL1 GPL2 GPL3 LCCH LCCL<br>PCCH PCCL<br>OMO OM1 OM2 CUL TO/NCH NCL NH NS SH/RL GPL1 GPL2 RGTLT |

| Recalibrate                                | US \$00<br>US \$00                                                                                                                     |

| Seek                                       | US \$00 NCAH NCAL<br>US \$00 NCAH NCAL                                                                                                 |

| Read Data                                  | US PHA LCAH LCAL LHA LSA SCNTH SCNTL<br>US PHA \$00 FLAG LCAH LCAL LHA LSA SCNTH SCNTL                                                 |

| Read Erroneous Data                        | US PHA SCNTH SCNTL<br>US PHA \$00 PSA SCNTH SCNTL                                                                                      |

| Read ID Skew (Note 1)                      | US PHA \$00 OFFSET \$00 SCNTL<br>US PHA \$00 PSA \$00 SCNTL                                                                            |

| Find ID                                    | US PHA \$00 OFFSET \$00 SCNTL<br>US PHA \$00 PSA \$00 SCNTL                                                                            |

| Check Data                                 | US PHA LCAH LCAL LHA LSA SCNTH SCNTL US PHA \$00 FLAG LCAH LCAL LHA LSA SCNTH SCNTL                                                    |

| Compare Data                               | US PHA LCAH LCAL LHA LSA SCNTH SCNTL<br>US PHA \$00 FLAG LCAH LCAL LHA LSA SCNTH SCNTL                                                 |

| Write Data                                 | US PHA LCAH LCAL LHA LSA SCNTH SCNTL<br>US PHA \$00 FLAG LCAH LCAL LHA LSA SCNTH SCNTL                                                 |

| Write Format<br>Write Format Skew (Note 1) | US PHA SCNTH SCNTL<br>US PHA \$00 PSA SCNTH SCNTL                                                                                      |

| Memory to Buffer                           | POFFH POFFL POFFH POFFL                                                                                                                |

| Buffer to Memory                           | POFFH POFFL POFFH POFFL                                                                                                                |

| Open Buffer Read                           | POFFH POFFL POFFH POFFL                                                                                                                |

| Open Buffer Write                          | POFFH POFFL POFFH POFFL                                                                                                                |

| Polling                                    | None                                                                                                                                   |

| Check Drive                                | US \$00<br>US \$00                                                                                                                     |

| Abort                                      | None                                                                                                                                   |

| Check ECC                                  | None                                                                                                                                   |

| Test                                       | None                                                                                                                                   |

| Polling Disable                            | None                                                                                                                                   |

| Recall                                     | None                                                                                                                                   |

(Note 1) Read ID Skew and Write Format Skew are valid only for SMD interface.

#### SPECIFY COMMAND PARAMETERS

Parameters of SPC command may be used to specify the HDC operation mode and the disk format. Parameters are listed in table 6. Contents of these parameters are different according to which type of drive is used: either ST506 or SMD. Each parameter is described in tables 7 and 8. Table 7 lists parameters

which are specified by a bit, and table 8 lists parameters which are specified by 3-16 bits.

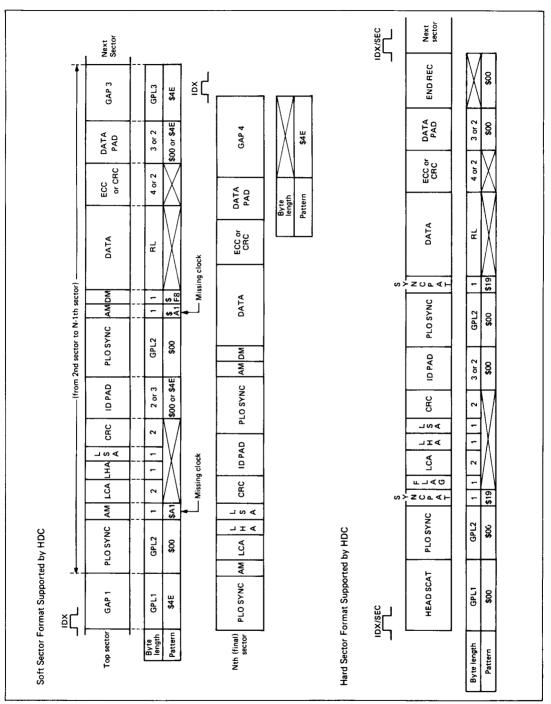

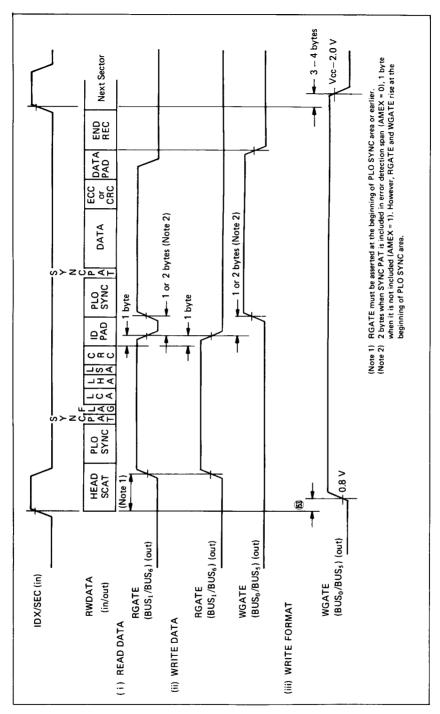

The HDC supports soft sector format (in ST506 interface) and hard sector format (in SMD interface) which are shown in figure 7.

Table 6 Specify Command Parameter Organization

| CRCP<br>0 | CRCI       | ACOR<br>PSK |  |  |  |  |  |  |  |

|-----------|------------|-------------|--|--|--|--|--|--|--|

| и о       | AMEX       | PSK         |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

|           | SL (ST506) |             |  |  |  |  |  |  |  |

| CUL       |            |             |  |  |  |  |  |  |  |

|           | N          | сн          |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

| SH RL     |            |             |  |  |  |  |  |  |  |

| GPL1      |            |             |  |  |  |  |  |  |  |

| GPL2      |            |             |  |  |  |  |  |  |  |

| _         |            |             |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

|           |            |             |  |  |  |  |  |  |  |

| M SOFP    | STBL       | STBE        |  |  |  |  |  |  |  |

|           | M SOFP     | RL          |  |  |  |  |  |  |  |

Table 7 Specify Command Parameters (a)

| Abbreviation | Name                 |                     |                                                        |      | SMD |

|--------------|----------------------|---------------------|--------------------------------------------------------|------|-----|

|              |                      | 0                   | 1                                                      |      |     |

| SECT         | Sector Organization  | Soft Sector         | Hard Sector                                            | 0    | 1   |

| MOD          | Data Modulation      | MFM                 | NRZ                                                    | 0    | 1   |

| DIF          | Drive Interface      | ST506               | SMD                                                    | 0    | 1   |

| PADP         | PAD Pattern          | \$00                | \$4E                                                   | *    | 0   |

| ECD          | Error Check Code     | CRC                 | ECC                                                    | *    | *   |

| CRCP         | CRC Polynomial       | X <sup>16</sup> + 1 | X <sup>16</sup> + X <sup>12</sup> + X <sup>5</sup> + 1 | *    | *   |

| CRCI         | CRC Initial Value    | \$0000              | \$FFFF                                                 | *    | *   |

| ACOR         | Automatic Correction | Disabled            | Enabled                                                | *    | *   |

| DTM          | Data Transfer Mode   | PIO                 | DMA                                                    | *    | *   |

| BRST         | DMA Burst Mode       | Cycle Steal         | Burst                                                  | *    | *   |

| CEDM         | Command End Mask     | Unmasked            | Masked                                                 | *    | *   |

| SEDM         | Seek End Mask        | Unmasked            | Masked                                                 | *    | *   |

| DERM         | Drive Error Mask     | Unmasked            | Masked                                                 | *    | *   |

| AMEX         | Address Mark Exclude | Included            | Not Included                                           | •    | *   |

| PSK          | Parallel Seek        | Normal              | Parallel                                               | *    | 1   |

| SOFM         | Servo Offset Minus   | Normal              | Minus                                                  | None | *   |

| SOFP         | Servo Offset Plus    | Normal              | Plus                                                   | None | *   |

| STBL         | Strobe Late          | Normal              | Late                                                   | None | *   |

| STBE         | Strobe Early         | Normal              | Early                                                  | None | *   |

<sup>•</sup> Either 0 or 1

Table 8 Specify Command Parameters (b)

| Abbreviation | Name                     | ST506    | SMD              |

|--------------|--------------------------|----------|------------------|

| SL           | Step Pulse Low           | 8 bits   | None             |

| CUL          | Connecting Unit List     | 4 bits   | 8 bits           |

| то           | Read/Write Time-over     | 6 bits   | 6 bits           |

| NC           | Number of Cylinders      | 10 bits  | 10 bits          |

| NH           | Number of Heads          | 3 bits   | 5 bits           |

| NS           | Number of Sectors        | 8 bits   | 8 bits           |

| SH           | Step Pulse High          | 5 bits   | None             |

| RL           | Record Length            | 3 bits   | 3 bits           |

| GPL1         | Gap Length 1 (8 bits)    | GAP1     | HEAD SCAT        |

| GPL2         | Gap Length 2 (8 bits)    | PLO SYNC | PLO SYNC         |

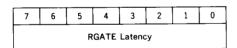

| GPL3         | Gap Length 3 (8 bits)    | GAP3     | RGATE<br>Latency |

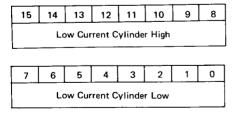

| LCC          | Low Current Cylinder     | 16 bits  | None             |

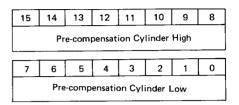

| PCC          | Precompensation Cylinder | 16 bits  | None             |

Figure 7 Disk Format

#### OM0 (Operation Mode 0)

# (1) SECT (Sector Format) bit

This bit specifies the format of the drive to be connected to the HDC. There are two drive formats available: hard sector and soft sector.

### (2) MOD (Modulation) bit

This bit specifies modulation mode for data written to/read from the drive.

| MOD = 1: | NRZ (Non Return to Zero) |

|----------|--------------------------|

| MOD = 0: | MEM (Modified FM)        |

#### (3) DIF (Drive Interface) bit

This bit specifies the type of drive interface: either ST506 or SMD. The pin function of the HDC changes according to the interface type.

In SMD interface, the HDC performs seek instruction, head specification, drive status check, etc to the drive through 5-bit bi-directional buffer BUS<sub>0</sub>/BUS<sub>5</sub>-BUS<sub>4</sub>/BUS<sub>9</sub>.

In ST506 interface, the HDC makes the drive perform seek operation by issuing step pulses.

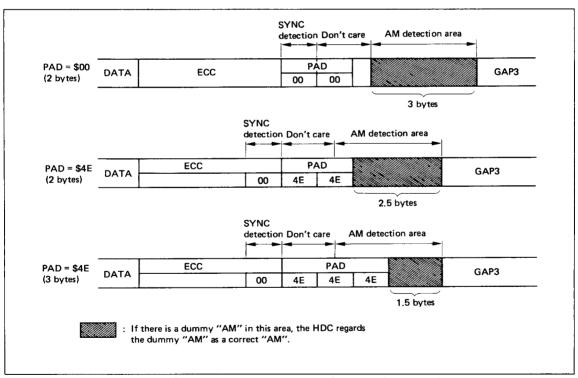

#### (4) PADP (PAD Pattern) bit

This bit specifies the data pattern of PAD area that follows ID and DATA areas. The value of the PADP bit gives the data pattern of PAD area that is written into the drive by WFM or WD command execution.

|          | Hard Sector | Soft Sector |

|----------|-------------|-------------|

| PADP = 1 | Prohibited  | \$4E        |

| PADP = 0 | \$00        | \$00        |

#### (5) ECD (Error Check Code) bit

This bit specifies the error check code which is added to the end of the DATA area. CRC code is always specified for the ID area regardless of ECD bit.

ECC enables error detection and correction. A 4-byte ECC code is added to the end of DATA area. A generation polynominal G(x) of ECC is as follows (the initial value is fixed to "00").

$$G(x) = (x^{21} + 1) (x^{11} + x^2 + 1)$$

=  $x^{32} + x^{23} + x^{21} + x^{11} + x^2 + 1$

CRC enables error detection, but not error correction. A 2-byte CRC code is added to the end of DATA area. A generation polynominal G(x) of CRC is specified by the CRCP bit.

# (6) CRCP (CRC Polynominal) bit

This bit determines the polynominal G(x) that generates CRC of ID and DATA areas when ECD = 0.

CRCP = 1:

$$G(x) = x^{16} + x^{12} + x^5 + 1$$

CRCP = 0:  $G(x) = x^{16} + 1$

#### (7) CRCI (CRC Initial) bit

This bit sets the initial value of CRC.

# (8) ACOR (Automatic Correction) bit

This bit selects whether or not the HDC will automatically correct an error detected in DATA area during RD command execution.

| ACOR = 1: Automatic correction is performed.     |

|--------------------------------------------------|

| ACOR = 0: Automatic correction is not performed. |

Automatic correction mode is valid when ECC is specified as the error check code of DATA area and the sector length is 256 bytes (RL = \$01, ECD = 1). For any other cases specify "0" to the ACOR bit.

#### OM1 (Operation Mode 1)

#### (1) DTM (Data Transfer Mode) bit

This bit is used to specify data transfer operation between the HDC and the main memory during the execution of the following commands:

| RD   | RED | RID |

|------|-----|-----|

| RIS  | FID | WD  |

| CMPD | WFM | WFS |

These commands normally perform transfer between drive and memory via HDC data buffers. However, it is possible to cease transfer between the HDC and memory during these command execution by utilizing DTM bit.

| DTM = 1: | DMA mode |

|----------|----------|

| DTM = 0: | PIO mode |

In DMA mode, the HDC performs transfer between drive and memory via HDC data buffer. In this case, DMA transfer is performed between the HDC and memory, and transfer mode is specified by BRST bit.

In PIO mode, the HDC performs transfer between drive and the HDC. In this case, transfer between the HDC and main

memory must be supported by the host system using one of four buffer access commands of the HDC: MTB, BTM, OPBR, and OPBW.

### (2) BRST (DMA Burst) bit

This bit specifies DMA transfer mode of buffer access commands and drive access commands which perform transfer between the HDC and the main memory.

| BRST = 1: | Burst mode       |

|-----------|------------------|

| BRST = 0: | Cycle Steal mode |

### (3) CEDM, SEDM, DERM bits

CEDM (Command End Mask), SEDM (Seek End Mask), and DERM (Drive Error Mask) bits specify whether the IRQ signal is to be asserted or not. CEDM, SEDM, and DERM correspond to CED (Command End), SED (Seek End), and DER (Drive Error) bits in STR (Status register).

| 1: | IRQ is masked (not asserted). |

|----|-------------------------------|

| 0: | IRQ is not masked (asserted). |

| Mask bit Corresponding bits in STR |     | g bits in STR |

|------------------------------------|-----|---------------|

| CEDM                               | CED | bit 5         |

| SEDM                               | SED | bit 4         |

| DERM                               | DER | bit 3         |

# (4) AMEX (Address Mark Excluded) bit

This bit specifies whether or not the byte-synchronization pattern marking the beginning of ID area or DATA area (AM in soft sector, SYNCPAT in hard sector) is to be included in the CRC or ECC error detection span. The AMEX bit affects the byte length of ID PAD area and DATA PAD area.

|          | AM or SYNCPAT | PAD Length |

|----------|---------------|------------|

| AMEX = 1 | Excluded      | 2 bytes    |

| AMEX = 0 | Included      | 3 bytes    |

#### (5) PSK (Parallel Seek) bit

This bit specifies seek operation mode, and is valid only in ST506 interface (in SMD interface, PSK must be fixed to "1"). The HDC specifies step pulse issue timing by utilizing the value of OM2, SH, and PSK bits.

| PSK = 0: | Normal Seek mode   |

|----------|--------------------|

| PSK = 1: | Parallel Seek mode |

In Normal Seek mode, the HDC issues step pulses in long cycle (0.1-32 ms). SEK and RCLB command execution ends when the HDC issues step pulses and then detects seek end.

In Parallel Seek mode, the HDC issues step pulses in short cycle (0.5–115  $\mu$ s). SEK and RCLB command execution ends when the HDC issues step pulses. Since the HDC does not check the seek end, parallel seek operation in multiple drives is realized by issuing SEK or RCLB command to these drives. Seek end is to be checked by using POL command.

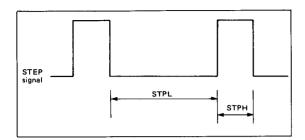

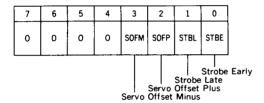

#### OM2 (Operation Mode 2)

This 8-bit register specifies step pulse low width in ST506 interface, and specifies drive control output signal during disk read command execution in SMD interface.

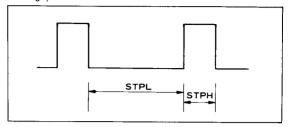

In ST506 interface, OM2 indicates SL which specifies step pulse low width (STPL: Step Pulse Low). Low-speed seek mode (Normal Seek mode) is selected when PSK = 0, and high-speed seek mode (Parallel Seek mode) is selected when PSK = 1. Highest seek speed is realized when PSK = 1 and SL = \$FF. The relation between step pulse low width and SL is shown in the following table (see Step Pulse High/Record Length register to specify step pulse high width).

| 7 | 6 | 5   | 4       | 3    | 2   | 1 | 0 |

|---|---|-----|---------|------|-----|---|---|

|   |   | Ste | p Pulse | Low( | SL) |   |   |

| Seek Mode               | SL                               | STPL (step pulse low)                                                |

|-------------------------|----------------------------------|----------------------------------------------------------------------|

| Normal seek (PSK = 0)   | SL = \$00                        | STPL = 988 CLK                                                       |

|                         | \$01 ≤ SL ≤ \$FE<br>(1) (254)    | STPL = (SL - 1) x 1280 + 2364 CLK<br>(2364 CLK ≤ STPL ≤ 326204 CLK)  |

|                         | SL = \$FF                        | Disabled                                                             |

| Parallel seek (PSK = 1) | SL = \$00                        | STPL = 27CLK                                                         |

|                         | $\$01 \le SL \le \$FE$ (1) (254) | STPL = SL $\times$ 6 + 28 CLK<br>(34CLK $\leq$ STPL $\leq$ 1152 CLK) |

|                         | SL = \$FF                        | STPL = 5CLK                                                          |

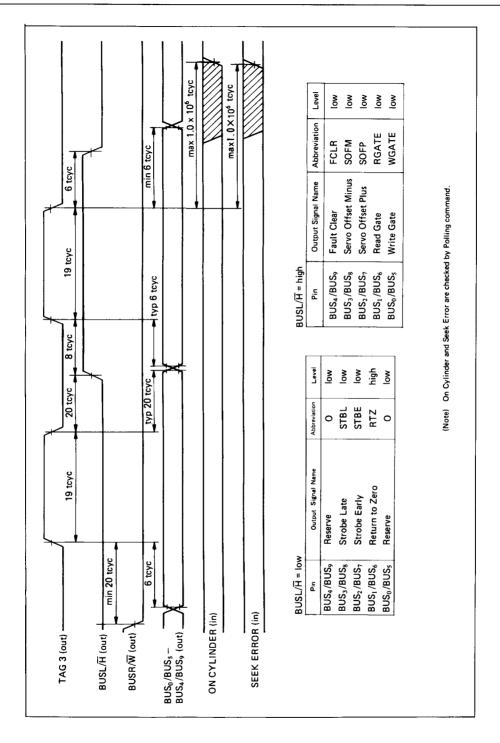

In SMD interface, OM2 specifies drive control output signal from the HDC during data read command execution. In data write command (all the commands that assert WGATE signal) and SEK, RCLB command execution, outputs of drive control signals are low regardless of the contents of OM2. Bits 4-7 in OM2 are to be set to "0".

SOFM bit: With SOFM = 1, the drive head is offset from the normal position away from the spindle.

SOFP bit: With SOFP = 1, the drive head is offset from

the normal position towards the spindle. With STBL = 1, the data from the drive PLO

STBL bit: data separator is strobed later than usual.

STBE bit: With STBE = 1, the data from the drive PLO data separator is strobed earlier than usual.

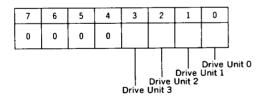

#### CUL (Connecting Unit List)

This register stores bit-map information indicating which drive is connected to the HDC.

In ST506 interface, bits 0-3 correspond to drives 0-3 respectively. To connect a drive, write "1" into the corresponding bit (up to 4 drives can be connected).

In SMD interface, bits 0-7 correspond to drives 0-7 respectively. To connect a drive, write "1" into the corresponding bit (up to 8 drives can be connected).

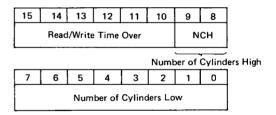

# TO/NCH, NCL (Read/Write Time Over, Number of Cylinders

NCH and NCL registers specify the number of cylinders in disk drive, and time-over during disk access command execution.

#### (1) TO (Read/Write Time Over)

The high-order 6 bits in TO/NCH are used to assign the ID search time: time-over (tover). According to the value of TO, the HDC sets time-over period as follows.

$\$01 \le TO \le \$3F$  (TO = \$00 is prohibited.)

$\overline{TO \times 8} \times 10^4 \text{ CLK} \le t_{\text{over}} \le (\overline{TO} + 1) \times 8 \times 10^4 \text{ CLK}$

#### (2) NC (Number of Cylinders)

The low-order 2 bits of TO/NCH and 8 bits of NCL specify the number of cylinders (NC). NC is 1023 at a maximum. Its value is number of cylinders minus 1.

The HDC uses NC to issue NC + 10 step pulses during RCLB command execution (ST506 interface), or to check whether or not the command parameter NCA (Next Cylinder Address) exceeds NC during SEK command execution.

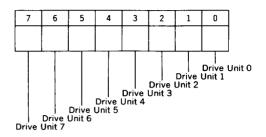

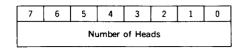

#### NH (Number of Heads)

This register indicates the number of heads. Its value is to be number of drive heads minus 1.

In disk access command execution, the HDC checks whether or not PHA (Physical Head Address) specified by command parameters exceeds NH. When PHA exceeds NH, the HDC sets IPH (Invalid Physical Head Address) to result parameter SSB (Sense Status Byte) and abnormally terminates the execution.

To select a head during multiple track operation in disk access command execution, the HDC checks whether PHA exceeds NH or not. When PHA exceeds NH, the HDC sets IPH to SSB and abnormally terminates the execution.

In ST506 interface, up to 8 heads can be selected ( $$00 \le NH \le $07$ ). Bits 3-7 must be fixed to "0".

| 7 | 6 | 5 | 4 | 3 | 2              | 1  | 0  |

|---|---|---|---|---|----------------|----|----|

| 0 | 0 | 0 | 0 | 0 | 2 <sup>2</sup> | 21 | 2º |

In SMD interface, up to 32 heads can be selected ( $\$00 \le NH \le \$1F$ ). Bits 5-7 must be fixed to "0".

| 7 | 6 | 5 | 4  | 3  | 2  | 1  | 0  |

|---|---|---|----|----|----|----|----|

| 0 | 0 | 0 | 24 | 2³ | 2² | 2¹ | 2º |

#### NS (Number of Sectors)

This register indicates the number of sectors. Its value is number of sectors/track minus 1 ( $\$00 \le NS \le \$FE$ ).

In data read/write command execution, the HDC checks whether LSA (Logical Sector Address) exceeds NS or not.

In multiple sector operation in data read/write command execution, the HDC checks whether LSA exceeds NS or not each time LSA is incremented after one sector operation. If LSA exceeds NS, the HDC sets "0" to LSA, increments LHA and PHA, and compares NH and PHA. If NH exceeds PHA, the HDC executes multiple track operation. If PHA exceeds NH, the HDC sets IPH (Invalid Physical Head Address) to result parameter SSB and abnormally terminates the execution.

| 6                 | 5 | 4             | 3                 | 2                       | 1                            | 0                              |  |

|-------------------|---|---------------|-------------------|-------------------------|------------------------------|--------------------------------|--|

| Number of Sectors |   |               |                   |                         |                              |                                |  |

|                   | 6 | 6   5  <br>Nu | 6 5 4<br>Number o | 6 5 4 3  Number of Sect | 6 5 4 3 2  Number of Sectors | 6 5 4 3 2 1  Number of Sectors |  |

#### SH/RL (Step Pulse High/Record Length)

| 7 | 6      | 5        | 4      | 3 | 2    | 1               | 0    |

|---|--------|----------|--------|---|------|-----------------|------|

| S | tep Pu | ılse Hig | gh (SH | ) | Reco | ord Ler<br>(RL) | ngth |

# (1) SH (Step Pulse High)

The high-order 5-bit SH/RL indicates step pulse high width (STPH: Step Pulse High) in ST506 interface.

STPH is fixed to 2CLK in highest speed seek mode (PSK = 1 and SL = \$FF). Otherwise, SH sets STPH regardless of the PSK bit. The relation between STPH and SH is shown in the following table. SH is ignored when maximum speed seek mode is selected in ST506 interface.

In SMD interface, the high-order 5 bits are to be fixed to "0"

| SH                              | STPH (step pulse high)                           |  |  |  |  |  |

|---------------------------------|--------------------------------------------------|--|--|--|--|--|

| SH = *<br>* : don't care        | STPH = 2 CLK (Note 1)                            |  |  |  |  |  |

| SH = \$00                       | STPH = 3 CLK                                     |  |  |  |  |  |

| $\$01 \le SH \le \$1F$ (1) (31) | STPH = SH x 3 + 1 CLK<br>(4 CLK ≤ STPH ≤ 94 CLK) |  |  |  |  |  |

(Note 1) Highest-speed seek mode (PSK = 1, SL = \$FF)

## (2) RL (Record Length)

The low-order 3-bit SH/RL indicates record length per sector.

|       | RL    |       | Record Length |

|-------|-------|-------|---------------|

| Bit 2 | Bit 1 | Bit 0 | Necora Length |

| 0     | 0     | 0     | Inhibited     |

| 0     | 0     | 1     | 256 bytes     |

| 0     | 1     | 0     | 512 bytes     |

| 0     | 1     | 1     | 1024 bytes    |

| 1     | 0     | О     | 2048 bytes    |

| 1     | 0     | 1     | 4096 bytes    |

| 1     | 1     | 0     | Inhibited     |

| 1     | 1     | 1     | Inhibited     |

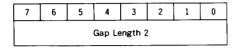

#### GPL1, 2 (Gap Length 1, 2)

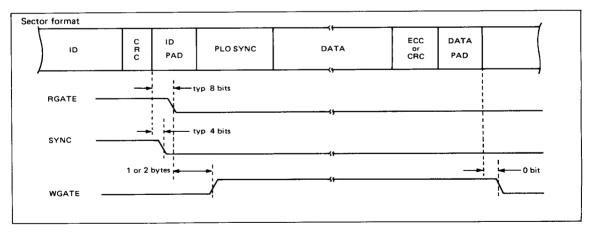

These registers specify the length of gap and SYNC area in the sector during WD and WFM command execution.

GPL1 specifies the length of gap areas (GAP1 in soft sector, HEAD SCAT in hard sector) that follow an index or a sector pulse by byte. It is used for WFM command execution. These areas are formatted 6 bytes longer than the value set to GPL1 during the command execution. [ $\$00 \le GPL1 \le \$FF$ ]

| 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------|---|---|---|---|---|---|---|

| Gap Length 1 |   |   |   |   |   |   |   |

GPL2 specifies the length of SYNC area located at the beginning of ID and DATA areas by byte. It is used for WD and WFM commands. This area is formatted 3 bytes longer than the value set to GPL2 during the command execution. [ $$08 \le GPL2 \le $FF$ ]

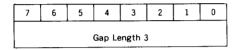

#### GPL3/RGTLT (Gap Length 3, Read Gate Latency)

GPL3/RGTLT specifies the length of GAP3 for the soft sector and read gate latency delay for the hard sector by byte.

GPL3 specifies the length of GAP3 located at the end of a sector in soft sector format by byte. It is used for WFM command. This area is formatted 3 bytes longer than the value set to GPL3. [ $\$09 \le GPL3 \le \$FF$ ]

RGTLT specifies the time period between the detection of an index or a sector pulse and the assertion of RGATE in unit of byte. It is used for disk read commands. RGATE is asserted 5 bytes later than the value set to RGTLT. RGTLT must be set to assert RGATE at the beginning of or before PLO SYNC area in the ID field. During RIS command execution, 64 bytes are added to the amount of latency automatically. [ $\$00 \le RGTLT \le \$FF$ ]

#### LCCH, LCCL (Low Current Cylinder High/Low)

For the inner cylinders of the drive, it is necessary to reduce write current during WFM and WD command execution. These registers specify address of the outermost cylinder from where write current is reduced. This is valid only in ST506 interface. When a disk write command is executed to any cylinder whose address is equal to or greater than LCC, the HDC asserts the LCT pin to high.  $[\$0000 \le LCC \le NC \text{ (Number of Cylinders)}]$

#### PCC (Precompensation Cylinder)

This register specifies the address of the outermost cylinder from where compensation of the bit data timing is required. This is valid only in ST506 interface. When a disk write command is executed to any cylinder whose address is equal to or greater than PCC, either EARLY or LATE signal is generated in accordance with the bit data timing. [ $$0000 \le PCC \le NC$ ]

#### OTHER COMMAND PARAMETERS

The following describes command parameters other than SPC command parameters in alphabetical order.

#### (1) FLAG

This parameter is used to specify the FLAG byte of ID area of a hard sector that the HDC will access. If the FLAG given by the command parameter does not match the FLAG read from ID area of the disk, the HDC will not access the sector.

#### (2) LCA (Logical Cylinder Address)

This parameter is used to specify the logical cylinder address of ID area (16 bits: the high-order 8 bits for LCAH and the low-order 8 bits for LCAL) of a sector that the HDC will access. If LCA given by the command parameter does not match LCA read from ID area, the HDC will not access the sector. In soft sector format, it is prohibited to specify \$F8 to the high-order 8 bits (LCAH).

#### (3) LHA (Logicai Head Address)

LHA is used to specify the logical head address of ID area of a sector that the HDC will access. If LHA given by the command parameter does not match the LHA read from ID area, the HDC will not access that sector. In multiple track operation, LHA is automatically incremented by one. Since LHA is logical, it may exceed the number specified by the parameter NH (number of heads).

#### (4) LSA (Logical Sector Address)

LSA is used to specify the logical sector address of ID area that the HDC will access. If LSA given by the command parameter does not match LSA read from ID area, the HDC will not access the sector. In multiple sector operation, LSA is automatically incremented by one. Since LSA is compared with the control register NS (number of sectors) for switching of heads, the LSA must not exceed the NS.

# (5) NCA (Next Cylinder Address)

This parameter is used to specify the physical address (10 bits) of a cylinder to which the head will move when a SEK command is issued. The outermost cylinder address is \$0000. The high-order 8 bits of NCA are used for NCAH and the low-order 8 bits for NCAL. The high-order 6 bits of NCAH must be fixed to "0". If NCA exceeds NC, com-

mand execution abnormally terminates.

#### (6) OFFSET

OFFSET specifies how many sectors to be skipped reading after an index pulse. Then the HDC reads ID fields, and stores them into the data buffer.

# (7) PHA (Physical Head Address)

The MPU specifies PHA when issuing a disk access command. Unlike LHA, PHA is physical, and the bit status of PHA is directly output as HSEL signals. The high-order 5 bits of PHA must be fixed to "0" for ST506 interface, and the high-order 3 bits for SMD interface. In multiple track operation, PHA is automatically incremented by one within the HDC if another head switching is required. If PHA exceeds the value given by NH, the command execution will abnormally terminate.

### (8) POFF (Pointer Offset)

The MPU specifies a transfer start address (16 bits) when issuing a command for accessing the data buffer. The MSB of the high-order 8 bits (POFFH) selects one of two data buffers, and the remaining 7 bits must be fixed to "0". The low-order 8 bits (POFFL) specifies a transfer start address of the selected data buffer (256 bytes). For the 16-bit data bus, POFF is limited to an even address only.

#### (9) PSA (Physical Sector Address)

This parameter is used to specify a physical address of a hard sector at which the execution of RID, RIS, FID, WFM, or WFS starts. If PSA is \$00, the sector following an index pulse is specified.

#### (10) SCNT (Sector Count)

This parameter is used to specify the number of sectors (16 bits) that the HDC will continuously access in a disk access command execution. Upper 8 bits are SCNTH, and lower 8 bits are SCNTL. Up to 1024 sectors are specified in ST506 interface (128 sectors x 8 heads), and up to 8160 sectors are specifiable in SMD interface (255 sectors x 32 heads). For commands relating to the ID (RID and WFM), they perform no multiple track operation. In addition, maximum number of sectors that can be formatted at a time by WFM command is 128 for soft sector, and 102 for hard sector.

#### (11) US (Unit Select)

The MPU specifies the address (8 bits) of a target drive when issuing a head positioning, disk access or drive check command. The contents of US are directly output from USEL signals. The high-order 6 bits of US must be fixed to "0" for ST506 interface, and the high-order 5 bits for SMD interface. US is the high-order 8 bits of a 16-bit word, and the low-order 8 bits of the word are PHA or \$00. It is not necessary to issue \$00 to the low-order 8 bits when CKV or RCLB command is issued.

#### RESULT PARAMETERS

Result parameters are listed in Table 9. In this table, result parameters used by the HDC to control ST506 type hard disk drive are found in the upper row of each command, and those for SMD type in the lower row.

Table 9 Result Parameters (Byte-organized)

| Command                                 | Parameter (Upper row: ST506) Lower row: SMD                                                              |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------|

| Recalibrate                             | \$00 SSB US VUL<br>\$00 SSB US VUL                                                                       |

| Specify                                 | (\$00 SSB)<br>(\$00 SSB)                                                                                 |

| Seek                                    | \$00 SSB US VUL<br>\$00 SSB US VUL                                                                       |

| Read Data                               | \$00 SSB US PHA LCAH LCAL LHA LSA SCNTH SCNTL<br>\$00 SSB US PHA \$00 FLAG LCAH LCAL LHA LSA SCNTH SCNTL |

| Read Erroneous Data                     | \$00 SSB US PHA SCNTH SCNTL<br>\$00 SSB US PHA \$00 PSA SCNTH SCNTL                                      |

| Read ID<br>Read ID Skew (Note 1)        | \$00 SSB US PHA \$00 SCNTL<br>\$00 SSB US PHA \$00 PSA \$00 SCNTL                                        |

| Find ID                                 | \$00 SSB US PHA \$00 SCNTL<br>\$00 SSB US PHA \$00 PSA \$00 SCNTL                                        |

| Check Data                              | \$00 SSB US PHA LCAH LCAL LHA LSA SCNTH SCNTL<br>\$00 SSB US PHA \$00 FLAG LCAH LCAL LHA LSA SCNTH SCNTL |

| Compare Data                            | \$00 SSB US PHA LCAL LHA LSA SCNTH SCNTL SOO SSB US PHA \$00 FLAG LCAH LCAL LHA LSA SCNTH SCNTL          |

| Write Data                              | \$00 SSB US PHA LCAH LCAL LHA LSA SCNTH SCNTL<br>\$00 SSB US PHA \$00 FLAG LCAH LCAL LHA LSA SCNTH SCNTL |

| Write Format Write Format Skew (Note 1) | \$00 SSB US PHA SCNTH SCNTL<br>\$00 SSB US PHA \$00 PSA SCNTH SCNTL                                      |

| Memory to Buffer                        | (\$00 SSB)<br>(\$00 SSB)                                                                                 |

| Buffer to Memory                        | (\$00 SSB)<br>(\$00 SSB)                                                                                 |

| Open Buffer Read                        | (\$00 SSB)<br>(\$00 SSB)                                                                                 |

| Open Buffer Write                       | (\$00 SSB)<br>(\$00 SSB)                                                                                 |

| Polling                                 | \$00 SSB US VUL<br>\$00 SSB US VUL                                                                       |

| Check Drive                             | \$00 SSB US \$00 DST0 \$00<br>\$00 SSB US \$00 DST0 DST1 DST2 DST3                                       |

| Abort                                   | \$00 SSB<br>\$00 SSB                                                                                     |

| Check ECC                               | \$00 SSB EA0 EA1 EP0 EP1 EP2 \$00<br>\$00 SSB EA0 EA1 EP0 EP1 EP2 \$00                                   |

| Test                                    | (\$00 SSB)<br>(\$00 SSB)                                                                                 |

| Polling Disable                         | (\$00 SSB US VUL)<br>(\$00 SSB US VUL)                                                                   |

| Recall                                  | (\$00 SSB US VUL)<br>(\$00 SSB US VUL)                                                                   |

(Note 1) Read ID Skew and Write Format Skew are valid only for SMD. (Note 2) Parenthesized parameters are reported when a command is issued under the illegal condition.

#### **DST (Drive Status)**

Table 10 Drive List (DST)

| В      | lit  | 7     | 6   | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|------|-------|-----|-------|-------|-------|-------|-------|-------|

| \$T506 | DST0 | READY | SCP | TRK0  | 0     | WFLT  | 0     | 0     | 0     |

|        | DST0 | *     | *   | *     | WPRT  | FLT   | SKERR | OCYL  | URDY  |

|        | DST1 |       | *   | SELER | WERR3 | WERR2 | WERR1 | SERR2 | SERR1 |

| SMD    | DST2 | *     | *   | SAD32 | SAD16 | SAD8  | SAD 4 | SAD 2 | SAD 1 |

|        | DST3 | ) •   | *   | DTP32 | DTP16 | DTP8  | DTP4  | DTP2  | DTP1  |

<sup>\*:</sup> Depends on the state of BUS, /BUS, - BUS, /BUS,

Each bit of DST indicates drive interface input signal level. DSTO (1 byte) is reported in ST506 interface, and DST0-3 (4 bytes) are reported in SMD interface.

In ST506 interface, the WFLT bit in DST0 indicates the signal level of WFLT pin. Even if WFLT signal is momentarily asserted, the internal latch memorizes this and reflects its state on WFLT bit. When WFLT signal is negated, the latch read operation by the HDC clears this latch.

In SMD interface, the HDC reads 8 bits by 4 words of the drive status signal which is selected by signals TAG2 and TAG5.

| TAG2 | TAG5 | Status |

|------|------|--------|

| 0    | 0    | DST0   |

| 0    | 1    | DST1   |

| 1    | 0    | DST2   |

| 1    | 1    | DST3   |

Following (1) through (5) are read during CKV command execution and checked during disk access command execution. DST1 through DST3 are referred to during CKV command execution.

Status that each bit in DST1-3 indicates may vary according to the drive connected to the HDC. Following descriptions indicate DST bit function when the HDC is connected to a Hitachi 8" disk drive, DK-812S.

- (1) URDY (Unit Ready)

- This bit indicates that a selected drive is in ready state.

- (2) OCYL (On Cylinder)

- This bit indicates that a head is positioned correctly on a track.

- (3) SKERR (Seek Error)