# **Graphic Memory Interface Controller** (GMIC)

# Description

The HD63485 LSI belongs to the ACRTC (advanced CRT controller) family. It provides memory access control to frame buffers for graphic display and drawing. Incorporating bus driver circuits and a DRAM (dynamic RAM) interface, the GMIC allows direct connection to DRAM with no external circuits. Its main function include address data latch, DRAM row and column address multiplexing, supplying RAS, CAS, OE, WE, and other signals, and generating the 2CLK signal for the ACRTC. Using the Hi-BiCMOS process, the HD63485 achieves high speed memory access with low power dissipation.

#### **Features**

- Drives frame buffer memory directly (I<sub>OL</sub> = 24 mA max)

- Generates <u>DRAM</u> signal: row and column addresses, <u>RAS</u>. <u>CAS</u>, <u>OE</u>, <u>WE</u>, etc

- High-speed dot rate input (64 MHz max)

- Direct ACRTC interface

- Generates horizontal scrolling control signals

- Generates load signals for horizontal smooth scrolling

- Programmable address incerment mode

- Generates 2CLK signal

- TTL-compatible input output

- Single + 5 V power supply

- Low power dissipation

# Type of Products

| Part No.    | Speed | Package                   |

|-------------|-------|---------------------------|

| HD63485PS32 | 32MHz | 64-pin Plastic Shrink DIP |

| HD63485PS48 | 48MHz | (DP-64S)                  |

| HD63485PS64 | 64MHz | _                         |

| HD63485CP32 | 32MHz | 68-pin PLCC               |

| HD63485CP48 | 48MHz | (CP-68)                   |

| HD63485CP64 | 64MHz | _                         |

# Pin Description

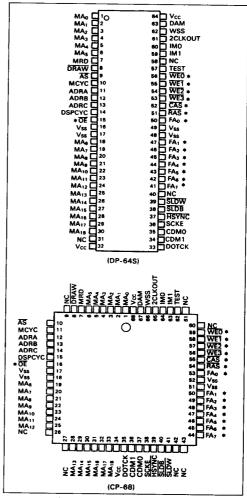

Figure 1 shows the pin arrangement for the 64-pin shrink-type DIP and the 68-pin PLCC packages. Pins marked with \*are bus drivers, which can handle a maximum output current  $I_{\rm OL}$  of 24mA. Table 1 describes the pins.

Figure 1. Pin Arrangement

# Power Supply (Vss, Vcc)

$V_{\text{SS}}$  and  $V_{\text{CC}}$  are the GMIC power supply pins.  $V_{\text{CC}}$  pins are +5 V  $\pm 5$  % supply pins.  $V_{\text{SS}}$  are the ground

pins. Be sure to connect all four  $V_{\text{SS}}$  pins to ground and both  $V_{\text{CC}}$  pins to the power supply.

Table 1. Pin Description

|                 | Pin Nu          | ımber                   |     |                       |

|-----------------|-----------------|-------------------------|-----|-----------------------|

| Signal          | DIP-64          | PLCC-68                 | 1/0 | Description           |

| Vcc             | 32,64           | 34,68                   |     | +5 V power supply     |

| V <sub>SS</sub> | 16,17,<br>48,49 | 17,18,<br>51,52         |     | Ground                |

| CDM1,<br>CDM0   | 34<br>35        | 36<br>37                | 1   | Clock division ratio  |

| DAM             | 63              | 67                      | 1   | Dual access mode      |

| IM1,<br>IMO     | 59<br>60        | 63<br>64                | I   | Increment mode        |

| wss             | 62              | 66                      | ı   | Window smooth scroll  |

| DOTCK           | 33              | 35                      | 1   | Dot clock             |

| TEST            | 57              | 62                      | 1   | Test                  |

| 2CLKOUT         | 61              | 65                      | 0   | Clock                 |

| MCYC            | 10              | 11                      | 1   | Memory cycle          |

| DRAW            | 8               | 8                       | 1   | Draw                  |

| MRD             | 7               | 7                       | 1   | Memory read           |

| AS              | 9               | 10                      | ı   | Address strobe        |

| MA18-<br>MA0    | 30-18,<br>6-1   | 33-28,<br>25-19,<br>6-1 | t   | Memory address bus    |

| HSYNC           | 37              | 39                      | I   | Horizontal sync       |

| RAS             | 51              | 54                      | 0   | Row address strobe    |

| CAS             | 52              | 55                      | 0   | Column address strobe |

| WE-3-WEO        | 53-56           | 56-59                   | 0   | Write enable          |

| ŌĒ              | 15              | 16                      | 0   | Output enable         |

| FA7-FA0         | 41-47,<br>50    | 44-50,<br>53            | 0   | Frame buffer address  |

| ADRA-<br>ADRC   | 11-13           | 12-14                   | 0   | Address               |

| DSPCYC          | 14              | 15                      | 0   | Display cycle         |

| SCKE            | 36              | 38                      | 0   | Shift clock enable    |

| SLDB,<br>SLDW   | 38, 39          | 40, 41                  | 0   | Shift load signals    |

#### **Program Pins**

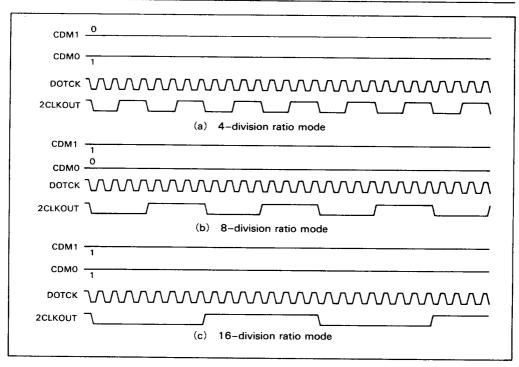

**Clock Division Ratio** (**CDM1**, **CDM0**): The CDM1 and CDM0 inputs determine the division ratio used to generate 2CLKOUT for the ACRTC from the DOTCK input. See table 2.

**Dual Access Mode** (**DAM**): The DAM input sets the access mode as shown in table 3.

Increment Mode (IM 1, IM 0): The IM 1 and IM 0 inputs determine the addresses sent from memory addresses (MA 18-MA 0) as the frame buffer output (FA 7-FA 0) to accommodate different DRAM types. Table 4 shows the memory address outputs corresponding to the IM 1 and IM 0 settings. Note that the frame buffer addresses (FA 7-FA 0) have multiplexed memory address outputs.

IM inputs are closely related to the graphic address increment (GAI) of the ACRTC (see ACRTC user's manual).

Window Smooth Scroll (WSS): When the WSS input is low (0), each base screen can be scrolled in single access mode, dual access mode 0, and dual access mode 1. The  $\overline{\text{SLDB}}$  signal contains the

scrolling data.

When the WSS input is high (1), the window screen can be smooth scrolled in dual access mode 1. The  $\overline{\text{SLDW}}$  signal contains the scrolling data.

# Operation Control Signals

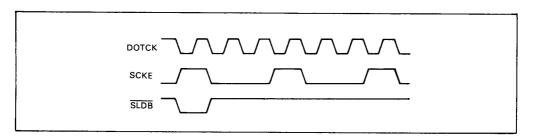

**Dot Clock** (**DOTCK**): The DOTCK input must be the same clock that is supplied to the shift register for video signal generation. Dot clock frequency is determined by the horizontal display resolution (pixel count) and the display period of one horizontal scan.

**Test** (**TEST**): The TEST input is used for manufacturing operational testing. It must be fixed low when the GMIC is mounted in a system.

#### **ACRTC Interface Signals**

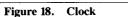

Clock (2CLK): The 2CLKOUT clock output is a basic clock for the ACRTC's internal operation. The GMIC generates 2CLKOUT by dividing the high-speed dot clock by the ratio determined by the CDM 1 and CDM 0 inputs.

Table 2. Clock Division Ratio

| CDM 1 | CDM 0 | Division Ratio |

|-------|-------|----------------|

| 0     | 0     | Not allowed    |

| 0     | 1     | Divide by 4    |

| 1     | 0     | Divide by 8    |

| 1     | 1     | Divide by 16   |

Table 3. Access Modes

| DAM | Access Mode        |  |

|-----|--------------------|--|

| 0   | Single access mode |  |

| 1   | Dual access mode   |  |

Table 4. Increment Mode

| IM 1 | IM O | Increment<br>Mode | Address Output to FA 7-FA 0                                            | Address Output to<br>ADRC-ADRA                         |

|------|------|-------------------|------------------------------------------------------------------------|--------------------------------------------------------|

| 0    | 0    | +1                | MA <sub>15</sub> -MA <sub>8</sub> , MA <sub>7</sub> -MA <sub>0</sub>   | MA <sub>18</sub> , MA <sub>17</sub> , MA <sub>16</sub> |

| 0    | 1    | +2                | MA <sub>16</sub> -MA <sub>9</sub> , MA <sub>8</sub> -MA <sub>1</sub>   | MA <sub>0</sub> , MA <sub>17</sub> , MA <sub>18</sub>  |

| 1    | 0    | +4                | MA <sub>17</sub> -MA <sub>10</sub> , MA <sub>9</sub> -MA <sub>2</sub>  | MA <sub>0</sub> , MA <sub>1</sub> , MA <sub>18</sub>   |

| 1    | 1    | +8                | MA <sub>18</sub> -MA <sub>11</sub> , MA <sub>10</sub> -MA <sub>3</sub> | MA <sub>0</sub> , MA <sub>1</sub> , MA <sub>2</sub>    |

|      |      |                   |                                                                        |                                                        |

**Memory Cycle (MCYC):** The MCYC input indicates the ACRTC's frame buffer access timing. MCYC is low when the ACRTC is in the address cycle, and high when the ACRTC is in the data cycle.

**Draw** (DRAW): The DRAW input indicates whether the ACRTC memory cycle is a drawing cycle. DRAW is low during drawing cycle, and high otherwise. The GMIC uses DRAW to recognize display cycles, and also to generate DRAM control signals (WE 3-WE 0).

Memory Read (MRD): The MRD input controls data transfer between frame buffers and the ACRTC. The ACRTC pulls MRD high when it reads data from the frame buffer, and low when it writes data.

The only exception is when the ACRTC is in superimpose display mode (dual access mode 1). In superimpose display mode, the ACRTC inputs a low level and reads data from a frame buffer in order to indicate that the display cycle is for a superimposed screen (window screen).

Address Storbe  $(\overline{AS})$ : The  $\overline{AS}$  input is a latch timing signal for the memory address sent from the ACRTC. Additionally,  $\overline{AS}$  indicates whether memory is begin accessed. For example, for horizontal zooming, the  $\overline{SLDB}$  signal is provided at a lower frequency, corresponding to the lower frequency of  $\overline{AS}$ .

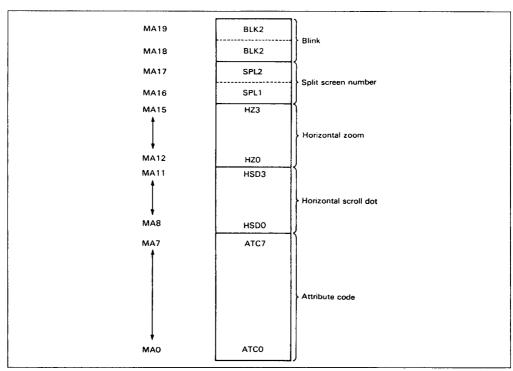

**Memory Address Bus** ( $MA_{18}$ - $MA_{0}$ ): The  $MA_{18}$ - $MA_{0}$  inputs are address signals for frame buffer access, provided by the ACRTC.

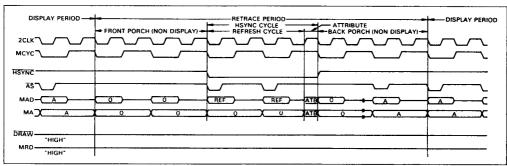

Horizontal Sync (HSYNC): The HSYNC input is a DRAM refresh cycle control signal to horizontally synchronize CRT displays. The GMIC performs RAS only refresh when HSYNC is low and DRAW is high when AS pulses are input.

Setting HSYNC low informs the GMIC of the end of a raster display. Usually, the ACRTC's HSYNC output supplies this input.

#### Frame Buffer Access Signals

Row Address Strobe  $(\overline{RAS})\colon$  The GMIC outputs the DRAMs'  $\overline{RAS}$  timing signal on the  $\overline{RAS}$  output.

Write Enable ( $\overline{WE3}$ - $\overline{WE0}$ ): The GMIC outputs the DRAM's  $\overline{WE}$  timing signals on the  $\overline{WE}$  outputs. Since  $\overline{WE3}$ - $\overline{WE0}$  are controlled by the incerment mode (IM 1, IM 0) and by the lower two bits of the

address (MA 1, MA 0), the GMIC can directly control up to four memory banks. Up to eight memory banks can be controlled by externally decoding the address (ADRC) and  $\overline{WE\ 3}.\overline{WE\ 0}.$

$\overline{WE~0}$  are bus driver that can handle a maximum output current  $I_{01}$  of 24 mA.

Output Enable  $(\overline{OE})$ : The GMIC outputs the DRAMs' output timing signal on the  $\overline{OE}$  output.  $\overline{OE}$  is a bus driver that can handle a maximum output current  $I_{OL}$  of 24 mA.

Frame Buffer Address (FA 7-FA 0): The GMIC outputs the multiplexed DRAM address on FA 7-FA 0. How the address is multiplexed depends on the incerment mode (table 4). FA 7-FA 0 are bus drivers that can handle a maximum output current  $I_{01}$  of 24 mA.

**Address** (**ADRA-ADRC**): The GMIC latches three address bits other than those delivered on the FA 7-FA 0 bits and outputs them on ADRA-ADRC in one memory cycle.

## **GVAC** Control Signals

Shift Clock Enable (SCKE): The SCKE output controls the GVACs' video signal generation shift register. It outputs a control signal for zooming according to the horizontal zoom signal (attribute control signal) from the ACRTC. The GVAC performs horizontal zoom by halting the clock when SCKE is low.

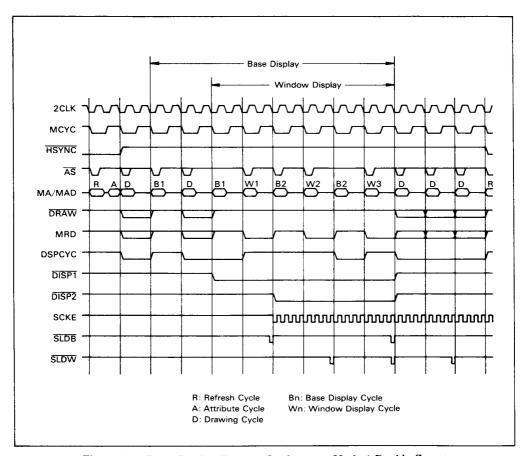

Shift Load Signals (SLDB, SLDW): The SLDB and SLDW outputs are load signals for the display data of the video signal generation shift register. The SLDB output is used for single access mode. dual access mode 0, and dual access mode 1. The SLDW output controls the window screen in dual access mode 1.

**Display Cycle** (**DSPCYC**): The DSPCYC output indicates whether a memory cycle is a display cycle.

DSPCYC is high during display cycle, and low otherwise.

| AS    | DRAW | MRD | cycle mode            | memory cycle | DSPCYC |

|-------|------|-----|-----------------------|--------------|--------|

|       | L    | L   | Drawing Write         | Memory Write | L      |

| 1.    | L    | Н   | Drawing Read          | Memory Read  | L      |

| Low   | Н    | L   | Window Screen Display | Memory Read  | Н      |

| pulse | Н    | Н   | Backscreen Display    | Memory Read  | Н      |

| Н     | x    | x   | _                     | No Access    | L      |

**OHITACHI**

# **Functional Description**

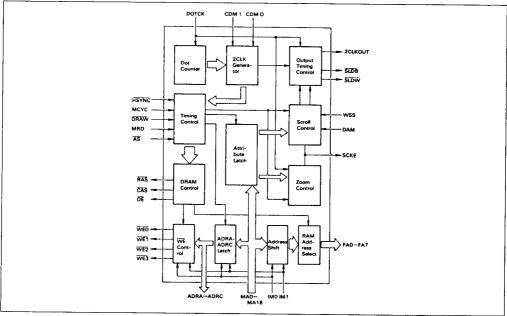

Figure 2 is a block diagram of the HD63485.

Figure 2. GMIC Block Diagram

#### 2CLK Generator

The 2CLK generator generates 2CLKOUT for the ACRTC and itself by dividing the external DOTCK signal. The ratio of DOTCK to 2CLKOUT is set externally by the CDM 1 and CDM 0 inputs.

#### Attribute Latch

The attribute latch temporarily stores the attribute codes input from the ACRTC on MA 18-MA 0 used for horizontal zoom (HZ 3-HZ 0) and horizontal scroll dot (HSD 3-HSD 0).

#### Zoom Control

Zoom control generates the SCKE signal from DOTCK to control the GVAC clock for horizontal display zooming.

#### Scroll Control

264

Scroll control generates shift load signals ( $\overline{SLDB}$ ,  $\overline{SLDW}$ ) which control video signal generation for the GVAC.

# Address Shifter

The address shifter stores memory addresses (MA 18-MA 0) sent from the ACRTC. It supplies them to the RAM address section according to the timesharing mode selected by the graphic increment mode (IM 1, IM0).

#### ADRA-ADRC Latches

The ADRA-ADRC latches store the lower or upper address bits which are not supplied to FA 7-FA 0 from the memory address sent from the ACRTC. It outputs them for the whole memory cycle.

#### RAM Address Selection

The RAM address selection circuits output the timeshared row and column addresses to the frame buffers according to the  $\overline{RAS}$  and  $\overline{CAS}$  timing.

# DRAM Control and WE Control

The DRAM and  $\overline{WE}$  control circuits generate  $\overline{RAS}$ .  $\overline{CAS}$ ,  $\overline{OE}$ , and  $\overline{WE}$  signals for frame buffer access from the ACRTC output signals.

**OHITACHI**

# System Description

#### Applications

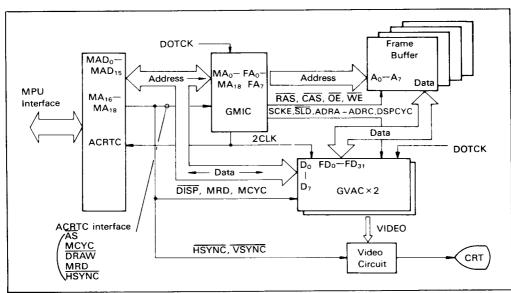

The GMIC provides communications between the ACRTC and frame buffers. It contains control circuits for generating signals necessary for the ACRTC to access a frame buffer. In addition it generates basic signals for operating the ACRTC and control signals for the GVAC (graphic video attribute controller), which generates the video signals for a CRT display.

The GMIC's operation mode can be controlled by it program pins. This makes the GMIC suitable for a wide range of operations, from small, low-speed systems to large, high-speed systems, and it allows it to flexibly change to suit system specification changes.

Figure 3 shows a graphic system configuration using an ACRTC, GMIC, and GVACs. Using a GMIC for interface to the frame buffers and a GAVCs for CRT video signal generation creates a flexible, high-performance graphic system with a minimum component count.

#### System Configuration

The typical graphic system application for the GMIC and GVAC shown in figure 3 uses two GVACs, but the number of GVACs used can be changed to accommodate CRT resolution and colorigrey scale per pixels for various applications.

The GMIC receives memory addresses (MAD<sub>15</sub>- $MAD_0$ ,  $MA_{18}$ - $MA_{16}$ ), address strobe ( $\overline{AS}$ ), memory cycle (MCYC), draw (DRAW), memory read (MRD), and other ACRTC outputs, and generates control signals for the frame buffers. The frame buffers are generally constructed from DRAM. since graphic systems require large memory capacity frame buffers. The GMIC therefore uses a DRAM-compatible multiplexing system. Through this multiplexing, the GMIC delivers address outputs and control signals such as RAS, CAS, WE. and  $\overline{OE}$ , acting as a direct interface between the ACRTC and the frame buffers. Furthermore, the GMIC generates a basic clock signal for the ACRTC (2CLK) by dividing the high-speed dot clock. It also generates control signals for the GVAC.

Figure 3. System Application Example

# Operation

#### Basic Clock

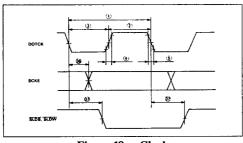

Timing for signals to and from the GMIC is based on the dot clock (DOTCK) supplied to the GMIC and the clock output (2CLKOUT) generated by the GMIC. 2CLKOUT is generated by dividing the DOTCK input by the ratio selected by the CDM 1 and CDM 0 inputs. Figure 4 shows the relation between DOTCK and 2CLKOUT. The frequency of DOTCK depends on the speed and resolution of the CRT display. DOTCK (in MHz) equals the horizontal resolution (pixels/raster line) by the horizontal display raster scan period ( $\mu$ s per raster).

$f_{DOTCh} = [Horizontal resolution (pixels/raster)]/$ [Horizontal display period( $\mu$ s)] (MHz)

The dot clock dividing mode should be chosen considering the frame buffer cycle time and the speed of the ACRTC used. For high-speed drawing, a smaller division ratio should be used to supply a

higher frequency chock to the ACRTC. For applications using low-speed frame buffers and external circuits, larger division rations should be selected to supply a lower frequency clock to the ACRTC.

Note: The maximum DOTCK frequency is sometimes limited by the DOTCK division ratio. If the division ratio is 8 or 16, the maximum frequency is allowed, but if a division ratio of 4 is used, the DOTCK frequency is limited to 32 MHz.

#### Frame Buffer Control

The GMIC is designed for use with DRAM frame buffer memories. Therefore, the GMIC generates DRAM access signals  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ , and  $\overline{OE}$ . Also, it outputs row and column addresses to the RAM, timeshared according to  $\overline{RAS}$  and  $\overline{CAS}$ .

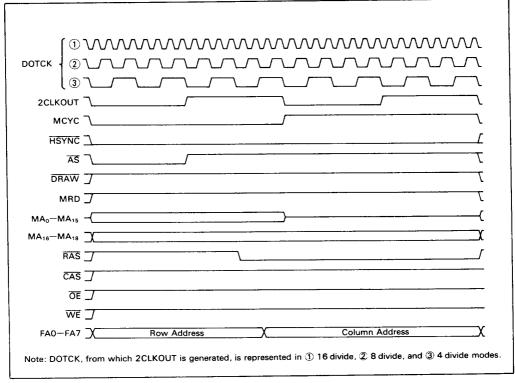

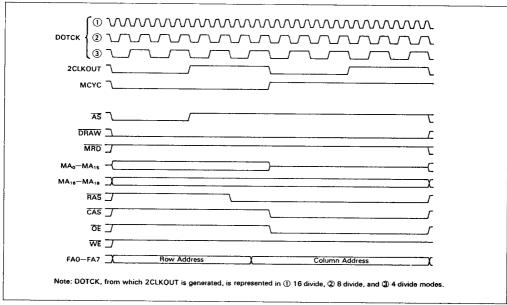

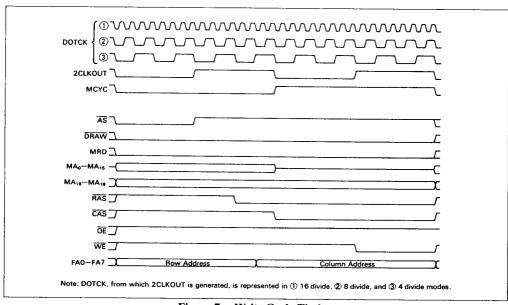

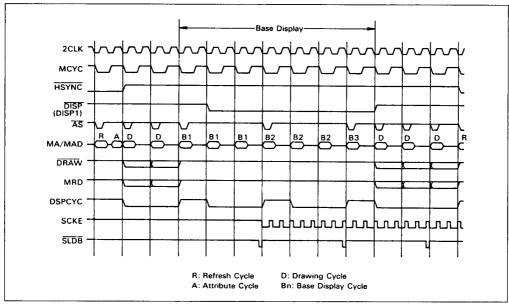

Table 5 shows the GMIC frame buffer access modes. The memory cycles are roughly divided into six types. They are distinguished by the ACRTC's

Figure 4. DOTCK Division

**OHITACHI**

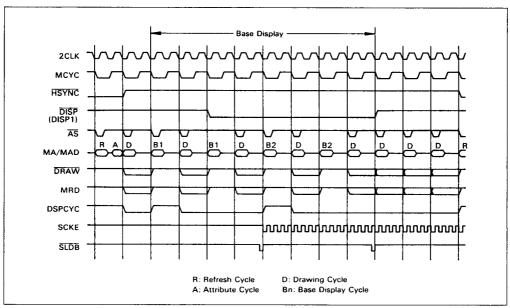

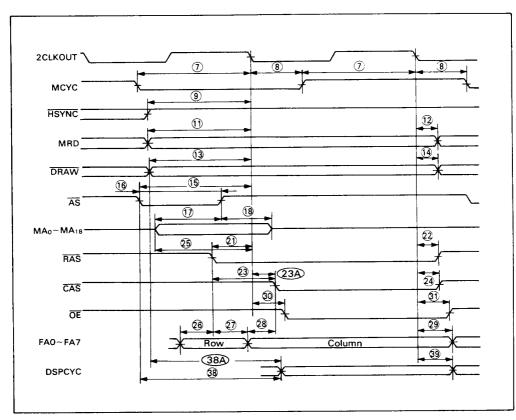

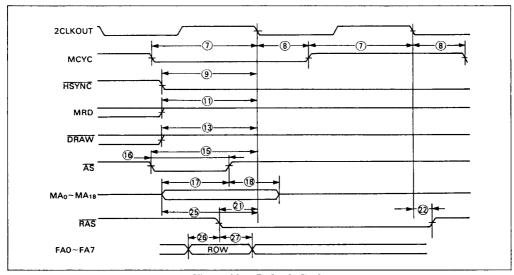

output signals (AS, HSYNC, DRAW, MRD). Figure 5 shows RAS only refresh cycle timing.

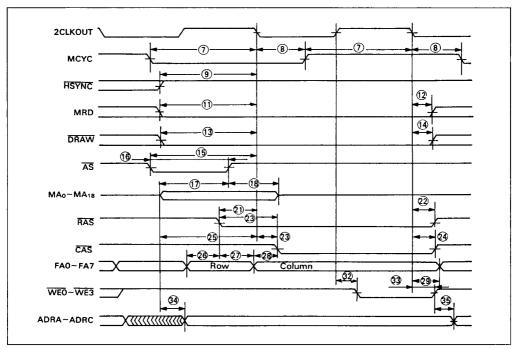

Figure 6 and 7 show read and write cycle timing, respectively.

Table 5. Memory Cycles

| AS    | HSYNC | DRAW | MRD  | Cycle Mode                | Memory Cycle     |

|-------|-------|------|------|---------------------------|------------------|

| Low   | Low   | High | High | Refresh cycle             | RAS only refresh |

| pulse |       | Low  | Low  | Drawing write cycle       | Memory write     |

|       |       | Low  | High | Drawing read cycle        | Memory read      |

|       | High  | High | Low  | Window screen cycle       | Memory read      |

|       | ŭ     | High | High | Background screen display | Memory read      |

| High  |       | High | High |                           | No access        |

Note: The GMIC performs a frame buffer refresh during a horizontal sync period (HSYNC=low), with DRAW high and AS pulse applied. During a refresh cycle, only RAS is output. CAS and OE are not output.

Figure 5. RAS Only Refresh Timing

Figure 6. Read Cycle Timing

Figure 7. Write Cycle Timing

Table 6 shows the relation between frame buffer addresses (FA7-FA0) and memory address (MA $_{\rm 18}$ - MA $_{\rm 0}$ ), as determined by the increment mode (IM1, IM0). FA pins provide multiplexed addresses for DRAM, and the remaining address bits are output at ADRA-ADRC. The GMIC has four increment modes:  $+1,\,+2,\,+4,$  and +8. This mode should be set the same as the ACRTC's GAI (graphic address increment) mode. GAI mode is a bit set according to the frame buffer, which sets the increment mode for display address output for a graphic address.

Graphic drawing data is processed on a single word (16 bit) basis. The ACRTC sets the bit count per pixel by the graphic bit mode (GBM) in its command control register, which is more suitable for multicolor/grey scale systems. However, if one word is definitely read from a frame buffer during each display cycle, four pixels per word can be displayed when GBM is set to 4 bits per pixel. To

implement a CRT display having a 1 bit per pixel resolution '16 pixels/word), an input clock four times faster must be supplied to the ACRTC. For more multicolor/grey scale systems, an ever faster clock is required.

On the other hand, if several words are read from a frame buffer during each display cycle, and the CRT can have a higher resolution without speeding up the ACRTC input clock. For example, in the +4 increment mode, when GBM is set to 4 bits pixel, 4 words (64 bits) containing 16 pixels can be read in one display cycle.

For one word  $^{\circ}16$  bits, read during one display cycle, the GAI must be set to 000.

When 32 64/128 bits are required during one display cycle for a high-resolution or multicolor grey scale system, GAI must be set to 001/010/011

Table 6. Frame Buffer and Memory Addresses

|               | +1 Mode |      | +2 Mode |      | + 4 Mode |      | +8 Mode |            |

|---------------|---------|------|---------|------|----------|------|---------|------------|

| Frame Address | Row     | Col  | Row     | Col  | Row      | Col  | Row     | Col        |

| FAO           | MAO     | MA8  | MA1     | MA9  | MA2      | MA10 | MA3     | MA11       |

| FA1           | MA1     | MA9  | MA2     | MA10 | MA3      | MA11 | MA4     | MA12       |

| FA2           | MA2     | MA10 | MA3     | MA11 | MA4      | MA12 | MA5     | MA13       |

| FA3           | MA3     | MA11 | MA4     | MA12 | MA5      | MA13 | MA6     | MA14       |

| FA4           | MA4     | MA12 | MA5     | MA13 | MA6      | MA14 | MA7     | MA15       |

| FA5           | MA5     | MA13 | MA6     | MA14 | MA7      | MA15 | MA8     | MA16       |

| FA6           | MA6     | MA14 | MA7     | MA15 | MA8      | MA16 | MA9     | MA17       |

| FA7           | MA7     | MA15 | MA8     | MA16 | MA9      | MA17 | MA10    | MA18       |

| ADRA          | M       | A16  | N       | /AO  | ١        | /AO  | M       | <b>A</b> 0 |

| ADRB          | N       | IA17 | N       | IA17 |          | /A1  | M       | A1         |

| ADRC          | N       | IA18 | N       | MA18 |          | IA18 | MA2     |            |

Table 7. WE Output Timing

| Increment |      | Input |     |     |     |     |     |     | Output |     |  |  |

|-----------|------|-------|-----|-----|-----|-----|-----|-----|--------|-----|--|--|

| Mode      | DRAW | MRD   | MA1 | MAO | IM1 | IMO | WE3 | WE2 | WE1    | WEO |  |  |

|           | Н    | ×     | x   | х   | ×   | ×   | Н   | н   | н      | Н   |  |  |

|           | L    | Н     | ×   | x   | ×   | ×   | Н   | Н   | н      | н   |  |  |

| +1        | L    | L     | ×   | х   | 0   | 0   | L   | L   | L      | L   |  |  |

| +2        | L    | L     | x   | 0   | 0   | 1   | Н   | L   | Н      | L_  |  |  |

|           | L    | L     | X   | 1   | 0   | 1   | L   | Н   | L      | Н   |  |  |

| +4/+8     | L    | L     | 0   | 0   | 1   | ×   | Н   | Н   | Н      | L   |  |  |

|           | L    | L     | 0   | 1   | 1   | x   | Н   | Н   | L      | Н   |  |  |

|           | L    | L     | 1   | 0   | 1   | х   | Н   | L   | Н      | Н   |  |  |

|           | L    | L     | 1   | 1   | 1   | x   | L   | Н   | Н      | Н   |  |  |

(1) HITACHI

respectively.

270

Table 7 shows the output condition of the write enable signals WE3-WE0. The four write enable signals can directly control up to four memory banks. The WE output is determined by DRAW. MA0. IM1, and IM0.

# $\frac{\text{Video}}{\text{SLDW}}$ Shifter Shift Load Signals ( $\overline{\text{SLDB}}$ ,

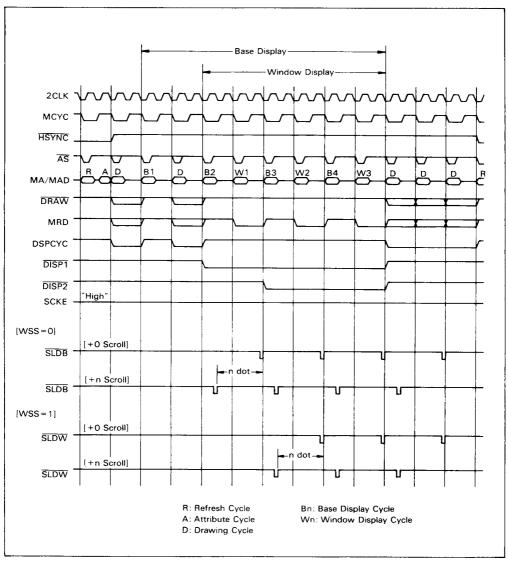

SLDB and SLDW load timing signals control the timing of display data input from a frame buffer to the video signal generation shift register (parallel-to-serial conversion circuit). SLDB is used for base screen in single access mode, dual access mode 0, and dual access mode 1. SLDW is used for window screens in dual access mode 1.

Relation of Access Mode and WSS to SLDB and SLDW: Table 8 shows the relationship between access modes, WSS, and SLDB and SLDW. When WSS=0 in single access or dual access mode 0, SLDB output timing can be varied according to the amount of scrolling for one display cycle. SLDW is not output.

When WSS=0 in dual access mode 1 for the bese screen,  $\overline{SLDB}$  output timing can be varied to accommodate smooth scrolling according to the horizontal scroll dot attribute control signals :HSD3-HSD0: supplied by the ACRTC. The

SLDW signal is asserted for one period of the last dot clock during a display cycle. Its output cannot be varied for scrolling.

When WSS=1, for the window in dual access mode 1. SLDB signal is asserted and fixed for one period of the last dot clock of one display cycle, where as SLDW timing can be varied according to scrolling amount in one display cycle.

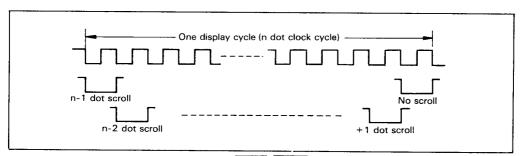

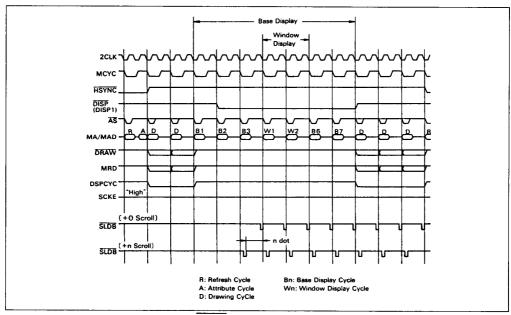

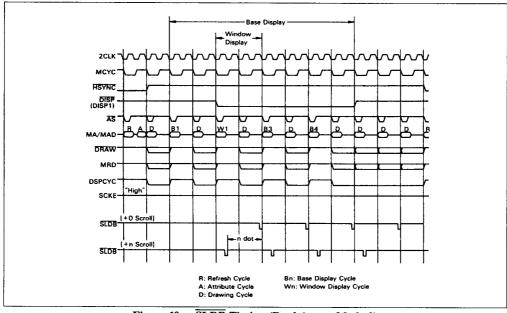

Amount of Scrolling and Output Timing: Figure 8 shows the output timing of the shift load signals (SLDB, SLDW) for different amounts of scrolling. With increased scrolling, the load signal is output earlier by one dot clock.

Figure 9, 10, and 11 show  $\overline{\text{SLDB}}$  and  $\overline{\text{SLDW}}$  timing for single access, dual access mode 0, and dual access mode 1, respectively. Figure 12, 13, and 14 show  $\overline{\text{SLDB}}$  timing for double and triple zooming.

Table 9 shows the attribute codes set for the ACRTC and the corresponding scrolling amounts. Table 10 shows the relationship between the GMIC dot clock division ratios and GVAC shift register lengths in corresponding access modes. Display colors are determined by the shift register length and amount of display data simultaneously read set in the ACRTC's GAI. The single and dual access modes are described in the ACRTC User's Manual, 3.2 CRT Interface.

Table 8. WSS, Access Mode, Shift Load Signals

| WSS | Access Mode                     | SLDB                          | SLDW                          |

|-----|---------------------------------|-------------------------------|-------------------------------|

| 0   | Single access,<br>Dual access 0 | Scrolling amount is permitted | No output                     |

|     | Dual access 1,<br>Base screen   | Scrolling amount is permitted | Scrolling impossible          |

| 1   | Dual access 1,<br>Base screen   | Scrolling impossible          | Scrolling amount is permitted |

Figure 8. Shift Load (SLDB, SLDW) Output Timing

**OHITACHI**

Table 9. ACRTC Attribute Codes and Scrolling Amounts

| Shift Bit<br>Length | HSD5 | HSD4 | HSD3 | HSD2 | HSD1 | HSDO | Scroll<br>Dot Count |

|---------------------|------|------|------|------|------|------|---------------------|

| 16 bits             | x    | ×    | 0    | 0    | 0    | 0    | 0                   |

|                     | ×    | ×    | 0    | 0    | 0    | 1    | 1                   |

|                     | X    | х    | 0    | 0    | 1    | 0    | 2                   |

|                     |      |      |      |      |      |      |                     |

|                     | x    | x    | 1    | 1    | 1    | 0    | 14                  |

|                     | ×    | ×    | 1    | 1    | 1    | 1    | 15                  |

| 32 bits             | x    | 0    | 0    | 0    | 0    | 0    | 0                   |

|                     | x    | 0    | 0    | 0    | 0    | 1    | 1                   |

|                     | ×    | 0    | 0    | 0    | 1    | 0    | 2                   |

|                     |      |      |      |      |      |      |                     |

|                     | x    | 1    | 1    | 1    | 1    | 0    | 30                  |

|                     | x    | 1    | 1    | 1    | 1    | 1    | 31                  |

| 64 bits             | 0    | 0    | 0    | 0    | 0    | 0    | 0                   |

|                     | 0    | 0    | 0    | 0    | 0    | 1    | 1                   |

|                     | 0    | 0    | 0    | 0    | 1    | 0    | 2                   |

|                     |      |      |      | :    |      |      |                     |

|                     | 1    | 1    | 1    | 1    | 1    | 0    | 62                  |

|                     | 1    | 1    | 1    | 1    | 1    | 1    | 63                  |

Note: The attribute code from the ACRTC supplies HSD3-HSD0, and memory address MA1 and MA0 supply HSD5 and HSD4. If these memory address bits are used (MA1 for 64-bit shifts, MA0 for 32-bit shifts), they must not be changed during one horizontal period.

Table 10. GMIC Division Ratio and GVAC Shift Lengths

| Division Ratio | Single Access | Dual Access         |

|----------------|---------------|---------------------|

| Divide by 4    | 8 dot shift   | 16 dot shift        |

| Divide by 8    | 16 dot shift  | 32 dot shift        |

| Divide by 16   | 32 dot shift  | 64 dot shift (note) |

Note: This mode cannot be used directly because the maximum shift register length is 32 dots.

Figure 9. SLDB Timing (Single Access Mode)

Figure 10. SLDB Timing (Dual Access Mode 0)

Figure 11. SLDB and SLDW Timing (Dual Access Mode 1)

Figure 12. Zoom Display Timing (Single Access Mode, Triple Zoom)

Figure 13. Zoom Display Timing (Dual Access Mode 0, Double Zoom)

Figure 14. Zoom Display Timing (Dual Access Mode 1, Double Zoom)

**Driving Priority Mode:** In the ACRTC drawing priority mode, drawing memory access takes priority over display memory access. In this mode, when display data is provided in the same manner as in the 32-bit shift mode but the system does not enter a display cycle, and a total output of 32 bits is completed, low-level output are provided until the next display cycle.

#### Shift Clock Enable (SCKE)

Shift clock enable (SCKE) is a control signal for the GVAC video signal generation shift register. GVAC drives the shift register on the falling edge of the dot clock. The SCKE control signal decreases the dot clock frequency to set the zoom scale. Figure 15 shows triple zoom (HZ=0011) timing. Table 11 shows attribute codes and corresponding zoom scales.

Table 11. Attribute Codes and Zoom Scales

| HZ3 | HZ2 | HZ1 | HZ0 | Zoom scale |

|-----|-----|-----|-----|------------|

| 0   | 0   | 0   | 0   | 1          |

| 0   | 0   | 0   | 1   | 2          |

| 0   | 0   | 1   | 0   | 3          |

| 0   | 0   | 1   | 1   | 4          |

| 0   | 1   | 0   | 0   | 5          |

| 0   | 1   | 0   | 1   | 6          |

| 0   | 1   | 1   | 0   | 7          |

| 0   | 1   | 1   | 1   | 8          |

| 1   | 0   | 0   | 0   | 9          |

| 1   | 0   | 0   | 1   | 10         |

| 1   | 0   | 1   | 0   | 11         |

| 1   | 0   | 1   | 1   | 12         |

| 1   | 1   | 0   | 0   | 13         |

| 1   | 1   | 0   | 1   | 14         |

| 1   | 1   | 1   | 0   | 15         |

| 1   | 1   | 1   | 1   | 16         |

Figure 15. Triple Zoom Timing

#### **Attribute Control Signals**

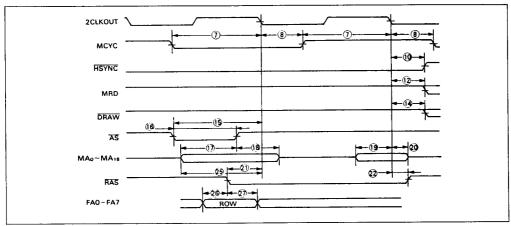

The GMIC receives attribute code control signals for horizontal zooming and horizontal smooth scrolling from the ACRTC. Figure 16 shows attribute control output timing, and figure 17 shows the corresponding output pins.

The GMIC can control horizontal smooth scrolling of up to a 63-dot shift. However, the ACRTC outputs a 4-bit code (HSD3-HSD0), directly supporting up to a 15-dot shift. Therefore, the GMIC latches the lower 2 bits of the display adddress (MA0, MA1) output every display cycle into its internal register in order to control a 63-dot shift

Figure 16. DRAM Refresh and Attribute Control Data Output (Single Access Mode)

Figure 17. Attribute Control Signal Output Pins

# Absolute Maximum Ratings (All voltages referenced to Vss = 0 V)

| Item                  | Symbol           | Rating                         | Unit |

|-----------------------|------------------|--------------------------------|------|

| Supply voltage        | Vcc              | - 0.3 to + 7.0                 | ٧    |

| Input voltage         | V <sub>in</sub>  | - 0.3 to V <sub>CC</sub> + 0.3 | ٧    |

| Output voltage        | $V_{out}$        | 5.5                            | ٧    |

| Operating temperature | Topr             | 0 to + 70                      | °C   |

| Storage temperature   | T <sub>str</sub> | - 55 to + 150                  | °C   |

Notes: Using an LSI beyond in maximum ratings may result in its permanent destruction. LSIs should usually be operated under the recommended operating conditions. Exceeding any of these conditions may adversely affect its reliability.

# Recommended Operating Conditions (All voltages referenced to $V_{SS} = 0 V$ )

| Item                  | Symbol          | Min  | Тур  | Max  | Unit |

|-----------------------|-----------------|------|------|------|------|

| Supply voltage        | Vcc             | 4.75 | 5.00 | 5.25 | ٧    |

| Input voltage low     | V <sub>IL</sub> | 0    | -    | 0.7  | ٧    |

| Input voltage high    | V <sub>IH</sub> | 2.2  |      | Vcc  | ٧    |

| Operating temperature | Topr            | 0    | 25   | 70   | °C   |

# **Electrical Characteristics**

# DC Characteristics ( $V_{CC} = 5.0 \text{ V} \pm 5\%$ , $V_{SS} = 0 \text{ V}$ , $T_a = 0\%$ to 70% unless otherwise noted)

| Item                   |                                                    | Symbol           | Min  | Max  | Unit                     | Test Condition                                        |

|------------------------|----------------------------------------------------|------------------|------|------|--------------------------|-------------------------------------------------------|

| Input voltage high     | 1                                                  | ViH              | 2.2  | Vcc  | ٧                        |                                                       |

| Input voltage low      |                                                    | V <sub>1L</sub>  | -0.3 | 0.7  | ٧                        |                                                       |

| Input clamp volta      | ge                                                 | Vi               |      | -1.5 | ٧                        | $V_{CC} = 4.75 \text{ V},$ $I_{in} = -18 \text{ mA}$  |

| Output voltage<br>high | ADRA-ADRC, SLDB,<br>SLDW, DSPCYC, SCKE,<br>2CLKOUT | V <sub>OH</sub>  | 2.7  |      | V                        | $V_{CC} = 4.75V,$ $I_{OH} = -400 \text{ mA}$          |

|                        | WE3-WEO. FA7-FA0,<br>RAS, CAS, OE                  | Vон              | 2.0  |      | ٧                        | $V_{CC} = 4.75 \text{ V},$ $I_{OH} = -15 \text{ mA}$  |

| Output voltage<br>low  | ADRA-ADRC, SLDB,<br>SLDW, DSPCYC, SCKE<br>2CLKOUT  | V <sub>OL</sub>  |      | 0.5  | V                        | $V_{CC} = 4.75 \text{ V},$ $I_{OL} = 8 \text{ mA}$    |

|                        | WE3-WEO, FA7-FA0,<br>RAS, CAS, OE                  | V <sub>OL</sub>  |      | 0.5  | ٧                        | $V_{CC} = 4.75 \text{ V},$ $I_{OL} = 24 \text{ mA}$   |

| Input current high     |                                                    | Ин               |      | 20   | μΑ                       | $V_{CC} = 5.25 \text{ V},$<br>$V_i = 2.7 \text{ V}$   |

| Input current low      |                                                    | 1 <sub>1</sub> L |      | -400 | μΑ                       | $V_{CC} = 5.25 \text{ V},$<br>$V_{I} = 0.4 \text{ V}$ |

| Output short circu     | it current                                         | los              | -40  | -120 | mA                       | $V_{CC} = 5.25 \text{ V}$                             |

| Current consumpt       | Icc                                                |                  | 160  | mA   | V <sub>CC</sub> = 5.25 V |                                                       |

| Input capacitance      |                                                    | Cin              |      | 10   | pF                       |                                                       |

AC Characteristics (VCC = 5.0 V  $\pm$  5%, VSS = 0 V,  $T_a$  = 0°C to + 70°C)

| No  | Item                         | Symbol             | 32 MHz               |            | 48 MHz               |     | 64 MHz               |     |      |             |

|-----|------------------------------|--------------------|----------------------|------------|----------------------|-----|----------------------|-----|------|-------------|

|     |                              |                    | Min                  | Max        | Min                  | Max | Min                  | Max | Unit | Figure      |

|     | DOTCK operation frequence    | f                  |                      | 32         |                      | 48  |                      | 64  | MHz  |             |

| 1   | DOTCK cycle time             | tc                 | 31.3                 |            | 20.8                 |     | 15.6                 |     | ns   | 18          |

| 2   | DOTCK high level pulse width | t <sub>HW</sub>    | 12                   |            | 9                    |     | 6                    |     | ns   | _           |

| 3   | DOTCK low level pulse width  | t <sub>L</sub> w   | 12                   |            | 9                    |     | 6                    |     | ns   | <del></del> |

| 4   | DOTCK rise time              | t <sub>R</sub>     |                      | 5          |                      | 5   |                      | 5   | ns   | _           |

| 5   | DOTCK fall time              | tr                 |                      | 5          |                      | 5   |                      | 5   | ns   | _           |

| 6   | 2CLKOUT delay                | t <sub>2CLKD</sub> |                      | 24         |                      | 17  |                      | 14  | ns   | 19          |

| 7   | MCYC setup time              | tmcycs             | t <sub>C</sub> +     |            | t <sub>C</sub> + 20  |     | t <sub>C</sub> +     |     | ns   | 20-23       |

| 8   | MCYC hold time               | tмсүсн             | 0                    |            | 0                    |     | 0                    |     | ns   | _           |

| 9   | HSYNC setup time             | H <sub>HSS</sub>   | t <sub>C</sub> + 20  |            | t <sub>C</sub> + 20  |     | t <sub>c</sub> +     |     | ns   | 20-22       |

| 10  | HSYNC hold time              | tusu               | 0                    | -          | 0                    |     | 0                    |     | ns   | 23          |

| 11) | MRD setup time               | tMRDS              | tc +                 |            | t <sub>C</sub> +     |     | tc +                 |     | ns   | 20-22       |

| 12  | MRD hold time                | tmrdh              | 5                    |            | 5                    |     | 5                    |     | ns   | 20, 21, 23  |

| 13) | DRAW setup time              | toraws             | t <sub>C</sub> +     | ,          | t <sub>C</sub> +     |     | t <sub>C</sub> +     |     | ns   | 20-22       |

| 14  | DRAW hold time               | torawh             | 5                    |            | 5                    |     | 5                    |     | ns   | 20, 21, 23  |

| 15) | AS setup time (CDM = 01)     | tass               | tc +<br>25           |            | t <sub>C</sub> +     |     | t <sub>C</sub> + 25  |     | ns   | 20-23       |

|     | AS setup time<br>(CMD = 10)  | tass               | 2t <sub>C</sub> + 25 | •          | 2t <sub>C</sub> +    |     | 2t <sub>C</sub> +    |     | ns   | _           |

|     | AS setup time (CDM = 11)     | tass               | 4t <sub>C</sub> + 25 |            | 4t <sub>C</sub> + 25 |     | 4t <sub>C</sub> +    |     | ns   | _           |

| 16  | AS pulse width               | tasw               | 25                   |            | 25                   |     | 25                   |     | ns   | _           |

| 10  | Memory address setup time    | tmas               | 10                   |            | 10                   |     | 10                   |     | ns   | 20-23       |

| 18  | Memory address hold time     | tmah               | 5                    |            | 5                    |     | 5                    |     | ns   | _           |

| 19  | Attribute code setup time    | tacs               | 20                   | <u>-</u> . | 20                   |     | 20                   |     | ns   | 23          |

| 20  | Attribute code hold time     | tach               | 5                    |            | 5                    |     | 5                    |     | ns   | _           |

| 21) | RAS setup time<br>(CDM = 01) | tess               | t <sub>C</sub> -     |            | t <sub>C</sub> -     |     | t <sub>C</sub> –     |     | ns   | 20-23       |

|     | RAS setup time<br>(CDM = 10) | tess               | 2t <sub>C</sub> — 20 |            | 2t <sub>C</sub> - 20 |     | 2t <sub>C</sub> — 20 |     | ns   | _           |

|     | RAS setup time<br>(CDM = 11) | trss               | 4t <sub>C</sub> -    |            | 4tc -                |     | 4t <sub>C</sub> -    |     | ns   |             |

| 22  | RAS hold time                | trsh               | 3                    |            | 3                    |     | 3                    |     | ns   | _           |

# **(1)** HITACHI

# AC Characteristics (cont)

|     | Item                                    | Symbol | 32 MHz                   |     | 48 MHz                 |     | 64 MHz                   |     |      |        |

|-----|-----------------------------------------|--------|--------------------------|-----|------------------------|-----|--------------------------|-----|------|--------|

| No  |                                         |        | Min                      | Max | Min                    | Max | Min                      | Max | Unit | Figure |

| 23) | CAS delay time (CDM = 01)               | tCASD  | t <sub>C</sub> - 7       |     | t <sub>C</sub> — 7     |     | t <sub>C</sub> — 7       |     | ns   | 20, 21 |

|     | CAS delay time<br>(CDM = 10)            | tCASD  | 2t <sub>C</sub> — 7      |     | 2t <sub>C</sub> — 7    | ·   | 2tc -<br>7               |     | ns   | _      |

|     | CAS delay time<br>(CDM = 11)            | tcasd  | 4tc<br>7                 |     | 4t <sub>C</sub> - 7    |     | 4t <sub>C</sub> —        |     | ns   | _      |

| 23A | CAS delay time<br>from 2CLK             | tCASDH |                          | 20  |                        | 20  |                          | 15  | ns   | _      |

| 24) | CAS hold time                           | tcash  | 5                        |     | 5                      |     | 5                        |     | ns   | -      |

| 25) | Memory address setup time (CDM = 01)    | tmasc  | t <sub>C</sub> +<br>25   |     | t <sub>C</sub> + 25    |     | t <sub>C</sub> + 25      |     | ns   | 20-23  |

|     | Memory address setup time (CDM = $10$ ) | tmasc  | 2t <sub>C</sub> +<br>25  |     | 2t <sub>C</sub> + 25   |     | 2t <sub>C</sub> + 25     |     | ns   | _      |

|     | Memory address setup time (CDM = $11$ ) | tmasc  | 4t <sub>C</sub> + 25     |     | 4t <sub>C</sub> + 25   |     | 4tc +<br>25              | •   | ns   | _      |

| 26  | Row address setup time                  | tras   | 0                        |     | 0                      |     | 0                        |     | ns   | _      |

| Ð   | Row address hold time (CDM = 01)        | trah   | t <sub>C</sub> /2<br>- 2 |     | tc/2<br>- 2            |     | t <sub>C</sub> /2<br>- 2 |     | ns   | -      |

|     | Row address hold time (CDM = 10)        | trah   | tc<br>- 2                |     | tc<br>- 2              |     | t <sub>C</sub> – 2       |     | ns   | -      |

|     | Row address hold time (CDM = 11)        | trah   | 2t <sub>C</sub><br>- 2   |     | 2t <sub>C</sub><br>- 2 | ,   | 2t <sub>C</sub><br>- 2   | ·   | ns   | _      |

| 28  | Column address setup time               | tcas   | 0                        |     | 0                      |     | 0                        |     | ns   | 20, 21 |

| 29  | Column address<br>hold time             | tcah   | 0                        |     | 0                      |     | 0                        |     | ns   |        |

| 30  | OE delay time                           | toed   |                          | 20  |                        | 20  |                          | 20  | ns   | 20     |

| 31) | OE hold time                            | toen   | 3                        |     | 3                      |     | 3                        |     | ns   | _      |

| 32  | WE delay time                           | tweD   | 5                        | 30  | 5                      | 30  | 5                        | 30  | ns   | 21     |

| 33  | WE hold time                            | twen   | 3                        |     | 3                      |     | 3                        |     | ns   | -      |

| 34  | Address delay time                      | tad    |                          | 30  |                        | 30  |                          | 30  | ns   |        |

| 35  | Address hold time                       | tah    | 0                        |     | 0                      |     | 0                        |     | ns   |        |

| 36  | SCKE delay time                         | tsckd  | 5                        | 24  | 5                      | 17  | 5                        | 14  | ns   | 18     |

| 37) | SLD delay time                          | tsldd  | 5                        | 24  | 5                      | 17  | 5                        | 14  | ns   |        |

| 38  | DSPCYC delay time from AS               | tospda |                          | 40  |                        | 40  |                          | 40  | ns   | 20     |

| 38A | DSPCYC delay time from DRAW             | tospod |                          | 20  |                        | 20  |                          | 20  | ns   |        |

| 39  | DSPCYC hold time                        | tosph  | 5                        |     | 5                      |     | 5                        |     | ns   |        |

Figure 19. 2CLKOUT

Figure 20. Memory Read Cycle (Drawing Read and Display)

Figure 21. Memory Write Cycle

Figure 22. Refresh Cycle

Figure 23. Attribute Cycle

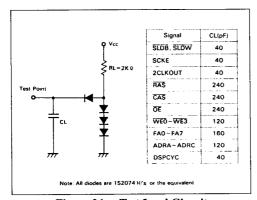

Figure 24. Test Load Circuit

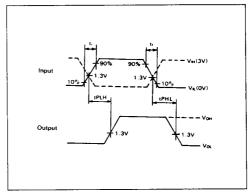

Figure 25. Input/Output Waveforms

# Reference Literature

| Product       | Data Sheet | User's Manual | Application Note                              | Others                |

|---------------|------------|---------------|-----------------------------------------------|-----------------------|

| HD63484 ACRTC | E-0045A    | 680-1-31A     | Introduction to ACRTC<br>Application 680-3-08 | Programming Reference |

|               |            |               | Circuits Software<br>680-3-07                 | AD-E0032A             |

| HD63486 GVAC  | AD-E0123   |               |                                               |                       |