# Hitachi Single-Chip Microcomputer H8/325 Series

H8/3257,H8/3256 H8/325,H8/324,H8/323,H8/322 Hardware Manual

# HITACHI

Hitachi Micro Systems, Incorporated

# Notice

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# Table Of Contents

| Preface                                                | 1  |

|--------------------------------------------------------|----|

| Section 1. Overview                                    | 3  |

| 1.1 Overview                                           |    |

| 1.2 Block Diagram                                      | 7  |

| 1.3 Pin Assignments and Functions                      |    |

| 1.3.1 Pin Arrangement                                  |    |

| 1.3.2 Pin Functions                                    |    |

| Section 2. MCU Operating Modes and Address Space       | 17 |

| 2.1 Overview                                           |    |

| 2.2 Mode Descriptions                                  |    |

| 2.3 Address Space Map                                  |    |

| 2.3.1 Access Speed                                     |    |

| 2.3.2 IOS                                              | 19 |

| 2.4 Mode and System Control Registers (MDCR and SYSCR) |    |

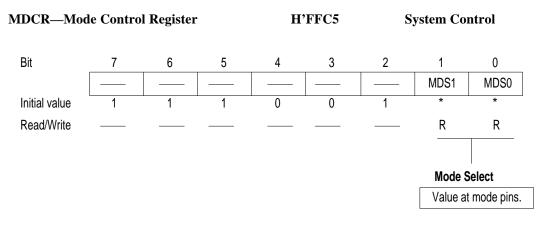

| 2.4.1 Mode Control Register (MDCR)—H'FFC5              |    |

| 2.4.2 System Control Register (SYSCR)—H'FFC4           |    |

| Section 3. CPU                                         |    |

| 3.1 Overview                                           |    |

| 3.1.1 Features                                         |    |

| 3.2 Register Configuration                             |    |

| 3.2.1 General Registers                                |    |

| 3.2.2 Control Registers                                |    |

| 3.2.3 Initial Register Values                          |    |

| 3.3 Addressing Modes                                   |    |

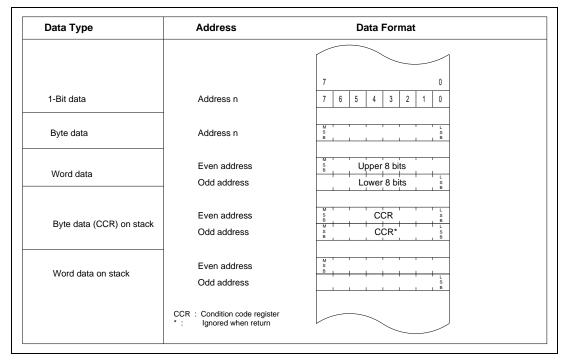

| 3.4 Data Formats                                       |    |

| 3.4.1 Data Formats in General Registers                |    |

| 3.4.2 Memory Data Formats                              |    |

| 3.5 Instruction Set                                    |    |

| 3.5.1 Data Transfer Instructions                       |    |

| 3.5.2 Arithmetic Operations                            |    |

| 3.5.3 Logic Operations                                 |    |

| 3.5.4 Shift Operations                                 |    |

| 3.5.5 Bit Manipulations                                |    |

| 3.5.6 Branching Instructions                           | 51 |

| 3.5.7 System Control Instructions                      | 53 |

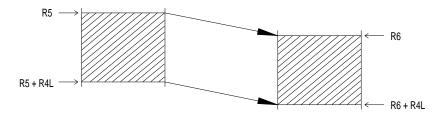

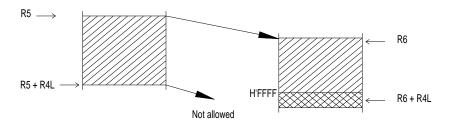

| 3.5.8 Block Data Transfer Instruction                  | 54 |

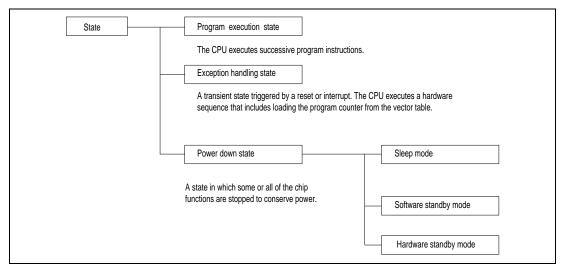

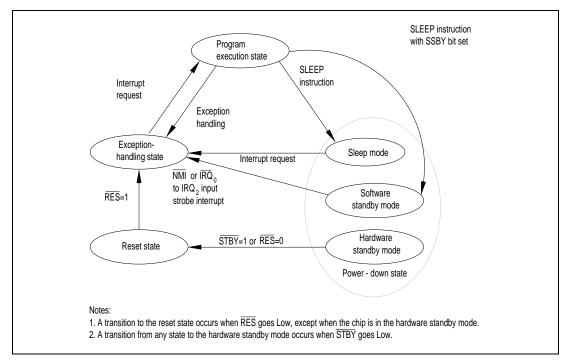

| 3.6 CPU States                                              | 56  |

|-------------------------------------------------------------|-----|

| 3.6.1 Program Execution State                               | 57  |

| 3.6.2 Exception-Handling State                              | 57  |

| 3.6.3 Power-Down State                                      | 58  |

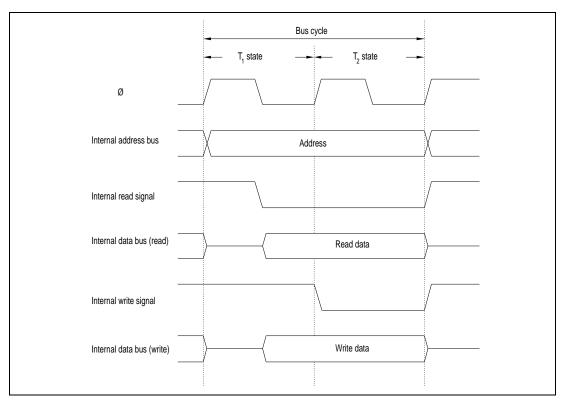

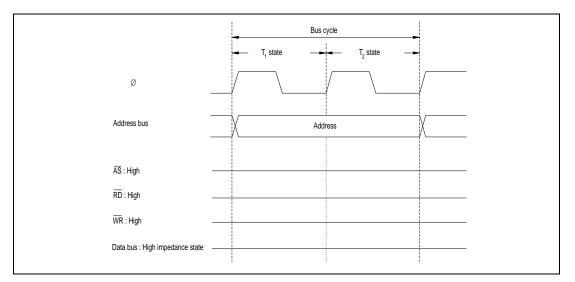

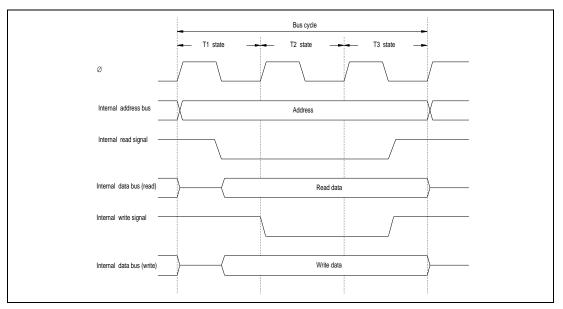

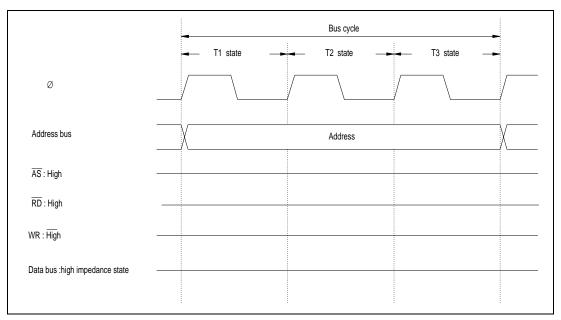

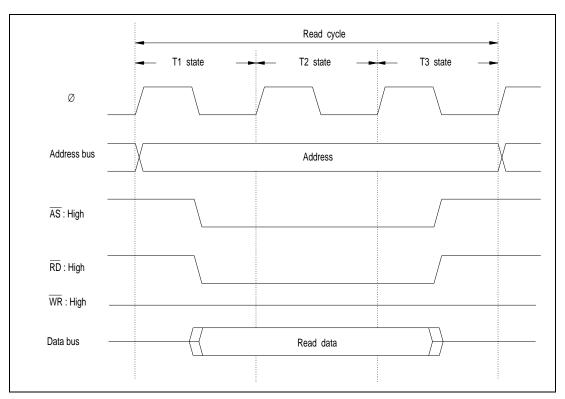

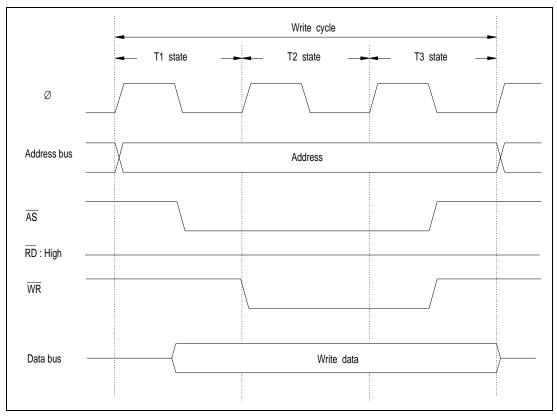

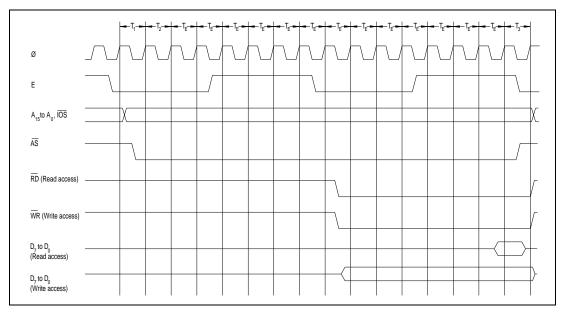

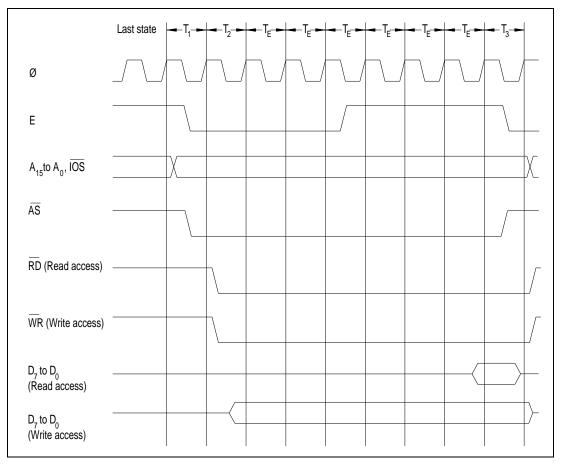

| 3.7 Access Timing and Bus Cycle                             | 58  |

| 3.7.1 Access to On-Chip Memory (RAM and ROM)                | 58  |

| 3.7.2 Access to On-Chip Register Field and External Devices | 60  |

| Section 4. Exception Handling                               | 63  |

| 4.1 Overview                                                |     |

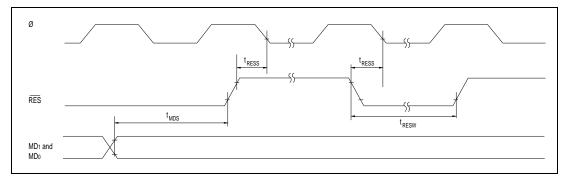

| 4.2 Reset                                                   | 53  |

| 4.2.1 Overview                                              | 63  |

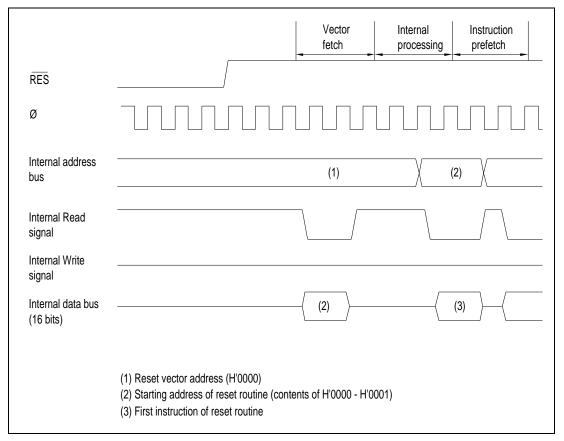

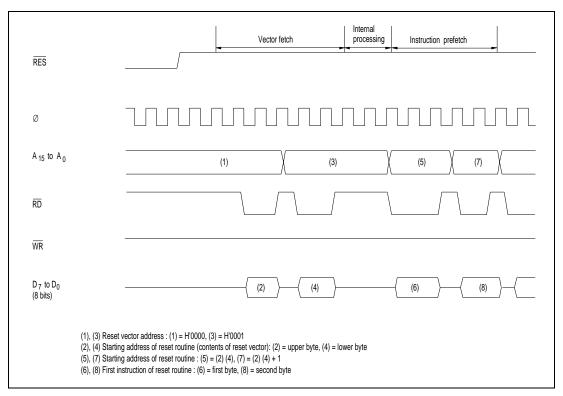

| 4.2.2 Reset Sequence                                        | 63  |

| 4.2.3 Disabling of Interrupts after Reset                   | 66  |

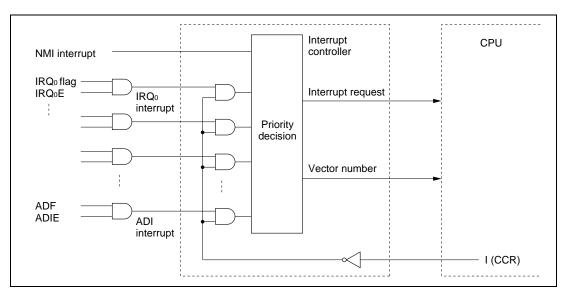

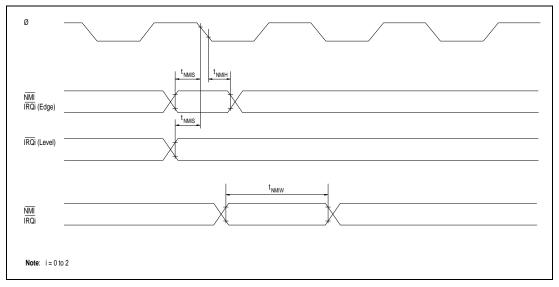

| 4.3 Interrupts                                              | 66  |

| 4.3.1 Overview                                              | 66  |

| 4.3.2 Interrupt-Related Registers                           | 67  |

| 4.3.3 External Interrupts                                   | 70  |

| 4.3.4 Internal Interrupts                                   | 71  |

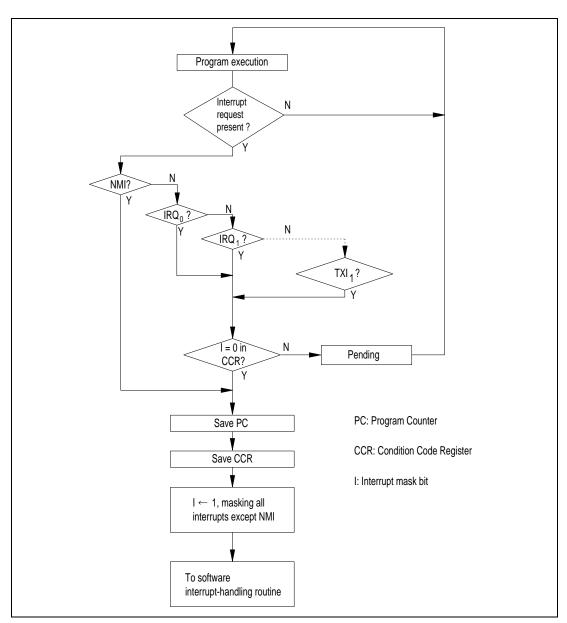

| 4.3.5 Interrupt Handling                                    | 72  |

| 4.3.6 Interrupt Response Time                               | 77  |

| 4.4 Note on Stack Handling                                  | 77  |

|                                                             |     |

| Section 5. I/O Ports                                        |     |

| 5.1 Overview                                                | 79  |

| 5.2 Port 1                                                  |     |

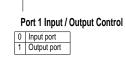

| Port 1 Data Direction Register (P1DDR)—H'FFB0               |     |

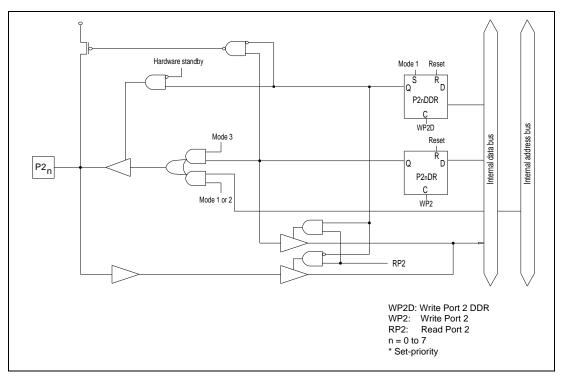

| 5.3 Port 2                                                  |     |

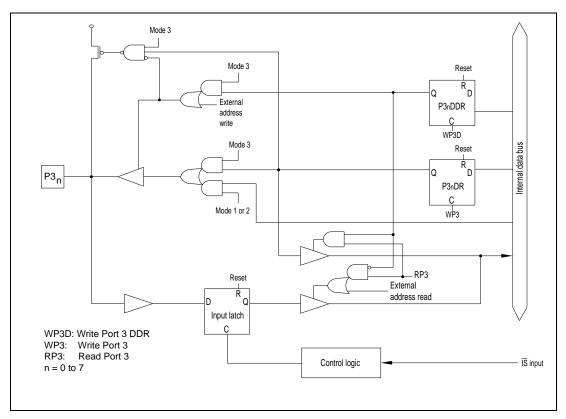

| 5.4 Port 3                                                  |     |

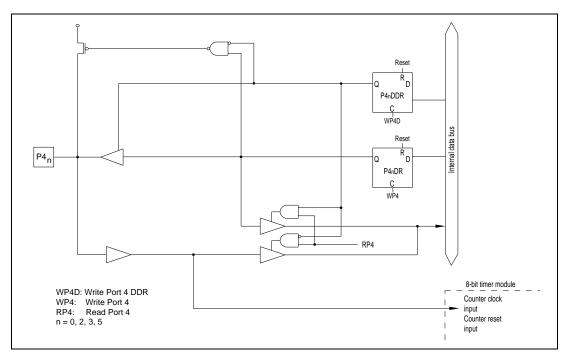

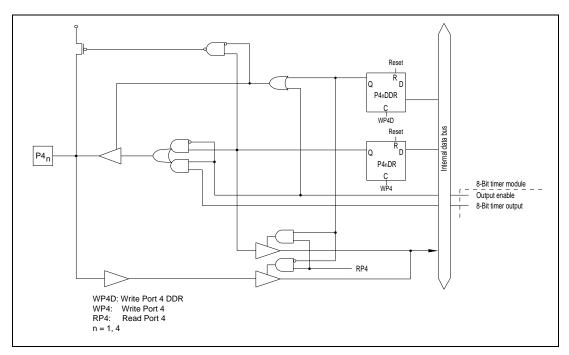

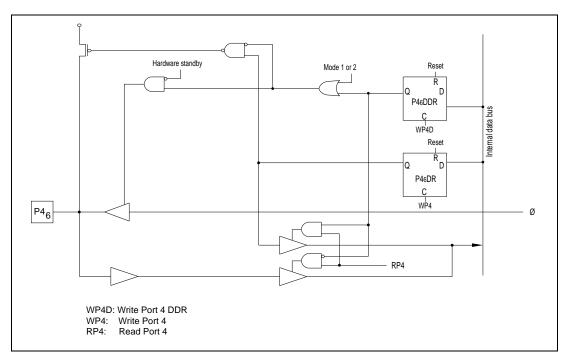

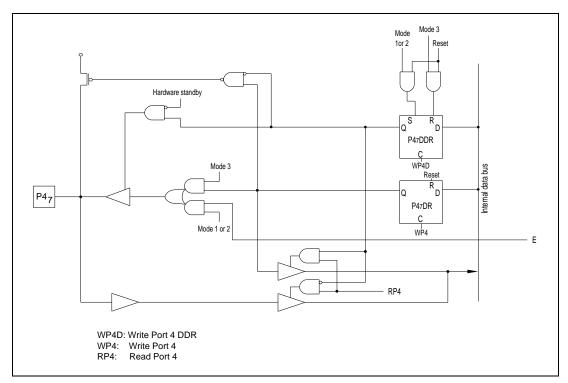

| 5.5 Port 4                                                  |     |

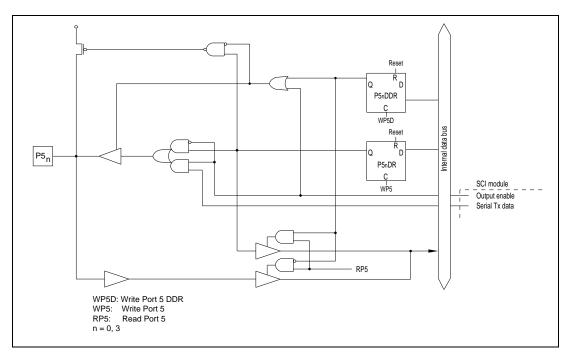

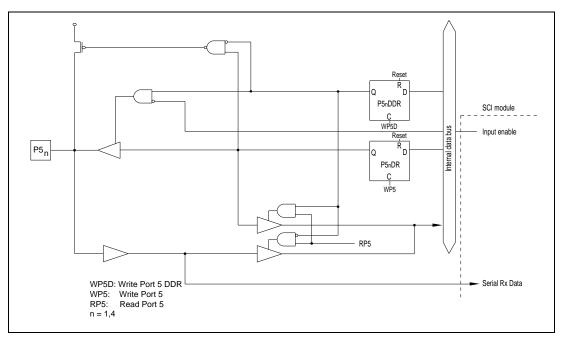

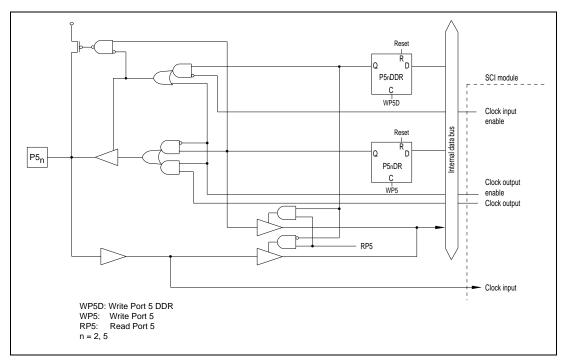

| 5.6 Port 5                                                  |     |

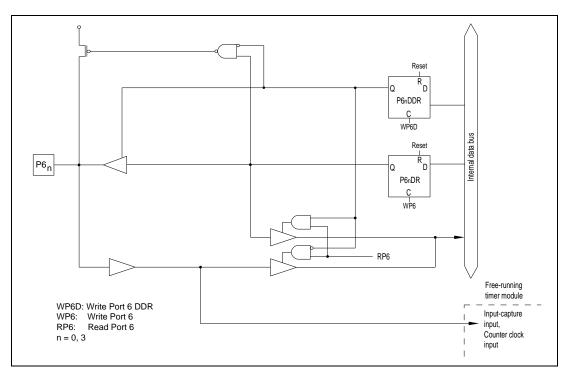

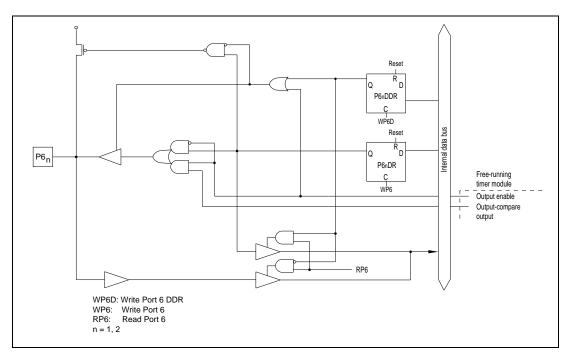

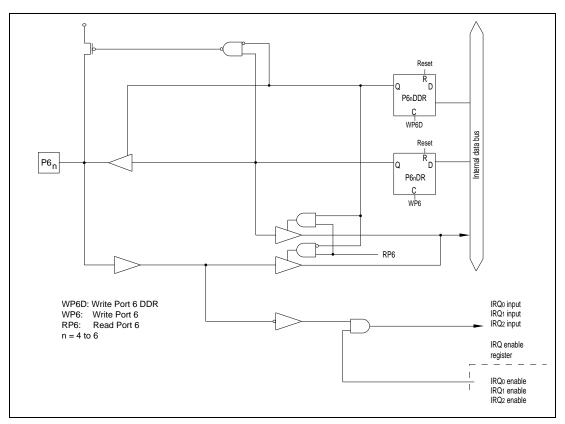

| 5.7 Port 6                                                  |     |

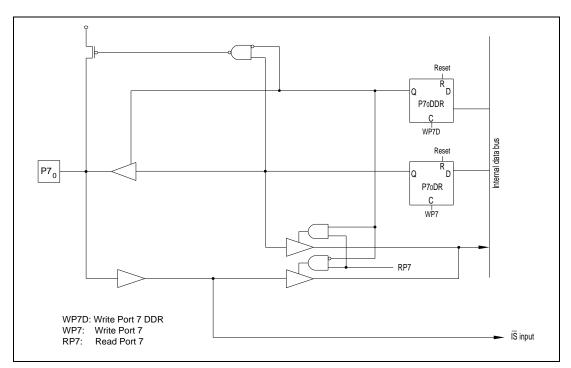

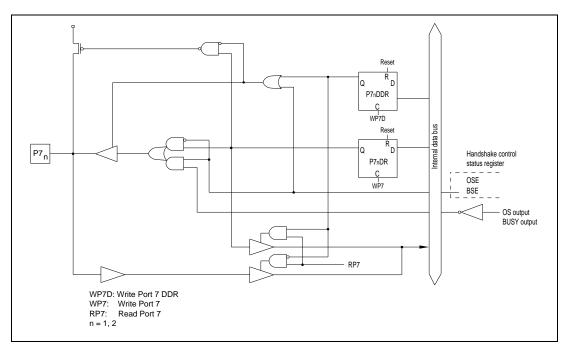

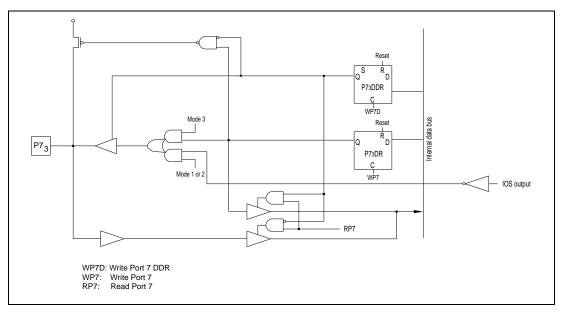

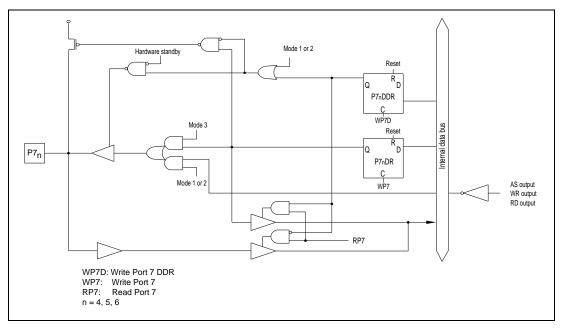

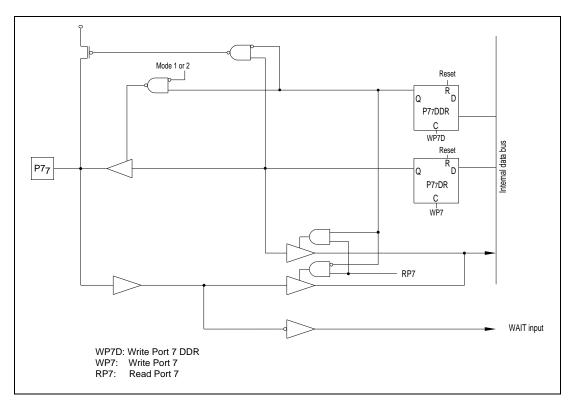

| 5.8 Port 7 1                                                | 106 |

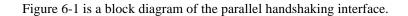

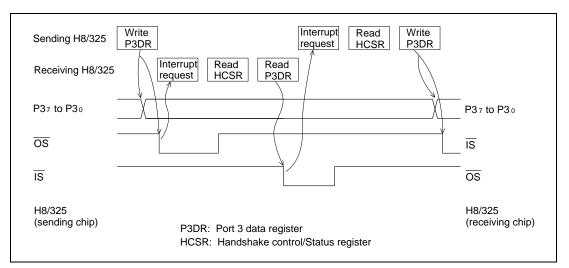

| Section 6. Parallel Handshaking Interface                   | 115 |

| 6.1 Overview                                                | 115 |

| 6.1.1 Features                                              | 115 |

| 6.1.2 Block Diagram                                         | 116 |

| 6.1.3 Input and Output Pins                                 |     |

| 6.2 Register Descriptions                                   | 117 |

| 6.2.1 Port 3 Data Direction Register (P3DDR)                | 117 |

| 6.2.2 Port 3 Data Register (P3DR)                           |     |

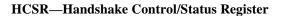

| 6.2.3 Handshake Control/Status Register (HCSR)              | 118 |

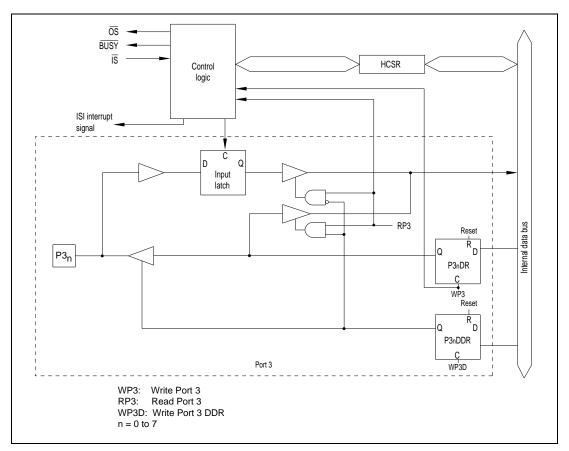

| 6.3 Operation                                             | J |

|-----------------------------------------------------------|---|

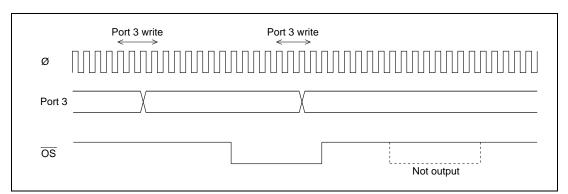

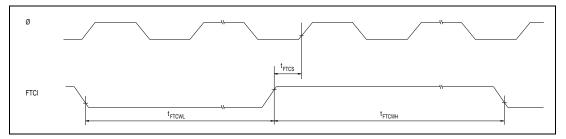

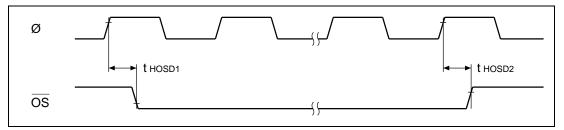

| 6.3.1 Output Timing of Output Strobe Signal               | ) |

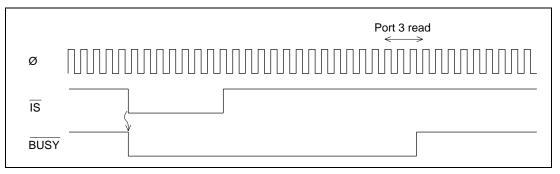

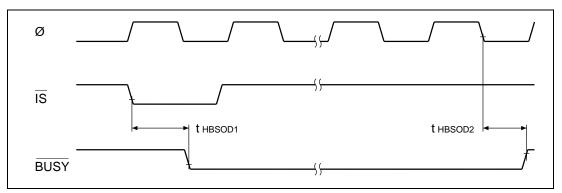

| 6.3.2 Busy Signal Output Timing                           |   |

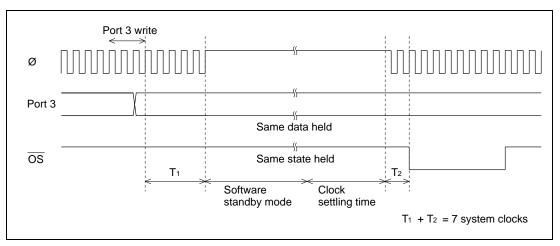

| 6.3.3 Operation in Software Standby Mode                  |   |

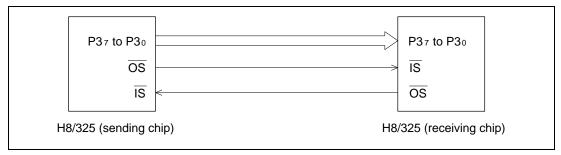

| 6.3.4 Sample Application                                  |   |

| 6.3.5 Interrupts                                          |   |

|                                                           |   |

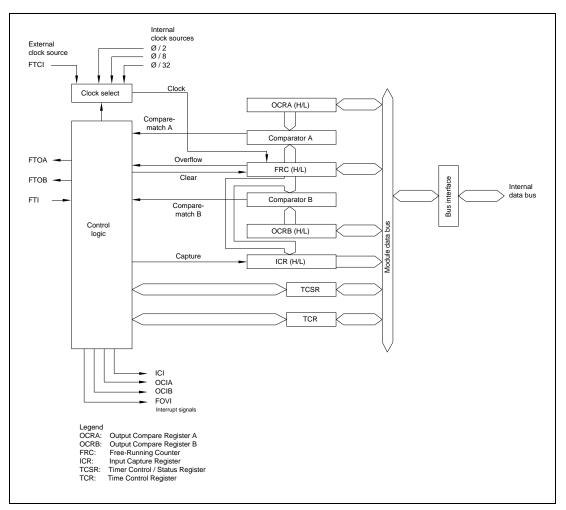

| Section 7. 16-BIT Free-Running Timer                      | 5 |

| 7.1 Overview                                              |   |

| 7.1.1 Features                                            |   |

| 7.1.2 Block Diagram                                       |   |

| 7.1.3 Input and Output Pins                               |   |

| 7.1.4 Register Configuration                              |   |

| 7.2 Register Descriptions                                 |   |

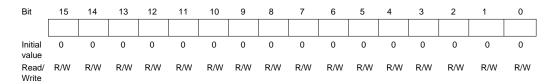

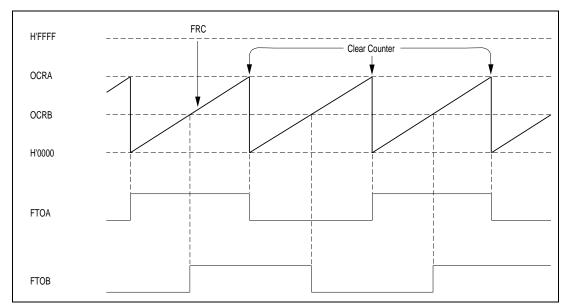

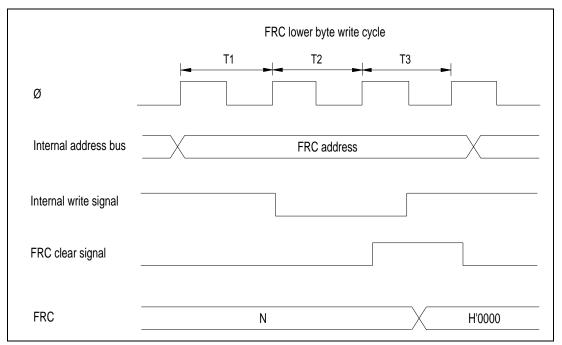

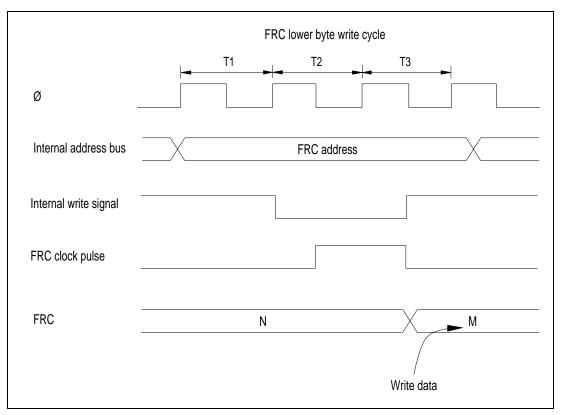

| 7.2.1 Free-Running Counter (FRC) - H'FF92                 |   |

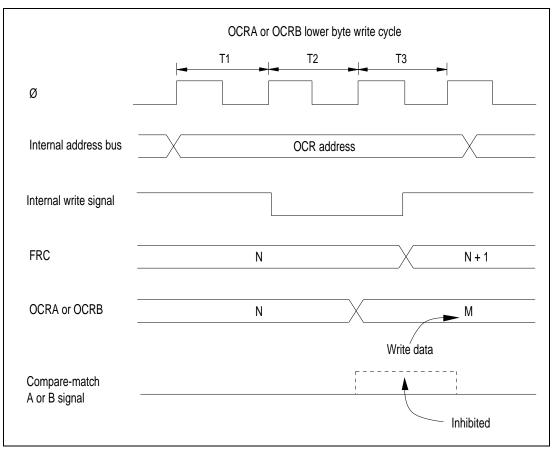

| 7.2.2 Output Compare Registers A and B                    |   |

| (OCRA and OCRB) - H'FF94 and H'FF96                       |   |

| 7.2.3 Input Capture Register (ICR) - H'FF98               |   |

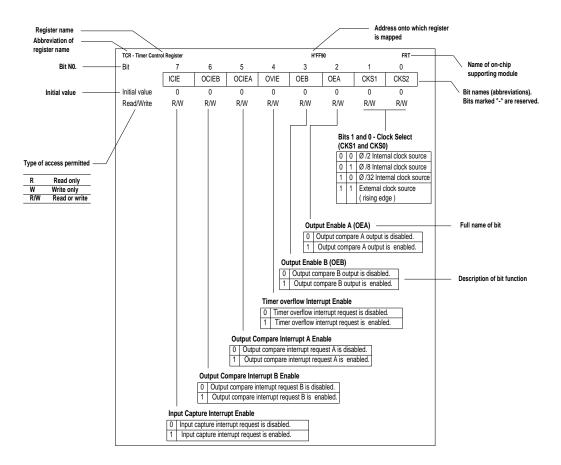

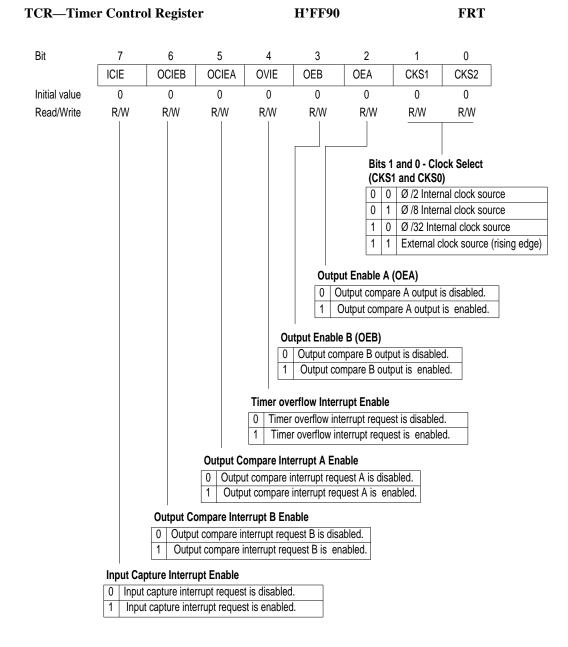

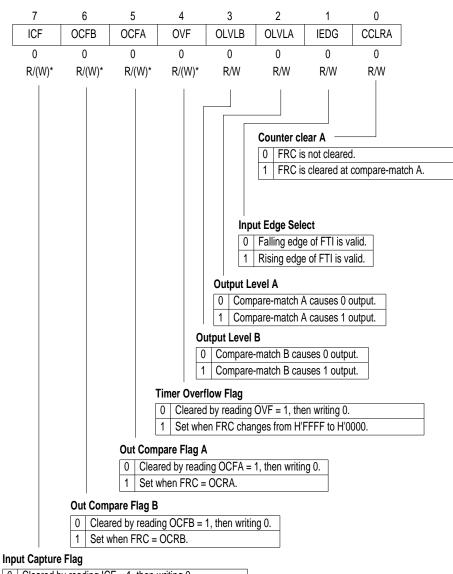

| 7.2.4 Timer Control Register (TCR) - H'FF90               |   |

| 7.2.5 Timer Control/Status Register (TCSR) - H'FF91       |   |

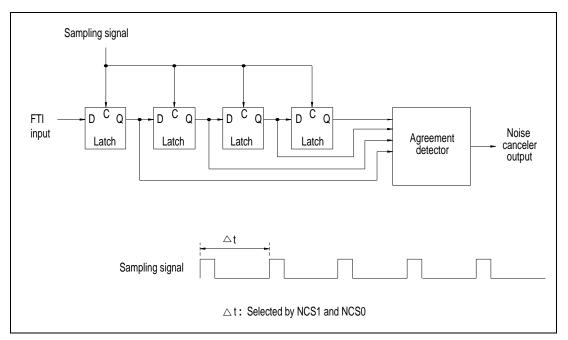

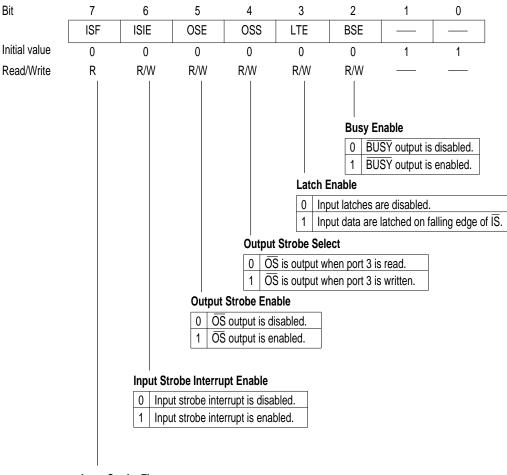

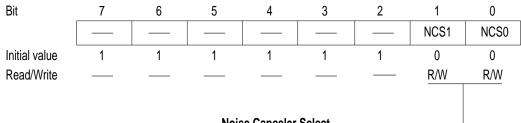

| 7.2.6 FRT Noise Canceler Control Register (FNCR) - H'FFFF |   |

| 7.3 CPU Interface                                         |   |

| 7.4 Operation                                             |   |

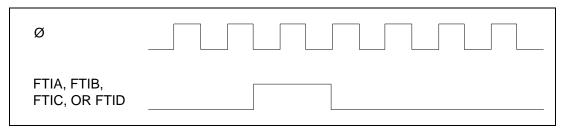

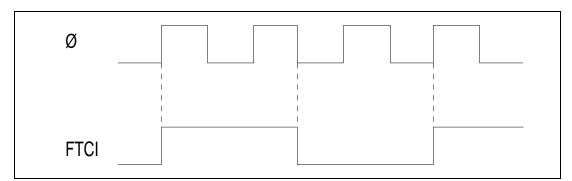

| 7.4.1 FRC Incrementation Timing                           |   |

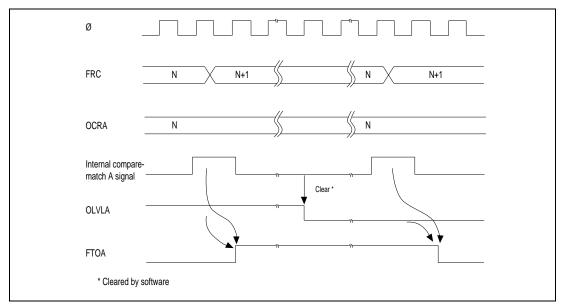

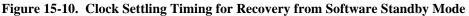

| 7.4.2 Output Compare Timing                               |   |

| 7.4.3 FRC Clear Timing                                    |   |

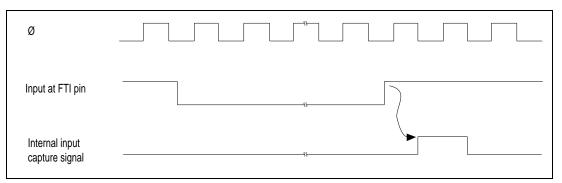

| 7.4.4 Input Capture Timing                                |   |

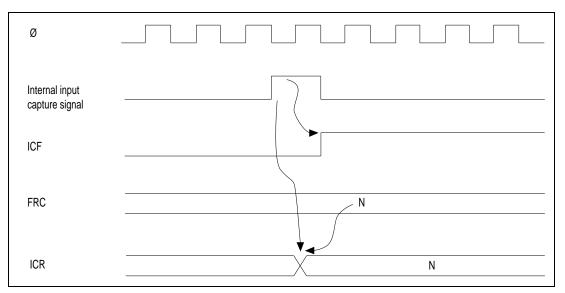

| 7.4.5 Timing of Input Capture Flag (ICF) Setting          |   |

| 7.4.6 Setting of FRC Overflow Flag (OVF)                  |   |

| 7.5 Interrupts                                            |   |

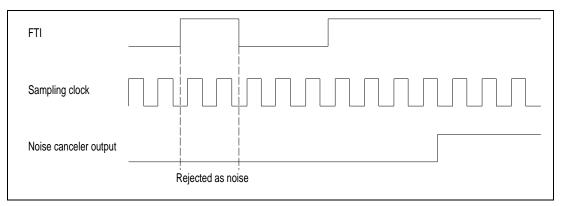

| 7.6 Noise Canceler                                        |   |

| 7.7 Sample Application                                    |   |

| 7.8 Application Notes                                     |   |

|                                                           |   |

| Section 8. 8-Bit Timers151                                | l |

| 8.1 Overview                                              |   |

| 8.1.1 Features                                            |   |

| 0.1.1 1 catalos                                           |   |

|                                                           |   |

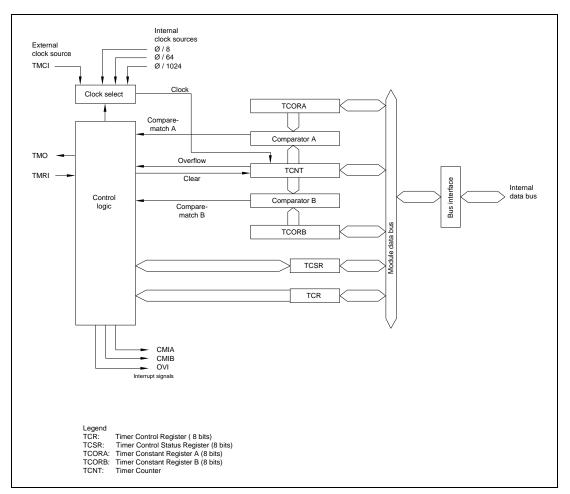

| 8.1.2 Block Diagram151                                    |   |

| 8.1.2 Block Diagram                                       |   |

| 8.1.2 Block Diagram151                                    |   |

| 8.2.2 Time Constant Registers A and B (TCORA and TCORB) |     |  |  |  |

|---------------------------------------------------------|-----|--|--|--|

| – H'FFCA and H'FFCB (TMR0), H'FFD2 and H'FFD3 (TMR1)    |     |  |  |  |

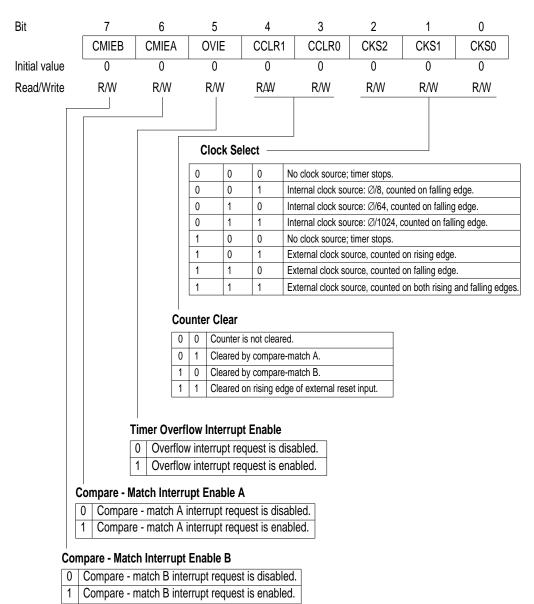

| 8.2.3 Timer Control Register (TCR)                      |     |  |  |  |

| – H'FFC8 (TMR0), H'FFD0 (TMR1)                          |     |  |  |  |

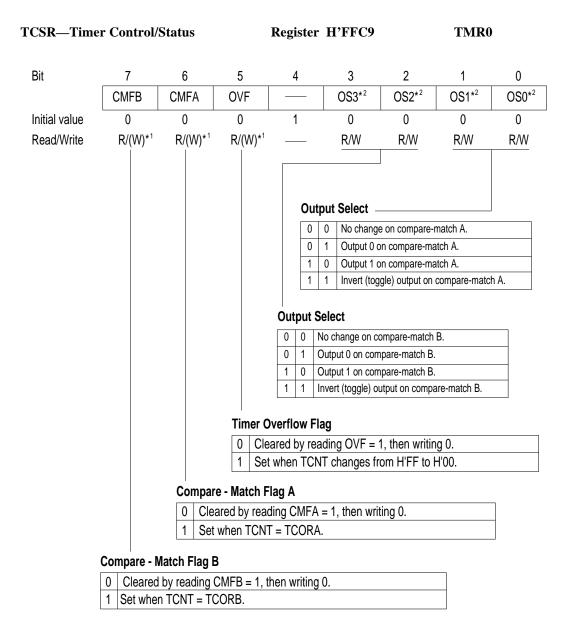

| 8.2.4 Timer Control/Status Register (TCSR)              |     |  |  |  |

| – H'FFC9 (TMR0), H'FFD1 (TMR1)                          |     |  |  |  |

| 8.3 Operation                                           |     |  |  |  |

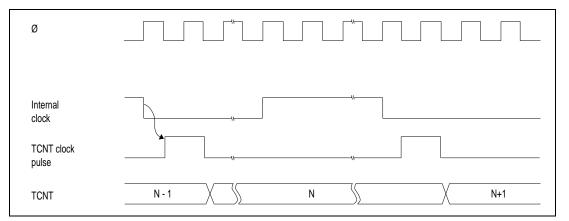

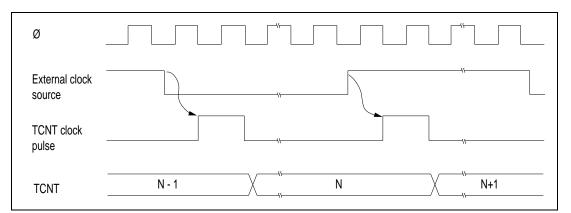

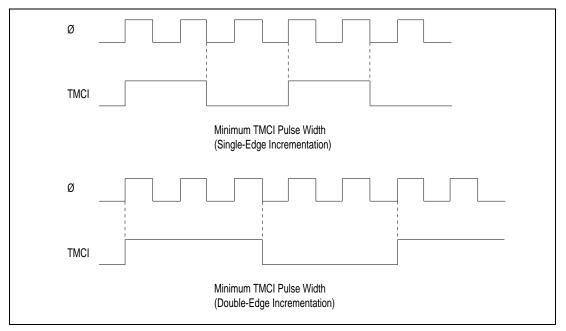

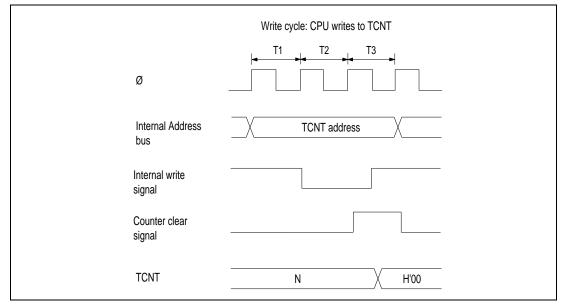

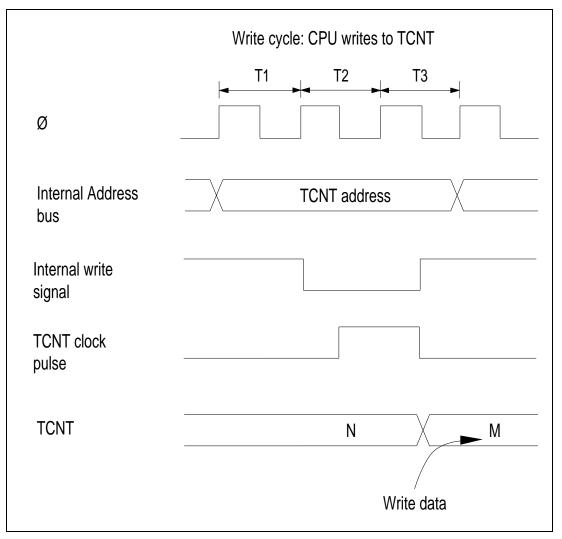

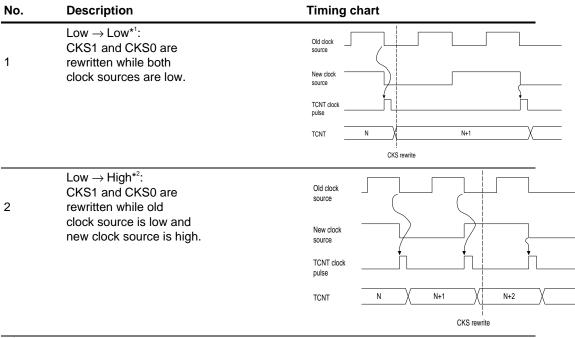

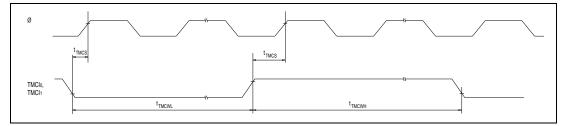

| 8.3.1 TCNT Incrementation Timing                        |     |  |  |  |

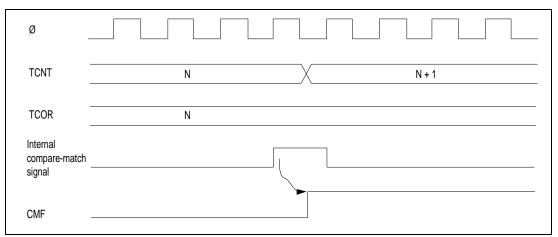

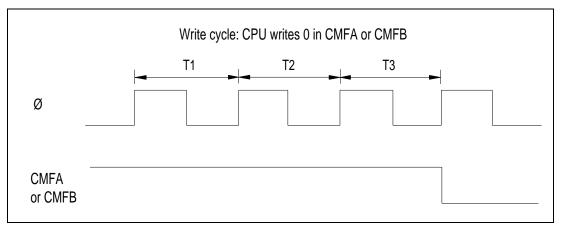

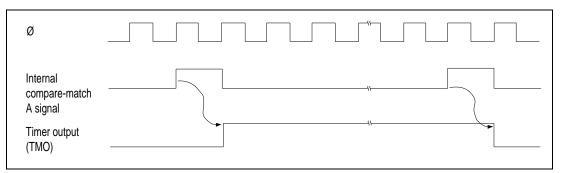

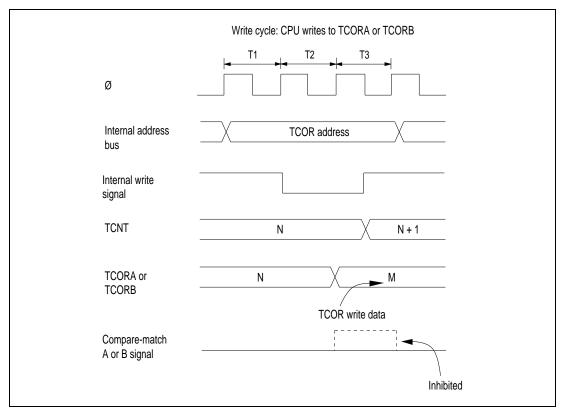

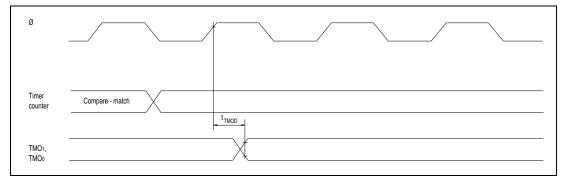

| 8.3.2 Compare Match Timing                              | 159 |  |  |  |

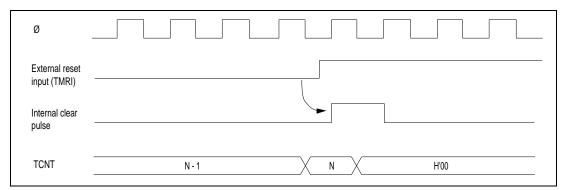

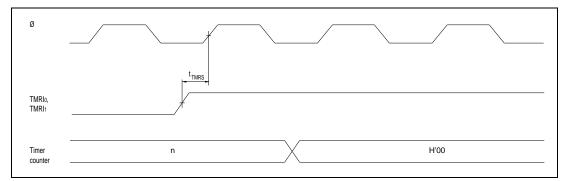

| 8.3.3 External Reset of TCNT                            | 161 |  |  |  |

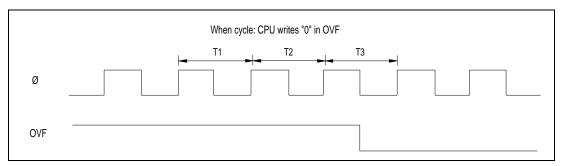

| 8.3.4 Setting of TCSR Overflow Flag                     |     |  |  |  |

| 8.4 Interrupts                                          |     |  |  |  |

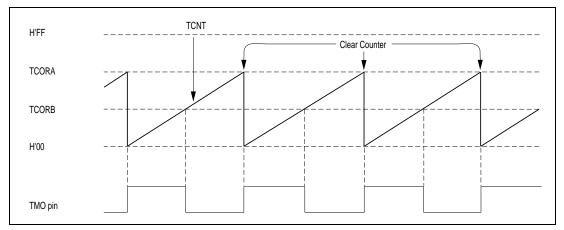

| 8.5 Sample Application                                  |     |  |  |  |

| 8.6 Application Notes                                   |     |  |  |  |

|                                                         |     |  |  |  |

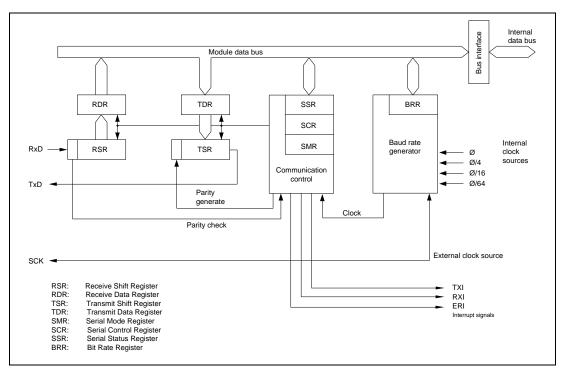

| Section 9. Serial Communication Interface               |     |  |  |  |

| 9.1 Overview                                            |     |  |  |  |

| 9.1.1 Features                                          |     |  |  |  |

| 9.1.2 Block Diagram                                     |     |  |  |  |

| 9.1.3 Input and Output Pins                             |     |  |  |  |

| 9.1.4 Register Configuration                            | 171 |  |  |  |

| 9.2 Register Descriptions                               | 171 |  |  |  |

| 9.2.1 Receive Shift Register (RSR)                      | 171 |  |  |  |

| 9.2.2 Receive Data Register (RDR) – H'FFDD              |     |  |  |  |

| 9.2.3 Transmit Shift Register (TSR)                     |     |  |  |  |

| 9.2.4 Transmit Data Register (TDR) – H'FFDB             |     |  |  |  |

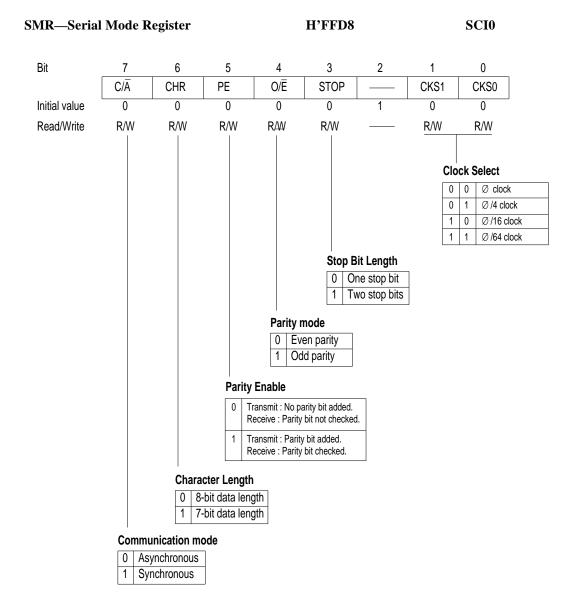

| 9.2.5 Serial Mode Register (SMR) – H'FFD8               |     |  |  |  |

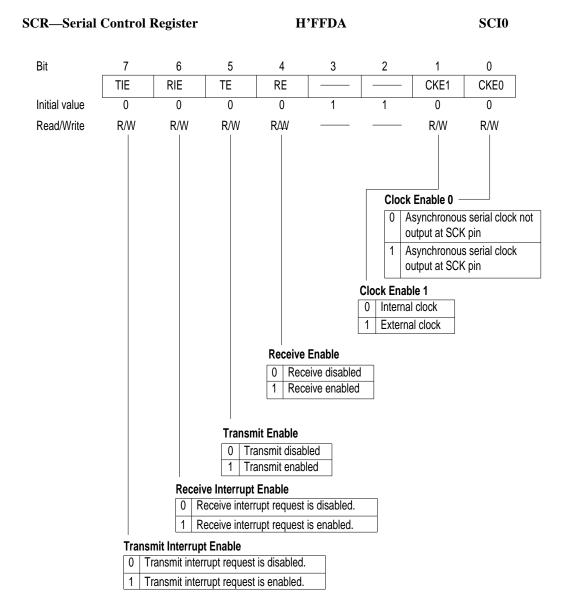

| 9.2.6 Serial Control Register (SCR) – H'FFDA            |     |  |  |  |

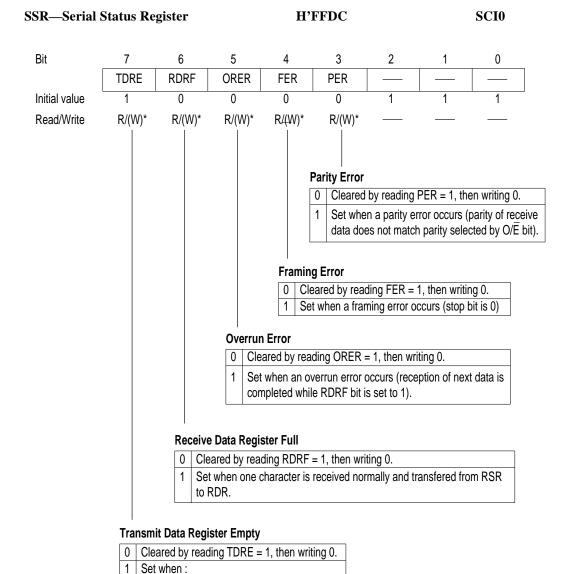

| 9.2.7 Serial Status Register (SSR) – H'FFDC             |     |  |  |  |

| 9.2.8 Bit Rate Register (BRR) – H'FFD9                  |     |  |  |  |

| 9.3 Operation                                           |     |  |  |  |

| 9.3.1 Overview                                          |     |  |  |  |

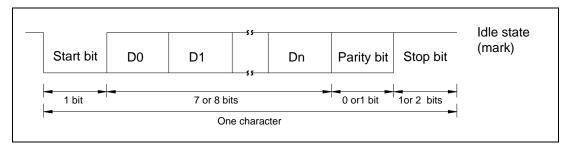

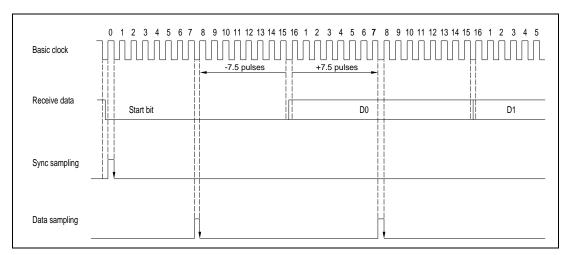

| 9.3.2 Asynchronous Mode                                 |     |  |  |  |

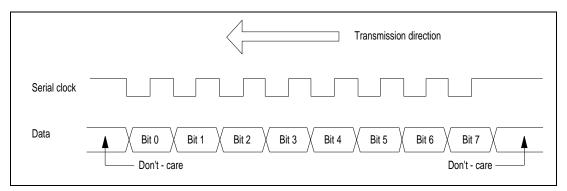

| 9.3.3 Synchronous Mode                                  |     |  |  |  |

| 9.4 Interrupts                                          |     |  |  |  |

| 9.5 Application Notes                                   |     |  |  |  |

| Section 10 DAM                                          | 107 |  |  |  |

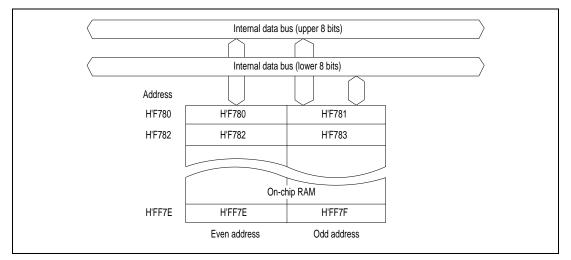

| Section 10. RAM.                                        |     |  |  |  |

| 10.1 Overview                                           |     |  |  |  |

| 10.2 Block Diagram.                                     |     |  |  |  |

| 10.3 RAM Enable Bit (RAME)                              |     |  |  |  |

| 10.4 Operation                                          |     |  |  |  |

| 10.4.1 Expanded Modes (Modes 1 and 2)                   |     |  |  |  |

| 10.4.2 Single-Chip Mode (Mode 3)                      | 199 |

|-------------------------------------------------------|-----|

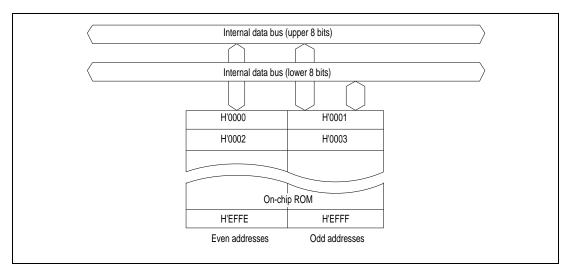

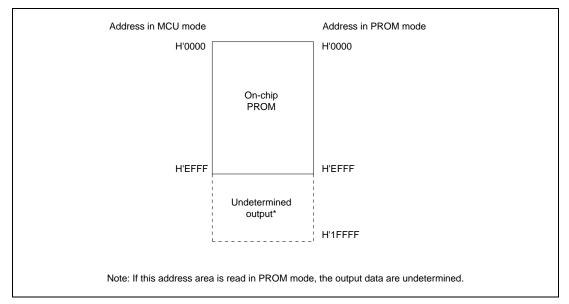

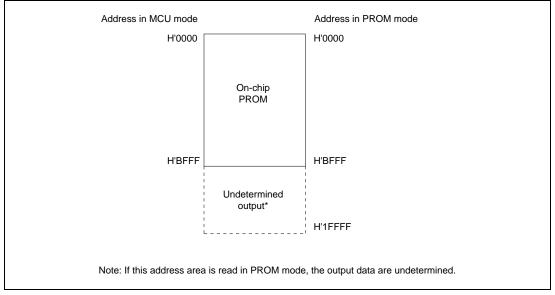

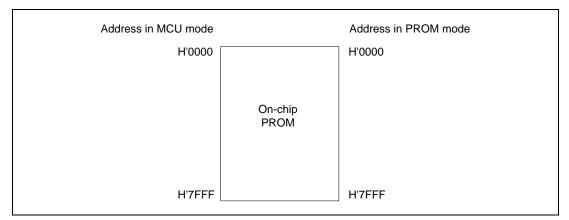

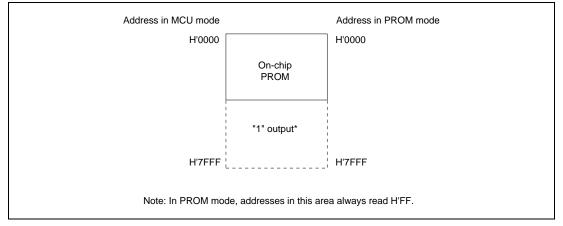

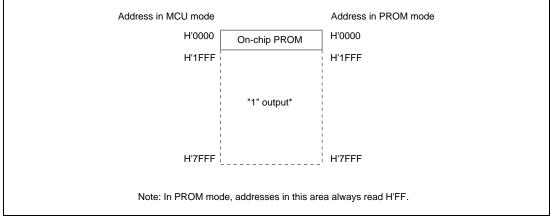

| Section 11. ROM                                       | 201 |

| 11.1 Overview                                         |     |

| 11.1.1 Block Diagram                                  |     |

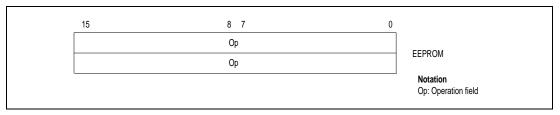

| 11.2 PROM Mode                                        |     |

| 11.2.1 PROM Mode Setup                                |     |

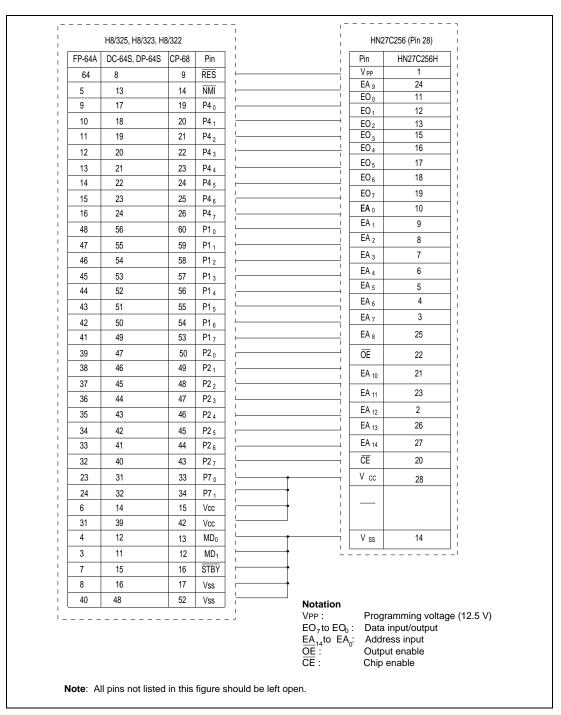

| 11.2.2 Socket Adapter Pin Assignments and Memory Map  |     |

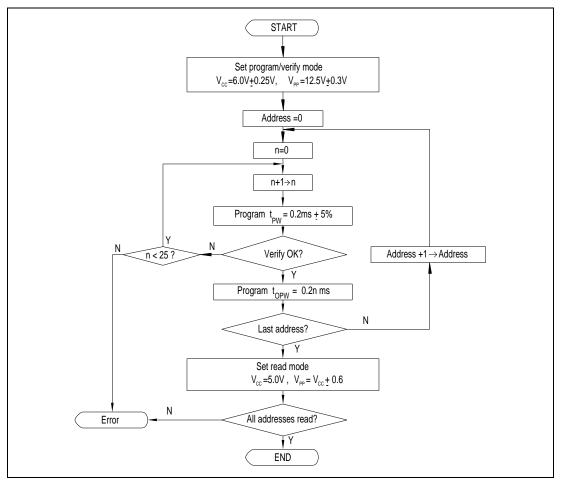

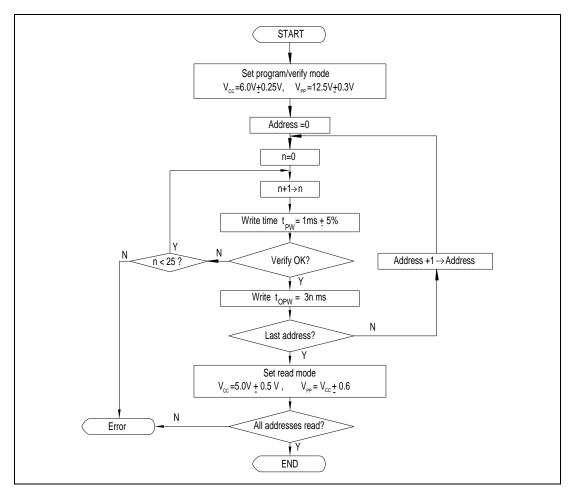

| 11.3 Programming                                      |     |

| 11.3.1 Selection of Sub-Modes in PROM Mode            |     |

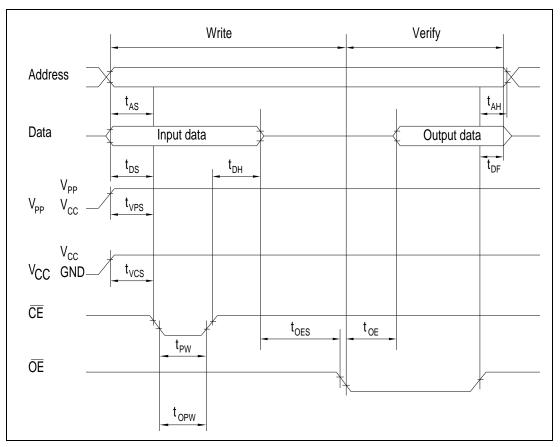

| 11.3.2 Writing and Verifying                          |     |

| 11.3.3 Notes on Writing                               |     |

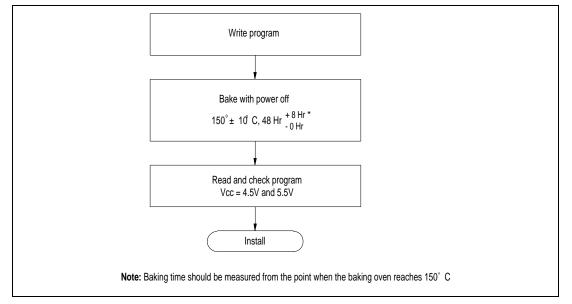

| 11.3.4 Reliability of Written Data                    |     |

| 11.3.5 Erasing of Data                                |     |

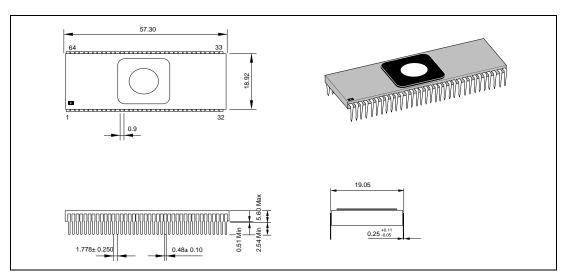

| 11.4 Handling of Windowed Packages                    |     |

|                                                       |     |

| Section 12. Power-Down State                          | 219 |

| 12.1 Overview                                         |     |

| 12.2 System Control Register: Power-Down Control Bits |     |

| 12.3 Sleep Mode                                       |     |

| 12.3.1 Transition to Sleep Mode                       |     |

| 12.3.2 Exit from Sleep Mode                           |     |

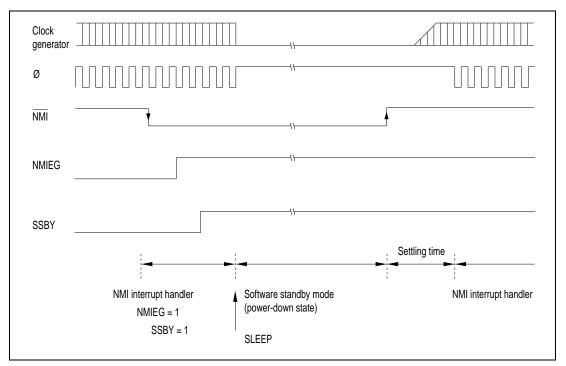

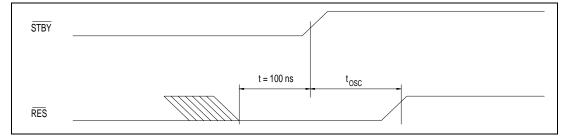

| 12.4 Software Standby Mode                            |     |

| 12.4.1 Transition to Software Standby Mode            |     |

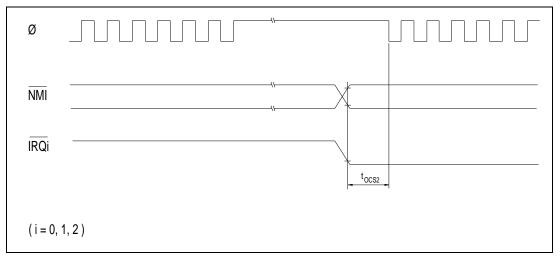

| 12.4.2 Exit from Software Standby Mode                |     |

| 12.4.3 Sample Application of Software Standby Mode    |     |

| 12.4.4 Notes on Current Dissipation                   |     |

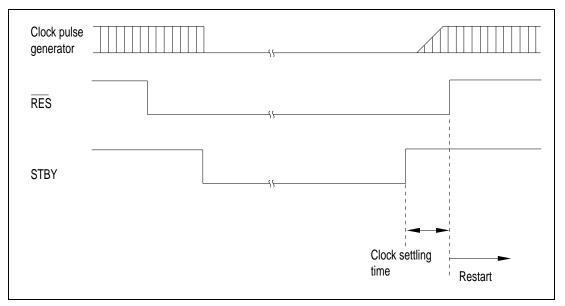

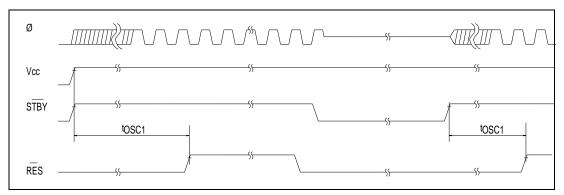

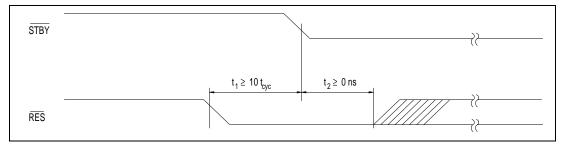

| 12.5 Hardware Standby Mode                            |     |

| 12.5.1 Transition to Hardware Standby Mode            |     |

| 12.5.2 Recovery from Hardware Standby Mode            |     |

| 12.5.3 Timing Relationships                           |     |

|                                                       |     |

| Section 13. E-Clock Interface                         | 227 |

| 13.1 Overview                                         |     |

|                                                       |     |

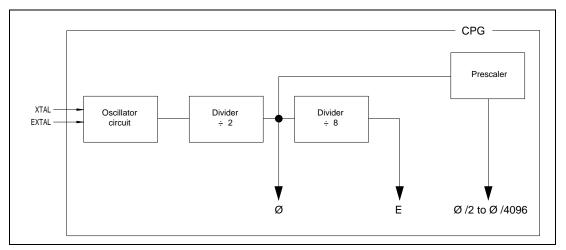

| Section 14. Clock Pulse Generator                     | 231 |

| 14.1 Overview                                         |     |

| 14.1.1 Block Diagram                                  |     |

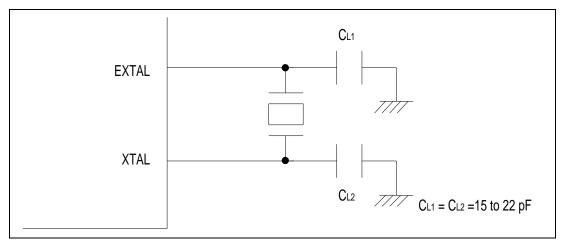

| 14.2 Oscillator Circuit                               |     |

| 14.3 System Clock Divider                             |     |

|                                                       |     |

| Section 15. Electrical Specifications                 | 235 |

| 15.1 Absolute Maximum Ratings                         |     |

|                                                       |     |

| 15.2 Electrical Characteristics              |     |

|----------------------------------------------|-----|

| 15.2.1 DC Characteristics                    |     |

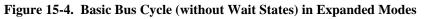

| 15.2.2 AC Characteristics                    |     |

| 15.3 MCU Operational Timing                  |     |

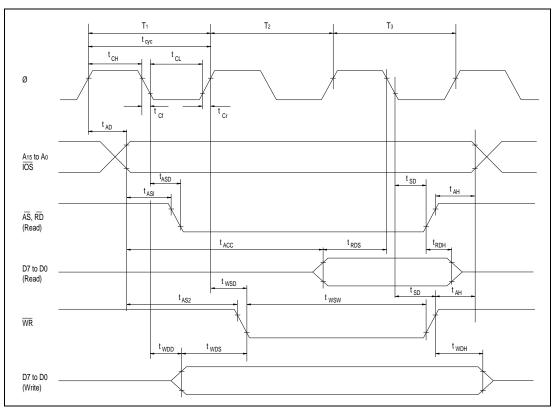

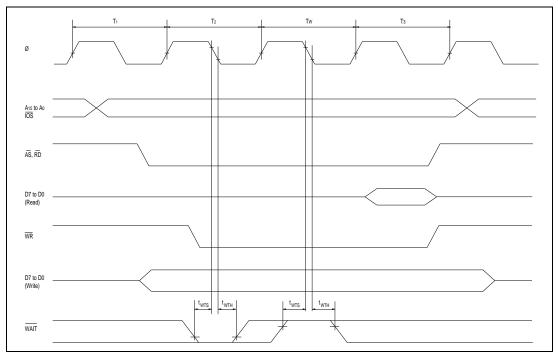

| 15.3.1 Bus Timing                            |     |

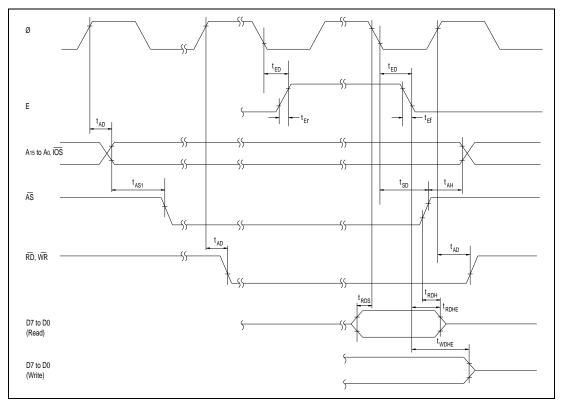

| 15.3.2 Control Signal Timing                 |     |

| 15.3.3 16-Bit Free-Running Timer Timing      |     |

| 15.3.4 8-Bit Timer Timing                    |     |

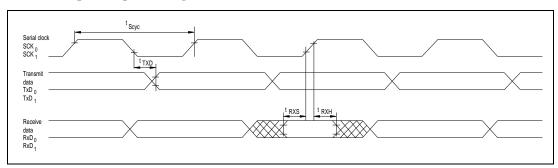

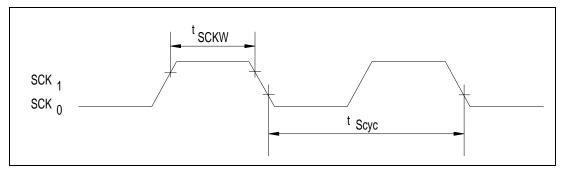

| 15.3.5 Serial Communication Interface Timing |     |

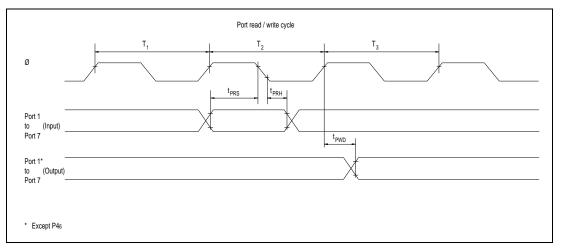

| 15.3.6 I/O Port Timing                       |     |

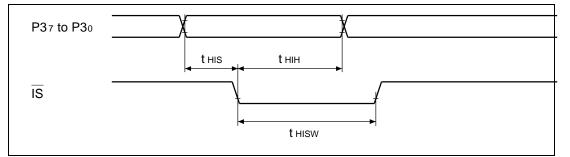

| 15.3.7 Parallel Handshake Interface Timing   |     |

| Appendix A. CPU Instruction Set              | 257 |

| A.1 Instruction Set List                     |     |

| A.2 Operation Code Map                       |     |

| A.3 Number of States Required for Execution  |     |

| Appendix B. Register Field                   | 273 |

| B.1 Register Addresses and Bit Names         |     |

| B.2 Register Descriptions                    |     |

| TCR—Timer Control Register                   |     |

| •                                            |     |

| FRC (H and L)—Free-Running Counter           |     |

| OCRA (H and L)—Output Compare Register A     |     |

| OCRB (H and L)—Output Compare Register B     |     |

| ICR (H and L)—Input Capture Register         |     |

| P1DDR—Port 1 Data Direction Register         |     |

| P2DDR—Port 2 Data Direction Register         |     |

| P2DR—Port 2 Data Register                    |     |

| P3DDR—Port 3 Data Direction Register         |     |

| P3DR—Port 3 Data Register                    |     |

| P4DDR—Port 4 Data Direction Register         |     |

| P4DR—Port 4 Data Register                    |     |

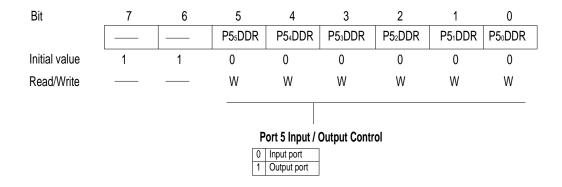

| P5DDR—Port 5 Data Direction Register         |     |

| P5DR—Port 5 Data Register                    |     |

| P6DDR—Port 6 Data Direction Register         |     |

| P6DR—Port 6 Data Register                    |     |

| P7DDR—Port 7 Data Direction Register         |     |

| P7DR—Port 7 Data Register                    |     |

| SYSCR—System Control Register                |     |

| MDCR—Mode Control Register                   |     |

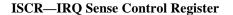

| ISCR—IRQ Sense Control Register              |     |

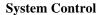

| IER—IRQ Enable Register                      |     |

| TCR—Timer Control Register                                                     |     |

|--------------------------------------------------------------------------------|-----|

| TCSR—Timer Control/Status Register                                             |     |

| TCORA—Time Constant Register A                                                 |     |

| TCORB—Time Constant Register B                                                 |     |

| TCNT—Timer Counter                                                             |     |

| TCR—Timer Control Register                                                     |     |

| TCSR—Timer Control/Status Register                                             |     |

| TCORA—Time Constant Register A                                                 |     |

| TCORB—Time Constant Register B                                                 |     |

| TCNT—Timer Counter                                                             |     |

| SMR—Serial Mode Register                                                       |     |

| TDR—Transmit Data Register                                                     |     |

| BRR—Bit Rate Register                                                          |     |

| SCR—Serial Control Register                                                    |     |

| SSR—Serial Status Register                                                     |     |

| RDR—Receive Data Register                                                      |     |

| SMR—Serial Mode Register                                                       |     |

| BRR—Bit Rate Register                                                          |     |

| SCR—Serial Control Register                                                    |     |

| TDR—Transmit Data Register                                                     |     |

| SSR—Serial Status Register                                                     |     |

| RDR—Receive Data Register                                                      |     |

| HCSR—Handshake Control/Status Register                                         |     |

| FNCR—FRT Noise Canceler Control Register                                       |     |

|                                                                                | 202 |

| Appendix C. Pin States                                                         |     |

| C.1 Pin States in Each Mode                                                    |     |

|                                                                                |     |

| Appendix D.<br>Timing of Transition to and Decourse from Handware Standby Mode | 205 |

| Timing of Transition to and Recovery from Hardware Standby Mode                |     |

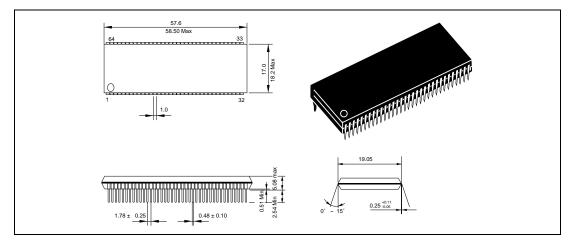

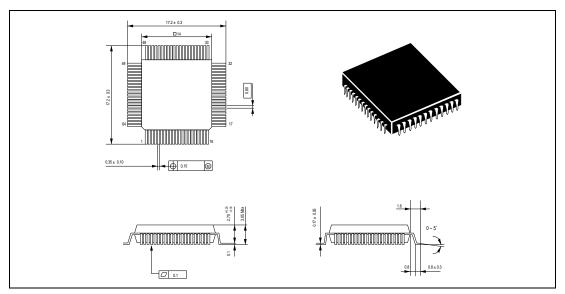

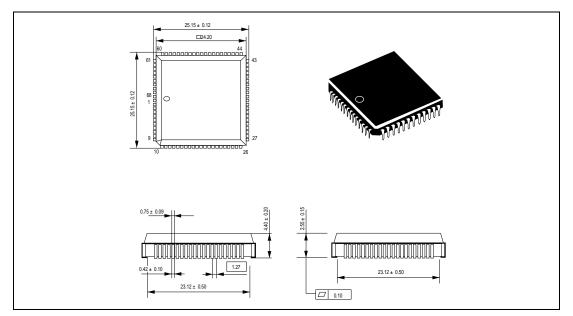

| Appendix E. Package Dimensions                                                 |     |

| r r · · · · · · · · · · · · · · · · · ·                                        |     |

## Preface

The H8/325 Series is a family of high-performance single-chip microcomputers ideally suited for embedded control of industrial equipment. The chips are built around an H8/300 CPU core: a high-speed processor. On-chip supporting modules provides ROM, RAM, two types of timers, I/O ports, and a serial communication interface for easy implementation of compact, high-speed control systems.

The H8/325 Series offers a selection of on-chip memory.

H8/3257: 60-kbyte ROM; 2-kbyte RAM H8/3256: 48-kbyte ROM; 2-kbyte RAM H8/325: 32-kbyte ROM; 1-kbyte RAM H8/324: 24-kbyte ROM; 1-kbyte RAM H8/323: 16-kbyte ROM; 512-byte RAM H8/322: 8-kbyte ROM; 256-byte RAM

The H8/3257, H8/3256, H8/325, H8/323, and H8/322 chips are available with either electrically programmable or mask-programmable ROM. Manufacturers can use the electrically programmable ZTAT<sup>™</sup> (Zero Turn-Around Time\*) version to get production off to a fast start and make software changes quickly, then switch over to the masked version for full-scale production runs.

This manual describes the H8/325 Series hardware. Refer to the *H8/300 Series Programming Manual* for a detailed description of the instruction set.

\* ZTAT is a registered trademark of Hitachi, Ltd.

## Section 1. Overview

#### 1.1 Overview

The H8/325 Series is a series of single-chip microcomputers integrating a CPU core together with a variety of peripheral functions needed in control systems.

The H8/300 CPU is a high-speed processor featuring powerful bit-manipulation instructions, ideally suited for realtime control applications. The on-chip supporting modules include ROM, RAM, two types of timers (16-bit free-running timer and 8-bit timer), a serial communication interface, I/O ports, and a parallel handshaking interface. The on-chip memory sizes of the three chips in the H8/325 Series are:

H8/3257: 60-kbyte ROM; 2-kbyte RAM H8/3256: 48-kbyte ROM; 2-kbyte RAM H8/325: 32-kbyte ROM; 1-kbyte RAM H8/324: 24-kbyte ROM; 1-kbyte RAM H8/323: 16-kbyte ROM; 512-byte RAM H8/322: 8-kbyte ROM; 256-byte RAM

The H8/325 Series can operate in single-chip mode or in two expanded modes, depending on the memory requirements of the application. The operating mode is referred to in this manual as the MCU mode (MCU: MicroComputer Unit).

The H8/3257, H8/3256, H8/325, H8/323, and H8/322 are available in a masked ROM version, or a ZTAT<sup>\*\*\*</sup> version with electrically programmable ROM that can be programmed at the user site.

\* ZTAT is a registered trademark of Hitachi, Ltd.

Table 1-1 lists the features of the H8/325 Series.

| Feature             | Description                                                                        |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------|--|--|--|--|

| CPU                 | General register architecture                                                      |  |  |  |  |

|                     | Eight 16-bit general registers, or                                                 |  |  |  |  |

|                     | Sixteen 8-bit general registers                                                    |  |  |  |  |

|                     | High speed                                                                         |  |  |  |  |

|                     | Maximum clock rate: 10 MHz                                                         |  |  |  |  |

|                     | • Add/subtract: 0.2 µs                                                             |  |  |  |  |

|                     | <ul> <li>Multiply/divide: 1.4 µs</li> </ul>                                        |  |  |  |  |

|                     | Concise, streamlined instruction set                                               |  |  |  |  |

|                     | All instructions are 2 or 4 bytes long                                             |  |  |  |  |

|                     | Register-register arithmetic and logic operations                                  |  |  |  |  |

|                     | Register-memory data transfer by MOV instruction                                   |  |  |  |  |

|                     | Instruction set features                                                           |  |  |  |  |

|                     | • Multiply instruction (8 bits × 8 bits)                                           |  |  |  |  |

|                     | • Divide instruction (16 bits ÷ 8 bits)                                            |  |  |  |  |

|                     | Bit-accumulator instructions                                                       |  |  |  |  |

|                     | Register-indirect specification of bit positions                                   |  |  |  |  |

| Vemory              | H8/3257                                                                            |  |  |  |  |

|                     | ROM: 60 kbytes                                                                     |  |  |  |  |

|                     | RAM: 2 kbytes                                                                      |  |  |  |  |

|                     | H8/3256                                                                            |  |  |  |  |

|                     | ROM: 48 kbytes                                                                     |  |  |  |  |

|                     | RAM: 2 kbytes                                                                      |  |  |  |  |

|                     | H8/325                                                                             |  |  |  |  |

|                     | ROM: 32 kbytes                                                                     |  |  |  |  |

|                     | RAM: 1 kbyte                                                                       |  |  |  |  |

|                     | H8/324                                                                             |  |  |  |  |

|                     | ROM: 24 kbytes                                                                     |  |  |  |  |

|                     | RAM: 1 kbyte                                                                       |  |  |  |  |

|                     | H8/323                                                                             |  |  |  |  |

|                     | ROM: 16 kbytes                                                                     |  |  |  |  |

|                     | RAM: 512 bytes                                                                     |  |  |  |  |

|                     | H8/322                                                                             |  |  |  |  |

|                     | ROM: 8 kbytes                                                                      |  |  |  |  |

|                     | RAM: 256 bytes                                                                     |  |  |  |  |

| 16-Bit free-running | One 16-bit free-running counter (also usable for external event counting)          |  |  |  |  |

| imer module         | Two compare outputs                                                                |  |  |  |  |

| (FRT: 1 channel)    | One capture input                                                                  |  |  |  |  |

| 3-Bit timer module  | Each channel has:                                                                  |  |  |  |  |

|                     |                                                                                    |  |  |  |  |

| 2 channels)         | <ul> <li>One 8-bit up-counter (also usable for external event counting)</li> </ul> |  |  |  |  |

#### Table 1-1. Features

| Table 1-1. | Features | (cont.) |

|------------|----------|---------|

|------------|----------|---------|

| Feature                             | Description                                                      |                                                    |                                       |        |  |

|-------------------------------------|------------------------------------------------------------------|----------------------------------------------------|---------------------------------------|--------|--|

| Serial communi-                     | Selection of asynchronous and synchronous modes                  |                                                    |                                       |        |  |

| cation interface                    | Simultaneous transmit and receive (full duplex operation)        |                                                    |                                       |        |  |

| (SCI: 2 channels)                   | On-chip baud ra                                                  | ate generator                                      |                                       |        |  |

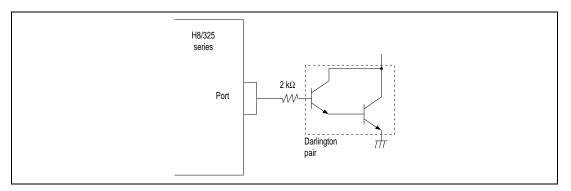

| I/O ports                           | 53 input/output pins (of which 16 can drive large current loads) |                                                    |                                       |        |  |

|                                     | All input pins ha                                                | ave programmable inpu                              | t pull-ups                            |        |  |

| Parallel hand-<br>shaking interface | Built-in parallel handshaking is available at port 3             |                                                    |                                       |        |  |

| Interrupts                          | Four external in                                                 | nterrupt pins: $\overline{NMI}$ , $\overline{IRQ}$ | $$ to $\overline{IRQ}_{\overline{2}}$ |        |  |

|                                     | Seventeen on-                                                    | chip interrupt sources                             |                                       |        |  |

| Operating modes                     | Mode 1: expansion                                                | ded mode with on-chip                              | ROM disabled                          |        |  |

|                                     | Mode 2: expansion                                                | ded mode with on-chip                              | ROM enabled                           |        |  |

|                                     | Mode 3: single-                                                  | chip mode                                          |                                       |        |  |

| Power-down                          | Sleep mode                                                       |                                                    |                                       |        |  |

| state                               | Software standby mode                                            |                                                    |                                       |        |  |

|                                     | Hardware standby mode                                            |                                                    |                                       |        |  |

| Other features                      | On-chip clock oscillator                                         |                                                    |                                       |        |  |

|                                     | E clock output                                                   |                                                    |                                       |        |  |

| Product lineup                      | Type code<br>(5V series)                                         | Type code<br>(3V series)                           | Package                               | ROM    |  |

|                                     | HD6473257C                                                       | HD6473257VC                                        | 64-Pin windowed shrink<br>DIP(DC-64S) | PROM   |  |

|                                     | HD6473257P                                                       | HD6473257VP                                        | 64-Pin shrink DIP (DP-64S)            |        |  |

|                                     | HD6473257F                                                       | HD6473257VF                                        | 64-Pin QFP (FP-64A)                   |        |  |

|                                     | HD6473257CP                                                      | HD6473257VCP                                       | 68-Pin PLCC (CP-68)                   |        |  |

|                                     | HD6433257P                                                       | HD6433257VP                                        | 64-Pin shrink DIP (DP-64S)            | Masked |  |

|                                     | HD6433257F                                                       | HD6433257VF                                        | 64-Pin QFP (FP-64A)                   | ROM    |  |

|                                     | HD6433257CP                                                      | HD6433257VCP                                       | 68-Pin PLCC (CP-68)                   |        |  |

|                                     | HD6473256P                                                       | HD6473256VP                                        | 64-Pin shrink DIP (DP-64S)            | PROM   |  |

|                                     | HD6473256F                                                       | HD6473256VF                                        | 64-Pin QFP (FP-64A)                   |        |  |

|                                     | HD6473256CP                                                      | HD6473256VCP                                       | 68-Pin PLCC (CP-68)                   |        |  |

|                                     | HD6433256P                                                       | HD6433256VP                                        | 64-Pin shrink DIP (DP-64S)            | Masked |  |

|                                     | 11201002001                                                      |                                                    |                                       |        |  |

|                                     | HD6433256F                                                       | HD6433256VF                                        | 64-Pin QFP (FP-64A)                   | ROM    |  |

### Table 1-1. Features (cont.)

| Feature                | Description                             |                          |                                                                          |            |

|------------------------|-----------------------------------------|--------------------------|--------------------------------------------------------------------------|------------|

| Product lineup (cont.) | Type code (5V<br>series)                | Type code<br>(3V series) | Package                                                                  | ROM        |

|                        | HD6473258C                              |                          | 64-Pin windowed shrink<br>DIP(DC-64S)                                    | PROM       |

|                        | HD6473258P                              |                          | 64-Pin shrink DIP (DP-64S)                                               |            |

|                        | HD6473258F                              |                          | 64-Pin QFP (FP-64A)                                                      |            |

|                        | HD6473258CP                             |                          | 68-Pin PLCC (CP-68)                                                      |            |

|                        | HD6433258P<br>HD6433258F<br>HD6433258CP |                          | 64-Pin shrink DIP (DP-64S)<br>64-Pin QFP (FP-64A)<br>68-Pin PLCC (CP-68) | Masked ROM |

|                        | HD6413258P<br>HD6413258F<br>HD6413258CP |                          | 64-Pin shrink DIP (DP-64S)<br>64-Pin QFP (FP-64A)<br>68-Pin PLCC (CP-68) | No ROM     |

|                        | HD6433248P<br>HD6433248F<br>HD6433248CP |                          | 64-Pin shrink DIP (DP-64S)<br>64-Pin QFP (FP-64A)<br>68-Pin PLCC (CP-68) | Masked ROM |

|                        | HD6473238P<br>HD6473238F<br>HD6473238CP |                          | 64-Pin shrink DIP (DP-64S)<br>64-Pin QFP (FP-64A)<br>68-Pin PLCC (CP-68) | PROM       |

|                        | HD6433238P<br>HD6433238F<br>HD6433238CP |                          | 64-Pin shrink DIP (DP-64S)<br>64-Pin QFP (FP-64A)<br>68-Pin PLCC (CP-68) | Masked ROM |

|                        | HD6413238P<br>HD6413238F<br>HD6413238CP |                          | 64-Pin shrink DIP (DP-64S)<br>64-Pin QFP (FP-64A)<br>68-Pin PLCC (CP-68) | No ROM     |

|                        | HD6473228P<br>HD6473228F<br>HD6473228CP |                          | 64-Pin shrink DIP (DP-64S)<br>64-Pin QFP (FP-64A)<br>68-Pin PLCC (CP-68) | PROM       |

|                        | HD6433228P<br>HD6433228F<br>HD6433228CP |                          | 64-Pin shrink DIP (DP-64S)<br>64-Pin QFP (FP-64A)<br>68-Pin PLCC (CP-68) | Masked ROM |

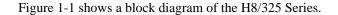

## 1.2 Block Diagram

Figure 1-1. Block Diagram

## **1.3 Pin Assignments and Functions**

#### 1.3.1 Pin Arrangement

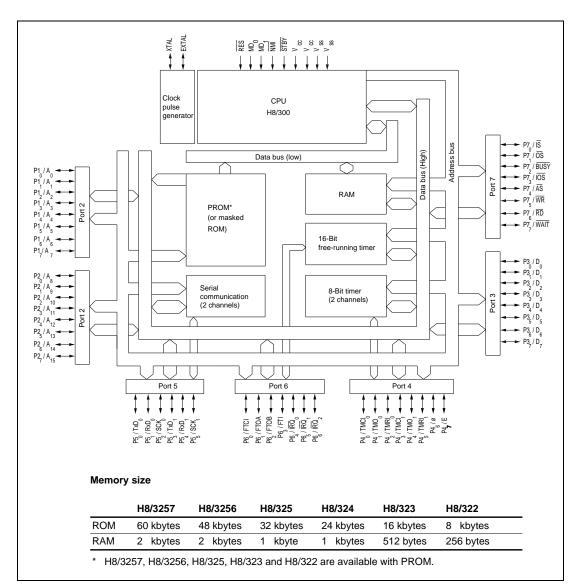

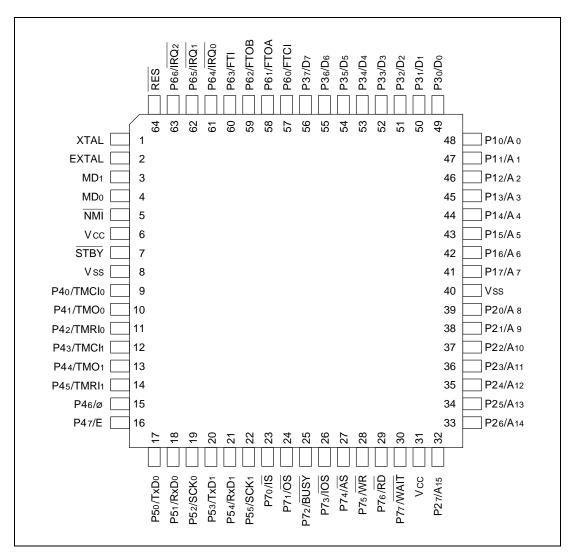

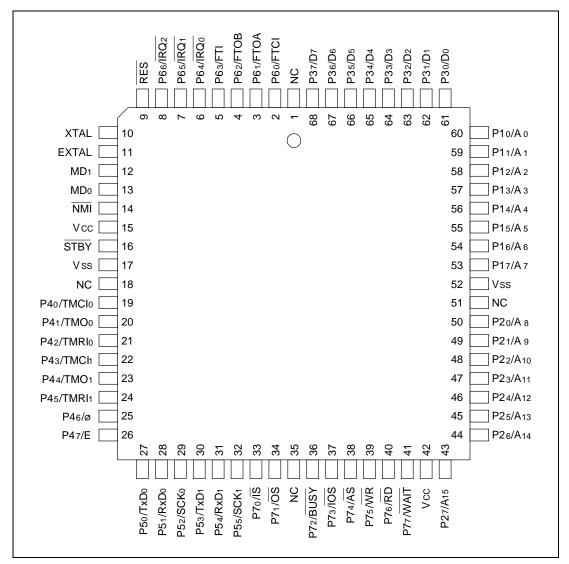

Figure 1-2 shows the pin arrangement of the H8/325 Series in the DC-64S and DP-64S packages. Figure 1-3 shows the pin arrangement in the FP-64A package. Figure 1-4 shows the pin arrangement in the CP-68 package.

| P60/FTCI 1 〇       | 64 P37/D7   |

|--------------------|-------------|

| P61/FTOA 2         | 63 P36/D6   |

| P62/FTOB 3         | 62 P35/D5   |

| P63/FTI 4          | 61 P34/D4   |

| P64/IRQ0 5         | 60 P33/D3   |

| P65/IRQ1 6         | 59 P32/D2   |

| P6 6/IRQ 2 7       | 58 P31/D1   |

| RES 8              | 57 P30/D0   |

| XTAL 9             | 56 P10/A0   |

| EXTAL 🛄 10         | 55 P11/A1   |

| MD1 11             | 54 P12/A2   |

| MD <sub>0</sub> 12 | 53 P13/A3   |

| NMI [ 13           | 52 P14/A4   |

| Vcc 14             | 51 P15/A5   |

| STBY 15            | 50 P16/A6   |

| Vss 16             | 49 P17/A7   |

| P4 0/TMCI0 17      | 48 🔛 Vss    |

| P41/TMO0 18        | 47 P20/A8   |

| P42/TMRI0 19       | 46 P21/A9   |

| P43/TMCl1 20       | 45 P22/A10  |

| P44/TMO1 21        | 44 P23/A11  |

| P45/TMRI1 22       | 43 P24/A12  |

| P46/ø 23           | 42 P25/A13  |

| P47/E 24           | 41 P26/A14  |

| P5 ₀/TxD₀ 25       | 40 P27/A15  |

| P51/RxD0 26        | 39 🔛 Vcc    |

| P52/SCK0 27        | 38 P77/WAIT |

| P53/TxD1 28        | 37 P76/RD   |

| P54/RxD1 29        | 36 P75/WR   |

| P55/SCK1 30        | 35 P74/AS   |

| P70/IS 31          | 34 P73/IOS  |

| P71/OS 32          | 33 P72/BUSY |

|                    | ]           |

Figure 1-2. Pin Arrangement (DC-64S, DP-64S, Top View)

Figure 1-3. Pin Arrangement (FP-64A, Top View)

• PLCC-68

Figure 1-4. Pin Arrangement (CP-68, Top View)

#### **1.3.2** Pin Functions

(1) Pin Assignments in Each Operating Mode: Table 1-2 lists the assignments of the pins of the DC-64S, DP-64S, FP-64A, and CP-68 packages in each operating mode.

| Pin no.          |        | Expan | Expanded modes                     |                                    |                                    |                 |

|------------------|--------|-------|------------------------------------|------------------------------------|------------------------------------|-----------------|

| DC-64S<br>DP-64S | FP-64A | CP-68 | Mode 1                             | Mode 2                             | Mode 3                             | PROM<br>mode    |

|                  | _      | 1     | NC                                 | NC                                 | NC                                 | NC              |

| 1                | 57     | 2     | P6 <sub>0</sub> /FTCI              | P6₀/FTCI                           | P6₀/FTCI                           | NC              |

| 2                | 58     | 3     | P6₁/FTOA                           | P6 <sub>1</sub> /FTOA              | P6₁/FTOA                           | NC              |

| 3                | 59     | 4     | P6 <sub>2</sub> /FTOB              | P6 <sub>2</sub> /FTOB              | P6 <sub>2</sub> /FTOB              | NC              |

| 4                | 60     | 5     | P6₃/FTI                            | P6 <sub>3</sub> /FTI               | P6₃/FTI                            | NC              |

| 5                | 61     | 6     | P6₄/IRQ₀                           | P6₄/ĪRQ <sub>0</sub>               | P6₄/IRQ₀                           | NC              |

| 6                | 62     | 7     | P6₅/IRQ₁                           | P6₅/IRQ <sub>1</sub>               | P6₅/IRQ <sub>1</sub>               | NC              |

| 7                | 63     | 8     | P6 <sub>6</sub> /IRQ <sub>2</sub>  | P6 <sub>6</sub> /IRQ <sub>2</sub>  | P6 <sub>6</sub> /IRQ <sub>2</sub>  | NC              |

| 8                | 64     | 9     | RES                                | RES                                | RES                                | V <sub>PP</sub> |

| 9                | 1      | 10    | XTAL                               | XTAL                               | XTAL                               | NC              |

| 10               | 2      | 11    | EXTAL                              | EXTAL                              | EXTAL                              | NC              |

| 11               | 3      | 12    | MD <sub>1</sub>                    | MD <sub>1</sub>                    | MD <sub>1</sub>                    | V <sub>ss</sub> |

| 12               | 4      | 13    | MD <sub>0</sub>                    | MD <sub>o</sub>                    | MD <sub>o</sub>                    | V <sub>ss</sub> |

| 13               | 5      | 14    | NMI                                | NMI                                | NMI                                | EA <sub>9</sub> |

| 14               | 6      | 15    | V <sub>cc</sub>                    | V <sub>cc</sub>                    | V <sub>cc</sub>                    | V <sub>cc</sub> |

| 15               | 7      | 16    | STBY                               | STBY                               | STBY                               | V <sub>ss</sub> |

| 16               | 8      | 17    | V <sub>ss</sub>                    | V <sub>ss</sub>                    | V <sub>ss</sub>                    | V <sub>ss</sub> |

| _                | _      | 18    | NC                                 | NC                                 | NC                                 | NC              |

| 17               | 9      | 19    | P4 <sub>0</sub> /TMCI <sub>0</sub> | P4 <sub>0</sub> /TMCI <sub>0</sub> | P4 <sub>0</sub> /TMCI <sub>0</sub> | EO₀             |

| 18               | 10     | 20    | P4 <sub>1</sub> /TMO <sub>0</sub>  | P4 <sub>1</sub> /TMO <sub>0</sub>  | P4 <sub>1</sub> /TMO <sub>0</sub>  | EO <sub>1</sub> |

| 19               | 11     | 21    | P4 <sub>2</sub> /TMRI <sub>0</sub> | P4 <sub>2</sub> /TMRI <sub>0</sub> | P4 <sub>2</sub> /TMRI <sub>0</sub> | EO <sub>2</sub> |

| 20               | 12     | 22    | P4 <sub>3</sub> /TMCI <sub>1</sub> | P4 <sub>3</sub> /TMCI <sub>1</sub> | P4 <sub>3</sub> /TMCI <sub>1</sub> | $EO_3$          |

| 21               | 13     | 23    | P4 <sub>4</sub> /TMO <sub>1</sub>  | P4 <sub>4</sub> /TMO <sub>1</sub>  | P4 <sub>4</sub> /TMO <sub>1</sub>  | $EO_4$          |

| 22               | 14     | 24    | P4 <sub>5</sub> /TMRI <sub>1</sub> | P4 <sub>5</sub> /TMRI <sub>1</sub> | P4 <sub>5</sub> /TMRI <sub>1</sub> | EO₅             |

| 23               | 15     | 25    | φ                                  | φ                                  | P4 <sub>6</sub> /φ                 | $EO_6$          |

| 24               | 16     | 26    | P4 <sub>7</sub> /E                 | P4 <sub>7</sub> /E                 | P4 <sub>7</sub>                    | EO <sub>7</sub> |

| 25               | 17     | 27    | P5 <sub>0</sub> /TxD <sub>0</sub>  | P5 <sub>0</sub> /TxD <sub>0</sub>  | P5₀/TxD₀                           | NC              |

| 26               | 18     | 28    | P5 <sub>1</sub> /RxD <sub>0</sub>  | P5 <sub>1</sub> /RxD <sub>0</sub>  | P5₁/RxD₀                           | NC              |

| 27               | 19     | 29    | P5 <sub>2</sub> /SCK <sub>0</sub>  | P5 <sub>2</sub> /SCK <sub>0</sub>  | P5 <sub>2</sub> /SCK <sub>0</sub>  | NC              |

Table 1-2. Pin Assignments in Each Operating Mode (1)

Notes: 1. Pins marked NC should be left unconnected.

2. The PROM mode is a non-operating mode used for programming the on-chip ROM. See section 11, ROM for details.

| Pin no.          |        |       | Expand                            | ed modes                          | Single-chip mode                  |                  |

|------------------|--------|-------|-----------------------------------|-----------------------------------|-----------------------------------|------------------|

| DC-64S<br>DP-64S | FP-64A | CP-68 | Mode 1                            | Mode 2                            | Mode 3                            | PROM<br>mode     |

| 28               | 20     | 30    | P5 <sub>3</sub> /TxD <sub>1</sub> | P5 <sub>3</sub> /TxD <sub>1</sub> | P5 <sub>3</sub> /TxD <sub>1</sub> | NC               |

| 29               | 21     | 31    | P5 <sub>4</sub> /RxD <sub>1</sub> | P5 <sub>4</sub> /RxD <sub>1</sub> | P5 <sub>4</sub> /RxD <sub>1</sub> | NC               |

| 30               | 22     | 32    | P5 <sub>5</sub> /SCK <sub>1</sub> | P5 <sub>5</sub> /SCK <sub>1</sub> | P5 <sub>5</sub> /SCK <sub>1</sub> | NC               |

| 31               | 23     | 33    | P7 <sub>0</sub> /IS               | P7 <sub>0</sub> /IS               | P7 <sub>0</sub> /IS               | V <sub>cc</sub>  |

| 32               | 24     | 34    | P7 <sub>1</sub>                   | P7 <sub>1</sub>                   | P7,/OS                            | V <sub>cc</sub>  |

| _                | _      | 35    | NC                                | NC                                | NC                                | NC               |

| 33               | 25     | 36    | P7 <sub>2</sub>                   | P7 <sub>2</sub>                   | P7 <sub>2</sub> /BUSY             | NC               |

| 34               | 26     | 37    | P7 <sub>3</sub> /IOS              | P7 <sub>3</sub> /IOS              | P7 <sub>3</sub>                   | NC               |

| 35               | 27     | 38    | ĀS                                | ĀS                                | P7,                               | NC               |

| 36               | 28     | 39    | WR                                | WR                                | P7 <sub>5</sub>                   | NC               |

| 37               | 29     | 40    | RD                                | RD                                | P7 <sub>6</sub>                   | NC               |

| 38               | 30     | 41    | WAIT                              | WAIT                              | P7,                               | NC               |

| 39               | 31     | 42    | V <sub>cc</sub>                   | V <sub>cc</sub>                   | V <sub>cc</sub>                   | V <sub>cc</sub>  |

| 40               | 32     | 43    | A <sub>15</sub>                   | P2 <sub>7</sub> /A <sub>15</sub>  | P2,                               | CE               |

| 41               | 33     | 44    | A <sub>14</sub>                   | P2 <sub>6</sub> /A <sub>14</sub>  | P2 <sub>6</sub>                   | EA <sub>14</sub> |

| 42               | 34     | 45    | A <sub>13</sub>                   | P2 <sub>5</sub> /A <sub>13</sub>  | P2 <sub>5</sub>                   | EA <sub>13</sub> |

| 43               | 35     | 46    | A <sub>12</sub>                   | P2 <sub>4</sub> /A <sub>12</sub>  | P2 <sub>4</sub>                   | EA <sub>12</sub> |

| 44               | 36     | 47    | A <sub>11</sub>                   | P2 <sub>3</sub> /A <sub>11</sub>  | P2 <sub>3</sub>                   | EA <sub>11</sub> |

| 45               | 37     | 48    | A <sub>10</sub>                   | P2 <sub>2</sub> /A <sub>10</sub>  | P2 <sub>2</sub>                   | EA <sub>10</sub> |

| 46               | 38     | 49    | A <sub>9</sub>                    | P2 <sub>1</sub> /A <sub>9</sub>   | P2,                               | OE               |

| 47               | 39     | 50    | A <sub>8</sub>                    | P2 <sub>0</sub> /A <sub>8</sub>   | P2 <sub>0</sub>                   | EA <sub>8</sub>  |

|                  | _      | 51    | NC                                | NC                                | NC                                | NC               |

| 48               | 40     | 52    | V <sub>ss</sub>                   | V <sub>ss</sub>                   | V <sub>ss</sub>                   | V <sub>ss</sub>  |

| 49               | 41     | 53    | A <sub>7</sub>                    | P1 <sub>7</sub> /A <sub>7</sub>   | P1 <sub>7</sub>                   | EA <sub>7</sub>  |

| 50               | 42     | 54    | A <sub>6</sub>                    | P1 <sub>6</sub> /A <sub>6</sub>   | P1 <sub>6</sub>                   | EA <sub>6</sub>  |

| 51               | 43     | 55    | A <sub>5</sub>                    | P1 <sub>5</sub> /A <sub>5</sub>   | P1 <sub>5</sub>                   | EA <sub>5</sub>  |

| 52               | 44     | 56    | A <sub>4</sub>                    | P1 <sub>4</sub> /A <sub>4</sub>   | P1 <sub>4</sub>                   | EA <sub>4</sub>  |

| 53               | 45     | 57    | A <sub>3</sub>                    | P1 <sub>3</sub> /A3               | P1 <sub>3</sub>                   | EA <sub>3</sub>  |

| 54               | 46     | 58    | A <sub>2</sub>                    | P1 <sub>2</sub> /A2               | P1 <sub>2</sub>                   | EA <sub>2</sub>  |

| Table 1-2. | <b>Pin Assignments</b> | in Each C | <b>Operating Mode (</b> | 1) |

|------------|------------------------|-----------|-------------------------|----|

|            |                        |           |                         |    |

**Notes:** 1. Pins marked NC should be left unconnected.

2. The PROM mode is a non-operating mode used for programming the on-chip ROM. See section 11, ROM for details.

|                  | Pin no. |              | E              | Expanded modes                  | Single-chip mode |                 |

|------------------|---------|--------------|----------------|---------------------------------|------------------|-----------------|

| DC-64S<br>DP-64S | FP-64A  | CP-68 Mode 1 |                | Mode 2                          | Mode 3           | PROM<br>mode    |

| 55               | 47      | 59           | A <sub>1</sub> | P1 <sub>1</sub> /A <sub>1</sub> | P1 <sub>1</sub>  | EA <sub>1</sub> |

| 56               | 48      | 60           | A <sub>0</sub> | P1 <sub>0</sub> /A <sub>0</sub> | P1 <sub>0</sub>  | EA <sub>0</sub> |

| 57               | 49      | 61           | D <sub>0</sub> | D <sub>o</sub>                  | P3 <sub>0</sub>  | NC              |

| 58               | 50      | 62           | D <sub>1</sub> | D <sub>1</sub>                  | P3 <sub>1</sub>  | NC              |

| 59               | 51      | 63           | D <sub>2</sub> | $D_2$                           | P3 <sub>2</sub>  | NC              |

| 60               | 52      | 64           | D <sub>3</sub> | D <sub>3</sub>                  | P3 <sub>3</sub>  | NC              |

| 61               | 53      | 65           | $D_4$          | $D_4$                           | P3 <sub>4</sub>  | NC              |

| 62               | 54      | 66           | D <sub>5</sub> | D <sub>5</sub>                  | P3 <sub>5</sub>  | NC              |

| 63               | 55      | 67           | D <sub>6</sub> | $D_6$                           | P3 <sub>6</sub>  | NC              |

| 64               | 56      | 68           | D <sub>7</sub> | D <sub>7</sub>                  | P3 <sub>7</sub>  | NC              |

|                  |         |              |                |                                 |                  |                 |

| Table 1-2. | Pin Assignmen       | ts in Each | Operating | Mode (1 | 1) |

|------------|---------------------|------------|-----------|---------|----|

| I UDIC I A | I III TROOLEIIIIICH | is m Luch  | Operating | mulue ( | -, |

**Notes:** 1. Pins marked NC should be left unconnected.

2. The PROM mode is a non-operating mode used for programming the on-chip ROM. See section 11, ROM for details.

| (2) Pin Functions: Table 1-3 gives a concise description of the function of each pin | 1. |

|--------------------------------------------------------------------------------------|----|

| Table 1-3. Pin Functions (1)                                                         |    |

| Туре           | Symbol            | I/O Name and function |                                                                                                                                                                                                                                                                         |  |  |

|----------------|-------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Power          | V <sub>cc</sub>   | I                     | <b>Power:</b> Connected to the power supply (+5 V or +3 V).<br>Connect both $V_{cc}$ pins to the system power supply (+5 V or +3 V).                                                                                                                                    |  |  |

|                | V <sub>ss</sub>   | I                     | <b>Ground:</b> Connected to ground (0 V). Connect both VSS pins to the system power supply (0 V).                                                                                                                                                                       |  |  |

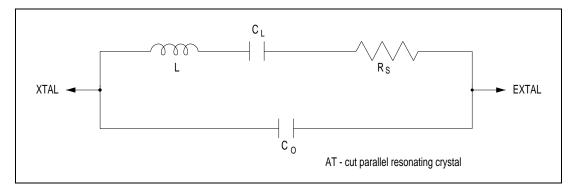

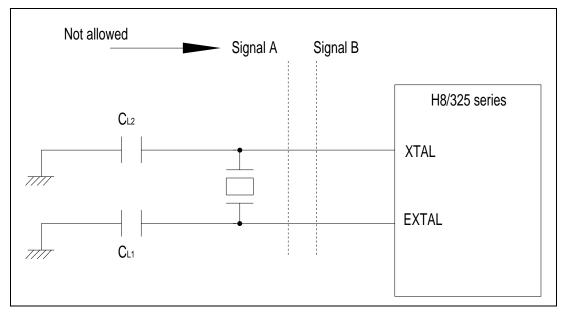

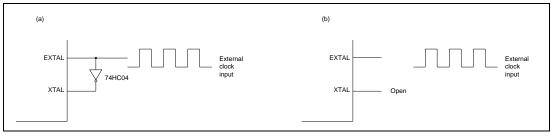

| Clock          | XTAL              | I                     | <b>Crystal:</b> Connected to a crystal oscillator. The crystal frequency must be double the desired system clock frequency. If an external clock is input at the EXTAL pin, a reverse-phase clock should be input at the XTAL pin.                                      |  |  |

|                | EXTAL             | I                     | <b>External crystal:</b> Connected to a crystal oscillator or external clock. The frequency of the external clock must be double the desired system clock frequency. See section 14, Clock Pulse Generator for examples of connections to a crystal and external clock. |  |  |

|                | φ                 | 0                     | System clock: Supplies the system clock to peripheral devices                                                                                                                                                                                                           |  |  |

|                | E                 | 0                     | Enable clock: Supplies an E clock to peripheral devices.                                                                                                                                                                                                                |  |  |

| System         | RES               | I                     | Reset: A low input causes the chip to reset.                                                                                                                                                                                                                            |  |  |

| control        | STBY              | I                     | <b>Standby:</b> A transition to the hardware standby mode (a power-<br>down state) occurs when a low input is received at the STBY<br>pin.                                                                                                                              |  |  |

| Address<br>bus | $A_{15}$ to $A_0$ | 0                     | Address bus: Address output pins.                                                                                                                                                                                                                                       |  |  |

| Data bus       | $D_7$ to $D_0$    | I/O                   | Data bus: 8-Bit bidirectional data bus.                                                                                                                                                                                                                                 |  |  |

| Bus<br>control | WAIT              | I                     | <b>Wait:</b> Requests the CPU to insert TW states into the bus cycle when an off-chip address is accessed.                                                                                                                                                              |  |  |

|                | RD                | 0                     | Read: Goes low to indicate that the CPU is reading an external address                                                                                                                                                                                                  |  |  |

|                | WR                | 0                     | Write: Goes low to indicate that the CPU is writing to an external address                                                                                                                                                                                              |  |  |

|                | ĀS                | 0                     | Address Strobe: Goes low to indicate that there is a valid address on the address bus                                                                                                                                                                                   |  |  |

### Table 1-3. Pin Functions (2)

| Туре                             | Symbol                                                                   | I/O | Name and function                                                                                                                                                                                                                      |                                                                                                        |                |                                                              |  |  |

|----------------------------------|--------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------|--|--|

| Bus control                      | ĪOS                                                                      | 0   | <b>I/O Select:</b> Goes low when the CPU accesses addresses H'FF00 to H'FFFF in expanded mode. Can be used as a chip select signal replacing the upper 8 bits of the address bus when external devices are mapped onto high addresses. |                                                                                                        |                |                                                              |  |  |

| Interrupt<br>signals             | NMI                                                                      | I   | <b>NonMaskable Interrupt:</b> Highest-priority interrupt request. The NMIEG bit in the system control register determines whether the interrupt is requested on the rising or falling edge of the $\overline{\text{NMI}}$ input.       |                                                                                                        |                |                                                              |  |  |

|                                  | $\frac{\overline{IRQ}_{\overline{0}}}{\overline{IRQ}_{\overline{2}}}$ to | I   | Interrupt Request 0 to 2: Maskable interrupt request pins.                                                                                                                                                                             |                                                                                                        |                |                                                              |  |  |

| Operating<br>mode<br>control     | MD <sub>1</sub> ,<br>MD <sub>0</sub>                                     | I   | <b>Mode:</b> Input pins for setting the MCU operating mode according to the table below.                                                                                                                                               |                                                                                                        |                |                                                              |  |  |

|                                  |                                                                          |     | MD1                                                                                                                                                                                                                                    | MD0                                                                                                    | Mode           | Description                                                  |  |  |

|                                  |                                                                          |     | 0                                                                                                                                                                                                                                      | 1                                                                                                      | Mode 1         | Expanded mode with on-chip ROM disabled                      |  |  |

|                                  |                                                                          |     | 1                                                                                                                                                                                                                                      | 0                                                                                                      | Mode 2         | Expanded mode with on-chip ROM enabled                       |  |  |

|                                  |                                                                          |     | 1                                                                                                                                                                                                                                      | 1                                                                                                      | Mode 3         | Single-chip mode                                             |  |  |

|                                  |                                                                          |     | (MDS1 ar                                                                                                                                                                                                                               |                                                                                                        | of the mode co | d in mode select bits 1 to 0<br>ntrol register (MDCR) on the |  |  |

| 16-Bit free-<br>running<br>timer | FTCI                                                                     | I   | <b>FRT counter Clock Input:</b> Input pin for an external clock signal for the free-running timer.                                                                                                                                     |                                                                                                        |                |                                                              |  |  |

|                                  | FTOA,<br>FTOB                                                            | 0   | FRT Output compare A and B: Output pins controlled by comparators A and B of the free-running timer.                                                                                                                                   |                                                                                                        |                |                                                              |  |  |

|                                  | FTI                                                                      | I   | FRT Inpu                                                                                                                                                                                                                               | it capture:                                                                                            | Input capture  | oin for the free-running timer.                              |  |  |

| 8-Bit timer                      | TMO <sub>0</sub> ,<br>TMO <sub>1</sub>                                   | 0   | 8-bit TiMer Output (channels 0 and 1): Compare-match ou<br>pins for the 8-bit timers.                                                                                                                                                  |                                                                                                        |                |                                                              |  |  |

|                                  | TMCI <sub>0</sub> ,<br>TMCI <sub>1</sub>                                 | I   |                                                                                                                                                                                                                                        | 8-bit TiMer Clock Input (channels 0 and 1):<br>External clock input pins for the 8-bit timer counters. |                |                                                              |  |  |

|                                  | TMRI₀,<br>TMRI₁                                                          | I   |                                                                                                                                                                                                                                        | <b>er Reset Ir</b><br>ts the 8-bit                                                                     | • •            | s 0 and 1): High input at these                              |  |  |

| Туре                                   | Symbol                               | I/O | Name and function                                                                                                                                                                                   |

|----------------------------------------|--------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial com-<br>munication<br>interface | TxD <sub>0</sub><br>TxD <sub>1</sub> | 0   | <b>Serial Transmit Data (channels 0 and 1):</b> Data output pins for the serial communication interface.                                                                                            |

|                                        | RxD <sub>0</sub><br>RxD <sub>1</sub> | I   | Serial Receive Data (channels 0 and 1): Data input pins for the serial communication interface.                                                                                                     |

|                                        | SCK₀<br>SCK₁                         | I/O | Serial ClocK (channels 0 and 1): Input/output pins for the serial clock signals.                                                                                                                    |

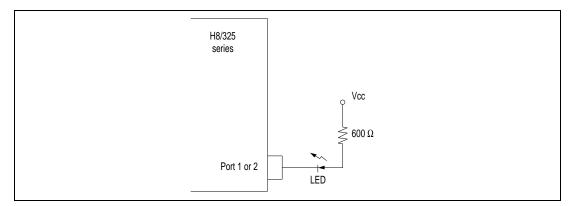

| General-<br>purpose I/O                | P1 <sub>7</sub> to P1 <sub>0</sub>   | I/O | <b>Port 1:</b> An 8-bit input/output port with programmable MOS input pull-ups and LED driving capability. The direction of each bit can be selected in the port 1 data direction register (P1DDR). |

|                                        | $P2_7$ to $P2_0$                     | I/O | <b>Port 2:</b> An 8-bit input/output port with programmable MOS input pull-ups and LED driving capability. The direction of each bit can be selected in the port 2 data direction register (P2DDR). |

|                                        | P3 <sub>7</sub> to P3 <sub>0</sub>   | I/O | <b>Port 3:</b> An 8-bit input/output port with programmable MOS input pull-ups. The direction of each bit can be selected in the port 3 data direction register (P3DDR).                            |

|                                        | $P4_7$ to $P4_0$                     | I/O | <b>Port 4:</b> An 8-bit input/output port with programmable MOS input pull-ups. The direction of each bit (except P46) can be selected in the port 4 data direction register (P4DDR).               |

|                                        | $P5_{5}$ to $P5_{0}$                 | I/O | <b>Port 5:</b> A 6-bit input/output port with programmable MOS input pull-ups. The direction of each bit can be selected in the port 5 data direction register (P5DDR).                             |

|                                        | P6 <sub>6</sub> to P6 <sub>0</sub>   | I/O | <b>Port 6:</b> A 7-bit input/output port with programmable MOS input pull-ups. The direction of each bit can be selected in the port 6 data direction register (P6DDR).                             |

|                                        | $P7_7$ to $P7_0$                     | I/O | <b>Port 7:</b> An 8-bit input/output port with programmable MOS input pull-ups. The direction of each bit can be selected in the port 7 data direction register (P7DDR).                            |

| Parallel hand-<br>shaking interface    | $P3_7$ to $P3_0$                     | I/O | <b>Data Input/Output:</b> Data input/output pins for the parallel handshaking interface.                                                                                                            |

|                                        | ĪS                                   | l   | <b>Input Strobe:</b> Strobe input signal from an external device.                                                                                                                                   |

|                                        | OS                                   | 0   | <b>Output Strobe:</b> Strobe output signal to an external device.                                                                                                                                   |

|                                        | BUSY                                 | 0   | <b>Busy:</b> Notifies an external device that the H8/325 Series chip is not ready to receive data.                                                                                                  |

#### Table 1-3. Pin Functions (3)

# Section 2. MCU Operating Modes and Address Space

### 2.1 Overview

The H8/325 Series operates in three modes numbered 1, 2, and 3. An additional non-operating mode (mode 0) is used for programming the PROM version of the H8/325. The mode is selected by the inputs at the mode pins ( $MD_1$  and  $MD_0$ ) at the instant when the chip comes out of a reset. As indicated in table 2-1, the mode determines the size of the address space and the usage of on-chip ROM and on-chip RAM. The ROMless versions (HD6413258, HD6413238) are used only in mode 1 (expanded mode with on-chip ROM disabled).

| MD1  | MD0  | Mode   | Address space | On-chip ROM | On-chip RAM |

|------|------|--------|---------------|-------------|-------------|

| Low  | Low  | Mode 0 | —             | —           | _           |

| Low  | High | Mode 1 | Expanded      | Disabled    | Enabled*    |

| High | Low  | Mode 2 | Expanded      | Enabled     | Enabled*    |

| High | High | Mode 3 | Single-chip   | Enabled     | Enabled     |

\* If the RAME bit in the system control register (SYSCR) is cleared to 0, off-chip memory can be accessed instead.

Modes 1 and 2 are expanded modes that permit access to off-chip memory and peripheral devices. The maximum address space supported by these externally expanded modes is 64 kbytes.

In mode 3 (single-chip mode), only on-chip ROM and RAM and the on-chip register field are used. All ports are available for general-purpose input and output.

Mode 0 is inoperative in the H8/325 Series. Avoid setting the mode pins to mode 0.

#### 2.2 Mode Descriptions

**Mode 1 (Expanded Mode without On-Chip ROM):** Mode 1 supports a 64-kbyte address space most of which is off-chip. In particular, the interrupt vector table is located in off-chip memory. The on-chip ROM is not used. Software can select whether to use the on-chip RAM. Ports 1, 2, 3 and 7 are used for the address and data bus lines and control signals as follows:

Ports 1 and 2:Address busPort 3:Data busPort 7 (partly):Bus control signals

**Mode 2** (Expanded Mode with On-Chip ROM): Mode 2 supports a 64-kbyte address space which includes the on-chip ROM. Software can select whether or not to use the on-chip RAM, and can select the usage of pins in ports 1 and 2.

Ports 1 and 2: Address bus (see note)

Port 3: Data bus

Port 7 (partly): Bus control signals

**Note:** In mode 2, ports 1 and 2 are initially general-purpose input ports. Software must change the desired pins to output before using them for the address bus. See section 5, I/O Ports for details.

**Mode 3 (Single-Chip Mode):** In this mode all memory is on-chip. Since no off-chip memory is accessed, there is no external address bus. All ports are available for general-purpose input and output.

## 2.3 Address Space Map

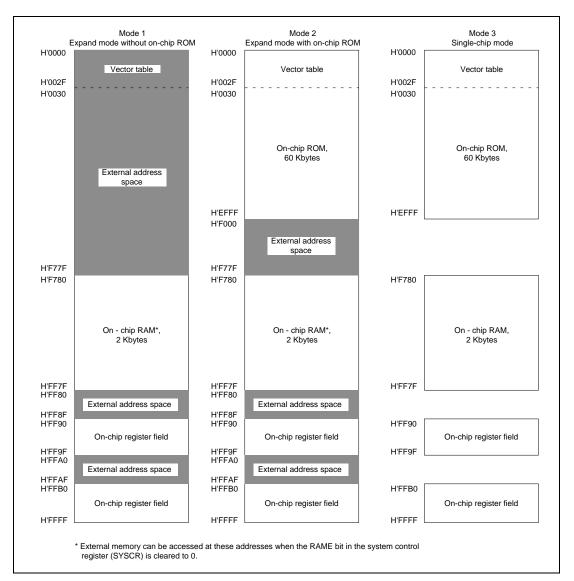

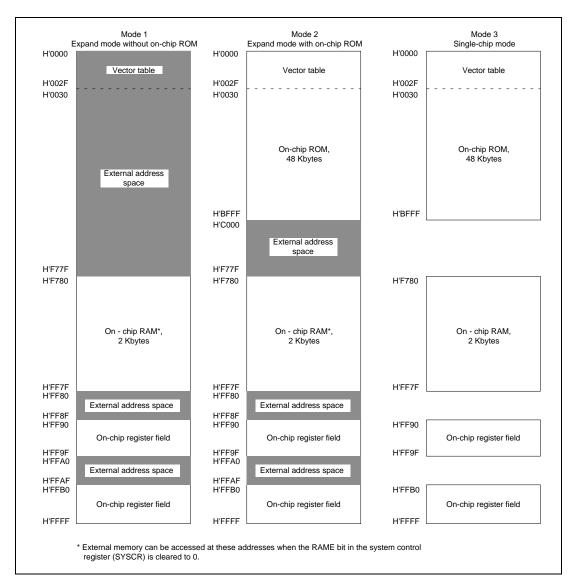

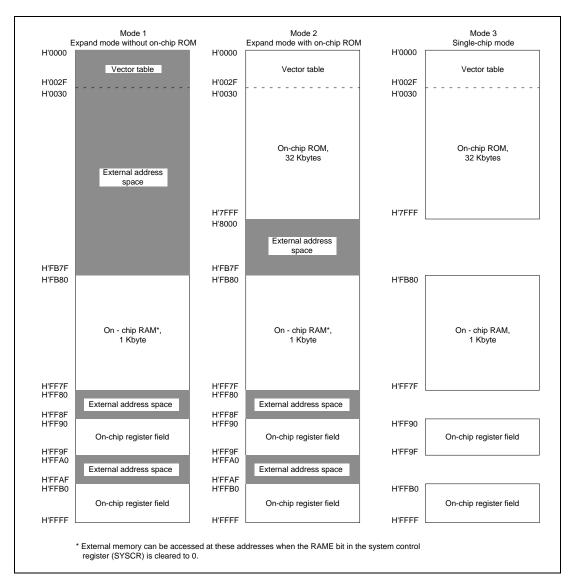

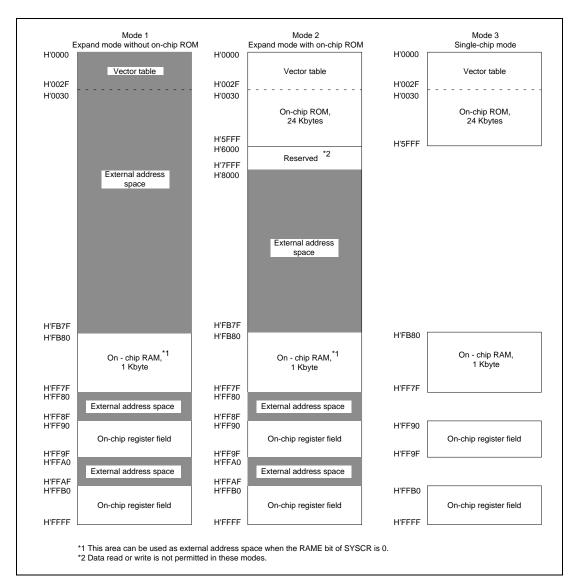

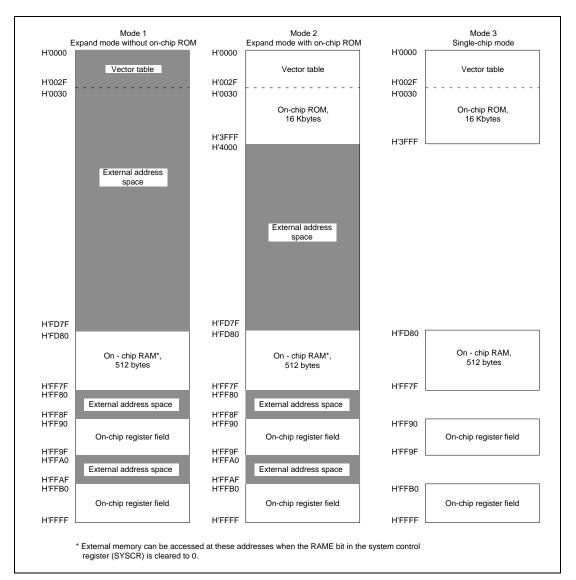

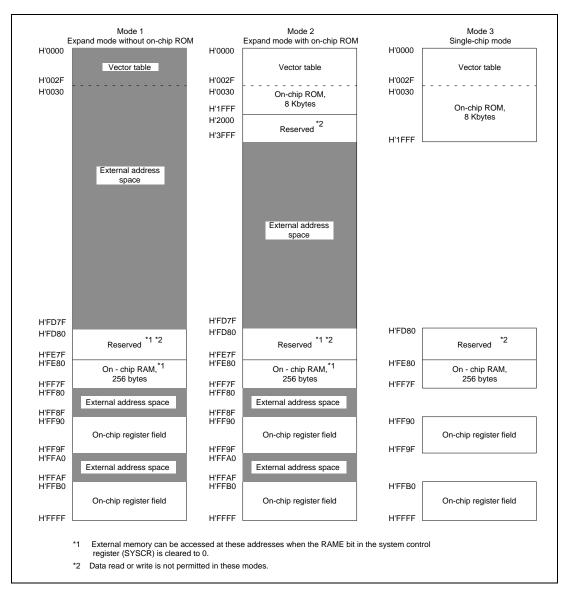

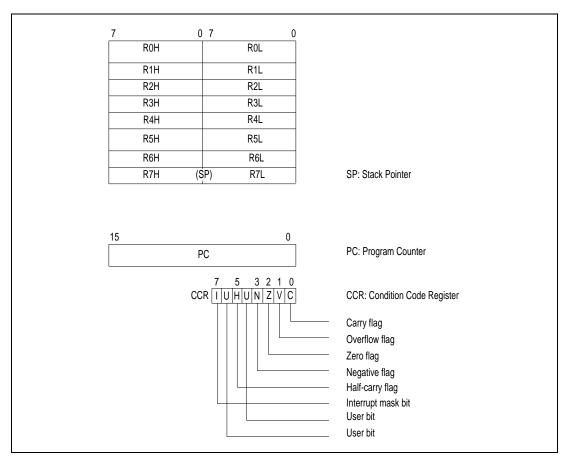

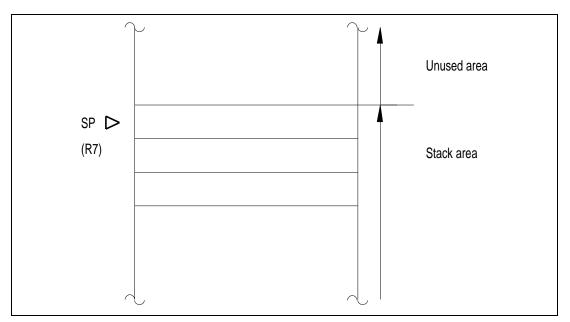

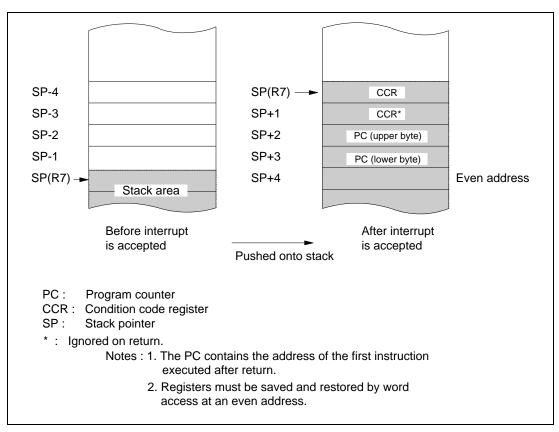

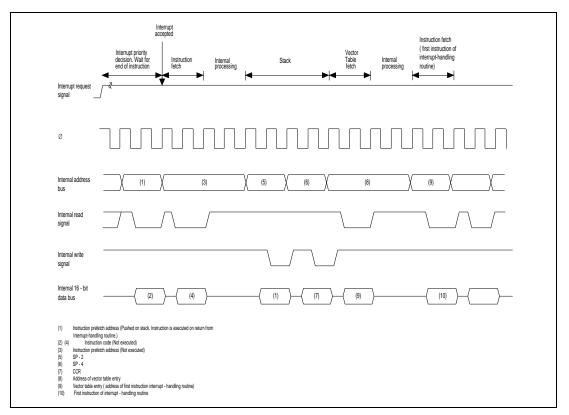

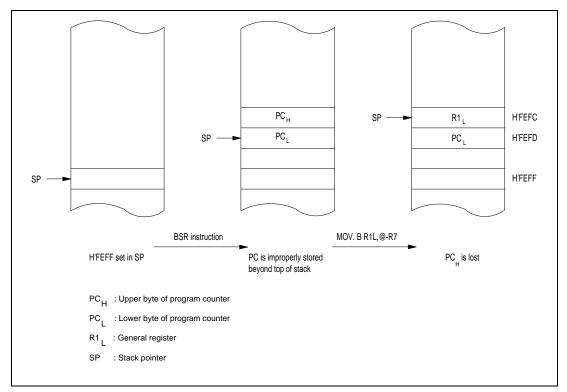

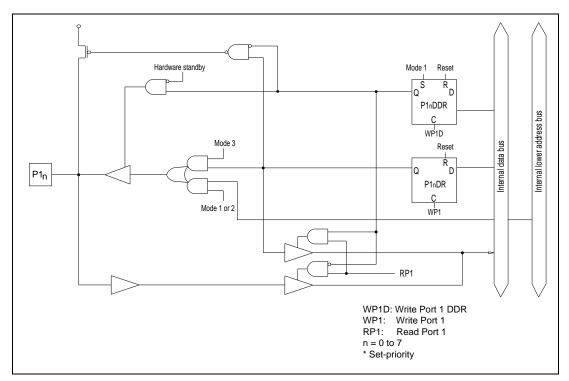

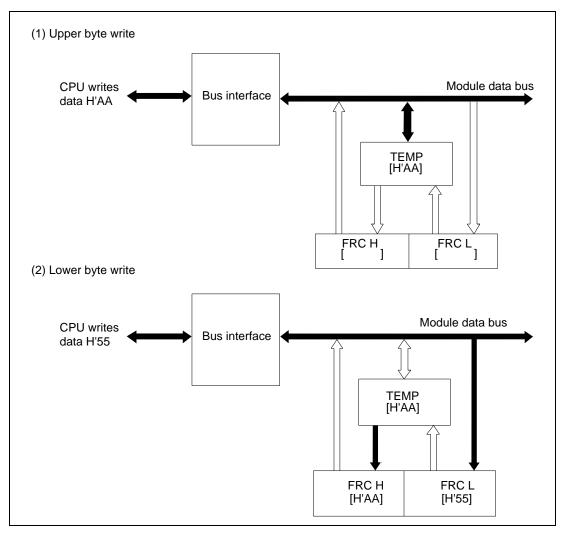

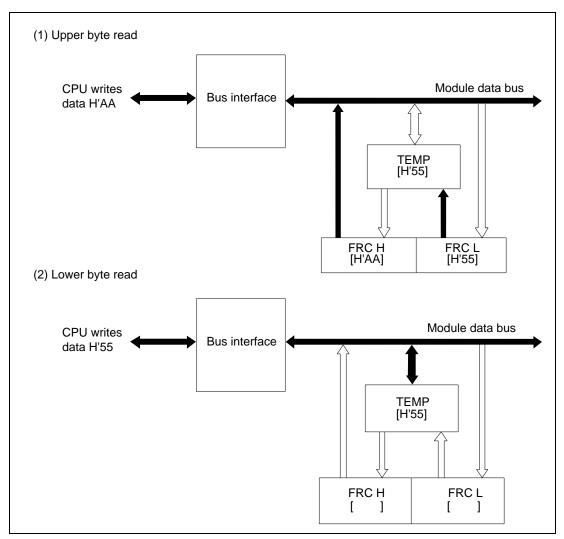

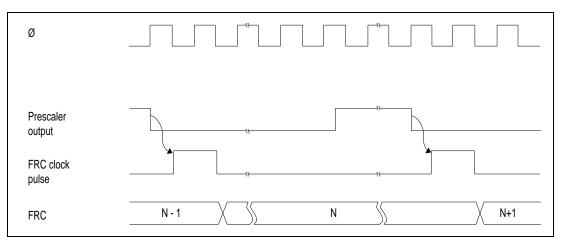

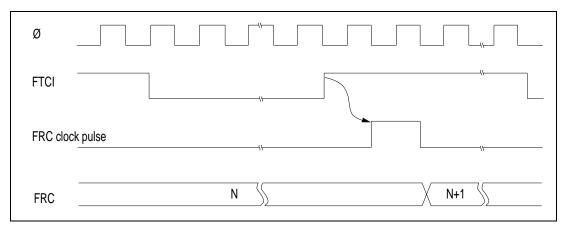

Figures 2-1 to 2-6 show memory maps of the H8/3257, H8/3256, H8/325, H8/324, H8/323, and H8/322 in each of the three operating modes. The on-chip register field consists of control, status, and data registers for the on-chip supporting modules and I/O ports.