# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### **Cautions**

Keep safety first in your circuit designs!

- Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but

there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire

or property damage.

- Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation

product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any

other rights, belonging to Renesas Technology Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors.

- Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these

materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

# Application Notes Hitachi Single-Chip Microcomputer Technical Questions and Answers H8/500 Series

#### Preface

The H8/500 Series is a series of highly integrated single-chip microcontrollers. Their CPU core has an internal 16-bit architecture, and each chip includes diverse high-performance peripheral hardware.

These technical questions and answers relate to the H8/510, H8/520, H8/532, H8/534, and H8/536.

#### **H8/500 Family**

| Item                   |          |                           | H8/510                             | H8/520                                  | H8/532               | H8/534                                  | H8/536                                |

|------------------------|----------|---------------------------|------------------------------------|-----------------------------------------|----------------------|-----------------------------------------|---------------------------------------|

| CPU                    |          |                           | H8/500                             | H8/500                                  | H8/500               | H8/500                                  | H8/500                                |

| Memory                 | ROM      | Masked ROM                | _                                  | 16 kbytes                               | 32 kbytes            | 32 kbytes                               | 62 kbytes                             |

|                        |          | ZTAT®*2                   | ×                                  | О                                       | О                    | О                                       | О                                     |

|                        | RAM      |                           | _                                  | 512 bytes                               | 1 kbyte              | 2 kbytes                                | 2 kbytes                              |

| Address                | space    | (bytes)                   | 16 M                               | 1 M                                     | 1 M                  | 1 M                                     | 1 M                                   |

| External               | data bu  | us width (bits)           | 8/16                               | 8                                       | 8                    | 8                                       | 8                                     |

| Timers                 | 16-bit   | free-running timer        | 2 ch                               | 2 ch                                    | 3 ch                 | 3 ch                                    | 3 ch                                  |

|                        | 8-bit ti | mer                       | 1 ch                               | 1 ch                                    | 1 ch                 | 1 ch                                    | 1 ch                                  |

|                        | Watch    | dog timer                 | 1 ch                               | 1 ch                                    | 1 ch                 | 1 ch                                    | 1 ch                                  |

|                        | PWM      | timer                     | _                                  | _                                       | 3 ch                 | 3 ch                                    | 3 ch                                  |

| Serial co<br>(async/sy |          | cation interface          | 2 ch                               | 2 ch                                    | 1 ch                 | 2 ch                                    | 2 ch                                  |

| A/D<br>converte        | r        | External<br>trigger input | 10 bits,<br>4 channels,<br>trigger | 10 bits, 4 or<br>8* channels<br>trigger |                      | 10 bits,<br>, 8 channels,<br>no trigger | 10 bits,<br>8 channels,<br>no trigger |

| Interrupts             | 3        | External interrupts       | 5                                  | 9                                       | 3                    | 7                                       | 7                                     |

|                        |          | Internal interrupts       | 18                                 | 18                                      | 19                   | 23                                      | 23                                    |

| I/O ports              |          |                           | 60                                 | 50/54*1                                 | 65                   | 65                                      | 65                                    |

| Package                | S        |                           | QFP-112                            | DILC-64S<br>(windowed)                  | LCC-84<br>(windowed) | LCC-84<br>(windowed)                    | LCC-84<br>(windowed)                  |

|                        |          |                           |                                    | DILP-64S                                | PLCC-84              | PLCC-84                                 | PLCC-84                               |

|                        |          |                           |                                    | PLCC-68*1                               | QFP-80               | QFP-80                                  | QFP-80                                |

|                        |          |                           |                                    | QFP-64                                  |                      |                                         |                                       |

Notes: 1. PLCC-68 package

2. ZTAT is a registered trademark of Hitachi, Ltd.

#### How to Use These Technical Questions and Answers

Technical Questions and Answers has been created by arranging technical questions actually asked by users of Hitachi microcomputers in a question-and-answer format. It should be read for technical reference in conjunction with the User's Manual.

Technical Questions and Answers can be read before beginning a microcomputer application design project to gain a more thorough understanding of the microcomputer, or during the design process to check up on difficult points.

(For questions and answers about the H8/500 CPU, see *H8/500 CPU Microcomputer Technical Questions and Answers.*)

# Contents

|                                                                  | Q&A No.          | Page |

|------------------------------------------------------------------|------------------|------|

| On-chip ROM                                                      |                  |      |

| (1) Address bus, data bus, and control line states during access | QA500 - 001B     | 1    |

| to on-chip address space                                         |                  |      |

| (2) Programming the H8/536 ZTAT                                  | QA500 - 046A     | 2    |

| Clock                                                            |                  |      |

| (1) EXTAL and system clock output line                           | QA500 - 002B     | 3    |

| (2) External clock specifications                                | QA500 - 047A     | 4    |

| (3) External clock input                                         | QA500 - 003B     | 5    |

| (4) External clock input (2)                                     | QA500 - 048A     | 6    |

| Timers                                                           |                  |      |

| (1) External clock input to 16-bit FRT                           | QA500 - 006B     | 7    |

| (2) Input capture signal for 16-bit FRT                          | QA500 - 007B     | 8    |

| (3) Access timing to FRC in 16-bit FRT                           | QA500 - 009B – 1 | 9    |

|                                                                  | QA500 - 009B - 2 | 10   |

| (4) TCNT of 8-bit timer                                          | QA500 - 011B     | 11   |

| (5) WDT when system clock stops                                  | QA500 - 012B     | 12   |

| (6) NMI requested by WDT                                         | QA500 - 013B     | 13   |

| Serial communication interface (SCI)                             |                  |      |

| (1) Input/output designation of SCI clock pin                    | QA500 - 018B     | 14   |

| (2) Serial I/O line status                                       | QA500 - 019B     | 15   |

| (3) RDRF bit set timing                                          | QA500 - 021B – 1 | 16   |

|                                                                  | QA500 - 021B – 2 | 17   |

| (4) TDRE bit set timing                                          | QA500 - 022B - 1 | 18   |

|                                                                  | QA500 - 022B – 2 | 19   |

| (5) RDR and DTR utilization when SCI is not used                 | QA500 - 023B     | 20   |

| (6) RDRF bit in SCI                                              | QA500 - 049A     | 21   |

| (7) SCI receive error 1                                          | QA500 - 050A     | 22   |

| (8) SCI receive error 2 (clocked synchronous mode)               | QA500 - 051A     | 23   |

| (9) SCI RxD input example (asynchronous mode)                    | QA500 - 052A     | 24   |

| (10) SCI transmit start (asynchronous mode)                      | QA500 - 053A     | 25   |

| (11) Simultaneous transmit/receive in clocked synchronous mode   | QA500 - 054A     | 26   |

| (12) Clearing the SCI's TDRE bit                                 | QA500 - 055A     | 27   |

|     |                                                                                         | Q&A No.      | Page |

|-----|-----------------------------------------------------------------------------------------|--------------|------|

| A/I | O converter                                                                             |              |      |

| (1) | Start of A/D conversion                                                                 | QA500 - 024B | 28   |

| (2) | Non-use of A/D converter reference voltage lines (AV <sub>CC</sub> , AV <sub>SS</sub> ) | QA500 - 025B | 29   |

| (3) | Changing A/D conversion mode or channels during conversion                              | QA500 - 027B | 30   |

| (4) | Resistor ladder in A/D converter                                                        | QA500 - 028B | 31   |

| (5) | Rise time of power supplies (AV <sub>CC</sub> , V <sub>CC</sub> )                       | QA500 - 029B | 32   |

| (6) | Allowable impedance of A/D signal sources                                               | QA500 - 056A | 33   |

| PW  | /M timer                                                                                |              |      |

| (1) | DTR of PWM timer                                                                        | QA500 - 031B | 34   |

| (2) | PWM pin assignments                                                                     | QA500 - 057A | 35   |

| Da  | ta transfer controller (DTC)                                                            |              |      |

|     | Interrupts during DTC operation                                                         | QA500 - 032B | 36   |

| (2) |                                                                                         | QA500 - 033B | 37   |

| I/O | ports                                                                                   |              |      |

| (1) | Analog input part data register during A/D conversion                                   | QA500 - 035B | 38   |

| (2) | Port output after reset                                                                 | QA500 - 037B | 39   |

| (3) | AS and RD signal timing                                                                 | QA500 - 039B | 40   |

|     | Unused I/O lines                                                                        | QA500 - 040B | 41   |

| Pov | wer-down modes                                                                          |              |      |

| _   | Power dissipation in hardware and software standby modes                                | QA500 - 041B | 42   |

| (1) | Tower dissipation in nardware and software standay modes                                | Q/1300 041B  | 72   |

| Bu  | s controller                                                                            |              |      |

| (1) | State of D <sub>0</sub> to D <sub>7</sub> with 8-bit data bus                           | QA500 - 058A | 43   |

| Bu  | s interface                                                                             |              |      |

| (1) | State of $D_0$ to $D_7$ during byte access in 16-bit data bus mode                      | QA500 - 059A | 44   |

| Mi  | scellaneous                                                                             |              |      |

| (1) | RAM standby voltage                                                                     | QA500 - 060A | 45   |

| Pro         | duct                                                | H8/500                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Q&A No.                          | QA500         | 0 - 001B                                                                                                                                                                                                           |

|-------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Тор         | oic                                                 | Address bus, data bus, and contro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I line states                    | during        | access to on-chip address space                                                                                                                                                                                    |

| 1.          | (1) (2)                                             | values are output on the following nemory or the on-chip register field Address bus Data bus Bus control signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |               | Classification—H8/500  Software On-chip ROM On-chip RAM Clock Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools |

| (1) (2) (3) | wheth<br>The d<br>and w<br>The R<br>access<br>high. | ddress bus carries the address data, her the access is to an on-chip or off ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access by the CPU to an on-chip ata bus is in the high-impedance startite access and the control is a starting at a star | chip addrest for both p address. | ss. read read | Miscellaneous Related Manuals Manual Title:  Other Technical Documentation Document Name:  Related Microcomputer Technical Q&A Title:                                                                              |

|             |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                  |               |                                                                                                                                                                                                                    |

| Prod | luct                       | H8/536                                                                                                                                                                                     | Q&A No.               | QA500                                                                                                                                                                                                                              | 4500 - 046A                                                                                                                |  |  |

|------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Topi | С                          | Programming the H8/536 ZTAT                                                                                                                                                                | -                     |                                                                                                                                                                                                                                    |                                                                                                                            |  |  |

| 1.   | Question                   |                                                                                                                                                                                            |                       | Classification—H8/536  Software O On-chip ROM On-chip RAM Clock Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |                                                                                                                            |  |  |

|      | When writer data in end ac | programming the H8/536, you must to memory type HN27C101 and ein addresses H'F680 to H'1FFFF or stidress.  The to use byte programming mode. The programming mode of the programming mode. | ther write Het H'F67F | H'FF<br>as the                                                                                                                                                                                                                     | Related Manuals  Manual Title:  Other Technical Documentation  Document Name:  Related Microcomputer Technical Q&A  Title: |  |  |

|      |                            | Information  OM writers do not support byte prog                                                                                                                                           | gramming fo           | or the H                                                                                                                                                                                                                           | IN27C101.                                                                                                                  |  |  |

|      |                            |                                                                                                                                                                                            |                       |                                                                                                                                                                                                                                    |                                                                                                                            |  |  |

| Product  | H8/500                                                                         | Q&A No. | QA50   | 0 - 002B                                                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Торіс    | EXTAL and system clock output lir                                              | ne      |        |                                                                                                                                                                                                             |

| Question |                                                                                |         |        | Classification—H8/500                                                                                                                                                                                       |

| 1. Durin | g external clock input, what is the pen EXTAL and the system clock output)?    |         | onship | Software On-chip ROM On-chip RAM O Clock Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |

| betwe    | g external clock input, the phase releen EXTAL and the system clock oun below. | _       | as     | Manual Title:  Other Technical Documentation Document Name:                                                                                                                                                 |

| ø output | approx. 40 ns internal delay                                                   |         |        | Related Microcomputer<br>Technical Q&A<br>Title:                                                                                                                                                            |

|          | al delay value is not guaranteed.                                              |         |        | 1                                                                                                                                                                                                           |

| Product                       | H8/500                                                                       | Q&A No.      | QA500              | 0 - 047A                                                                                                                                                                                                                           |

|-------------------------------|------------------------------------------------------------------------------|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Topic                         | External clock specifications                                                | '            |                    |                                                                                                                                                                                                                                    |

|                               | an external clock is supplied to the are the rise-time and fall-time require |              | n,                 | Classification—H8/500  Software On-chip ROM On-chip RAM O Clock Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |

| should<br>External<br>(EXTAL) | t <sub>Cf</sub> t <sub>Cr</sub>                                              | nd fall time | (t <sub>Cf</sub> ) | Related Manuals Manual Title:  Other Technical Documentation Document Name:  Related Microcomputer Technical Q&A Title:                                                                                                            |

| Additional                    | Information                                                                  |              |                    |                                                                                                                                                                                                                                    |

| Product          | H8/520, 532, 534, 536                                                                                  | Q&A No.   | QA500   | 0 - 003B                                                                                                                                                                    |

|------------------|--------------------------------------------------------------------------------------------------------|-----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Topic            | External clock input                                                                                   |           |         |                                                                                                                                                                             |

| Question         |                                                                                                        |           |         | Classification—H8/53                                                                                                                                                        |

| 1. For exemp     | kternal clock input, the Hardware M<br>ple of a circuit using a 74HC04 (see<br>HC04 necessary?  T4HC04 |           | hy is   | Software On-chip ROM On-chip RAM O Clock Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion |

|                  |                                                                                                        |           |         | Development tools Miscellaneous                                                                                                                                             |

| 1. If the unstal | XTAL pin open is left open, operatiole.                                                                | on may be | come    | Related Manuals  Manual Title:                                                                                                                                              |

| The 7 clock      | 4HC04 is necessary to assure stable rates.                                                             | operation | at high | Other Technical Documentation Document Name:                                                                                                                                |

|                  |                                                                                                        |           |         | Related Microcomputer<br>Technical Q&A<br>Title:                                                                                                                            |

| Additional       | I Information                                                                                          |           |         |                                                                                                                                                                             |

Note: The XTAL pin can be left open if the external clock rate is 16 MHz or less. For masked-ROM versions and the H8/510, the XTAL pin can be left open for external clock rates up to 20 MHz.

| <b>Product</b> H8/520, 532, 534, 536 <b>Q&amp;A No.</b> QAS |                                                                                                                            | QA500        | QA500 - 048A |                                                                                                                                                                                                                                    |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Topic                                                       | External clock input (2)                                                                                                   |              |              |                                                                                                                                                                                                                                    |

| a circ<br>diagra                                            | H8/500 Series User's Manuals (exceuit using a 74HC04 for external cloam on previous page.) Can an ALSple, be used instead? | ck input. (S |              | Classification—H8/532  Software On-chip ROM On-chip RAM O Clock Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |

|                                                             | LS-TTL device can be used if its prand drivability are equivalent to the                                                   |              | lelay        | Related Manuals  Manual Title:  Other Technical Documentation  Document Name:  Related Microcomputer Technical Q&A  Title:                                                                                                         |

| Additiona                                                   | I Information                                                                                                              |              |              | I                                                                                                                                                                                                                                  |

| Product                  | H8/500                                                                                   | Q&A No.       | QA500 | 0 - 006B                                                                                                                                                                                                                           |

|--------------------------|------------------------------------------------------------------------------------------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Topic                    | External clock input to 16-bit FRT                                                       |               |       |                                                                                                                                                                                                                                    |

| Question  1. When free-r | the external clock source is selecte unning timer, what is the minimum nal clock (FTCI)? |               |       | Classification—H8/500  Software On-chip ROM On-chip RAM Clock O Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |

|                          | ninimum pulse width of the externa                                                       | l clock is 1. | 5     | Related Manuals  Manual Title:  Other Technical Documentation Document Name:                                                                                                                                                       |

| FTCI inpu                | 1.5 system clocks                                                                        |               |       | Related Microcomputer Technical Q&A Title:                                                                                                                                                                                         |

| Additiona                | I Information                                                                            |               |       |                                                                                                                                                                                                                                    |

| Product          | H8/500                                                                                                                      | Q&A No.      | QA500 - 007B |                                                                                                                                                                                                                      |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Topic            | Input capture signal for 16-bit FRT                                                                                         |              |              |                                                                                                                                                                                                                      |  |

| gener<br>will th | FRT input capture line (FTI) is multal-purpose input/output port that is ne rise and fall of the output data upre register? | used for out | tput,        | Classification—H8/500  Software On-chip ROM On-chip RAM Clock O Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools |  |

| on the           | The input capture register will be up a input/output line, on the edge select select bit (IEDG) in the timer controls.      | cted by the  | input        | Miscellaneous  Related Manuals  Manual Title:  Other Technical Documentation Document Name:  Related Microcomputer Technical Q&A  Title:                                                                             |  |

| Additiona        | I Information                                                                                                               |              |              |                                                                                                                                                                                                                      |  |

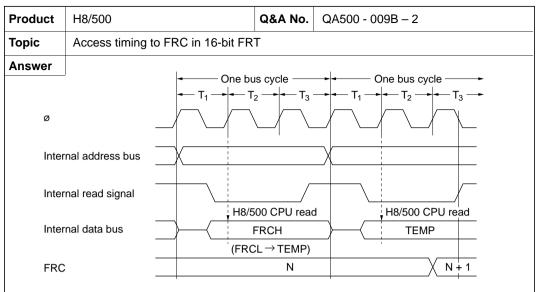

| Product   | H8/500                                                                                                                   | Q&A No.      | . QA500 - 009B – 1 |                                                                                                                                                                                                                                    |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Topic     | Access timing to FRC in 16-bit FR                                                                                        | Т            |                    |                                                                                                                                                                                                                                    |  |

|           | is the read and write timing of the fer (FRC) in the 16-bit free-running                                                 | -            |                    | Classification—H8/500  Software On-chip ROM On-chip RAM Clock O Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |  |

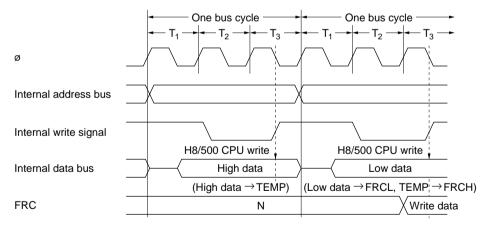

| the ne    | ccess timing of the 16-bit timer's Frext page.  access (or two successive byte acce The upper byte has to be accessed to | esses) shoul |                    | Related Manuals Manual Title:  Other Technical Documentation Document Name:  Related Microcomputer Technical Q&A Title:                                                                                                            |  |

| Additiona | I Information                                                                                                            |              |                    |                                                                                                                                                                                                                                    |  |

FRC Access Timing (read)

#### Operation when register is read

When the upper byte is read, the upper byte value is passed to the CPU and the lower byte value is transferred to TEMP. Next, when the lower byte is read, the lower byte value in TEMP is passed to the CPU.

FRC Access Timing (write)

#### Operation when register is written

When the upper byte is written, the upper byte value is stored in TEMP. Next, when the lower byte is written, it is combined with the upper byte value in TEMP and all 16 data bits are written in the register.

| Product                   | H8/500                                                                                     | Q&A No.               | QA500 - 011B |                                                                                                                                                                                                             |  |

|---------------------------|--------------------------------------------------------------------------------------------|-----------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Topic TCNT of 8-bit timer |                                                                                            |                       |              |                                                                                                                                                                                                             |  |

| Question                  |                                                                                            | Classification—H8/500 |              |                                                                                                                                                                                                             |  |

| (TCN                      | a compare-match signal clears the T) to H'00, does TCNT remain at H counting up from H'00? |                       |              | Software On-chip ROM On-chip RAM Clock O Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |  |

| 1. TCNT                   | Γ starts counting up from H'00.                                                            |                       |              | Related Manuals  Manual Title:  Other Technical Documentation  Document Name:  Related Microcomputer Technical Q&A  Title:                                                                                  |  |

| Additiona                 | I Information                                                                              |                       |              |                                                                                                                                                                                                             |  |

| Product    | H8/500                                                                 | Q&A No.     | QA500 - 012B |                   |                                                                                                                                                                                                           |  |

|------------|------------------------------------------------------------------------|-------------|--------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Topic      | WDT when system clock stops                                            |             |              |                   |                                                                                                                                                                                                           |  |

|            | system clock stops, will the watchd anything wrong?                    | og timer (V | VDT)         | 0                 | Software On-chip ROM On-chip RAM Clock Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |  |

|            | system clock for the whole chip sto also stops, so the WDT cannot dete | -           |              | Oth<br>Doo<br>Doo | er Technical cumentation cument Name:                                                                                                                                                                     |  |

| Additional | Information                                                            |             |              |                   |                                                                                                                                                                                                           |  |

| Product                | H8/532                                                                                                          | Q&A No.          | QA500      | - 013B                                                                                                                                                                                                               |

|------------------------|-----------------------------------------------------------------------------------------------------------------|------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Topic                  | NMI requested by WDT                                                                                            |                  |            |                                                                                                                                                                                                                      |

| Question  1. How reque |                                                                                                                 |                  |            | Classification—H8/532  Software On-chip ROM On-chip RAM Clock O Timers Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools |

| overfl                 | n the WDT requests an NMI interrup<br>low bit (OVF) in the WDT timer sta<br>er (TCSR) to 1. You can detect this | itus/control     |            | Miscellaneous Related Manuals Manual Title:                                                                                                                                                                          |

| NIML                   | requested by input signal from pin                                                                              | OVF Bit in       | TCSR       | Other Technical Documentation                                                                                                                                                                                        |

|                        | requested by WDT                                                                                                | 1                |            | Document Name:                                                                                                                                                                                                       |

|                        |                                                                                                                 |                  |            | Related Microcomputer Technical Q&A                                                                                                                                                                                  |

|                        |                                                                                                                 |                  |            | Title:                                                                                                                                                                                                               |

| When the               | Information  <br>WDT is used in interval timer mode<br>520, H8/532)                                             | e, IR $Q_0$ inte | errupts ca | an be discriminated in the same                                                                                                                                                                                      |

| Pro           | duct                     | H8/500                                                                                                                                                                        | Q&A No.                      | QA500 - 018B              |                                                                                                                                                                                                                                    |  |

|---------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Тор           | ic                       | Input/output designation of SCI clo                                                                                                                                           | ock pin                      | l                         |                                                                                                                                                                                                                                    |  |

| <b>Que</b> 1. | input                    | the SCI is used, is the serial clock or output by writing a 0 or 1 in the er (DDR) of the corresponding port                                                                  | data directi                 |                           | Classification—H8/500  Software On-chip ROM On-chip RAM Clock Timers O Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |  |

| 1.            | clock<br>in the<br>and 0 | you use the SCI, the input or output line depends on the communication serial mode register (SMR) and the bits (CKE1 and CKE0) in the serial). You don't have to set the DDR. | n mode bit (<br>e clock enat | $(C/\overline{A}.)$ ole 1 | Related Manuals  Manual Title:  Other Technical Documentation  Document Name:  Related Microcomputer Technical Q&A  Title:                                                                                                         |  |

| Add           | litional                 | Information                                                                                                                                                                   |                              |                           |                                                                                                                                                                                                                                    |  |

| Product                       | H8/500                                                                                                                                                                                                         | Q&A No.                                      | QA500     | 0 - 019B                                                                                                                                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Topic                         | Serial I/O line status                                                                                                                                                                                         | 1                                            |           |                                                                                                                                                                                                                                   |

| SCK<br>suppo<br>made<br>regis | input/output ports multiplexed with lines have been used for serial compose they are redesignated as I/O port in the serial control register (SCR) are (SMR).  Evalues will the corresponding data R) contain? | munication,<br>as by setting<br>or serial mo | gs<br>ode | Classification—H8/500 Software On-chip ROM On-chip RAM Clock Timers O Serial I/O A/D PWM DTC I/O ports Power-down modes Elec. characteristics Exception handling Bus interface External expansion Development tools Miscellaneous |

| of ing<br>the D               | operations do not affect the contents out/output ports. Given the condition DR bits will retain the values they have for serial communication.                                                                 | ns you descr                                 | ribe,     | Related Manuals Manual Title:  Other Technical Documentation Document Name:  Related Microcomputer Technical Q&A Title:                                                                                                           |

| Additiona                     | Il Information                                                                                                                                                                                                 |                                              |           |                                                                                                                                                                                                                                   |

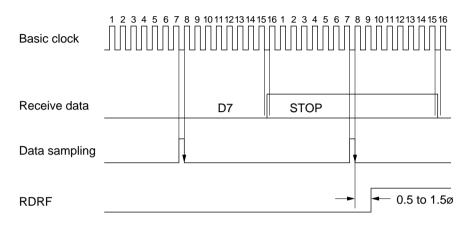

| Produc                       | ct                                                                                                                                                                                | H8/500              | Q&A No. | QA500 - 021B – 1 |                                                                                                                                                |                                                                                   |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Topic                        |                                                                                                                                                                                   | RDRF bit set timing |         |                  |                                                                                                                                                |                                                                                   |

| Question  1. W full 1. 2. At | When data reception is completed, the receive data register full bit (RDRF) in the serial status register (SSR) is set to 1. At what timing does this occur in asynchronous mode? |                     |         | Side   O         | ssification—H8/500 oftware n-chip ROM n-chip RAM lock mers erial I/O //D WM TC D ports ower-down modes lec. characteristics exception handling |                                                                                   |

| Answe See the                |                                                                                                                                                                                   | xt page.            |         |                  | Bi<br>Ex<br>Do<br>M<br>Relate                                                                                                                  | us interface external expansion evelopment tools iscellaneous d Manuals il Title: |

|                              |                                                                                                                                                                                   |                     |         |                  | Docum<br>Docum<br>Relate                                                                                                                       | Technical nentation nent Name:  d Microcomputer ical Q&A                          |

| Additio                      | onal                                                                                                                                                                              | Information         |         |                  |                                                                                                                                                |                                                                                   |

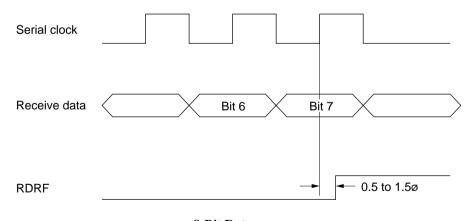

| Product | H8/500              | Q&A No. | QA500 - 021B – 2 |

|---------|---------------------|---------|------------------|

| Topic   | RDRF bit set timing |         |                  |

| Answer  |                     |         |                  |

1. The RDRF bit is set to 1 after the fall of the next data sampling clock after the MSB of the data is received. (See the diagram below.)

8-Bit Data, 1 Stop Bit, Internal Clock

2. The RDRF bit is set to 1 after the rising edge of the serial clock cycle in which the MSB of the data is received. (See the diagram below.)

8-Bit Data

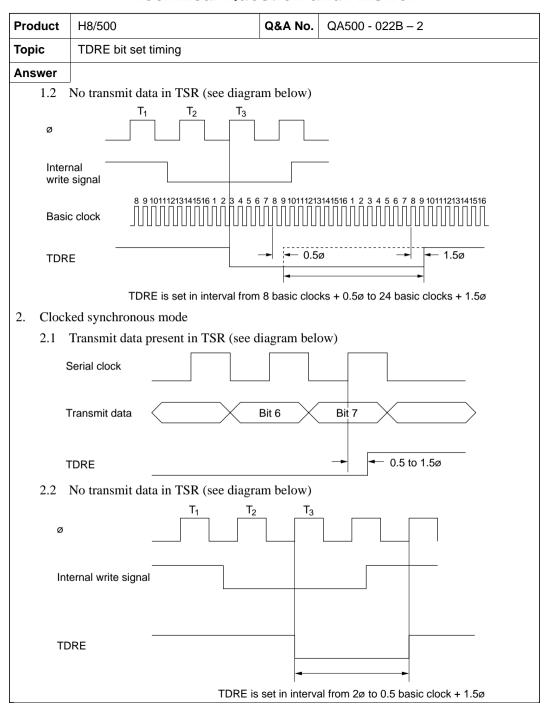

| Product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | H8/500                                                                                                                                                                  | Q&A No.                     | QA500 - 022B – 1 |                                                                                                                                                                                                                                    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|