# HD66214T (Micro-TAB)

# (80-Channel Column Driver in Micro-TCP)

#### Description

The HD66214T, the column driver for a large liquid crystal graphic display, features as many as 80 LCD outputs powered by 80 internal LCD drive circuits. This device latches 4-bit parallel data sent from an LCD controller, and generates LCD drive signals. In standby mode provided by its internal standby function, only one drive circuit operates, lowering power dissipation. The HD66214, packaged in an 8-mm-wide micro-tape carrier package (micro-TCP), enables a compact LCD system with a narrower frame (peripheral areas for LCD drivers) -about half as large as that os an existing system. The HD66214T is a low power dissipation device powered by 2.7-5.5 V suitable for battery-driven portable equipment such as notebook personal computers and palmtop personal computers.

#### **Features**

Duty cycle: 1/64 to 1/240

High voltage

— LCD drive: 10-28 V

High clock speed

- 8 MHz max under 5-V operation (HD66214T)

- 4 MHz max under 3-V operation (HD66214TL)

- Display off function

- · Internal automatic chip enable signal generator

- Various LCD controller interfaces

- LCTC series: HD63645, HD64645, HD64646

- LVIC series: HD66840, HD66841

— CLINE: HD66850

98-pin TCP

#### **Ordering Information**

| Type No.    | Voltage Range | Outer Lead Pitch 1 | Outer Lead Pitch 2 | Device Length    |  |

|-------------|---------------|--------------------|--------------------|------------------|--|

| HD66214TA1  | 2.7–5.5 V     | 0.15 mm            | 0.80 mm            | 3 sprocket holes |  |

| HD66214TA2  | 2.7–5.5 V     | 0.18 mm            | 0.80 mm            | 3 sprocket holes |  |

| HD66214TA3  | 2.7–5.5 V     | 0.20 mm            | 0.80 mm            | 3 sprocket holes |  |

| HD66214TA6  | 2.7–5.5 V     | 0.20 mm            | 0.45 mm            | 3 sprocket holes |  |

| HD66214TA9L | 2.7–5.5 V     | 0.22 mm            | 0.45 mm            | 2 sprocket holes |  |

Notes: 1. Outer lead pitch 1 is for LCD drive output pins, and outer lead pitch 2 for the other pins.

- 2. Device length includes test pad areas.

- 3. Spacing between two sprocket holes is 4.75 mm.

- 4. Tape film is Upirex (a trademark of Ube Industries, Ltd.).

- 5. 35-mm-wide tape is used.

- 6. Leads are plated with Sn.

- 7. The details of TCP pattern are shown in "The Information of TCP."

HITACHI

722

4496204 0046518 26T **=**

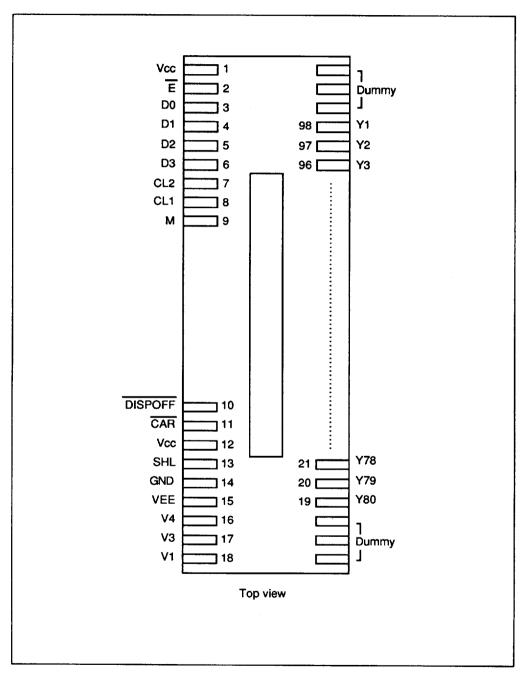

# Pin Arrangement

HITACHI

\* 4496204 DO46519 1T6 🖿

723

# **Pin Description**

| Symbol                          | Pin No. | Pin Name        | Input/Output | Classification   |

|---------------------------------|---------|-----------------|--------------|------------------|

| V <sub>CC</sub>                 | 1, 12   | V <sub>CC</sub> | _            | Power supply     |

| GND                             | 14      | GND             | _            | Power supply     |

| V <sub>EE</sub>                 | 15      | V <sub>EE</sub> | _            | Power supply     |

| V1                              | 18      | V1              | Input        | Power supply     |

| V3                              | 17      | V3              | input        | Power supply     |

| V4                              | 16      | V4              | Input        | Power supply     |

| CL1                             | 8       | Clock 1         | Input        | Control signal   |

| CL2                             | 7       | Clock 2         | Input        | Control signal   |

| М                               | 9       | М               | Input        | Control signal   |

| D <sub>0</sub> -D <sub>3</sub>  | 3–6     | Data 0-data 3   | Input        | Control signal   |

| SHL                             | 13      | Shift left      | Input        | Control signal   |

| CAR                             | 2       | Enable          | Input        | Control signal   |

| CAR                             | 11      | Carry           | Output       | Control signal   |

| DISPOFF                         | 10      | Display off     | Input        | Control signal   |

| Y <sub>1</sub> -Y <sub>80</sub> | 1998    | Y1-Y80          | Output       | LCD drive output |

**HITACHI**

724

**44**95204 0046520 **918**

#### Pin Functions

#### **Power Supply**

V<sub>CC</sub>, V<sub>EE</sub>, GND: V<sub>CC</sub>-GND supplies power to the internal logic circuits. Vcc-VEE supplies power to the LCD drive circuits.

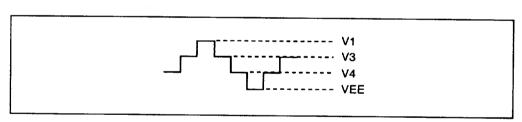

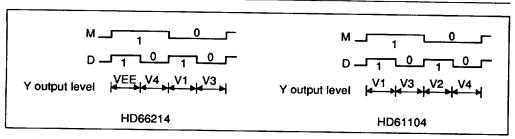

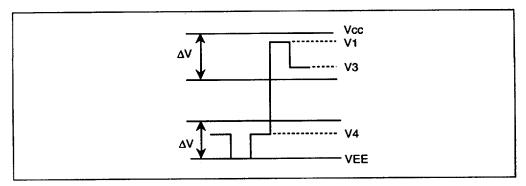

V1, V3, V4: Supply different levels of power to drive the LCD. V1 and  $V_{EE}$  are selected levels, and V3 and V4 are non-selected levels. See figure 1.

#### Control Signal

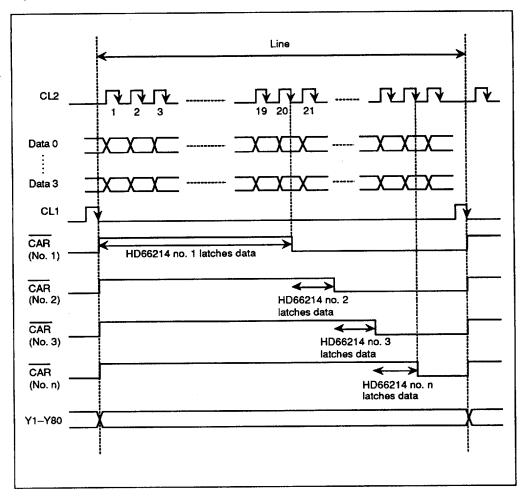

CL1: Inputs display data latch pulses for the line data latch circuit. The line data latch circuit latches display data input from the 4-bit latch circuit, and outputs LCD drive signals corresponding to the latched data, both at the falling edge of each CL1 pulse.

CL2: Inputs display data latch pulses for the 4-bit latch circuit. The 4-bit latch circuit latches display data input via  $D_0$ – $D_3$  at the falling edge of each CL2 pulse.

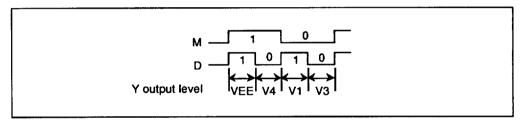

M: Changes LCD drive outputs to AC.

D<sub>0</sub>-D<sub>3</sub>: Input display data. High-voltage level of data corresponds to a selected level and turns an LCD pixel on, and low-voltage level data corresponds to a non-selected level and turns an LCD pixel off.

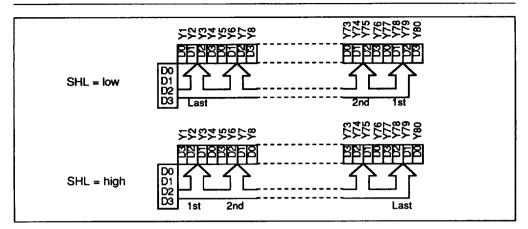

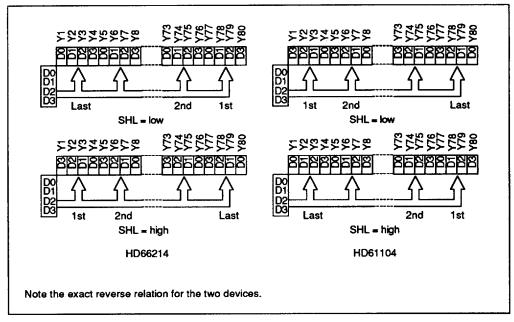

SHL: Shifts the destinations of display data output. See figure 2.

$\overline{E}$ : A low  $\overline{E}$  enables the chip, and a high  $\overline{E}$  disables the chip.

$\overline{\text{CAR}}$ : Outputs the  $\overline{\text{E}}$  signal to the next HD66214 if HD66214s are connected in cascade.

DISPOFF: A low DISP sets LCD drive outputs Y<sub>1</sub>-Y<sub>80</sub> to V1 level.

## **LCD Drive Output**

$Y_1-Y_{80}$ : Each Y outputs one of the four voltage levels V1, V3, V4, or  $V_{EE}$ , depending on a combination of the M signal and display data levels. See figure 3.

Figure 1 Different Power Supply Voltage Levels for LCD Drive Circuits

Figure 2 Selection of Destinations of Display Data Output

Figure 3 Selection of LCD Drive Output Level

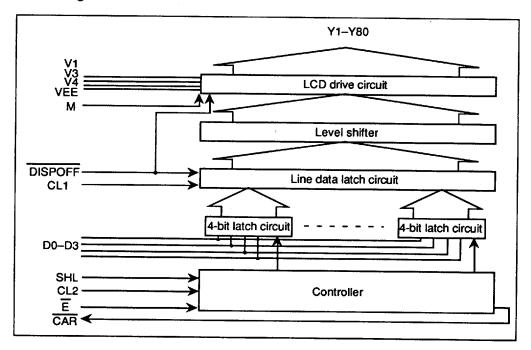

#### **Block Functions**

Controller: The controller generates the latch signal at the falling edge of each CL2 pulse for the 4-bit latch circuit.

#### 4-Bit Latch Circuit

The 4-bit latch circuit latches 4-bit parallel data input via the D0 to D3 pins at the timing generated by the control circuit.

#### Line Data Latch Circuit

The 80-bit line data latch circuit latches data input from the 4-bit latch circuit, and outputs the latched data to the level shifter, both at the falling edge of each clock 1 (CL1) pulse.

#### **Level Shifter**

The level shifter changes 5-V signals into highvoltage signals for the LCD drive circuit.

#### **LCD Drive Circuit**

The 80-bit LCD drive circuit generates four voltage levels V1, V3, V4, and VEE, for driving an LCD panel. One of the four levels is output to the corresponding Y pin, depending on a combination of the M signal and the data in the line data latch circuit.

#### **Block Diagram**

HITACHI

| 4496204 0046523 627 |

727

#### Comparison of the HD66214 with the HD61104

| Item                                             | HD66214                                           | HD61104                 |

|--------------------------------------------------|---------------------------------------------------|-------------------------|

| Clock speed                                      | 8.0 MHz max.                                      | 3.5 MHz max.            |

| Display off function                             | Provided                                          | Not provided            |

| LCD drive voltage range                          | 10–28 V                                           | 10-26 V                 |

| Relation between SHL and LCD output destinations | See figure 4                                      | See figure 4            |

| Relation between LCD output levels, M, and data  | See figure 5                                      | See figure 5            |

| LCD drive V pins                                 | V1, V3, V4<br>(V2 level is the same as VEE level) | V1, V2, V3, V4          |

| Storage temperature                              | -40 to 125°C                                      | -55 to 125°C            |

| Package                                          | TCP (tape carrier package)                        | QFP (quad flat package) |

Figure 4 Relation between SHL and LCD Output Destinations for the HD66214 and HD61104

Figure 5 Relation between LCD Output Levels, M, and Data for the HD66214 and HD61104

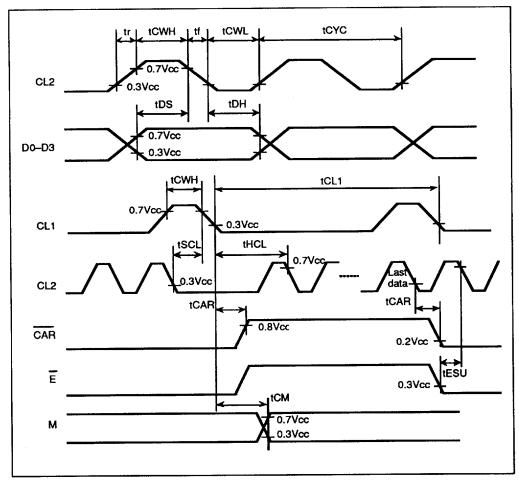

# **Operation Timing**

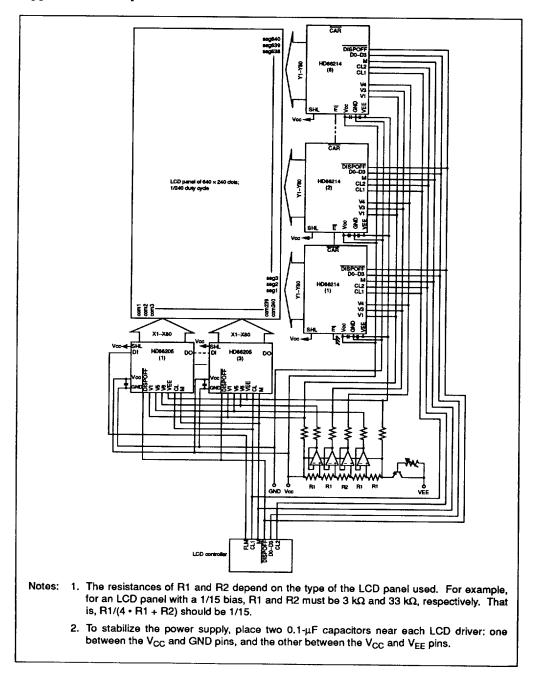

## **Application Example**

**HITACHI**

**=** 4496204 0046527 272 **=**

731

#### **Absolute Maximum Ratings**

| Item                                        | Symbol           | Rating                                   | Unit | Notes |

|---------------------------------------------|------------------|------------------------------------------|------|-------|

| Power supply voltage for logic circuits     | V <sub>CC</sub>  | -0.3 to +7.0                             | V    | 1     |

| Power supply voltage for LCD drive circuits | V <sub>EE</sub>  | $V_{CC} = 30.0 \text{ to } V_{CC} + 0.3$ | V    |       |

| Input voltage 1                             | V <sub>T1</sub>  | -0.3 to V <sub>CC</sub> + 0.3            | ٧    | 1, 2  |

| Input voltage 2                             | V <sub>T2</sub>  | $V_{EE} - 0.3$ to $V_{CC} + 0.3$         | V    | 1, 3  |

| Operating temperature                       | Topr             | -20 to +75                               | °C   |       |

| Storage temperature                         | T <sub>stg</sub> | -40 to +125                              | °C   |       |

- Notes: 1. The reference point is GND (0 V).

- 2. Applies to pins CL1, CL2, M, SHL, E, D<sub>0</sub>-D<sub>3</sub>, DISPOFF.

- 3. Applies to pins V1, V3, and V4.

- 4. If the LSI is used beyond its absolute maximum ratings, it may be permanently damaged. It should always be used within its electrical characteristics in order to prevent malfunctioning or degradation of reliability.

#### **Electrical Characteristics**

DC Characteristics for the HD66214T ( $V_{CC}$  = 5 V  $\pm$  10%, GND = 0 V,  $V_{CC}$  -  $V_{EE}$  = 10 to 28 V, and  $Ta = -20 \text{ to } +75^{\circ}\text{C}$ , unless otherwise noted.)

| Item                    | Symbol           | Pins | Min.                  | Тур. | Max.                  | Unit | Condition                                                                                           | Notes |

|-------------------------|------------------|------|-----------------------|------|-----------------------|------|-----------------------------------------------------------------------------------------------------|-------|

| Input high voltage      | VIH              | 1    | 0.7 × V <sub>CC</sub> |      | V <sub>CC</sub>       | ٧    |                                                                                                     |       |

| Input low voltage       | V <sub>IL</sub>  | 1    | 0                     | _    | 0.3 × V <sub>CC</sub> | ٧    |                                                                                                     |       |

| Output high voltage     | V <sub>OH</sub>  | 2    | V <sub>CC</sub> - 0.4 | _    | _                     | ٧    | l <sub>OH</sub> = -0.4 mA                                                                           |       |

| Output low voltage      | Vol              | 2    | _                     | _    | 0.4                   | ٧    | l <sub>OL</sub> = 0.4 mA                                                                            | •     |

| Vi-Yj on resistance     | R <sub>ON</sub>  | 3    |                       | _    | 4.0                   | kΩ   | l <sub>ON</sub> = 100 μA                                                                            | 1     |

| Input leakage current 1 | I <sub>IL1</sub> | 1    | -1.0                  | _    | 1.0                   | μА   | V <sub>IN</sub> = V <sub>CC</sub> to GND                                                            |       |

| Input leakage current 2 | I <sub>IL2</sub> | 4    | -25                   |      | 25                    | μА   | VIN = VCC to VEE                                                                                    |       |

| Current consumption 1   | I <sub>GND</sub> | _    |                       |      | 3.0                   | mA   | f <sub>CL2</sub> = 8.0 MHz<br>f <sub>CL1</sub> = 20 kHz<br>V <sub>CC</sub> - V <sub>EE</sub> = 28 V | 2     |

| Current consumption 2   | I <sub>EE</sub>  |      | _                     | 150  | 500                   | μΑ   | Same as above                                                                                       | 2     |

| Current consumption 3   | I <sub>ST</sub>  |      | _                     |      | 200                   | μΑ   | Same as above                                                                                       | 2, 3  |

Pins and notes on next page.

DC Characteristics for the HD66214T ( $V_{CC}$  = 2.7 to 5.5 V, GND = 0 V,  $V_{CC}$  -  $V_{EE}$  = 10 to 28 V, and Ta = -20 to +75°C, unless otherwise noted.)

| Item                    | Symbol           | Pins | Min.                  | Max.                  | Unit | Condition                                                                                                                                                                              | Notes |

|-------------------------|------------------|------|-----------------------|-----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Input high voltage      | V <sub>IH</sub>  | 1    | 0.7 × V <sub>CC</sub> | V <sub>CC</sub>       | v    |                                                                                                                                                                                        |       |

| Input low voltage       | V <sub>IL</sub>  | 1    | 0                     | 0.3 × V <sub>CC</sub> | ٧    |                                                                                                                                                                                        |       |

| Output high voltage     | V <sub>OH</sub>  | 2    | V <sub>CC</sub> - 0.4 | _                     | V    | I <sub>OH</sub> = -0.4 mA                                                                                                                                                              |       |

| Output low voltage      | V <sub>OL</sub>  | 2    | _                     | 0.4                   | V    | I <sub>OL</sub> = 0.4 mA                                                                                                                                                               |       |

| Vi–Yj on resistance     | R <sub>ON</sub>  | 3    |                       | 4.0                   | kΩ   | l <sub>ON</sub> = 100 μA                                                                                                                                                               | 1     |

| Input leakage current 1 | I <sub>IL1</sub> | 1    | -1.0                  | 1.0                   | μА   | V <sub>IN</sub> = V <sub>CC</sub> to GND                                                                                                                                               |       |

| Input leakage current 2 | l <sub>iL2</sub> | 4    | -25                   | 25                    | μА   | V <sub>IN</sub> = V <sub>CC</sub> to V <sub>EE</sub>                                                                                                                                   |       |

| Current consumption 1   | I <sub>GND</sub> |      | _                     | 1.0                   | mA   | f <sub>CL2</sub> = 4.0 MHz<br>f <sub>CL1</sub> = 16.8 kHz<br>f <sub>M</sub> = 35 Hz<br>V <sub>CC</sub> = 3.0 V<br>V <sub>CC</sub> - V <sub>EE</sub> = 28 V<br>Checker-board<br>pattern | 2     |

| Current consumption 2   | IEE              | _    | _                     | 500                   | μΑ   | Same as above                                                                                                                                                                          | 2     |

| Current consumption 3   | I <sub>ST</sub>  |      | _                     | 50                    | μА   | Same as above                                                                                                                                                                          | 2, 3  |

Pins:

1. CL1, CL2, M, SHL, E, D<sub>0</sub>-D<sub>3</sub>, DISPOFF

- 2. CAR

- 3. Y1-Y80, V1, V3, V4

- 4. V1, V3, V4

Notes: 1. Indicates the resistance between one pin from Y1-Y80 and another pin from V1, V3, V4, and V<sub>EE</sub>, when load current is applied to the Y pin; defined under the following conditions.

V1, V3 =

$$V_{CC} - \{2/10(V_{CC} - V_{EE})\}$$

$$V4 = V_{EE} + \{2/10(V_{CC} - V_{EE})\}$$

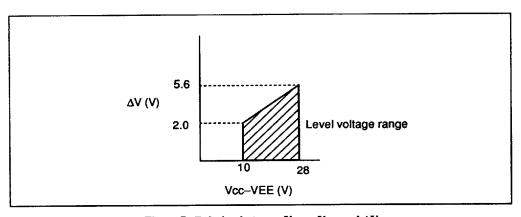

V1 and V3 should be near Vcc level, and V4 should be near VEE level (figure 6). All voltage must be within  $\Delta V$ .  $\Delta V$  is the range within which R<sub>ON</sub>, the LCD drive circuits' output impedance, is stable. Note that ΔV depends on power supply voltage V<sub>CC</sub>-V<sub>EE</sub> (figure 7).

- 2. Input and output current is excluded. When a CMOS input is floating, excess current flows from the power supply through the input circuit. To avoid this,  $V_{IH}$  and  $\bar{V}_{IL}$  must be held to  $V_{CC}$ and GND levels, respectively.

- 3. Applies to standby mode.

Figure 6 Relation between Driver Output Waveform and Level Voltages

Figure 7 Relation between  $V_{CC}$  –  $V_{EE}$  and  $\Delta V$

# AC Characteristics for the HD66214T ( $V_{CC}$ = 5 V $\pm$ 10%, GND = 0 V, and Ta = -20 to +75°C, unless otherwise noted.)

| Item                          | Symbol           | Pins                                 | Min.                  | Max.         | Unit | Notes |

|-------------------------------|------------------|--------------------------------------|-----------------------|--------------|------|-------|

| Clock cycle time              | tcyc             | CL2                                  | 125                   |              | ns   |       |

| Clock high-level width 1      | <sup>t</sup> cwH | CL1, CL2                             | 45                    |              | ns   |       |

| Clock low-level width         | t <sub>CWL</sub> | CL2                                  | 45                    |              | ns   | _     |

| Clock setup time              | tscl             | CL1, CL2                             | 80                    |              | ns   |       |

| Clock hold time               | tHCL             | CL1, CL2                             | 80                    |              | ns   |       |

| Clock rise time               | tr               | CL1, CL2                             |                       | *1           | ns   | 1     |

| Clock fall time               | t <sub>f</sub>   | CL1, CL2                             |                       | *1           | ns   | 1     |

| Data setup time               | t <sub>DS</sub>  | D <sub>0</sub> -D <sub>3</sub> , CL2 | 20                    |              | ns   | •     |

| Data hold time                | t <sub>DH</sub>  | D <sub>0</sub> D <sub>3</sub> , CL2  | 20                    |              | ns   |       |

| Enable (E) setup time         | t <sub>ESU</sub> | E, CL2                               | 30                    | <del>_</del> | ns   |       |

| Carry (CAR) output delay time | t <sub>CAR</sub> | CAR, CL2                             |                       | 80           | ns   | 2     |

| M phase difference time       | t <sub>CM</sub>  | M, CL2                               |                       | 300          | ns   |       |

| CL1 cycle time                | t <sub>CL1</sub> | CL1                                  | t <sub>CYC</sub> × 50 |              | ns   |       |

# AC Characteristics for the HD66214T ( $V_{CC}$ = 2.7 to 5.5 V, GND = 0 V, and Ta = -20 to +75°C, unless otherwise noted.)

| Item                          | Symbol           | Pins                                 | Min.                  | Max. | Unit | Notes                                 |

|-------------------------------|------------------|--------------------------------------|-----------------------|------|------|---------------------------------------|

| Clock cycle time              | t <sub>CYC</sub> | CL2                                  | 250                   |      | ns   |                                       |

| Clock high-level width 1      | tcwH             | CL1, CL2                             | 95                    |      | ns   |                                       |

| Clock low-level width         | t <sub>CWL</sub> | CL2                                  | 95                    | _    | ns   |                                       |

| Clock setup time              | tscL             | CL1, CL2                             | 80                    |      | ns   | · · · · · · · · · · · · · · · · · · · |

| Clock hold time               | tHCL             | CL1, CL2                             | 120                   |      | ns   |                                       |

| Clock rise time               | t <sub>r</sub>   | CL1, CL2                             | _                     | *1   | ns   | 1                                     |

| Clock fall time               | t <sub>f</sub>   | CL1, CL2                             |                       | *1   | ns   | <u> </u>                              |

| Data setup time               | t <sub>DS</sub>  | D <sub>0</sub> -D <sub>3</sub> , CL2 | 50                    |      | ns   | <del></del>                           |

| Data hold time                | t <sub>DH</sub>  | D <sub>0</sub> -D <sub>3</sub> , CL2 | 50                    |      | ns   |                                       |

| Enable (E) setup time         | t <sub>ESU</sub> | E, CL2                               | 65                    | _    | ns   |                                       |

| Carry (CAR) output delay time | t <sub>CAR</sub> | CAR, CL2                             | _                     | 155  | ns   | 2                                     |

| M phase difference time       | t <sub>CM</sub>  | M, CL2                               | _                     | 300  | ns   |                                       |

| CL1 cycle time                | t <sub>CL1</sub> | CL1                                  | t <sub>CYC</sub> × 50 | _    | ns   |                                       |

|                               |                  |                                      |                       |      |      |                                       |

Notes: 1.  $t_r$ ,  $t_f < (t_{CYC} - t_{CWH} - t_{CWL})/2$  and  $t_r$ ,  $t_f \le 50$  ns

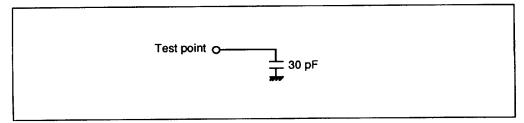

2. The load circuit shown in figure 8 is connected.

#### HITACHI

Figure 8 Load Circuit

Figure 9 LCD Controller Interface Timing

736 **HITACHI**■ 4496204 0046532 63T ■