# HDAC7545A

# **CMOS, 12-BIT BUFFERED MULTIPLYING DAC**

# **FEATURES**

- Improved Version of the AD7545

- Low Gain Error <2 LSB</li>

- · Low Output Capacitance (<75 pF)

- 500 ns Settling Time

- · 12-Bit Linearity Over Temperature

- · 8 or 16-Bit Bus Compatibility

#### **APPLICATIONS**

- · µP Controlled Gain Circuits

- μP Controlled Function Generation

- Bus Structured Instruments

- μP Based Control Systems

### **GENERAL DESCRIPTION**

The HDAC754A is a monolithic, low cost, multiplying 12-bit digital-to-analog converter (DAC) designed for direct microprocessor interface. It is compatible with the industry standard 7545 but has significant performance improvements in speed and gain accuracy. The HDAC7545A is fabricated in a three-micron, polysilicon gate BEMOS process and operates from a single +5 V (maximum) supply. Excellent linearity and gain accuracy are achieved through the use of laser-trimmed thin film resistors. Latch-up immunity is ensured by the use of an epi process base. This eliminates the need for external Schottky clamping diodes for latch-up protection.

The HDAC7545A incorporates a parallel loading architecture for the DAC conversion bits. When pins  $\overline{CS}$  and  $\overline{WR}$  are low, the 12 input data registers read the bus data. The single load and convert operation allows one-cycle updating by 16-bit microprocessors.

With direct parallel bus data loading, the HDAC7545A is ideally suited for microprocessor-based instruments and industrial or process controllers.

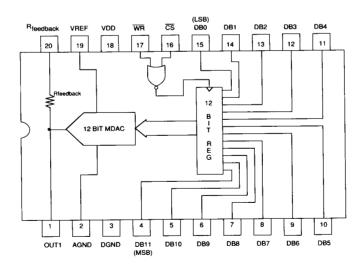

# **BLOCK DIAGRAM**

SPT

# ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur) 25 °C

| Supply Voltages         V <sub>DD</sub> to GND         +7 V           AGND to GND         -0.3 to V <sub>DD</sub> Input Voltages         V <sub>Rieedback</sub> to GND         ±25 V           Digital Input Voltage to GND         0.3 to V <sub>DD</sub> Outputs | Temperature Operating Temperature, ambient55 to +125 °C junction+150 °C Lead Temperature, (soldering 10 seconds)+300 °C Storage Temperature65 to +150 °C Power Dissipation (Any Package) to +75 °C450mW |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Outputs V <sub>out1</sub> to GND0.3 V to V <sub>DD</sub>                                                                                                                                                                                                           | (Derates above +75 °C by 6 mW/°C)                                                                                                                                                                       |

Note 1: Operation at any Absolute Maximum Rating is not implied. See Operating Conditions for proper nominal applied conditions in typical applications.

# **ELECTRICAL SPECIFICATIONS**

$T_A=T_{MIN}$  to  $T_{MAX}$ ,  $V_{DD}=+5$  V;  $V_{REF}=+10$  V, OUT1=0 V, AGND=DGND, unless otherwise specified.

| TEST                                                                                                    | TEST                                        | TEST   | TEST HDAC7545A |       |         | HD   | HDAC7545AA |         | HDAC7545AB    |       |         | Γ          |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------|--------|----------------|-------|---------|------|------------|---------|---------------|-------|---------|------------|

| PARAMETERS                                                                                              | CONDITIONS                                  | LEVEL  | MIN            | NOM   | MAX     | MIN  | NOM        | MAX     | MIN           | NOM   | MAX     | UNITS      |

| DC ELECTRICAL CHARAC                                                                                    | CTERISTICS                                  |        |                |       |         |      |            |         | <del></del> - |       |         |            |

| Resolution                                                                                              |                                             | ı      |                | 12    |         |      | 12         |         |               | 12    |         | Bits       |

| Relative Accuracy                                                                                       |                                             | I      | 5              | ±.25  | +.5     | 5    |            | +.5     | -1            |       | +1      | LSB        |

| Differential Nonlinearity                                                                               |                                             | ı      | 5              | ±.25  | +.5     | 5    |            | +.5     | -1            |       | +1      | LSB        |

| Gain Error                                                                                              | 25 °C                                       | ı      | 5              |       | +.5     | -2   |            | +2      | -3            |       | +3      | LSB        |

| Using Internal R <sub>feedback</sub>                                                                    | Tmin - Tmax                                 |        | -1.5           |       | +1.5    | -3   |            | +3      | -4            |       | +4      | LSB        |

| Gain Temperature<br>Coefficient                                                                         |                                             | IV     |                | 0.3   | 3       |      | 0.3        | 3       |               | 0.3   | 3       | ppm/°C     |

| Output Leakage OUT14                                                                                    |                                             |        |                |       |         |      |            |         |               |       |         |            |

|                                                                                                         | 25 °C                                       | 1      | -5             |       | +5      | -5   |            | +5      | -5            |       | +5      | n <b>A</b> |

|                                                                                                         | 0-70 °C/-25 to +85 °C                       | 1      | -10            |       | +10     | -10  |            | +10     | -10           |       | +10     | nA         |

|                                                                                                         | -55 to +125 °C<br>All digital inputs at 0 V | ı      | -100           |       | +100    | -100 |            | +100    | -100          |       | +100    | nA         |

| Reference Input Resistance                                                                              | Pin 19 to GND                               |        |                |       |         |      |            |         |               | _     |         |            |

| ,                                                                                                       | +25 °C                                      | l iv l | 7              | 12.5  | 18      | 7    | 12.5       | 18      | 7             | 12.5  | 18      | kΩ         |

|                                                                                                         | Temp. Coefficient                           | ΙV     |                | -180  |         | ·    | -180       |         | •             | -180  | , ,     | ppm/°C     |

| DIGITAL INPUTS V <sub>IH</sub> (High Input Voltage)                                                     |                                             | 1      | 2.4            |       |         | 2.4  |            |         | 2.4           |       |         | v          |

| V <sub>IL</sub> (Low Input Voltage) I <sub>IN</sub> (Input Currents I <sub>IH</sub> , I <sub>II</sub> ) |                                             |        |                | ±.005 | 0.8     |      | . 005      | 0.8     |               |       | 0.8     | ٧.         |

| C <sub>IN</sub> (Input Capacitance)                                                                     | VIN=0 Volts                                 | ıv     |                | ±.005 | ±1<br>5 |      | ±.005      | ±1<br>5 |               | ±.005 | ±1<br>5 | μA<br>pF   |

# **ELECTRICAL SPECIFICATIONS**

$\mathsf{T_{A}\text{=}}\mathsf{T_{MIN}}\ \mathsf{to}\ \mathsf{T_{MAX}},\ \mathsf{V_{DD}\text{=}}\text{+}5\ \mathsf{V};\ \mathsf{V_{REF}\text{=}}\text{+}10\ \mathsf{V},\ \mathsf{OUT1\text{=}0}\ \mathsf{V},\ \mathsf{AGND\text{=}}\mathsf{DGND},\ \mathsf{unless}\ \mathsf{otherwise}\ \mathsf{specified}.$

| TEST                                        | TEST                                                                               | TEST  | HDAC754 | ΔΔ/G  | HDAC754 | 5AA | HDA   | C754 | SAB |         |

|---------------------------------------------|------------------------------------------------------------------------------------|-------|---------|-------|---------|-----|-------|------|-----|---------|

| PARAMETERS                                  | CONDITIONS                                                                         | LEVEL | MIN NON |       | MIN NOM |     | MIN N |      |     | UNITS   |

| l <sub>aa</sub> l                           | Logic Inputs                                                                       | 1     |         | 4     |         | 4   |       |      | 4   | mA      |

| l <sub>DD</sub>                             | at V <sub>IL</sub> or V <sub>IH</sub> 25 °C Logic Inputs at 0 V or V <sub>DD</sub> | ı     | 10      | 100   | 10      | 100 |       | 10   | 100 | μА      |

|                                             | T <sub>MIN</sub> to T <sub>MAX</sub>                                               | 1     |         | 500   |         | 500 |       |      | 500 | μА      |

| AC ELECTRICAL CHARACTE                      | RISTICS                                                                            |       |         |       |         |     |       |      |     |         |

| Propagation Delay <sup>5</sup>              |                                                                                    | IV    | 50      | 100   | 50      | 100 |       | 50   | 100 | ns      |

| Digital to Analog Glitch Impulse1           | V <sub>REF</sub> =AGND                                                             | IV    | 200     | 400   | 200     | 400 |       | 200  | 400 | nV-sec  |

| Multiplying Feedthrough Error               | V <sub>REF</sub> to V <sub>OUT</sub><br>V <sub>REF</sub> =±10 V<br>10 kHz Sinewave | IV    | 0.3     | 3 0.5 | 0.3     | 0.5 |       | 0.3  | 0.5 | mV(p-p) |

| Output Current Settling Time <sup>1,3</sup> |                                                                                    | IV    | 0.9     | 5 1.0 | 0.5     | 1.0 |       | 0.5  | 1.0 | µsес    |

| Capacitance OUT1                            | Digital Inputs=V <sub>IH</sub> WR=CS=0 V                                           | IV    |         | 75    |         | 75  |       |      | 75  | pF      |

| Capacitance OUT2                            | Digital Inputs=V <sub>IL</sub> WR=CS=0 V                                           | IV    |         | 30    | 1       | 30  |       |      | 30  | pF      |

| t <sub>CS</sub> (Chip select set-up time)   |                                                                                    | 1     | 60      |       | 60      |     | 60    |      | -   | ns      |

| t <sub>CH</sub> (Chip select hold time)     |                                                                                    | 1     | 0       |       | 0       |     | 0     |      |     | ns      |

| t <sub>wR</sub> ( pulse width)              | t <sub>cs</sub> ≥t <sub>wn</sub>                                                   | 1     | 100     |       | 100     |     | 100   |      |     | ns      |

| t <sub>DS</sub> (Data set-up time)          |                                                                                    | 1     | 50      |       | 50      |     | 50    |      |     | ns      |

| t <sub>DH</sub> (Data hold time)            |                                                                                    |       | 9       |       | 9       |     | 9     |      |     | ns      |

Note 1: OUT1 load: 100 Ω + 13 pF

Note 2: Digital inputs change from 0 V to V<sub>DD</sub> or V<sub>DD</sub> to 0 V

Note 3: Measured from falling edge of  $\overline{WR}$ . Note 4: Digital inputs  $\overline{WR}$  and  $\overline{CS}$  at 0 V.

Note 5: Measured from falling edge of WR to 90% of final output value.

| TEST LEVEL CODES                                                                                                                                  | TEST LEVEL | TEST PROCEDURE                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------------------------------------------------|

| All electrical characteristics are subject to the following con-                                                                                  | l          | 100% production tested at the specified temperature.                          |

| ditions:                                                                                                                                          | 11         | 100% production tested at $T_A = 25$ °C,                                      |

| All parameters having min/max specifications are guaran-<br>teed. The Test Level column indicates the specific device                             |            | and sample tested at the specified temperatures.                              |

| testing actually performed during production and Quality Assurance inspection. Any blank section in the data column                               | 111        | QA sample tested only at the speci-<br>fied temperatures.                     |

| indicates that the specification is not tested at the specified condition.                                                                        | IV         | Parameter is guaranteed (but not tested) by design and characterization data. |

| Unless otherwise noted, all tests are pulsed tests, therefore $\mathbf{T}_{_{\mathrm{I}}}=\mathbf{T}_{_{\mathrm{C}}}=\mathbf{T}_{_{\mathrm{A}}}.$ | V          | Parameter is a typical value for information purposes only.                   |

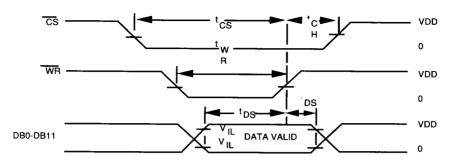

Figure 1 - Write Cycle Timing Diagram

#### **MODE SELECTION FOR FIGURE 1**

WRITE MODE: CS and WR low. DAC responds to

data inputs DB0-DB11.

HOLD MODE:  $\overline{CS}$  and  $\overline{WR}$  high. Data inputs DB0-DB11 are locked out; DAC holds last data present when  $\overline{CS}$  or  $\overline{WR}$

assumes high state.

#### **TERMINOLOGY**

#### **RELATIVE ACCURACY**

Relative accuracy or endpoint nonlinearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero and full scale and is expressed in percentage of full scale range or (sub)multiples of 1 LSB.

#### **DIFFERENTIAL NONLINEARITY**

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of 1 LSB (max) over the operating temperature range ensures monotonicity.

#### **GAIN ERROR**

Gain error or full-scale error is a measure of the output error between an ideal DAC and the actual device output. For the HDAC7545A ideal full-scale output is -(4095)/(4096)  $^{\bullet}(V_{\text{REF}})$ . Gain error is adjustable to zero using external trims as shown in figures 6 and 7 and in Table 1.

#### **OUTPUT LEAKAGE CURRENT**

Current which appears at OUT1 with the DAC loaded to all 0's.

# **MULTIPLYING FEEDTHROUGH ERROR**

AC error due to capacitive feedthrough from the  $V_{\text{REF}}$  terminal to OUT1 with the DAC loaded to all 0s.

#### **OUTPUT CURRENT SETTLING TIME**

Time required for the output of the DAC to settle to within 1/2 LSB for a given digital input stimulus, i.e., 0 to Full Scale.

#### **PROPAGATION DELAY**

This is a measure of the internal delay of the circuit and is measured from the time a digital input changes to the point at which the analog output at OUT1 reaches 90% of its final value.

#### DIGITAL TO ANALOG GLITCH IMPULSE

This is a measure of the amount of charge injected from the digital inputs to the analog outputs when the inputs change state. It is usually specified as the area of the glitch in nV-secs and is measured with  $V_{\rm per}$ =GND.

#### CIRCUIT DESCRIPTION

As shown in the block diagram, the HDAC7545A consists of a 12 bit multiplying DAC and a 12 bit data latch. Data at pins DB0 - DB11 are latched when both pins  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  are low. Current latched data establishes the digital-to-analog conversion code, therefore, conversion is actually controlled by pins  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$ . This is described further in the Interface Logic section.

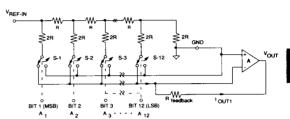

Figure 2A shows a simplified version of the 12-bit multiplying DAC circuitry. Note that the HDAC7545A uses a modified R-2R ladder technique that provides for superior linearity over similar devices which use the basic R-2R ladder.

A basic R-2R ladder portion is used within the HDAC7545A for the nine least-significant bits (bits 0-8). This ladder portion successively divides the remaining VREF input to produce a binary weighted nine-stage current division. In other words, in moving from left to right, each 2R resistor leg has half the current flow of the previous leg. Double-pole switches within each leg are controlled by the respective input data bit. The switches route the bit-weighted current of the leg to either analog ground or to the output (pin OUT1). OUT1 is a virtual ground by means of the external active circuitry. Hence, with every switch in either position, the R-2R ladder resistive integrity is maintained. Input resistance of pin VREF is kept constant.

Modification of the basic R-2R ladder structure occurs in the three most-significant bits. Here, the switches of seven equally weighted current dividers are controlled by bits 9-11 via a logic decoder. Although more complex, this method provides increased accuracy. Application of the HDAC7545A is identical to similar devices that use an unmodified R-2R ladder network.

The DAC output current is converted to a voltage by the feedback resistance composed of the external resistor shown in Figure 2A in series with internal resistor  $R_{\rm feedback}$ . The operational amplifier provides a buffered VOUT, and in combination with the feedback resistance maintains OUT1 at virtual ground. The transfer function of Figure 2B shows the relationship of VOUT for an equivalent R-2R resistor network, shown in the same figure. A more detailed explanation of the circuit operation and performance aspects is found in the following Equivalent Circuit Analysis section.

Figure 2A - Simplified Circuit Description

Figure 2B - Equivalent R-2R Network

The transfer function for the HDAC7545A connected in the multiplying mode as shown in figure 2B is:

$$V_0 = V_{IN} \times \left( \frac{A_1}{2^1} + \frac{A_2}{2^2} + \frac{A_3}{2^3} \cdot \cdot \cdot \frac{A_{12}}{2^{12}} \right)$$

in which  $A_x$  assumes a value of 1 for a HIGH bit and 0 for a Low bit.

#### **EQUIVALENT CIRCUIT ANALYSIS**

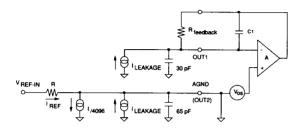

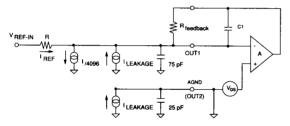

The equivalent output circuit of the HDAC7545A is the key to understanding offset, linearity and settling time. Figures 3 and 4 illustrate these effects.

In figure 3, the equivalent unipolar operation is illustrated with an external op-amp and all switches LOW to route all current to OUT2. OUT2 is internally connected to AGND in packaged versions of the HDAC7545A. The current from OUT2 is composed of (4095/4096)-th's of the input current at pin  $V_{\rm REF}$  plus parasitic leakage currents of the switches. These leakage currents are due to both junction and surface leakage on the MOS switches. 1/4096-th of the input current passes to the ground through the ladder terminal 2R resistor. OUT1 DC current is due only to switch leakage.

Figure 4 shows the same equivalent circuit when all switches are HIGH thereby routing all current to OUT1. The conditions are symmetrical in this case to figure 3.

The main effect of switch leakages in either case is an offset voltage from the DAC when used in voltage output mode as shown in figures 3 and 4.

Figure 3 - HDAC7545A DAC Equivalent Circuit

All Digital inputs Low

Figure 4 - HDAC7545A DAC Equivalent Circuit

All Digital Inputs High

The output resistance seen at the input terminals of the opamp varies with the code chosen. Between figures 3 and 4, resistance at each op-amp input can change from 10k Ohms to an open for extremes in code. This causes the gain of the offsets (due to either leakage currents of the DAC or op-amp offset) to be code dependent. For example, the gain of offsets of the op-amp under these extreme cases is given below:

Offset gain=1 + R<sub>feedback</sub>/RDAC

With all code bits LOW: RDAC >> R<sub>feedback</sub>; offset gain=1

With all code bits HIGH: RDAC= R<sub>tendback</sub>; offset gain=2

Thus, the offset is not amplified by a constant gain over the

range of code input. This variation in offset gain is seen as a nonlinearity in the voltage output over the full scale output. The magnitude of nonlinearity is the difference in the gains at code extremes times the offset voltage. In this DAC, this nonlinearity is equal to the offset itself. Thus, the total offset voltage of the op-amp plus leakage induced offset of the DAC and op-amp must be kept to less than 1 LSB to prevent degradation to the DAC linearity performance.

The dynamic output impedance of OUT1 and OUT2 is composed of the DAC switch capacitances to ground. OUT2 has the capacitance of the OFF switches while OUT1 has switch capacitance for ON switches.

The capacitance on OUT1 creates a feedback pole in the voltage output operation mode (figures 3 and 4). Instability of the output amplifier can occur due to the presence of this pole. This pole's instability effect is typically compensated by the use of a feedback capacitor - C1 (figures 6 and 7). Although all R-2R DAC's have the need for this type of compensation, the HDAC7545A maintains faster settling times when used in the voltage output mode. This is due to the lower output capacitance of the HDAC7545A.

The choice of compensation capacitor is bounded by three limits:

- C1 along with R<sub>leedback</sub> determines the settling time of the output voltage from the op-amp; therefore C1 should be as small as possible for minimum settling time.

- The pole defined by C1 and R<sub>feedback</sub> should be smaller than secondary poles in the op-amp: as a rule of thumb, about one half of the op-amp's gain-bandwidth.

- Settling time is proportional to √C<sub>OUT 1</sub>+ C1.

For an OP-27 used as an output op-amp with 8 MHz gainbandwidth, the choice of C1 is:

Fast settling time with small amounts of ringing are obtained when the small values of C1 (given by the criteria above) are as close as possible to the DAC output capacitance. The HDAC7545A 's low output capacitance comes much closer to fulfilling this goal than most other 7545 compatible DAC's. Thus, faster, more well controlled settling is seen with the HDAC7545A.

SPT

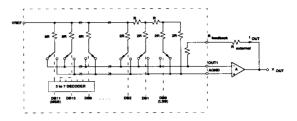

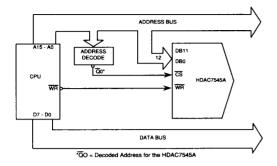

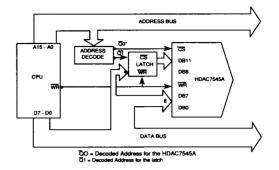

Figure 5 - Typical Microprocessor Bus Interfaces

MULTIPLEXED BUS ARCHITECTURE

SEPARATE ADDRESS/DATA BUS ARCHITECTURE

#### **INTERFACE LOGIC**

The HDAC7545A is designed to allow control of the output via a parallel microprocessor bus I/O. This section describes operation of the intrface controls to accomplish this.

A typical parallel bus I/O configuration is shown in figure 5. The microprocessor provides the DAC code as well as all control signals to load the code and update the analog output. During loading, the HDAC7545A accepts the DAC input code in a 12-bit word.

When the  $\overline{\text{CS}}$  pin is a logic 0, the input register of the HDAC7545A is enabled. The  $\overline{\text{WR}}$  input actually strobes the input data from the paralled bus into the HDAC7545A data register. This occurs on the falling edge of this  $\overline{\text{WR}}$  pulse. Figure 1, the Write Timing Diagram, defines the minimum setup and hold times required by the control lines to successfully transfer data in this fashion.

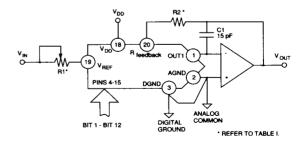

# UNIPOLAR BINARY OPERATION - 2 QUADRANT MULTIPLICATION

Figure 6 illustrates the use of the HDAC7545A in a unipolar (or 2 quadrant multiplication) mode. The  $V_{\rm REF}$  is applied from pin 19 to ground voltage or an input current can be applied to pin 19. Positive or negative voltages/current can be applied. The input is multiplied by (-1) times the DAC code scaling.

R1 can be used to provide full scale output trimming capability. The adjustment is made by selecting code 1111 1111 1111 and changing R1 for (4095/4096) of the  $V_{\rm REF}$  voltage out. If the source of  $V_{\rm REF}$  is adjustable,  $V_{\rm REF}$  could be directly

adjusted for full scale calibration. (See Table II.)

The output capacitance of OUT1 must be compensated as described in Equivalent Circuit Analysis by the use of C1 in the feedback path. This cancels the feedback pole caused by OUT1's capacitance.

The op-amp used with the HDAC7545A should be selected for low offset voltage and low bias currents to reduce offset and linearity errors as described in Equivalent Circuit Analysis. The op-amp's bias currents appear as errors in the same fashion as the DAC's leakage currents. The op-amp offset voltage should be less than approximately 10% of an LSB (of the output full scale voltage). This is due to the offset effect which is code dependent and contributes to the nonlinearity in proportion to its size with respect to full scale output voltage.

Figure 6 - Unipolar Binary Operation

SPT

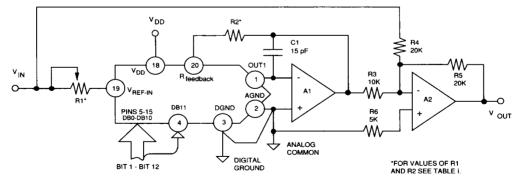

#### BIPOLAR OPERATION -4 QUADRANT MULTIPLICATION

The use of the HDAC7545A in a bipolar (or 4 quadrant multiplication) mode is illustrated in figure 7. The  $V_{\rm REF}$  is applied from pin 17 to ground voltage or an input current can be applied to pin 17. Positive or negative voltages/current can be applied. The output is either +1 or -1 times the code scaling of the DAC. The polarity is selected by the MSB of the DAC input code.

Amplifier A1's output is subtracted from 1/2 the value of V<sub>REF</sub> to produce a maximum output which is half of V<sub>REF</sub> in either polarity (see Table III for the exact scaling). The MSB of the DAC selects the polarity of the output.

Full scale calibration of the output can be made by adjusting R5 or the  $V_{\rm REF}$  source itself. Calibration of the zero output at code 1000 0000 0000 is made by adjusting R1. It is key that R3, R4 and R5 track each other for the stability of the summation made at A2. Failure of these resistors to track will result in both gain and offset drift over temperature even though calibration is done at room temperature.

As with unipolar operation, C1 is needed to compensate the OUT1 capacitance. A1 must be selected for low offset voltage and bias current to minimize nonlinearity and offset errors.

Table I - Recommended Trim Resistor Values vs Grades

|    | TRIM<br>RESISTOR |            |

|----|------------------|------------|

|    | "A" grades       | "B" grades |

| R1 | 20Ω              | 100Ω       |

| R2 | 6.8Ω             | 33Ω        |

Table II - Unipolar Binary Code Table for Circuit of Figure 4

| BINARY NUMBER IN DAC |      |      | ANALOG OUTPUT, V OUT                                     |

|----------------------|------|------|----------------------------------------------------------|

| MSB                  |      | LSB  |                                                          |

| 1111                 | 1111 | 1111 | $^{-V}$ IN $\left(\frac{4095}{4096}\right)$              |

| 1000                 | 0000 | 0000 | $-V_{IN} \left( \frac{2048}{4096} \right) = -1/2 V_{IN}$ |

| 0000                 | 0000 | 0001 | $-V$ IN $\left(\frac{1}{4096}\right)$                    |

| 0000                 | 0000 | 0000 | 0 Volts                                                  |

Table III - Bipolar Binary Code Table for Circuit of Figure 5

| MS  | BINARY NU<br>DAG<br>B |      | ANALOG OUTPUT, V OUT                        |

|-----|-----------------------|------|---------------------------------------------|

| 111 | 1 1111                | 1111 | +V <sub>IN</sub> ( 2047 / 2048 )            |

| 100 | 0000                  | 0001 | $+V_{1N} \left(\frac{1}{2048}\right)$       |

| 100 | 0000                  | 0000 | ov                                          |

| 011 | 1 1111                | 1111 | $-V$ IN $\left(\frac{1}{2048}\right)$       |

| 000 | 0000                  | 0000 | $^{-V}$ IN $\left(\frac{2048}{2048}\right)$ |

Figure 7 - Bipolar Operation

SPT

# **PIN ASSIGNMENT HDAC7545A**

#### OUT1 20 R feedback AGND 2 19 $v_{\mathsf{REF}}$ 18 DGND 3 $V_{DD}$ MSB DB11 17 WR HDAC7545A CS BIT 10 5 16 BIT 9 15 BIT 0 (LSB) BIT 1 BIT 8 7 14 13 BIT 2 BIT 7 12 BIT 3 BIT 6 BIT 4 BIT 5 11 10

# **PIN FUNCTIONS HDAC7545A**

| NAME | FUNCTION                 |

|------|--------------------------|

| OUT1 | Analog Current Output    |

| AGND | Analog Ground            |

| DGND | Digital Logic Ground     |

| DB11 | Input Data Bit 11 (MSB)  |

| DB10 | Input Data Bit 10        |

| DB9  | Input Data Bit 9         |

| DB8  | Input Data Bit 8         |

| DB7  | Input Data Bit 7         |

| DB6  | Input Data Bit 6         |

| DB5  | Input Data Bit 5         |

| DB4  | Input Data Bit 4         |

| DB3  | Input Data Bit 3         |

| DB2  | Input Data Bit 2         |

| DB1  | Input Data Bit 1         |

| DB0  | Input Data Bit 0 (LSB)   |

| cs   | Chip Select              |

| WR   | Data Write               |

| VDD  | Positive Power Supply    |

| VREF | Reference Input Voltage  |

| R    | Internal Feedback Resist |