### HYBRID TWO-SPEED TRACKING CONVERTER Resolution to 20 Bits; Any Speed Ratio

#### DESCRIPTION

The HSDC-360 is an application of the hybrid control transformer and data processor modules in the HSDC-14 to form a two-speed tracking converter. A circuit diagram with a list of discrete components is provided so that a crossover detector and other required circuit elements can be added to two standard hybrid control transformer modules and one standard data processor module. The additional components and their interconnections determine the speed ratio and resolution of the converter. The circuit for a 1 and 36 speed converter with 16 bit output is described in the data sheet; circuit diagrams for other speed ratios and resolutions will be supplied on request.

The HSDC-360 has most of the characteristics listed in the description of the HSDC-14, including ratiometric conversion, phase sensitive detection, broadband inputs, and DC analog velocity output. The power supply voltage ranges are the same, and the -15V power supply can also be eliminated with a trade-off reduction in the maximum tracking

The accuracy of the HSDC-360 depends on the speed ratio and resolution, and on whether standard or high-accuracy control transformers are used. For a 16 bit, 1 and 36 speed converter the accuracy can be as high as ±1.2 LSB, including the ±1 LSB quantizing error.

#### **APPLICATIONS**

The HSDC-360 may be used wherever analog angle data from a two-speed synchro or resolver system must be converted rapidly and accurately to digital form for transmission, storage, or analysis. Because of the small size, low weight, low power requirement, and high MTBF of its hybrid components, the HSDC-360 is well suited for remotely located and hard to access equipment. All hybrid modules are processed to MIL-STD-883 (burn-in is optional), and can be used in the most stringent industrial and military ground or avionics applications. Designed for printed circuit board mounting by standard techniques, the HSDC-14 can be readily incorporated into other equipment for computer control.

#### **FEATURES**

- THREE STANDARD HYBRID MODULES PLUS DISCRETE COMPONENTS WIRED BY **CUSTOMER TO DETERMINE** SPEED RATIO AND RESO-LUTION

- SIGNAL AND REF. INPUTS: Internal solid state isolation or external isolation transformers All common synchro and resolver L-L voltage levels and fre*quencies*

LOGIC:

TTL and CMOS compatible Up to 20 bit parallel binary angle output Converter Busy and Inhibit

POWER REQUIRED: ±15V DC and logic voltage supply

\*Patented

# **HSDC-360\***

I L C DATA DEVICE CORP 10E D 4678769 0005858 9

| SPECIFICATIONS                                                                      |                                                                                                            |                                                      | T-71-35-03                                                                            |  |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| Apply over reference amplitude                                                      | a, temperature, and power supply ranges; 10%                                                               | signal amplitude variation; and u                    | p to 10% harmonic distortion in the reference.                                        |  |  |

| PARAMETER                                                                           | VALUE                                                                                                      | PARAMETER                                            | VALUE                                                                                 |  |  |

| RESOLUTION                                                                          | 16 to 20 bits                                                                                              | 60 Hz TRANSFORMERS                                   | Date C. N. Const. and Malana Follows                                                  |  |  |

| ACCURACY                                                                            |                                                                                                            | Reference Transformer (Optiona<br>Input Options)     | l for Both Solid State and Voltage Follower                                           |  |  |

| Depends on Speed Ratio,                                                             | ±4 min (or 2 min) ±0.9 LSB                                                                                 | mpar options                                         |                                                                                       |  |  |

| Resolution and Whether                                                              | speed ratio ±0.9 LSB                                                                                       | Carrier Frequency Range                              | 47 — 440 Hz                                                                           |  |  |

| Option "a" (±2 min) Is                                                              |                                                                                                            | Input Voltage Range .                                | 80 – 138V rms; 115V rms nominal                                                       |  |  |

| Used                                                                                | 10 45 min 11 m 12 4 67                                                                                     | Input Impedance<br>Input Common Mode Voltage         | 600 KΩ min, resistive ±500V rms, transformer isolated                                 |  |  |

| Accuracy For 1:36 Speed Ratio and 16 Bit                                            | ±0.45 min with standard CT<br>±0.39 min with high accuracy CT                                              | Output Description                                   | +R (in phase with RH-RL) and ·R (in phase with                                        |  |  |

| Resolution                                                                          | 20.03 milit with high accuracy of                                                                          |                                                      | RL-RH) derived from op-amps. Short circuit proof.                                     |  |  |

|                                                                                     |                                                                                                            | Output Voltage                                       | 3.0V nominal riding on DC reference V. Output                                         |  |  |

| SPEED RATIO                                                                         | Any speed ratio can be accommodated                                                                        | Parisan Pagestrand                                   | voltage level tracks input level.  4 mA typ, 7 mA max from +15V supplies.             |  |  |

|                                                                                     | by an appropriate multiplier and angle offset made with discrete components.                               | Power Required                                       |                                                                                       |  |  |

|                                                                                     | Consult factory for circuit diagram.                                                                       | Signal Transformer                                   |                                                                                       |  |  |

|                                                                                     |                                                                                                            | Carrier Frequency Range                              | 47 — 440 Hz                                                                           |  |  |

|                                                                                     |                                                                                                            | Input Voltage Range                                  | 10 – 100V rms; L-L 90V rms L-L nominal                                                |  |  |

| SIGNAL AND REFERENCE INPUT                                                          |                                                                                                            | Input Impedance                                      | 148 K $\Omega$ min L-L balanced resistive e $\pm 500V$ rms, transformer isolated      |  |  |

| SOLID STATE BUFFER INPU                                                             | T (HSCT AND HRCT UNITS)                                                                                    | Output Description                                   | Resolver output ±sine (±S) and ±cosine (-C)                                           |  |  |

| Carrier Frequency Range                                                             | 47 1000 Hz                                                                                                 | Cutput Bescription                                   | derived from op-amps. Short circuit proof                                             |  |  |

|                                                                                     |                                                                                                            | Output Voltage                                       | 1.0V rms nominal riding on DC reference V.                                            |  |  |

| Synchro and Resolver Input Ch                                                       |                                                                                                            |                                                      | Output voltage level tracks input level.                                              |  |  |

| Voltage Options and Minimu<br>Input Impedance (Balanced                             |                                                                                                            | Power Required                                       | 4 mA type 7 mA max from +15V supply                                                   |  |  |

| impor impedance (balanced                                                           | Z <sub>IN</sub> Z <sub>IN</sub> Each                                                                       | DIGITAL INPUT/OUTPUT                                 |                                                                                       |  |  |

| Synchro (HSCT)                                                                      | Line to Line Line to Gnd                                                                                   | Logic Type                                           | TTL/DTL/CMOS compatible, depending on logic                                           |  |  |

| 90V L-L (Option H)                                                                  | 130 ΚΩ 85 ΚΩ                                                                                               |                                                      | supply voltage                                                                        |  |  |

| 11.8V L-L (Option                                                                   |                                                                                                            | Outputs                                              |                                                                                       |  |  |

| Resolver (HRCT)                                                                     | Z <sub>1N</sub> Z <sub>1N</sub> Z <sub>1N</sub> Z <sub>1N</sub> Each Single Ended Differential Line to Gnd | 14 Parallel Data Bits                                | Natural binary angle positive logic  1.5 — 3µs positive pulse, leading edge initiates |  |  |

| 90V L-L (Option H)                                                                  |                                                                                                            | Converter Busy (CB)                                  | counter update                                                                        |  |  |

| 26V L-L Option M)                                                                   | · ]                                                                                                        | Drive Capability                                     | 2 or 4 standard TTL loads                                                             |  |  |

| 11.8V L·L (Option                                                                   |                                                                                                            | Inhibit Input (INH)                                  | Z <sub>IN</sub> > 80 KΩ pull-up resistor to V <sub>M</sub>                            |  |  |

| Common Mode Range (DC Con                                                           | nmon Mode Plus Recurrent AC Peak)                                                                          | i                                                    | (VM = logic supply voltage or ±15 supply voltage,                                     |  |  |

| 90V L·L (Option H                                                                   | -Vs = 0V                                                                                                   |                                                      | See Interconnection Diagrams.)                                                        |  |  |

| 26V L-L (Option M                                                                   |                                                                                                            | ANALOG OUTPUTS                                       |                                                                                       |  |  |

| 11.8V L-L (Option                                                                   | •                                                                                                          | Internal D.C. Ref. (V)                               | +3.9 VDC nominal                                                                      |  |  |

|                                                                                     | 1                                                                                                          | AC Error Voltage (θ)                                 | 0.38 mV rms per LSB of error                                                          |  |  |

|                                                                                     |                                                                                                            | DC Érror Voltage (Ε) DC Velocity Voltage (θ)         | 1 VDC per : LSB of error                                                              |  |  |

| VOLTAGE FOLLOWER INPUT                                                              |                                                                                                            | For 16 Bit Resolution                                | +1.0V DC per +112°/sec at 400 Hz                                                      |  |  |

| Carrier Frequency Range                                                             | 47 1000 Hz                                                                                                 |                                                      | +1.0V DC per +28 '/sec at 60 Hz                                                       |  |  |

| Voltage Range<br>−Vs ≃ 0V                                                           | 1V rms nominal; 1.15V max; 0.1V min                                                                        | For Higher Resolutions                               | Scales according to number of bits. At 400 HZ                                         |  |  |

| V <sub>L</sub> = +6.2 and -V <sub>S</sub> = -7V                                     | 3V rms nominal; 3.5V max; 0.1V min                                                                         |                                                      | for instance, a 1.0V DC # output corresponds                                          |  |  |

| Max Voltage Without Damage                                                          | 15V rms continuous                                                                                         |                                                      | to 28 /sec at 16 bits and 7°/sec at 20 bits.                                          |  |  |

|                                                                                     | 100V peak transient                                                                                        | DYNAMIC CHARACTERISTICS                              |                                                                                       |  |  |

| Input Impedance                                                                     | ZIN > 10 MS (transient protected voltage follower)                                                         | Input Rate For Full Accuracy                         | İ                                                                                     |  |  |

|                                                                                     |                                                                                                            | For 16 Bit Resolution                                | 0.000                                                                                 |  |  |

|                                                                                     |                                                                                                            | At 400 Hz<br>At 60 Hz                                | 0 to · 2.5 rps min<br>0 to : 0.625 rps min                                            |  |  |

| TRANSFORMER CHARACTERIS                                                             | STICS (FOR HXCT UNITS)                                                                                     | For Higher Resolutions                               | Maximum input rate scales according to number o                                       |  |  |

| Reference Transformer                                                               |                                                                                                            | - S                                                  | bits: 1/4 at 18 bits, and 1/16 at 20 bits.                                            |  |  |

| Reference Transformer (Optional for Both Solid State and Transformer Input Options) |                                                                                                            | Velocity Constant                                    | Ky = ∞ (No limitation with Type II servo loop)                                        |  |  |

| Carrier Frequency Range                                                             | Option 4 = 360 — 1000 Hz                                                                                   | Acceleration Constant                                |                                                                                       |  |  |

| Voltage Range                                                                       | 18 – 130V                                                                                                  | At 400 Hz                                            | Ka = 58,000 sec <sup>-2</sup> nominal =                                               |  |  |

| Input Impedance                                                                     | 40 KΩ min                                                                                                  | At 60 Hz                                             | K <sub>a</sub> = 3,600 sec <sup>-2</sup> nominal                                      |  |  |

| Breakdown Voltage to                                                                | l                                                                                                          | Settling Time                                        |                                                                                       |  |  |

| GND                                                                                 | 1200V peak                                                                                                 | For Normal Tracking For 179" Step Change with        | No lag error up to specified input rates                                              |  |  |

| Signal Transformer                                                                  |                                                                                                            | 1:36 Speed Ratio                                     | 1                                                                                     |  |  |

|                                                                                     |                                                                                                            | At 400 Hz                                            | 270 msec typ to 1 LSB                                                                 |  |  |

| Carrier Frequency Range                                                             | (Dalaman)                                                                                                  |                                                      | 350 msec max to final value                                                           |  |  |

| Carrier Frequency Range Minimum Input Impedances                                    |                                                                                                            |                                                      |                                                                                       |  |  |

| Minimum Input Impedances                                                            | Synchro Z <sub>IN</sub> (Z <sub>so</sub> ) Resolver Z <sub>IN</sub>                                        | At 60 Hz                                             | 1080 msec typ to 1 LSB                                                                |  |  |

| Minimum Input Impedances (                                                          | Synchro Z <sub>IN</sub> (Z <sub>SO</sub> ) Resolver Z <sub>IN</sub> 180 KΩ 100 KΩ                          | At 60 Hz                                             | 1080 msec typ to 1 LSB<br>1400 msec max to final value                                |  |  |

| Minimum Input Impedances (<br>90V L-L (Option 4H)<br>26V L-L (Option 4M)            | Synchro Z <sub>IN</sub> (Z <sub>50</sub> )   Resolver Z <sub>IN</sub>   180 ΚΩ   100 ΚΩ   30 ΚΩ            |                                                      | 1400 msec max to final value                                                          |  |  |

| Minimum Input Impedances (                                                          | Synchro Z <sub>IN</sub> (Z <sub>SO</sub> ) Resolver Z <sub>IN</sub> 180 KΩ 100 KΩ                          | At 60 Hz  For 179 Step Change With Other Speed Ratio | 1 · · · · · · · · · · · · · · · · · · ·                                               |  |  |

I L C DATA DEVICE CORP LOE D

4678769 0005859 0

## T-71-35-03

#### TECHNICAL INFORMATION

#### INTRODUCTION

The applications information for the HSDC-360 has much in common with that for the HSDC-14, since the same control transformer and data processor modules are used. The HSDC-14 data sheet will be referenced frequently to avoid repeating information and diagrams.

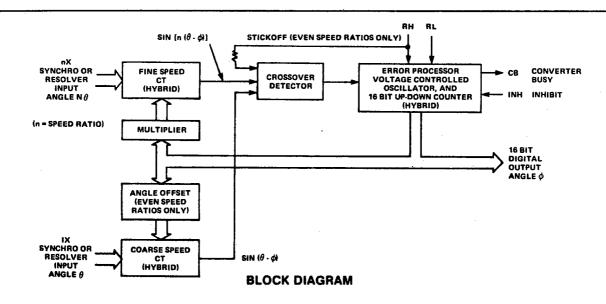

The block diagram shows the main components of the HSDC-360. The multiplier, angle offset, stickoff resistor, and crossover detector are composed of discrete components.

The operation of a two-speed S/D is essentially the same as a single speed except there are two control transformers (CT) which generate two error voltages. These two CTs are fed by a common up-down counter with the counter data multiplied by the speed ratio for the fine speed CT.

Assuming an off-null condition, as when the system is first energized, the crossover detector feeds the coarse (1X) CT error signal output to the demodulator and error processor. The converter seeks a null as it would for a single speed S/D. As null is approached (to within 2.5° nominally) the coarse CT output drops below a preset threshold and the crossover detector then switches the fine speed CT error signal into the demodulator and error processor. Since the counter angle  $\theta$  is multiplied by the speed ratio, the gradient of the fine speed CT is n times the coarse (1X) CT output. The servo loop then is able to seek an even finer null, using the fine speed CT error signal. The converter will continue to use the fine error signal for continuous tracking, swtiching back to the coarse signal only when the coarse error exceeds the crossover threshold. An angle offset and stickoff voltage are introduced in the coarse channel for even speed ratios in order to eliminate the false stable nulls which can occur when the fine and coarse speed angles are simultaneously at 180°.

#### **MODULE INTERCONNECTIONS**

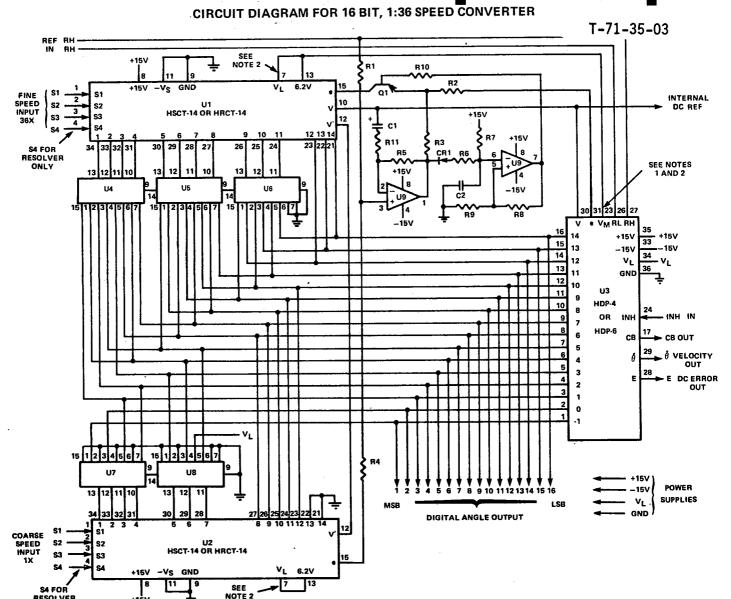

A circuit diagram and list of components for a 16 bit 1:36 speed converter are given to illustrate the most common resolution and speed ratio. Interconnection layout is not critical. The analog outputs are derived from op-amps, have low output impedance, and are short circuit proof.

The output drive capability can be either 2 or 4 standard TTL loads as indicated in the Notes. The penalty for 4 TTL load capability is that the Inhibit input, which is internally connected to  $V_M$  by an  $80~\mathrm{K}\Omega$  pull-up resistor, will be referenced to the

SIGNAL AND REFERENCE INPUTS AND TRANSFORMERS

+15V supply rather than to the logic supply voltage.

All information listed under this section heading in the HSDC-14 data applies. Note especially the protective voltage suppressors that must be installed on all 90V L-L solid state input modules to prevent voltage transients from destroying the input resistor networks.

#### **LOGIC INPUTS AND OUTPUTS**

Logic outputs consist of 16 to 20 parallel data bits and a Converter Busy (CB). These outputs are short circuit proof to ground or to positive voltages as high as  $V_L$ .

Information about the Inhibit (INH) is given in the corresponding section of the HSDC-14 data.

#### **ANALOG OUTPUTS**

The analog outputs are V, e, E, and  $\theta$ . V is an internal D.C. ground, +3.9V DC nominal, and is used as reference ground with the voltage follower buffer input option (HXDC). The other analog outputs, which ride on the D.C. reference V, are not used externally in normal operation.

The HSDC-14 data sheet describes the characteristics of the analog outputs e, E, and  $\dot{\theta}$ . The only difference for the HSDC-360 is the scaling for the velocity output  $\dot{\theta}$ . This scaling is given in the HSDC-360 specifications table.

#### **TIMING AND DYNAMIC PERFORMANCE**

The discussion and diagrams in the HSDC-14 data sheet concerning timing and dynamic performance apply to the HSDC-360 without modification.

E

#### NOTES:

RESOLVER

- 1. Digital output drive capability is normally 2 standard TTL loads. If logic supply  $V_L$  = +5V for TTL interface and 4 unit load capability is desired, disconnect pin 23 (VM) on U3 from 6.2V and connect it to +15V. Note that the Inhibit logic 1 is referred to VM.

- 2. If the external logic supply voltage VL is greater than 6.2V, do not connect pins 7 (VL) on U1, U2 and pin 23 (VM) on U3 to 6.2V. Instead, connect these three pins to the external logic supply V<sub>L</sub>.

- 3. If signal isolation transformers are required, use HXCT-14 for U1, U2. See Interconnection Diagram in HSDC-14 data sheet for signal and reference transformer connections.

#### PARTS LIST:

See ordering U1, U2 = DDC hybrid control Transformers U3 = DDC hybrid data processor information

U9 = 4558, dual op-amp

R1 = Coarse speed stickoff. Value depends on reference voltage level. R1 = 22 M $\Omega$ , 5% for 115V rms ref and R1 = 5.1 M $\Omega$ , 5% for 26V ref.

U4 - U8 = 4008, CMOS 4-bit adders. U4, U5, U6 form 36X multiplier U7, U8 form 1X angle offset

Coarse and fine speed loop gain

1% Resistors: R2 = 80.6 K $\Omega$ ; R3 = 100 K $\Omega$ , R4 = 10 K $\Omega$ ; R5 = 750 KΩ; R11 = 10 KΩ

$C1 = 10\mu F$ , 6V DC

Crossover Detector

5% Resistors: R6 = 1 K $\Omega$ ; R7, R8 = 1 M $\Omega$ , R9 = 200 K $\Omega$ ,  $R10 = 30 K\Omega$

$C2 = 0.1 \mu F \text{ ceramic; } CR1 \cdot 1N4148$

**Crossover Switch**

Q1 = 2N2946

### **HSDC-360\***

| I L C DATA DEVICE CORP LOE D 4678769 0005861 9 -                                           |                                                    |                                                                                    |                                                                                               |                                                                                                                                                     |  |  |

|--------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PARAMETER                                                                                  | VALUE                                              | PARAMETER                                                                          | VALUE                                                                                         | T-71-35-03                                                                                                                                          |  |  |

| TEMPERATURE RANGES Operating -1 option -3 option Storage                                   | -55°C to +125°C<br>0°C to +70°C<br>-55°C to +135°C | PHYSICAL CHARACTERISTIC<br>Converter Module and Data Pro<br>Type<br>Size<br>Weight | ocessor Module<br>36 pin double DIP                                                           | 36 pin double DIP<br>0.78 x 1.9 x 0.21 inch (2.0 x 4.8 x 0.53 cm)                                                                                   |  |  |

| POWER SUPPLIES  Nominal Voltage  Voltage Range  Absolute Max Voltage  Current or Impedance | +15 VDC                                            | vveignt                                                                            | (T1A and T2B) Re 0.8 x 0.6 x 0.3 inch 0.4 oz max (11 g) Encapsulated modul transformer each o | Encapsulated module. Signal transformer and reference transformer each consist of one such module 1.125 x 1.125 x 0.42 inch (2.86 x 2.86 x 1.07 cm) |  |  |

### ORDERING INFORMATION

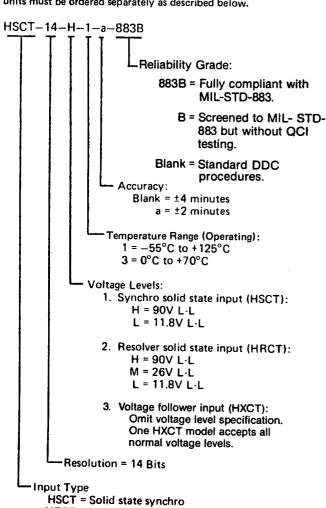

Order two hybrid control transformers and one hybrid data processor. DDC does not supply the discrete components for the angle multiplier, angle offset, and stickoff.

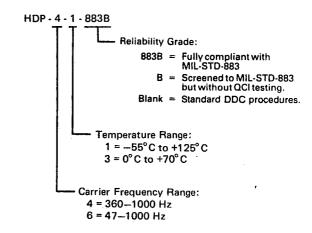

Order two control transformers as follows. These units operate over the full 47-1000 Hz frequency range. Transformers for HXCT-14 units must be ordered separately as described below.

HRCT = Solid state resolver

HXCT = Voltage follower buffer. Requires external signal conditioner such as

an isolation transformer.

2. Order one data processor as follows:

3. Isolation transformers for CT modules with voltage follower buffer inputs (HXCT-14) must be ordered separately by part number.

|          |           |         |         | Part Numbers |              |  |

|----------|-----------|---------|---------|--------------|--------------|--|

|          |           | Ref.    | L-L     |              | <u>-</u>     |  |

| Type     | Frequency | Voltage | Voltage | Ref. Xfmr.   | Signal Xfmr. |  |

| Synchro  | 400 Hz    | 115V    | 90V     | 21049        | 21045*       |  |

| Synchro  | 400 Hz    | 26V     | 11.8V   | 21049        | 21044*       |  |

| Resolver | 400 Hz    | 115V    | 90V     | 21049        | 21048*       |  |

| Resolver | 400 Hz    | 26V     | 26V     | 21049        | 21047*       |  |

| Resolver | 400 Hz    | 26V     | 11.8V   | 21049        | 21046*       |  |

| Synchro  | 60 Hz     | 115V    | 90V     | 24133        | 24126*       |  |

\*The part number for each 400 Hz synchro or resolver isolation transformer includes two separate modules as shown in the outline drawings.

#### **MECHANICAL OUTLINES**

Mechanical outlines, pin assignments, and schematic diagrams for the control transformer and error processor modules and for all transformers are available from the factory.

E