# H1802A/AC H1802BC

1800 CMOS Microprocessor Family Central Processing Unit

## MICROELECTRONICS CENTER

#### DESCRIPTION

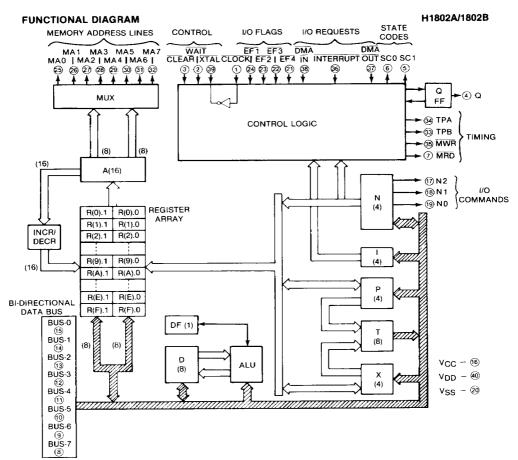

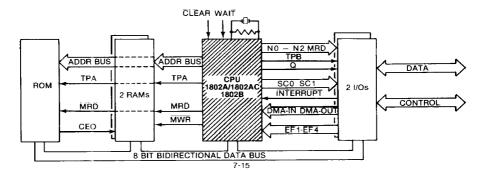

Hughes 1802A is an 8 bit register-oriented Central Processing Unit (CPU) designed for use as a general-purpose computing or control element in a wide range of stored program systems or products. The 1802A has a common bi-directional bus shared between all internal data, control, status and array registers. Accessing of memory is accomplished by time multiplexing a 16 bit address representing 65,536 locations into two sequentially transmitted bytes (8 bits). The presence of the most significant address bits is signified by the TPA clock. The 16x16 array of registers may be selected by the P,X, and N register designators to represent a program counter, data pointer and general pointer register respectively. Switching of programs may be readily accomplished by manipulating the register designators.

It has a flexible I/O interface including separate control signals (N0-N2) and memory access signals allowing direct memory data transfer with peripherals under CPU program control (through I/O instructions) or under peripheral control (DMA-IN and DMA-OUT signals). In addition to nonprogrammed Interrupt response, the CPU can monitor 4 flag inputs (EF1-EF4) from peripherals and set an output (Q) to the peripheral under program control. This may be used for serial data transfer or general control signals. State Codes (SC0-SC1) are available to monitor the CPU internal states.

The 1802A operates over a 4-10.5 voltage range while the 1802AC has a recommended 4-6.5 volts. The CPUs are available in a 40 lead dual-in-line ceramic package (D suffix), plastic package (P suffix), cerdip (Y suffix) or leadless chip carrier (L suffix). Devices in chip form (H suffix) are available upon request.

Hughes 1802BC (operating with 5 MHz Clock at 5V) is available for designs requiring higher system speed.

### **FEATURES**

- Instruction Cycle Time 2.5-3.75 µs at 6.4 MHz

- 8 Bit Parallel Data Organization

- . Memory Addressing to 65,536 Bytes

- . On Chip Direct Memory Access

- 16x16 General Purpose Register Matrix

- Four Flag Inputs and One Program-

- mable Output

Direct Memory to Peripheral Transfer on I/O Instructions

- T2L, NMOS and CMOS Compatible

- Optional On Chip Xtal Controlled Oscillator

- Low Power Single Voltage Supply

- 91 Instructions

- Schmitt Triggered Clear

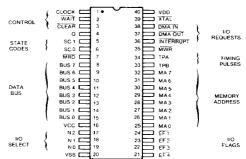

## PIN CONFIGURATION

## ARCHITECTURAL ORGANIZATION

N,X,P Registers — These three registers provide a 4 bit binary number which designates (selects) one of the registers in the register array to provide an address to memory. In addition, the N register holds device selection codes for input/output operations, and acts as a buffer for the lower 4 bits of the opcode.

**Q-Flip Flop** — This internal flip flop can be set or reset by instruction and can be sensed by conditional branch instructions. **Q** can also be used as a microprocessor output control.

Register Array — These 16 registers of 16 bit word size can be used to provide three separate functions: as program counters, as data pointers or as a scratch pad buffer. Each array register designated by N, X, or P provides a 16 bit memory address latched by the A register and multiplexed 8 bits at a time onto the memory address lines.

- Program Counter Any register may be used as the main program counter or as a subroutine program counter. This is determined by the user by setting the P register (4 bits) to point to any of the 16 array registers. When interrupts are serviced R(1) is used as the interrupt service routine program counter.

- Data Pointers Any array register may be selected by the N and X registers to provide the address of a data word location in memory. The N register selects an array register to provide addresses for several Load D from memory and Store D (accumulator) to memory instructions. The X register can also select array registers to provide addresses of memory data used in ALU operations and Input/Output operations, and additional Load from Memory and Store to Memory instructions with the D register.

- Data Register The N register also selects an array register location to act as a scratch pad buffer for data exchange with the D register. Data is transferred by a set of four instructions which select the high order byte R(N).1, or the low order byte R(N).0. Additionally an array register may be incremented or decremented for usage as loop counters.

## INTERFACE MODES -

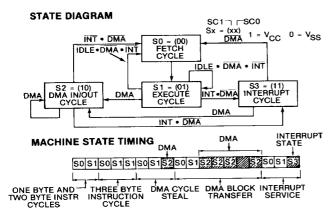

There are three modes of peripheral data transfer in the 1802A. These are programmed I/O, Interrupt Servicing, and Direct Memory Access.

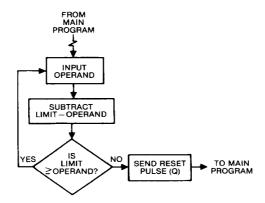

- Programmed I/O The 1802A provides a direct memory to peripheral device interface. The N0-N2 lines select a peripheral device while the memory address lines access a memory location. On Input instructions the peripheral data is read into the D register and memory simultaneously. On Output instructions the memory data is sent directly to the peripheral device. The EF flags and Q output can be used as additional programmable controls or as a serial data transfer path.

- Interrupt Servicing Upon the completion of an instruction, a non-masked (enabled) interrupt request will be acknowledged by the 1802A. This results in the saving of the present X and P register values in the T register, resetting the Interrupt Enable flip flop, and setting of X to point to Register 2 and P to Register 1. At the end of an Interrupt routine, a Return instruction restores old values of X and P and allows reactivation of the Interrupt Enable flip flop.

- Direct Memory Access The DMA mode is entered at the end of the execute machine cycle in the

currently held instruction. This is a special extension of programmed input/output. When a DMA-In

or DMA-Out request is activated, array register R(0) provides the location in memory for data

transfer. On each byte transfer R(0) is incremented. The DMA mode can also be used to initially

load memory after Reset and eliminates the requirement for specialized "bootstrap" load programs.

## 1802A REGISTER SUMMARY

| REG. | NO. OF | DESCRIPTION                                            |

|------|--------|--------------------------------------------------------|

| D    | 8      | DATA REGISTER (ACCUMULATOR)                            |

| DF   | 1      | DATA FLAG (ALU CARRY/BORROW)                           |

| R    | 16     | 1 OF 16 SCRATCHPAD REGISTER                            |

| Р    | 4      | DESIGNATES WHICH REGISTER IS PROGRAM COUNTER           |

| Х    | 4      | DESIGNATES WHICH REGISTER IS DATA OR STACK POINTER     |

| N    | 4      | HOLDS LOW ORDER INSTRUCTION DIGIT/DESIGNATES DATA PTR  |

| 1    | 4      | HOLDS HIGH ORDER (OP CODE) INSTRUCTION DIGIT           |

| Т    | 8      | HOLDS OLD X, P VALUES AFTER INTERRUPT (X IS HIGH BYTE) |

| IE   | 1 1    | INTERRUPT ENABLE FLIP FLOP                             |

| Q    | 1      | OUTPUT FLIP FLOP                                       |

## **ABSOLUTE MAXIMUM RATINGS**

DC SUPPLY-VOLTAGE RANGE (VCC, VDD) (All voltage values referenced to VSS terminal)

VGC ≤ VDD:

INPUT VOLTAGE RANGE, ALL INPUTS VSS-0.3V to VDD+0.3V those indicated in the operational sec-DC INPUT CURRENT, ANY ONE INPUT ± 10mA those indicated in the operational sec-tions of this specification is not im-OPERATING TEMPERATURE RANGE (TA) CERAMIC PACKAGE . -55 to + 125°C

PLASTIC PACKAGE . . -40 to + 85 °C STORAGE TEMPERATURE RANGE (Tstg) .....-65 to + 150 ℃

STATIC ELECTRICAL CHARACTERISTICS at  $T_A = -55$  to +125°C, except as noted.

NOTE: Operating the device above the "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above plied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

|                                                                           | _   GI      | MOITION  | <b>45</b> |                  |                    | MITS A     | T IMDIÇA | ITEO TEI           | PERAT | URES (9 | 9                  | 7,37 |       |

|---------------------------------------------------------------------------|-------------|----------|-----------|------------------|--------------------|------------|----------|--------------------|-------|---------|--------------------|------|-------|

|                                                                           | Va          |          | Yes       | $[\cdot, \cdot]$ | 18028              |            | لبناء    | 180240             | 周劃    |         | 18020C             |      |       |

| CHARACTERIBITES                                                           | 70<br>(8)   | (4)      | 10        | in the same      | Typ.7              | Mex.       | Min.     | Typ."              | Max.  | Min.    | Тур.*              | Max. | UNITS |

| Quiescent Device                                                          | -           | -        | 5         | _                | 0.01               | 100        | -        | 0.02               | 400   | -       | 0.02               | 400  |       |

| Current, IL Max. 5                                                        |             |          | 10        |                  | 1                  | 400        | -        | -                  | -     |         | -                  |      | μА    |

| Output Low Drive                                                          | 0.4         | 0,5      | 5         | 1.1              | 2.5                | -          | 1.1      | 2.5                | _     | 1.1     | 2.5                | _    |       |

| (Sink) Current,<br>IOL Min<br>(Except Xtal)                               | 0.5         | 0,10     | 10        | 2.2              | 4.4                | _          | -        | -                  | 1     | _       | -                  | -    | mA    |

| Xtal Output                                                               | 0.4         | 5        | 5         | 180              | 360                | -          | 180      | 360                | _     | 180     | 360                | -    | μА    |

| Output High Drive                                                         | 4.6         | 0,5      | 5         | -0.27            | -0.80              | -          | -0.27    | -0.80              |       | -0.27   | -0.80              | _    | mA    |

| (Source Current)<br>IOH Min. (Except Xtal)                                | 9.5         | 0,10     | 10        | -0.55            | -1.2               |            |          | _                  |       | _       |                    |      |       |

| Xtal Output<br>IOH Min. ₅                                                 | 4.6         | 0        | 5         | -90              | -260               | -          | -90      | -260               | -     | -90     | -260               | -    | μA    |

| Output Voltage                                                            | _           | 0,5      | 5         | _                | 0                  | 0.1        |          | 0                  | 0.1   |         | 0                  | 0.1  |       |

| Low Level<br>V <sub>OL</sub> Max. <sub>4</sub>                            | -           | 0,10     | 10        | -                | 0                  | 0.1        | _        |                    | -     | -       | -                  | -    |       |

| Output Voltage                                                            |             | 0,5      | 5         | 4.9              | 5                  | _          | 4.9      | 5                  | -     | 4.9     | 5                  | -    |       |

| High Level.<br>VOH Min.₄                                                  | -           | 0,10     | 10        | 9.9              | 10                 | -          | -        | -                  |       | _       |                    |      |       |

| Input Low Voltage                                                         | 2.5 2.5     | _        | 5         | -                | -                  | 1.5        | -        | _                  | 1.5   | _       | _                  | 1.5  | v     |

| V <sub>IL</sub> Max.                                                      | 0.5, 4.5    | _        | 5, 10     |                  | _                  | 1          | _        | _                  | 1     | _       | _                  | t    |       |

|                                                                           | 5, <b>5</b> | _        | 10        |                  |                    | 3          | _        | _                  |       |         | _                  | -    |       |

| Input High Voltage                                                        | 2.5, 2.5    | -        | 5         | 3.5              | -                  | -          | 3.5      | -                  |       | 3.5     |                    |      |       |

| V <sub>IH</sub> Min.                                                      | 0.5, 4.5    | -        | 5, 10     | 4                | _                  | _          | 4        | -                  |       | 4       | -                  |      |       |

|                                                                           | 5, <b>5</b> | -        | 10        | 7                | _                  | _          | _        | -                  | _     | -       | -                  |      |       |

| Input Leakage<br>Current                                                  | Any         | 0.5      | 7         | _                | ± 10 <sup>-4</sup> | <u>+</u> 1 |          | · 10 <sup>-4</sup> | + 1   |         | ± 10 <sup>-4</sup> | 1    | uА    |

| IN Max.5                                                                  | Input       | 0,10     | 11        | _                | ± 10 <sup>-4</sup> | ÷ 1        | _        |                    |       | -       | _                  |      | μ     |

| 3-State Output                                                            | 0.5         | 0,5      | 5         |                  | ± 10⁻⁴             | ± 1        | -        | 10-4               | - 1   |         | ± 10 <sup>-4</sup> | -1   | μA    |

| Leakage Current.<br>IOUT Max. 5                                           | 0.10        | 0, 10    | 10        | -                | ± 10 <sup>-4</sup> | + 1        | _        | -                  |       | -       |                    | -    | μ~    |

| Minimum Data<br>Retention<br>Voltage, V <sub>DR 4</sub>                   | v           | DD = VD  | PR .      | -                | 2                  | 2.4        | -        | 2                  | 2.4   | _       | 2                  | 2.4  | ٧     |

| Data Retention<br>Current, IDR 4                                          | ٧           | DD = 2.4 | IV        | -                | 0.1                | 1          | ~        | 0.5                | 5     | _       | 0.5                | 5    | μА    |

| Effective Input<br>Capacitance, C <sub>IN</sub><br>Any Input <sub>4</sub> |             | _        |           | _                | 5                  | 7.5        | -        | 5                  | 7.5   | -       | 5                  | 7.5  | pF    |

| Effective 3-State<br>Terminal Capaci-<br>tance Data Bus <sub>4</sub>      |             | -        |           | _                | 10                 | 15         | _        | 10                 | 15    | _       | 10                 | 15   | ρF    |

<sup>\*</sup>Typical Values are for TA = 25 C and Nominal VDD

H1802A/1802B

# RECOMMENDED OPERATION CONDITIONS at TA = -55 to +125°C Unless Otherwise Specified

| CHARACTER 1                                                                          | 765 m  | Yes    |            |            |            | in parts   |  |

|--------------------------------------------------------------------------------------|--------|--------|------------|------------|------------|------------|--|

| Supply-Voltage Range                                                                 | _      | _      | 4 to 10.5  | 4 to 6.5   | 4 to 6.5   | ٧          |  |

| Input Voltage Range                                                                  | -      | _      | VSS to VDD | Vss to Vpp | VSS to VDD | V          |  |

| Maximum Clock Input Rise or Fall Time, t <sub>r</sub> or t <sub>f</sub> <sup>4</sup> | 4-10.5 | 4-10.5 | 1          | 1          | 1          | μs         |  |

| Minimum                                                                              | 5      | 5      | 5          | 5          | 3.2        |            |  |

| Instruction Time <sup>2,4</sup>                                                      | 5      | 10     | 4          | _          |            | μs         |  |

| (See Fig. 6)                                                                         | 10     | 10     | 2.5        |            | _          |            |  |

|                                                                                      | 5      | 5      | 400        | 400        | 625        |            |  |

| Maximum DMA Transfer Rate <sup>4</sup>                                               | 5      | 10     | 500        | _          | _          | KBytes/sec |  |

|                                                                                      | 10     | 10     | 800        | _          | _          |            |  |

|                                                                                      | 5      | 5      | DC - 3.2   | DC - 3.2   | DC - 5.0   |            |  |

| Maximum Clock Input Frequency,                                                       | 5      | 10     | DC - 4     | _          | _          | MHz        |  |

| f <sub>CL</sub> 3,4                                                                  | 10     | 10     | DC - 6.4   | _          | _          |            |  |

NOTE 1: V<sub>CC</sub> ≤ V<sub>DD</sub>: for 1802AC V<sub>DD</sub> = V<sub>CC</sub> = 5 volts.

NOTE 2: Equals 2 machine cycles - one Fetch and one Execute operation for all instructions except Long Branch and Long Skip, which require 3 machine cycles - one Fetch and two Execute operations.

NOTE 3: Load Capacitance (CL) = 50 pF.

NOTE 4: Design assured but not tested.

NOTE 5: Parameters guaranteed by other tests at -55°C

## NOTES:

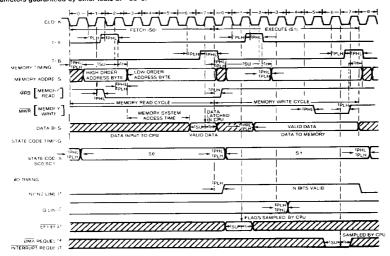

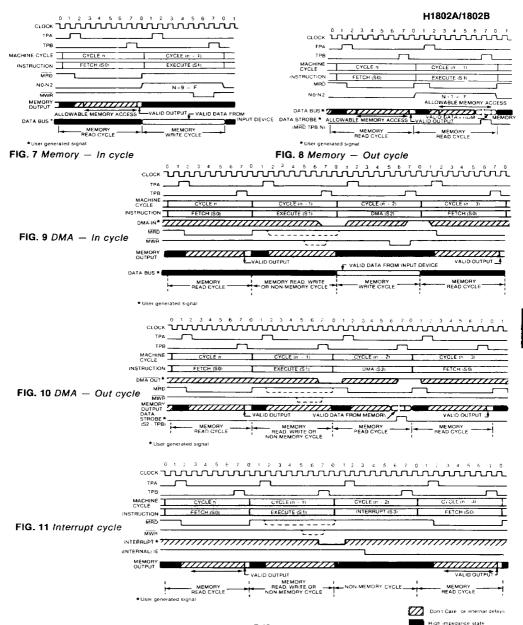

This timing diagram is used to show signal relationship only. All measurements are referenced to 50% point of the wave forms. Shaded areas Indicate "Don't Care" on Inputs or Undefined State on Outputs. Sample or setting action at clock is designated by an arrow.

- 1. The N0-N2 bits are valid during the S1 cycle of Input or Output instructions only (61-67 and 69-6F)

- 2. The Q line is set or reset during the S1 cycle of the SEQ or REQ instructions

- 3. The flag inputs (EF1-EF4) are sampled during an S1 cycle

- The DMA and Interrupt inputs are sampled during cycles S1, S2 or S3. The priority on concurrent signal inputs are (i) DMA-In (ii) DMA-Out and (iii) Interrupt.

Figure - 1 General Timing Diagram

# DYNAMIC ELECTRICAL CHARACTERISTICS at TA = -55 to +125°C, VDD nominal

|                                     | , V <sub>55</sub> | 799     | Total Section | LIMITS |      | LINTS            |

|-------------------------------------|-------------------|---------|---------------|--------|------|------------------|

|                                     |                   | -       |               | 200    | 500  | 1 to 1 1 1 1 1 1 |

| ropagation Delay Time, tpLH, tpHL   | 5 5               | 5<br>10 | _             | 150    | 250  | ns               |

| Clock to TPA, TPB                   | 10                | 10      | _             | 100    | 190  |                  |

|                                     | 5                 | 5       | _             | 575    | 1100 |                  |

| Clock-to-Memory High Address Byte   | 5                 | 10      | -             | 350    | 600  | ns               |

| (Long Branch Instruction)           | 10                | 10      |               | 240    | 450  |                  |

|                                     | 5                 | 5       | _             | 220    | 350  |                  |

| Clock-to-Memory Low Address Byte 4  | 5                 | 10      | _             | 150    | 250  | ns               |

| Clock to Montory 200 Floations 2710 | 10                | 10      | -             | 100    | 160  |                  |

|                                     | 5                 | 5       |               | 220    | 360  |                  |

| Clock to MRD, tpLH, tpHL⁴           | 5                 | 10      | -             | 150    | 250  | ns               |

| CIOCK TO IMAD, APLAI APAL           | 10                | 10      | _             | 100    | 150  |                  |

|                                     | 5                 | 5       | _             | 190    | 300  |                  |

| Clock to MWR, tpLH, tpHL⁴           | 5                 | 10      | -             | 150    | 250  | ns               |

| CIOCK TO MITTIN, TPER, TPINE        | 10                | 10      | _             | 75     | 150  |                  |

|                                     | 5                 | 5       | _             | 310    | 480  |                  |

| Clock (CPU Data to Bus)4            | 5                 | 10      | _             | 250    | 350  | ns               |

| 2.00.1 (0. 0 22.11 11 22.7)         | 10                | 10      | _             | 150    | 220  |                  |

|                                     | 5                 | 5       | _             | 290    | 480  |                  |

| Clock to State Code 4               | 5                 | 10      | _             | 250    | 370  | ns               |

|                                     | 10                | 10      |               | 130    | 250  |                  |

|                                     | 5                 | 5       | _             | 250    | 400  |                  |

| Clock to Q ⁴                        | 5                 | 10      | -             | 150    | 300  | ns               |

|                                     | 10                | 10      |               | 115    | 180  | 1                |

|                                     | 5                 | 5       |               | 280    | 550  |                  |

| Clock to N (0-2), tpLH, tpHL⁴       | 5                 | 10      | _             | 200    | 400  | ns               |

| · ·· I LIV THE                      | 10                | 10      | _             | 130    | 250  |                  |

# TIMING SPECIFICATIONS as a function of T (T = 1/f Clock) at TA = 25°C

|                                         |     |       | - 1 - Maria - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - | ATS     | UNIT8 |

|-----------------------------------------|-----|-------|---------------------------------------------------|---------|-------|

| CHARACTERISTICS                         | Yes | YDD . | Sile.                                             | Typ*    |       |

| High Order Memory Address Byte          | 5   | 5     | 2T-550                                            | 2T-670  |       |

| Setup to TPA Time                       | 5   | 10    | 2T-350                                            | 2T-200  | ns    |

| t <sub>SU</sub>                         | 10  | 10    | 2T-200                                            | 2T-275  | 115   |

| 1802B                                   | 5   | 5     | 2T-350**                                          | 2T-670  | L     |

| High Order Memory Address Byte          | 5   | 5     | T/2-25                                            | T/2-15  |       |

| Hold after TPA Time <sup>4</sup> tH     | 5   | 10    | T/2-35                                            | T/2-25  | ns    |

| Troid actor 1777 Times                  | 10  | 10    | T/2-10                                            | T/2 + 0 |       |

| Low Order Memory Address Byte           | 5   | 5     | T-30                                              | T+0     | ns    |

| Hold after WR Time 4 tH                 | 5   | 10    | T-20                                              | T+0     |       |

| Troid ditor Title                       | 10  | 10    | T-10                                              | T+0     |       |

| CPU Data to Bus Hold                    | 5   | 5     | T-200                                             | T-150   |       |

| after WR Time <sup>4</sup> tH           | 5   | 10    | T-150                                             | T-100   | ns    |

|                                         | 10  | 10    | T-100                                             | T-50    | i     |

| Required Memory Access Time             | 5   | 5     | 5T-350                                            | 5T-220  |       |

| Address to Data 4 tACC                  | 5   | 10    | 5T-250                                            | 5T-150  | ns    |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 10  | 10    | 5T-150                                            | 5T-100  | 1     |

<sup>\*</sup>Typical values are for T<sub>A</sub> =25 °C and nominal V<sub>DD</sub>

\*\*Minimum value for 1802B  $t_{SU}$  is measured at +25 °C.

<sup>2</sup>T-350 ns insures 50 ns set-up at F = 5 MHz.

NOTE 4: Design assured but not tested.

## H1802A/1802B

# DYNAMIC ELECTRICAL CHARACTERISTICS (Cont'd) TA = 25°C

|                                                                |    | 196.1514 | IN. and the | NAME OF STREET |   |              |

|----------------------------------------------------------------|----|----------|-------------|----------------|---|--------------|

| Minimum Set Up and Hold Times, t <sub>SU,</sub> t <sub>H</sub> | 5  | 5        | 0           | -20            | - |              |

| Data Input Set Up4                                             | 5  | 10       | 0           | - 15           | - | ns           |

|                                                                | 10 | 10       | 0           | <b>– 10</b>    |   |              |

|                                                                | 5  | 5        | 240         | 150            | - |              |

| Data Input Hold⁴                                               | 5  | 10       | 125         | 100            | - | ns           |

|                                                                | 10 | 10       | 120         | 75             |   |              |

|                                                                | 5  | 5        | 50          | 0              | _ |              |

| DMA Set Up ⁴                                                   | 5  | 10       | 20          | 0              | - | ns           |

|                                                                | 10 | 10       | 20          | 0              | _ | 1            |

|                                                                | 5  | 5        | 250         | 150            | _ |              |

| DMA Hold ⁴                                                     | 5  | 10       | 200         | 100            | _ | ns           |

|                                                                | 10 | 10       | 125         | 75             | _ |              |

|                                                                | 5  | 5        | 0           | - 75           | _ |              |

| Interrupt Set Up 4                                             | 5  | 10       | Ŏ           | -50            | _ | ns           |

| monopi out op                                                  | 10 | 10       | Ŏ           | 25             | _ |              |

|                                                                | 5  | 5        | 180         | 100            |   | <u> </u>     |

| Interrupt Hold <sup>4</sup>                                    | 5  | 10       | 100         | 75             | _ | ns           |

| interrupt riolo                                                | 10 | 10       | 80          | 50             | _ |              |

|                                                                | 5  | 5        | 10          | -15            |   | <del> </del> |

| Wait Set Up 4                                                  | 5  | 10       | 10          | - 15<br>- 25   |   | ns           |

| wan set op                                                     | 10 | 10       | 10          | - 5            | _ | 113          |

|                                                                | 5  | 5        | 0           | 50             |   | <b></b>      |

| EF1-4 Set Up4                                                  | 5  | 10       | 0           | 30<br>30       | _ |              |

| EFT-4 Set Up                                                   | 10 | 10       | 0           | -30<br>-20     | _ | ns           |

|                                                                |    | <b>-</b> |             |                |   | <del> </del> |

| ====                                                           | 5  | 5        | 200         | 100            | _ |              |

| ĒF1-4 Hold ⁴                                                   | 5  | 10       | 150         | 75<br>50       | _ | ns           |

|                                                                | 10 | 10       | 100         | 50             |   |              |

| Minimum Pulse Width,                                           | 5  | 5        | 300         | 100            | - |              |

| Clear Pulse Width, tWL4                                        | 5  | 10       | 200         | 75             | - | ns           |

| Clear Fulse Wildfil, tWL                                       | 10 | 10       | 150         | 50             |   | <b></b>      |

|                                                                | 5  | 5        | 175         | 100            | - |              |

| Clock Pulse Width, tWL⁴                                        | 5  | 10       | 125         | 75             | - | ns           |

|                                                                | 10 | 10       | 80          | 50             |   |              |

| ypical Total Power Dissipation4                                | 5  | 5        | _           | 7.5            | _ |              |

| f=2.0 MHz                                                      |    | 1        |             |                |   | mW           |

| Idle "00" at M (0000),                                         | 10 | 10       | -           | 70             |   | 1            |

| $C_L = 50 \text{ pF}$ $f = 4.0 \text{ MHz}$                    |    |          |             |                |   |              |

## NOTE:

Typical values are for T<sub>A</sub> = 25°C and nominal V<sub>DD</sub>

Minimum characteristics are the values above which all devices function, i.e., data hold at 5 volts requires 200 msec. minimum to function over the temperature range but only 150 msec. at + 25°C.

Design assured but not tested.

### INSTRUCTION SUMMARY

In all registers bits are numbered from least significant bit (LSB) to most significant bit (MSB) starting with 0.

R(W) Indicates an array register designated by the W register where  $W = N_1X_1$ , or P. Example if

X = 3, array reg. R(3) addresses memory data.

R(W).0 Low order byte contents of R(W)

R(W).1 High order byte contents of R(W)

NO Least significant bit of N register

M(R(W)) Contents of Memory addressed by selected array register

Operation Notation: M(R(N))-D; R(N)+1

This is interpreted as the memory byte addressed by the array register

R(N) is loaded into the D reg., and the contents of R(N) are incremented by 1.

|                 | المثلما   | 12           | i maine |                           |                                                                                                                                                                                           |

|-----------------|-----------|--------------|---------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CODE            | 1000      | <b>STATE</b> | (de e   | : manustros               | DESCRIPTION OF OPERATION                                                                                                                                                                  |

| REGIS           | TER OPERA | TIONS        |         |                           |                                                                                                                                                                                           |

| 1N              | INC       | 1            | 2       | INCREMENT REGISTER N      | R(N)+1. The register selected by the hex digit in N is incremented by 1.                                                                                                                  |

| 2N              | DEC       | 1            | 2       | DECREMENT REGISTER N      | R(N) – 1. The register selected by the hex digit in N is decremented by 1.                                                                                                                |

| 60              | IRX       | 1            | 2       | INCREMENT REGISTER X      | R(X) + 1. The register selected by the hex digit in X is incremented by 1.                                                                                                                |

| 8N              | GLO       | 1            | 2       | GET LOW REGISTER N        | R(N).0→D. The low order byte of the register selected by N replaces the byte in the D register.                                                                                           |

| AN              | PLO       | 1            | 2       | PUT LOW REGISTER N        | D→R(N).0. The byte contained in the D register replaces the low order<br>byte of the register selected by N. D is not changed.                                                            |

| 9N              | GHI       | 1            | 2       | GET HIGH REGISTER N       | R(N).1 → D. The high order byte of the register selected by N replaces the byte in the D register.                                                                                        |

| BN              | PHI       | 1            | 2       | PUT HIGH REGISTER N       | D→R(N).1. The byte contained in the D register replaces the high order<br>byte of the register selected by N. D is unchanged.                                                             |

| MEMO            | RY REFERE | NCE OPE      | RATIONS |                           |                                                                                                                                                                                           |

| ON              | LDN       | 1            | 2       | LOAD VIA N                | $M(R(N)) \rightarrow D$ ; $N \neq 0$ . The memory byte addressed by the contents of the reg. selected by N, R(N), replaces the byte in the D reg. Memory is unchanged.                    |

| 4N              | LDA       | 1            | 2       | LOAD VIA N AND ADVANCE    | $M(R(N)) \longrightarrow D$ ; $R(N) + 1$ . The memory byte addressed by $R(N)$ replaces the byte in the $D$ reg. The memory address, $R(N)$ , is incremented. Memory is unchanged.        |

| FO              | LDX       | 1            | 2       | LOAD VIA X                | M(R(X))—D. The memory byte addressed by the contents of the reg. selected by X, R(X), replaces the byte in the D reg. Memory is unchanged.                                                |

| 72              | LDXA      | 1            | 2       | LOAD VIA X AND ADVANCE    | M(R(X)) — D; R(X) + 1. The memory byte addressed by R(X) replaces the byte in the D reg. The memory address, R(X), is incremented. Memory is unchanged.                                   |

| F8<br><b2></b2> | LDI       | 2            | 2       | LOAD IMMEDIATE            | M(R(P))—D; R(P)+1. The memory byte following the F8 instruction replaces the byte in the D reg. The program counter R(P) is incremented to point to the next instruction.                 |

| 5N              | STR       | 1            | 2       | STORE VIA N               | D→ M (R(N)). The byte in the D reg. replaces the memory byte addressed<br>by the contents of the reg. selected by X, R(X). D is unchanged.                                                |

| 73              | STXD      | 1            | 2       | STORE VIA X AND DECREMENT | $D\!=\!M(R(X));\;R(X)\!=\!1.$ The byte in the D reg, replaces the memory byte addressed by R(X). The memory address, R(X), is decremented. D is unchanged.                                |

| LOGIC           | OPERATIO  | NS           |         |                           |                                                                                                                                                                                           |

| F1              | OR        | 1            | 2       | OR MEMORY WITH D          | M(R(X)) OR D—≠D. The 8 bit contents of the D reg. are logically ORed with the contents of the memory byte addressed by R(X).                                                              |

| F9<br>(B2)      | ORI       | 2            | 2       | OR IMMEDIATE WITH D       | M(R(P)) OR D—D; R(P) • 1. The 8 bit contents of the D reg. are logically ORed with the memory byte following the F9 instruction. R(P) is incremented to point to the next instruction.    |

| F3              | ROX       | 1            | 2       | EXCLUSIVE OR              | M(R(X)) XOR D→D. The 8 bit contents of the D reg. are logically XORed with the memory byte addressed by R(X).                                                                             |

| FB<br>(B2)      | XRI       | 2            | 2       | EXCLUSIVE OR IMMEDIATE    | M(R(P)) XOR D→D; R(P)+1. The 8 bit contents of the D reg, are logically XORed with the memory byte following the FB instruction. R(P) is incremented to point to the next instruction.    |

| F2              | AND       | 1            | 2       | AND MEMORY WITH D         | M(R(X)) AND D→D. The 8 bit contents of the D reg. are logically ANDed with the memory byte addressed by R(X).                                                                             |

| FA<br>⟨B2⟩      | ANI       | 2            | 2       | AND IMMEDIATE WITH D      | M(R(P)) AND D → D; R(P) · 1. The 8 bit contents of the D reg are logically ANDed with the memory byte following the FA instruction. R(P) is incremented to point to the next instruction. |

(B2) - 2nd byte of instruction.

The DF flip flop can only be altered by arithmetic and shift operations.

After an add instruction, DF=1 denotes a carry has occurred.

After a subtraction instruction, DF=0 denotes a borrow. D is in Two's compliment form.

The syntax — "(NOT DF)" denotes the subtraction of the borrow.

- (110) bi) denotes the subtraction of the bollow.

## **INSTRUCTION SUMMARY (Continued)**

| 18         | 1               | Tell S       |        | 10.000242434 |                                                         |                                                                                                                                                                                                                                                                                                         |

|------------|-----------------|--------------|--------|--------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTRACTOR | da              | <b>'385</b>  |        |              |                                                         |                                                                                                                                                                                                                                                                                                         |

|            | F6              | SHR          | 1      | 2            | SHIFT D RIGHT                                           | SHIFT D RIGHT; LSB(D)→DF, 0 →MSB(D). The 8 bits in D reg. are shifted one bit position to the right. The original LSB of D reg. is placed in DF. A *O" is placed in the MSB of D.                                                                                                                       |

|            | 76              | SHAC<br>RSHR | 1      | 2            | SHIFT D RIGHT WITH CARRY<br>RING SHIFT RIGHT            | SHIFT D RIGHT; LSB(D) DF, DF MSB(D). The 8 bits in D are shifted one bit position to the right. The original LSB of D is placed in DF. The original content of DF is placed in MSB of D.                                                                                                                |

|            | FE              | SHL          | 1      | 2            | SHIFT D LEFT                                            | SHIFT D LEFT; MSB(D) DF, 0 LSB(D). The 8 bits in D are shifted one bit position to the left. The original MSB of D is placed in DF, A "0" is                                                                                                                                                            |

|            | 7E              | SHLC<br>RSHL | 1      | 2            | SHIFT D LEFT WITH CARRY<br>RING SHIFT LEFT              | placed in the LSB of D.  SHIFT D LEFT, MSR(D) → DF, DF → LSB(D). The 8 bits in D are shifted one bit position to the left. The original MSB of D is placed in DF. The original content of DF is placed in LSB of D.                                                                                     |

| Ì          | ARITH           | METIC OPE    | RATION |              |                                                         | ,                                                                                                                                                                                                                                                                                                       |

|            | F4              | ADD          | 1      | 2            | ADD MEMORY WITH D                                       | $M(R(X)) + D \longrightarrow DF_{*}D$ . The memory byte addressed by $R(X)$ is added to the                                                                                                                                                                                                             |

|            | FC<br>〈B2〉      | ADI          | 2      | 2            | ADD IMMEDIATE WITH D                                    | contents of the D reg. DF receives any carry generated from the addition. M(RIP): D—DFD, RIP): 1. The memory byte following the FC instruction is added to the D reg. DF receives any carry. R(P) is incremented to point to the next instruction.                                                      |

|            | 74              | ADC          | 1      | 2            | ADD MEM. WITH CARRY                                     | point to the rest instruction.  M(R(X))+D+DF→DF,D. The memory byte addressed by R(X) plus the content of DF are added to the D reg. DF receives any carry generated from the addition.                                                                                                                  |

|            | 7C<br>〈B2〉      | ADCI         | 2      | 2            | ADD IMMED. WITH CARRY                                   | M(R(P))-D+PF→DF,D, R(P)+1. The memory byte following the 7C instruction plus DF are added to the D reg. DF receives any carry, (R(P) points to the next instruction.                                                                                                                                    |

|            | F7              | SM           | 1      | 2            | SUBTRACT MEM FROM D<br>(2's Compliment)                 | D= M (R(X)) DF,D. The memory byte addressed by R(X) is subtracted from the D reg. Any resulting carry is stored in DF (DF=0 indicates a borrow).                                                                                                                                                        |

|            | FF<br>(B2)      | SMI          | 2      | 2            | SUBTRACT MEM. IMMED. FROM D (2's Compliment)            | D – M (R(P)) → DF,D; R(P)+1. The memory byte following the FF instruction is subtracted from the D reg. Any carry is stored in DF. R(P) points to the next instruction.                                                                                                                                 |

|            | 77              | SMB          | 1      | 2            | SUBTRACT MEMORY WITH<br>BORROW (1's Compliment +DF)     | D – M (R(X)) – (NOT DF) → DF,D. The memory byte addressed by R(X) plus the borrow indicator, DF, is subtracted from the D reg. Any resulting carry is stored in DF.                                                                                                                                     |

|            | 7F<br>〈B2〉      | SMBI         | 2      | 2            | SUB. MEM. IMMED. WITH BOR-<br>ROW (1's Compliment + DF) | D = M(R(P)) = NOT DF) → DF,D; R(P) - 1. The memory byte following the 7F instruction plus DF is subtracted from the D reg. Any carry is stored in DF. R(P) points to next instruction.                                                                                                                  |

|            | F5              | SD           | 1      | 2            | SUBTRACT D FROM MEMORY<br>(2's Compliment)              | M(R(X)) – D → DF,D. The 8 bit contents of the D reg. are subtracted from the memory byte addressed by R(X). DF receives any carry. Memory is unchanged.                                                                                                                                                 |

|            | FD<br>⟨B2⟩      | SDI          | 5      | 2            | SUB D FROM IMMEDIATE<br>(2's Compliment)                | M(R(P)) = D→DF,D; R(P)+1. The contents of the D reg, are subtracted from the memory byte following the PD instruction. DF receives any carry. R(P) points to the next instruction.                                                                                                                      |

|            | 75              | SDB          |        | 2            | SUB D WITH BORROW<br>(1's Compliment +DF)               | M(R(X)) – D – (NOT DF) ← DF.D. The contents of the D reg, plus DF are subtracted from the memory byte addressed by R(X). OF receives any carry, Memory is unchanged.                                                                                                                                    |

|            | 7D<br>⟨B2⟩      | SDBI         | 2      | 2            | SUB D WITH BORROW, IMMED.<br>(1's Compliment + DF)      | M(R(P)) – D – (NOT DF) → DF,D; R(P)+1. The D reg. plus $\overline{DF}$ are subtracted from the memory byte following the 7D instruction. DF receives any carry (R(P) points to the next instruction.                                                                                                    |

|            | BRANCI          | H OPERATI    | ONS    |              |                                                         | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                 |

| -          | 30              | BR           | 2      | 2            | UNCONDITIONAL BRANCH                                    | M(R(P))                                                                                                                                                                                                                                                                                                 |

|            | ⟨B2⟩<br>38      | NBR          |        | 2            | NO SHORT BRANCH                                         | the low order byte of the program counter R(P).  R(P)+1. The byte following the 38 instruction is always skipped. This in-                                                                                                                                                                              |

|            | 32<br><b2></b2> | BZ           | 2      | 2            | SHORT BRANCH IF D = 0                                   | struction may also be considered a SHORT SKIP. If D = 0, M(R(P)) $\rightarrow$ R(P)+0; ELSE R(P)+1. If each bit of the D reg. is "0" the byte following the 32 instruction replaces the low order byte of the program counter R(P). If D $\neq$ 0, R(P) is incremented to point to the following instru |

|            | 3A<br>〈B2〉      | BNZ          | 2      | 2            | SHORT BRANCH IF D #0                                    | If $D + 0$ , $M(R(P)) = R(P) + 0$ , ELSE $R(P) + 1$ . If any bit of the D reg. is "1" the immediate byte replaces the low order byte of $R(P)$ , if $D = 0$ , $R(P)$ points to the following instruction. All short branches below are similar in operation.                                            |

|            | 33<br><b2></b2> | BDF          | 2      | 2            | SHORT BRANCH IF DF =1                                   | The following instruction. An instruction less below are similar in operation. IF OF =1, M(R(P)) — R(P)-0; ELSE R(P) =1. This instruction may also be called a short branch if pos or zero (BPZ) or short branch if greater or equal (BGE).                                                             |

|            | 3B<br><b2></b2> | BNF          | ê      | 2            | SHORT BRANCH IF DF=0                                    | equal (BGE).<br>If DF=0, M(R(P)) $\rightarrow$ R(P)-0; ELSE R(P)+1. This instruction may also be called a short branch if minus (BM) or short branch if less (BL).                                                                                                                                      |

|            | 31<br>〈B2〉      | BQ           | 2      | 2            | SHORT BRANCH IF Q-1                                     | called a short branch it minus (BM) or short branch it less (BL).<br>IF $Q = 1$ , $M(R(P)) \rightarrow R(P) \cdot 0$ ; ELSE $R(P) \cdot 1$ .                                                                                                                                                            |

|            | 39<br>(B2)      | BNQ          | ž.     | 2            | SHORT BRANCH IF Q=0                                     | IF $Q=0$ , $M(R(P)) \longrightarrow R(P)\cdot 0$ ; ELSE $R(P)\cdot 1$ .                                                                                                                                                                                                                                 |

|            | 34<br><b2></b2> | 81           | 2      | 2            | SHORT BRANCH IF EF1=1                                   | IF EF1 = 1, M(R(P)) → R(P)-0; ELSE R(P) - 1.                                                                                                                                                                                                                                                            |

|            | 3G<br>(B2)      | BNI          | ž      | 2            | SHORT BRANCH IF EF1=0                                   | IF EF1 -0, M(R(P)) → R(P)-0; ELSE R(P) - 1.                                                                                                                                                                                                                                                             |

|            | 35<br><82>      | B2           | 2      | 2            | SHORT BRANCH IF EF2-1                                   | IF EF2+1, M(R(P)) → R(P)-0; ELSE R(P)+1.                                                                                                                                                                                                                                                                |

| '_         | \               |              |        |              |                                                         |                                                                                                                                                                                                                                                                                                         |

Instruction is associated with more than one mnemonics.

(B2) = 2nd byte of instruction.

All instructions require two machine cycles except Long Branches and Long Skips which take three machine cycles. Each machine cycle = 8 external clocks, i.e. @ 6.4 MHz, cycle =  $1.25\mu$ s.

EF = 1, if  $\overline{EF}$  input = 0 (GND).

# INSTRUCTION SUMMARY (Continued)

| cobe                                         | ************************************** | 411      |        |                                           | estation or or system.                                                                                                                                                                                                                                                                  |

|----------------------------------------------|----------------------------------------|----------|--------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3D 1                                         | BN2                                    | 2        | 2      | SHORT BRANCH IF EF2=0                     | IF EF2 = 0, M(R(P)) → R(P)-0; Else R(P) + 1.                                                                                                                                                                                                                                            |

| (B2) <sup>1</sup><br>36<br>(B2) <sup>1</sup> | В3.                                    | 2        | 2      | SHORT BRANCH IF EF3 = 1                   | IF EF3 = 1, M(R(P)) → R(P)-0; Else R(P) + 1.                                                                                                                                                                                                                                            |

| 3E<br>(B2)                                   | BN3,                                   | 2        | 2      | SHORT BRANCH IF EF3=0                     | IF EF3 =0, M(R(P))→ R(P)-0; ELSE R(P) + 1.                                                                                                                                                                                                                                              |

| 37<br>(B2)                                   | B4,                                    | 2        | 2      | SHORT BRANCH IF EF4=1                     | IF EF4 = 1, M(R(P)) → R(P)-0; Else R(P) - 1.                                                                                                                                                                                                                                            |

| 3F<br>(B2)                                   | BN4,                                   | 2        | 2      | SHORT BRANCH IF EF4=0                     | IF EF4 = 0, M(R(P)) → R(P)-0; Else R(P) + 1.                                                                                                                                                                                                                                            |

| (B2) <sup>1</sup>                            | LBR<br>⟨B3⟩                            | 3        | 3      | UNCONDITIONAL LONG<br>BRANCH              | $M(R(P)) \rightarrow R(P)-1$ , $M(R(P+1)) \rightarrow R(P)-0$ . The two bytes following the CO instruction always replace the high and low order bytes of the program counter $R(P)$                                                                                                    |

| C8 <sup>2</sup>                              | NLBR                                   | 1        | 3      | NO LONG BRANCH                            | R(P)+2. The next two bytes after the C8 instruction are always skipped. This instruction may also be considered a Long Skip.                                                                                                                                                            |

| C2<br><b2>1</b2>                             | LBZ<br>〈B3〉                            | 3        | 3      | LONG BRANCH IF D = 0                      | IF D = 0, M(R(P)→R(P)+1, M(R(P+1))→R(P)+0; Else R(P)+2. If all bits of the D reg, are '0", the two bytes following the C2 instruction replace the contents of the program counter, R(P). If not R(P) points to the next instruction All loop transfers hellow are similar in operation. |

| CA<br>(B2) <sup>1</sup>                      | LBNZ                                   | 3        | 3      | LONG BRANCH IF D # 0                      | If D not 0, M(R(P)) → R(P)-1, M(R(P + 1)) → R(P)-0. Else R(P) + 2.                                                                                                                                                                                                                      |

| (B2)1                                        | LBDF<br>(B3)                           | 3        | 3      | LONG BRANCH IF DF = 1                     | If $DF = 1$ , $M(R(P)) \rightarrow R(P) - 1$ , $M(R(P+1)) \rightarrow R(P) - 0$ ; Else $R(P) - 2$ .                                                                                                                                                                                     |

| (B2)1                                        | LBNF<br>(B3)                           | 3        | 3      | LONG BRANCH IF DF = 0                     | IF DF=0, M(R(P)) $\longrightarrow$ R(P)-1, M(R(P + 1)) $\longrightarrow$ R(P)-0; Else R(P) + 2.                                                                                                                                                                                         |

| C1<br>(82)1                                  | LBQ<br>(B3)                            | 3        | 3      | LONG BRANCH IF Q = 1                      | IF Q=1, M(R(P)) $\rightarrow$ R(P)-1, M(R(P+1)) $\rightarrow$ R(P)-0; Else R(P)+2.                                                                                                                                                                                                      |

| C9<br><b2> 1<br/>38<sup>2</sup></b2>         | LBNQ<br>(B3)                           | 3        | 3      | LONG BRANCH IF Q =0                       | $I Q = 0$ , $M[R(P)] \longrightarrow R(P) = 1$ , $M[R(P + 1)] \longrightarrow R(P) = 0$ ; Else $R(P) + 2$ .<br>R(P) + 1. Always skips the following byte. Also called No Short Branch                                                                                                   |

|                                              | SKP                                    | 1        | 2      | SHORT SKIP                                | (NBR). R(P)+1. Always skips the following byte. Also called No Short blanch R(P)+2. Always skips the following two bytes. Also called No Long                                                                                                                                           |

| C8 <sup>2</sup>                              | LSKP                                   | 1        | 3      | LONG SKIP                                 | Branch (NLBR).  IF D=0, R(P)+2; Else Continue, If all bits of D are "0", the next two bytes                                                                                                                                                                                             |

| CE                                           | LSZ                                    | 1        | 3      | LONG SKIP IF D=0                          | following the CE instruction are skipped. If not, they are accessed as the                                                                                                                                                                                                              |

| C6                                           | LSNZ                                   | 1        | 3      | LONG SKIP IF D + 0<br>LONG SKIP IF DF - 1 | IF D NOT 0, R(P)+2; Else Continue. IF DF = 1, R(P)+2; Else Continue.                                                                                                                                                                                                                    |

| CF<br>C7                                     | LSDF<br>LSNF                           | 1        | 3      | LONG SKIP IF DF = 0                       | IF DF = 0, R(P) + 2; Else Continue.                                                                                                                                                                                                                                                     |

| l cp                                         | LSQ                                    | i        | 3      | LONG SKIP IF Q = 1                        | IF Q-1, R(P)+2; Else Continue.                                                                                                                                                                                                                                                          |

| C5                                           | LSNQ                                   | 1        | 3      | LONG SKIP IF Q-0                          | IF Q = 0, R(P) + 2; Else Continue.                                                                                                                                                                                                                                                      |

| cc                                           | LSIE                                   | 1        | 3      | LONG SKIP IF IE - 1                       | IF IE = 1, R(P) - 2; Else Continue. 1E is interrupt enable.                                                                                                                                                                                                                             |

| co                                           | NTROL OPER                             | ATIONS   |        |                                           |                                                                                                                                                                                                                                                                                         |

| 00                                           | IDL                                    | 1        | 2      | IDLE (WAIT)                               | M(R(0)) → Bus. The processor repeats execute (S1) cycles until an I/O request (INTERRUPT, DMA-IN, or DMA-OUT) is asserted.                                                                                                                                                              |

| C4                                           | NOP                                    | 1        | 3      | NO OPERATION                              | The processor performs no change of status during this instruction.  N — P. The low order hex digit of the instruction is placed in the P                                                                                                                                               |

| DN                                           | SEP                                    | 1        | 2      | SET P                                     | register and designates which register is to serve as program counter,                                                                                                                                                                                                                  |

| EN                                           | SEX                                    | 1        | 2      | SET X                                     | N — X. The low order hex digit of the instruction is placed in the X register.                                                                                                                                                                                                          |

| 7B                                           | SEQ                                    | 1        | 2      | SET Q                                     | 1 → Q. Sets the Q flip flop to logic high. 0 → Q. Besets the Q flip flop to a logic low.                                                                                                                                                                                                |

| 7 <b>A</b><br>78                             | REQ<br>SAV                             | 1        | 2<br>2 | RESET Q<br>SAVE                           | 0 → Q. Hesets the Q hip hop to a logic low. T→ M(R X). The T reg. containing previous X and P information is stored in the memory location addressed by R(X).                                                                                                                           |

| 79                                           | MARK                                   | 1        | 2      | PUSH X, P TO STACK                        | If the helitory location audiesses $y = (X, P) + X_1 = 1$ . The current contents of $(X, P) + X_1 = 1$ . Then $P \to X_1 = 1$ . The current contents of $X$ and $P$ are stored in temporary reg. T and memory addressed by R(2). New $P$ is set equal to $X$ and $R(2)$ is decremented. |

| 70                                           | RET                                    | 1        | 2      | RETURN                                    | M(R(X))→(X,P), R(X)+1; 1—→1E. The memory byte addressed by R(X) replaces X and P contents. The memory address, R(X), is incremented                                                                                                                                                     |

| 71                                           | DIS                                    | 1        | 2      | DISABLE                                   | and IE is enabled. M(R(X)) → (X,P), R(X) · 1: 0 → IE. Same operation as RET except IE is disabled. Both RET and DIS are used primarily in                                                                                                                                               |

|                                              |                                        |          |        |                                           | returns from interrupt processing.                                                                                                                                                                                                                                                      |

| INF                                          | UT/OUTPUT (                            | PERATION | ıs     |                                           |                                                                                                                                                                                                                                                                                         |

| 6N                                           | OUT                                    | 1        | 2      | OUTPUT                                    | M(R(X)).→B <sub>US</sub> : R(X) + 1. N = 1 − 7. When N is 1 through 7, the memory byte addressed by R(X) is accessed and placed on the memory bus. The three low order bits of N are also placed on the N2 − N0 signal lines memory address. R(X) is incremented.                       |

| 6N                                           | INP                                    | 1        | 2      | INPUT                                     | Bus— $M(R(X))$ : Bus — $D$ . $N-9$ — $F$ . When $N$ is $9$ through $F$ a byte is input to the $D$ reg, and the memory location addressed by $R(X)$ . The low order $3$ Dits of $N$ are placed on the $N2$ — $N0$ signal line. $R(X)$ is not modified.                                   |

|                                              |                                        |          |        |                                           |                                                                                                                                                                                                                                                                                         |

NOTE:

1. Instruction associated with more than one mnemonic.

2. (82) 2nd byte of instruction (83) 3rd byte of instruction.

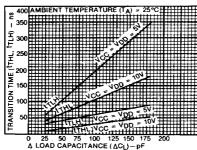

FIG. 2 Typical transition time vs. load capacitance.

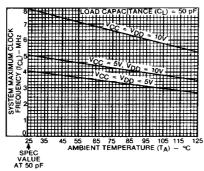

FIG. 4 Typical maximum clock frequency as a function of temperature.

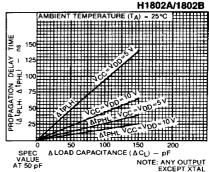

FIG. 3 Typical change in propagation delay as a function of a change in load capacitance.

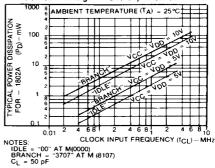

FIG. 5 Typical power dissipation as a function of clock frequency for Branch instruction and Idle instruction for 1802A.

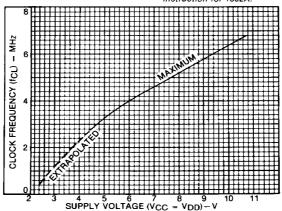

FIG. 6 Clock frequency is a function of supply voltage.

TABLE 1 — CONDITIONS ON DATA BUS AND MEMORY ADDRESS LINES DURING ALL MACHINE STATES

| STATE       |              | i di             |             |                              | Greaties .                                   |                    | 722                 | حفا | HOTE                                             |

|-------------|--------------|------------------|-------------|------------------------------|----------------------------------------------|--------------------|---------------------|-----|--------------------------------------------------|

| S1          | F            | ESET             |             |                              | JAM: I,N,Q,X,P=0 IE=1                        | 0                  | R(0)<br>UNDEFINED   | 1   | Α                                                |

|             |              |                  | CLE AFTER I | RESET<br>CCESSIBLE           | INITIALIZE                                   | 0                  | R(0)<br>UNDEFINED   | 1   | В                                                |

| S0          |              | FETCH            |             |                              | M(R(P))1,N R(P)+1                            | M(R(P))            | R(P)                | 0   | C_<br>D                                          |

|             | 0            | 0 IDL IDLE       |             | IDLE                         | [Load=0 (Program idle)] [Load=1 (Load Mode)] | M(R(0))            | PREVIOUS<br>ADDRESS | 0   | E                                                |

|             | 1            | N = 0            | LDN         | LOAD [D VIA N]               | M(R(N))→D                                    | M(R(N))            | R(N)                | 0   |                                                  |

|             | 1            | N                | INC         | INCREMENT                    | R(N)+1                                       | FLOAT              | R(N)                | 1   |                                                  |

|             | 2            | N                | DEC         | DECREMENT                    | R(N) - 1                                     | FLOAT              | R(N)                | 0   |                                                  |

|             |              |                  |             | SHORT                        | (BRANCH NOT TAKEN)                           | M(R(P))<br>M(R(P)) | R(P)                | 0   |                                                  |

|             | 3            | N N              | LDA         | BRANCH<br>LOAD ADVANCE       | (BRANCH TAKEN)<br>M(R(N))→D R(N)+1           | M(R(N))            | R(N)                | 0   |                                                  |

|             | <b>4</b> 5   | N N              | STR         | STORE VIA N                  | D→M(R(N))                                    | D D                | R(N)                | 1   |                                                  |

|             | 3            | 0                | IRX         | INC REG X                    | R(X) + 1                                     | M(R(X))            | R(X)                | 0   |                                                  |

|             | 6            | N=1-7            | OUT N       | OUTPUT                       | M(R(X))—→BUS R(X)+1                          | M(R(X))            | R(X)                | 0   |                                                  |

|             | 0            | N=9-F            | INP N       | INPUT                        | BUS→M(R(X)), D                               | I/O<br>DEVICE      | R(X)                | 1   |                                                  |

|             |              | 0                | RET         | RETURN                       | M((R)(X))—→(X,P)<br>R(X)+1;1—→IE             | M(R(X))            | R(X)                | 0   |                                                  |

|             |              | 1                | DIS         | DISABLE                      | M(R(X))→(X,P)<br>R(X)+1;0→1E                 | M(R(X))            | R(X)                | 0   |                                                  |

|             |              | 2                | LDXA        | LOAD VIA X<br>AND ADVANCE    | M(R(X)) → D<br>P(X) – 1                      | M(R(X))            | R(X)                | 0   |                                                  |

|             |              | 3                | STXD        | STORE VIA X<br>AND DECREMENT | D- M(R(X))<br>R(X)-1                         | D                  | R(X)                | 1   |                                                  |

|             | 7            | 4,5,7            | _           |                              | ALU OPERATION                                | M(R(X))            | R(X)                | 0   |                                                  |

|             |              | 6                | _           |                              | ALU OPERATION                                | FLOAT              | R(X)                | 1   |                                                  |

|             | ļ            | 8                | SAV         | SAVE                         | TM(R(X))                                     | т                  | R(X)                | 1   | -                                                |

|             |              | 9                | MARK        | MARK                         | (X,P) → T,M(R(2))<br>P→ X;R(2) − 1           | т                  | R(2)                | 1   |                                                  |

|             |              | A                | REQ         | RESET Q                      | Q=0                                          | FLOAT              | (R(P)               | 1   |                                                  |

| S1<br>(Exe- |              | В                | SEQ         | SET Q                        | Q=1                                          | FLOAT              | R(P)                | 1   | ļ                                                |

| cute)       | 1            | C,D,F            |             |                              | ALU OPERATION IMMEDIATE                      | M(R(P))            | R(P)                | 0   |                                                  |

|             |              | E                |             |                              | ALU OPERATION                                | FLOAT              | R(X)                | 1   |                                                  |

|             | 8_           | N                | GLO         | GET LOW                      | R(N) 0D                                      | R(N) .0            | R(N)                |     | <del> </del>                                     |