262144-word × 4-bit Multiport CMOS Video RAM

# **HITACHI**

Rev. 0.0 Dec. 1, 1995

### **Description**

The HM534251B is a 1-Mbit multiport video RAM equipped with a 256-kword  $\times$  4-bit dynamic RAM and a 512-word  $\times$  4-bit SAM (serial access memory). Its RAM and SAM operate independently and asynchronously. It can transfer data between RAM and SAM and has write mask function.

#### **Features**

• Multiport organization

Asynchronous and simultaneous operation of RAM and SAM capability

RAM: 256-kword  $\times$  4-bit SAM: 512-word  $\times$  4-bit

Access time

RAM: 60 ns/70 ns/80 ns/100 ns max SAM: 20 ns/22 ns/25 ns/25 ns max

• Cycle time

RAM: 125 ns/135 ns/150 ns/180 ns min SAM: 25 ns/25 ns/30 ns/30 ns min

• Low power

Active RAM: 413 mW max SAM: 275 mW max

Standby 38.5 mW max

- · High-speed page mode capability

- Mask write mode capability

- Bidirectional data transfer cycle between RAM and SAM capability

- · Real time read transfer cycle capability

- 3 variations of refresh (8 ms/512 cycles)

RAS-only refresh

CAS-before-RAS refresh

Hidden refresh

TTL compatible

## **Ordering Information**

| Type No.      | Access Time | Package                             |

|---------------|-------------|-------------------------------------|

| HM534251BJ-6  | 60 ns       | 400-mil 28-pin plastic SOJ (CP-28D) |

| HM534251BJ-7  | 70 ns       |                                     |

| HM534251BJ-8  | 80 ns       |                                     |

| HM534251BJ-10 | 100 ns      |                                     |

| HM534251BZ-6  | 60 ns       | 400-mil 28-pin plastic ZIP (ZP-28)  |

| HM534251BZ-7  | 70 ns       |                                     |

| HM534251BZ-8  | 80 ns       |                                     |

| HM534251BZ-10 | 100 ns      |                                     |

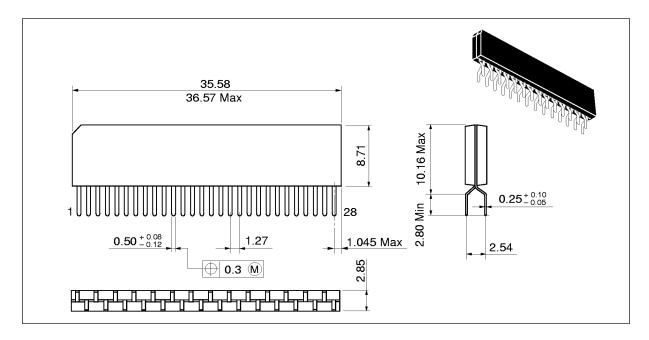

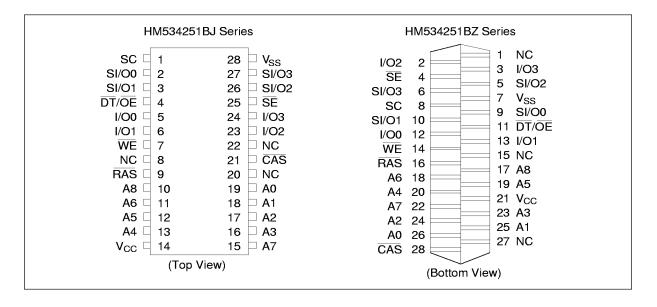

### **Pin Arrangement**

# **Pin Description**

| Pin Name        | Function                     |

|-----------------|------------------------------|

| A0 – A8         | Address inputs               |

| I/O0 – I/O3     | RAM port data inputs/outputs |

| SI/O0 – SI/O3   | SAM port data inputs/outputs |

| RAS             | Row address strobe           |

| CAS             | Column address strobe        |

| WE              | Write enable                 |

| DT/OE           | Data transfer/Output enable  |

| SC              | Serial clock                 |

| SE              | SAM port enable              |

| V <sub>cc</sub> | Power supply                 |

| V <sub>ss</sub> | Ground                       |

| NC              | No connection                |

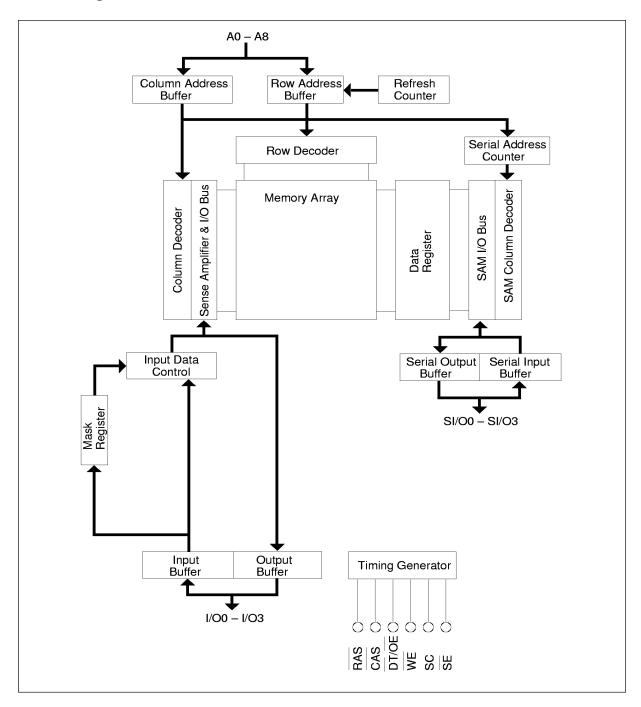

### **Block Diagram**

#### **Pin Functions**

$\overline{RAS}$  (input pin):  $\overline{RAS}$  is a basic RAM signal. It is active in low level and standby in high level. Row address and signals as shown in table 1 are input at the falling edge of  $\overline{RAS}$ . The input level of these signals determine the operation cycle of the HM534251B.

Table 1. Operation Cycles of the HM534251B

Input Level At The Falling Edge Of RAS

| CAS | DT/OE | WE | SE | Operation Mode  |

|-----|-------|----|----|-----------------|

| L   | Х     | X  | X  | CBR refresh     |

| Н   | L     | L  | L  | Write transfer  |

| Н   | L     | L  | Н  | Pseudo transfer |

| Н   | L     | Н  | X  | Read transfer   |

| Н   | Н     | L  | Χ  | Read/mask write |

| Н   | Н     | Н  | Χ  | Read/write      |

Note: X: Don't care.

$\overline{\text{CAS}}$  (input pin): Column address is fetched into chip at the falling edge of  $\overline{\text{CAS}}$ .  $\overline{\text{CAS}}$  controls output impedance of I/O in RAM.

**A0–A8** (input pins): Row address is determined by A0–A8 level at the falling edge of  $\overline{RAS}$ . Column address is determined by A0-A8 level at the falling edge of  $\overline{CAS}$ . In transfer cycles, row address is the address on the word line which transfers data with SAM data register, and column address is the SAM start address after transfer.

$\overline{\text{WE}}$  (input pin):  $\overline{\text{WE}}$  pin has two functions at the falling edge of  $\overline{\text{RAS}}$  and after. When  $\overline{\text{WE}}$  is low at the falling edge of  $\overline{\text{RAS}}$ , the HM534251B turns to mask write mode. According to the I/O level at the time, write on each I/O can be masked. ( $\overline{\text{WE}}$  level at the falling edge of  $\overline{\text{RAS}}$  is don't care in read cycle.) When  $\overline{\text{WE}}$  is high at the falling edge of  $\overline{\text{RAS}}$ , a normal write cycle is executed. After that,  $\overline{\text{WE}}$  switches read/write cycles as in a standard DRAM. In a transfer cycle, the direction of transfer is determined by  $\overline{\text{WE}}$  level at the falling edge of  $\overline{\text{RAS}}$ . When  $\overline{\text{WE}}$  is low, data is transferred from SAM to RAM (data is written into RAM), and when  $\overline{\text{WE}}$  is high, data is transferred from RAM to SAM (data is read from RAM).

I/O0 - I/O3 (input/output pins): I/O pins function as mask data at the falling edge of  $\overline{RAS}$  (in mask write mode). Data is written only to high I/O pins. Data on low I/O pins are masked and internal data are retained. After that, they function as input/output pins as those of a standard DRAM.

$\overline{DT}/\overline{OE}$  (input pin):  $\overline{DT}/\overline{OE}$  pin functions as  $\overline{DT}$  (data transfer) pin at the falling edge of  $\overline{RAS}$  and as  $\overline{OE}$  (output enable) pin after that. When  $\overline{DT}$  is low at the falling edge of  $\overline{RAS}$ , this cycle becomes a transfer cycle. When  $\overline{DT}$  is high at the falling edge of  $\overline{RAS}$ , RAM and SAM operate independently.

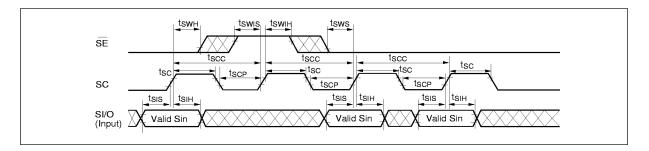

**SC** (**input pin**): SC is a basic SAM clock. In a serial read cycle, data outputs from an SI/O pin synchronously with the rising edge of SC. In a serial write cycle, data on an SI/O pin at the rising edge of SC is fetched into the SAM data register.

$\overline{SE}$  (input pin):  $\overline{SE}$  pin activates SAM. When  $\overline{SE}$  is high, SI/O is in the high impedance state in serial read cycle and data on SI/O is not fetched into the SAM data register in serial write cycle.  $\overline{SE}$  can be used as a mask for serial write because internal pointer is incremented at the rising edge of SC.

SI/O0-SI/O3 (input/output pins): SI/Os are input/output pins in SAM. Direction of input/output is determined by the previous transfer cycle. When it was a read transfer cycle, SI/O outputs data. When it was a pseudo transfer cycle or write transfer cycle, SI/O inputs data.

### **Operation of HM534251B**

**RAM Read Cycle** ( $\overline{DT/OE}$  high and  $\overline{CAS}$  high at the falling edge of  $\overline{RAS}$ )

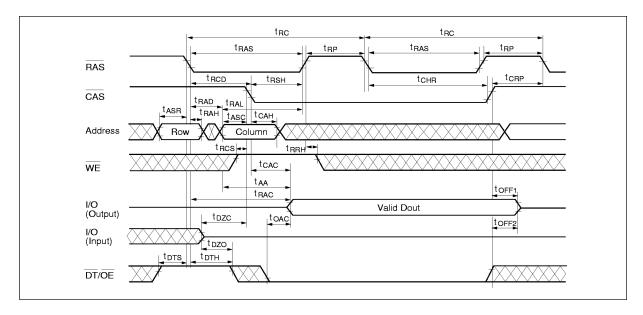

Row address is entered at the  $\overline{RAS}$  falling edge and column address at the  $\overline{CAS}$  falling edge to the device as in standard DRAM. Then, when  $\overline{WE}$  is high and  $\overline{DT/OE}$  is low while  $\overline{CAS}$  is low, the selected address data outputs through I/O pin. At the falling edge of  $\overline{RAS}$ ,  $\overline{DT/OE}$  and  $\overline{CAS}$  become high to distinguish RAM read cycle from transfer cycle and CBR refresh cycle. Address access time ( $t_{AA}$ ) and  $\overline{RAS}$  to column address delay time ( $t_{RAD}$ ) specifications are added to enable high-speed page mode.

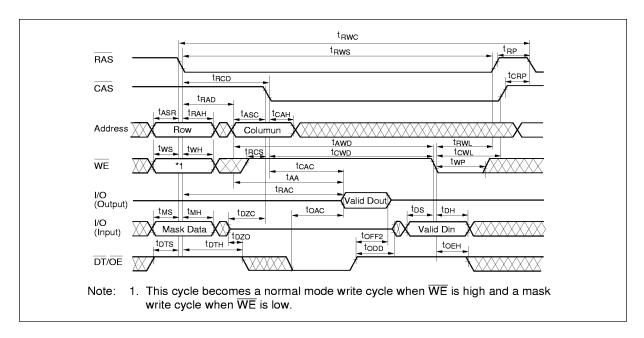

RAM Write Cycle (Early Write, Delayed Write, Read-Modify-Write)

$(\overline{DT}/\overline{OE})$  high and  $\overline{CAS}$  high at the falling edge of  $\overline{RAS}$

• Normal Mode Write Cycle ( $\overline{\text{WE}}$  high at the falling edge of  $\overline{\text{RAS}}$ )

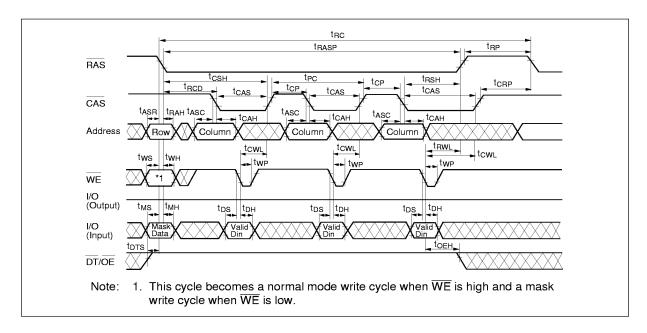

When  $\overline{CAS}$  and  $\overline{WE}$  are set low after driving  $\overline{RAS}$  low, a write cycle is executed and I/O data is written in the selected addresses. When all 4 I/Os are written,  $\overline{WE}$  should be high at the falling edge of  $\overline{RAS}$  to distinguish normal mode from mask write mode.

If  $\overline{\text{WE}}$  is set low before the  $\overline{\text{CAS}}$  falling edge, this cycle becomes an early write cycle and I/O becomes in high impedance. Data is entered at the  $\overline{\text{CAS}}$  falling edge.

If  $\overline{WE}$  is set low after the  $\overline{CAS}$  falling edge, this cycle becomes a delalyed write cycle. Data is input at the  $\overline{WE}$  falling. I/O does not become high impedance in this cycle, so data should be entered with  $\overline{OE}$  in high.

If  $\overline{\text{WE}}$  is set low after  $t_{\text{CWD}}$  (min) and  $t_{\text{AWD}}$  (min) after the  $\overline{\text{CAS}}$  falling edge, this cycle becomes a read-modify-write cycle and enables read/write at the same address in one cycle. In this cycle also, to avoid I/O contention, data should be input after reading data and driving  $\overline{\text{OE}}$  high.

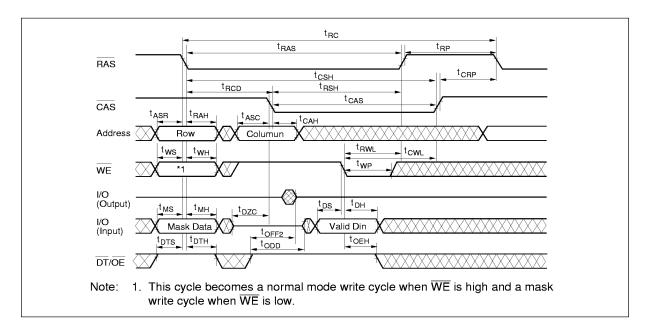

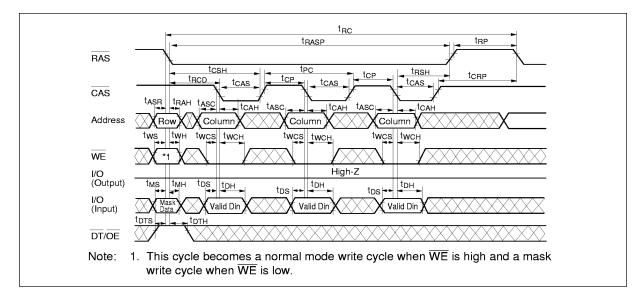

• Mask Write Mode (WE low at the falling edge of RAS)

If WE is set low at the falling edge of RAS, the cycle becomes a mask write mode cycle which writes only to selected I/O. Whether or not an I/O is written depends on I/O level (mask data) at the falling edge of  $\overline{RAS}$ . Then the data is written in high I/O pins and masked in low ones and internal data is retained. This mask data is effective during the  $\overline{RAS}$  cycle. So, in high-speed page mode cycle, the mask data is retained during the page access.

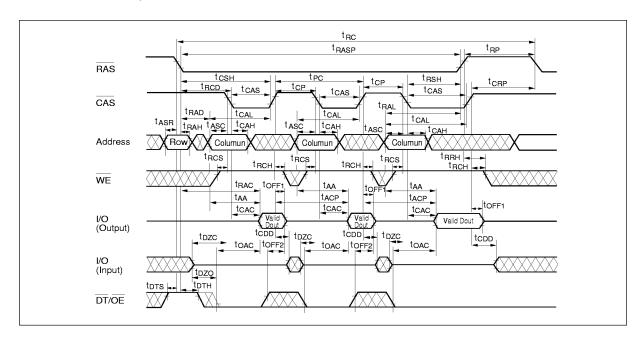

**High-Speed Page Mode Cycle** ( $\overline{DT/OE}$  high and  $\overline{CAS}$  high at the falling edge of  $\overline{RAS}$ )

High-speed page mode cycle reads/writes the data of the same row address at high speed by toggling  $\overline{CAS}$  while  $\overline{RAS}$  is low. Its cycle time is one third of the random read/write cycle. Note that address access time  $(t_{AA})$ ,  $\overline{RAS}$  to column address delay time  $(t_{RAD})$ , and access time from  $\overline{CAS}$  precharge  $(t_{ACP})$  are added. In one  $\overline{RAS}$  cycle, 512-word memory cells of the same row address can be accessed. It is necessary to specify access frequency within  $t_{RASP}$  max  $(100~\mu s)$ .

### **Transfer Operation**

The HM534251B provides the read transfer cycle, pseudo transfer cycle and write transfer cycle as data transfer cycles. These transfer cycles are set by driving  $\overline{CAS}$  high and  $\overline{DT/OE}$  low at the falling edge of  $\overline{RAS}$ . They have following functions:

(1) Transfer data between row address and SAM data register (except for pseudo transfer cycle)

Read transfer cycle:RAM to SAM

Write transfer cycle:SAM to RAM

(2) Determine SI/O state

Read transfer cycle:SI/O output

Pseudo transfer cycle

and write transfer cycle: SI/O input

(3) Determine first SAM address to access after transferring at column address (SAM start address). SAM start address must be determined by read transfer cycle or pseudo transfer cycle after power on, and determined for each transfer cycle.

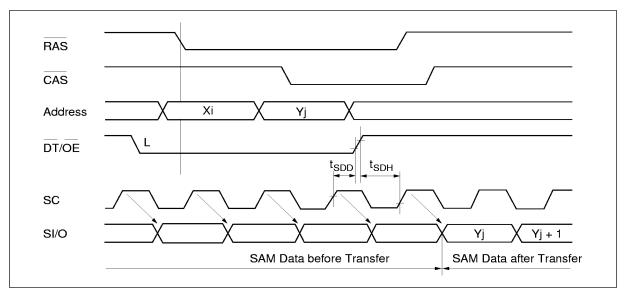

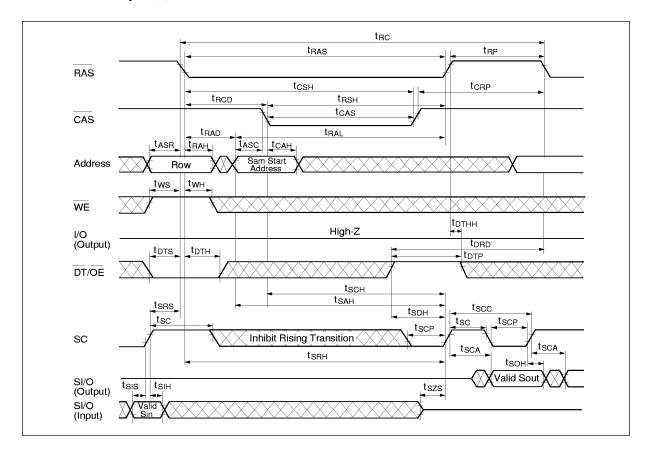

**Read Transfer Cycle** ( $\overline{CAS}$  high,  $\overline{DT}/\overline{OE}$  low and  $\overline{WE}$  high at the falling edge of  $\overline{RAS}$ )

This cycle becomes read transfer cycle by driving  $\overline{DT/OE}$  low and  $\overline{WE}$  high at the falling edge of  $\overline{RAS}$ . The row address data (512 × 4-bit) determined by this cycle is transferred to SAM data register synchronously at the rising edge of  $\overline{DT/OE}$ . After the rising edge of  $\overline{DT/OE}$ , the new address data outputs from SAM start address determined by column address. In read transfer cycle,  $\overline{DT/OE}$  must be risen to transfer data from RAM to SAM.

This cycle can access SAM even during transfer (real time read transfer). In this case, the timing  $t_{SDD}$  (min) specified between the last SAM access before transfer and  $\overline{DT/OE}$  rising edge and  $t_{SDH}$  (min) specified between the first SAM access and  $\overline{DT/OE}$  rising edge must be satisfied. (See figure 1.).

Figure 1. Real Time Read Transfer

When read transfer cycle is executed, SI/O becomes output state by first SAM access. Input must be set high impedance before  $t_{SZS}$  (min) of the first SAM access to avoid data contention.

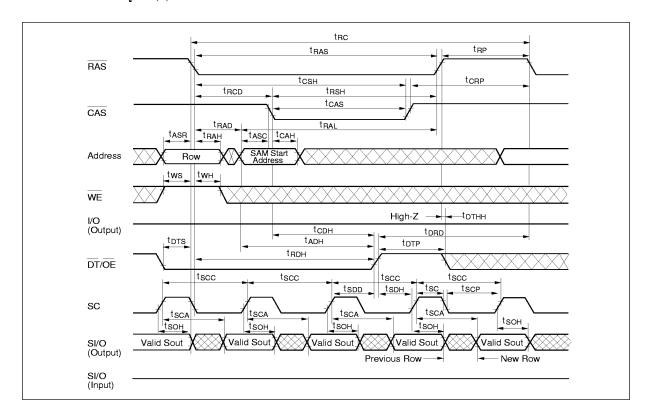

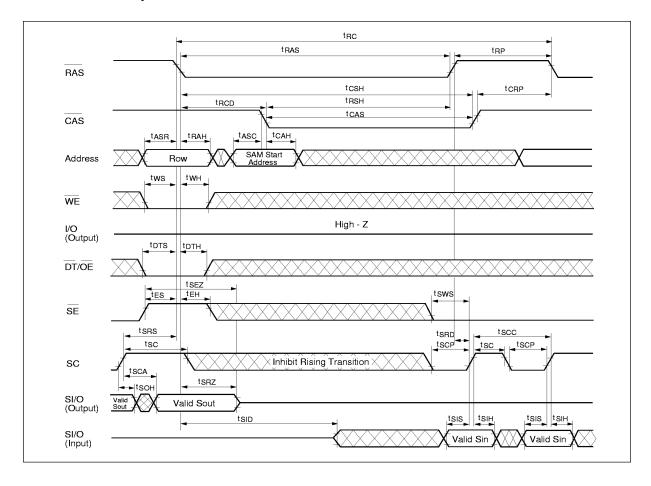

Pseudo Transfer Cycle (CAS high, DT/OE low, WE low and SE high at the falling edge of RAS)

Pseudo transfer cycle switches SI/O to input state and set SAM start address without data transfer to RAM.

This cycle starts when  $\overline{CAS}$  is high,  $\overline{DT/OE}$  low,  $\overline{WE}$  low and  $\overline{SE}$  high at the falling edge of  $\overline{RAS}$ . Data should be input to SI/O later than  $t_{SID}$  (min) after  $\overline{RAS}$  becomes low to avoid data contention. SAM access becomes enabled after  $t_{SRD}$  (min) after  $\overline{RAS}$  becomes high. In this cycle, SAM access is inhibited during  $\overline{RAS}$  low, therefore, SC must not be risen.

Write Transfer Cycle ( $\overline{CAS}$  high,  $\overline{DT}/\overline{OE}$  low,  $\overline{WE}$  low and  $\overline{SE}$  low at the falling edge of  $\overline{RAS}$ )

Write transfer cycle can transfer a row of data input by serial write cycle to  $\overline{RAM}$ . The row address of data transferred into RAM is determined by the address at the falling edge of  $\overline{RAS}$ . The column address is specified as the first address for serial write after terminating this cycle. Also in this cycle, SAM access becomes enabled after  $t_{SRD}$  (min) after  $\overline{RAS}$  becomes high. SAM access is inhibited during  $\overline{RAS}$  low. In this period, SC must not be risen.

Data transferred to SAM by read transfer cycle can be written to other address of RAM by write transfer cycle. However, the address to write data must be the same MSB of row address (AX8) as that of the read transfer cycle.

### **SAM Port Operation**

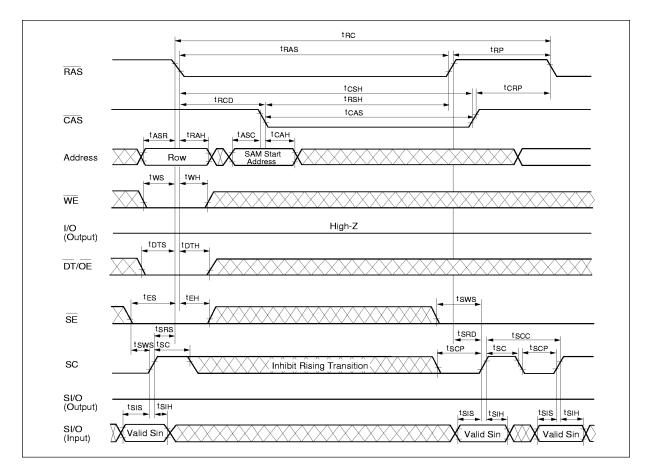

#### Serial Read Cycle

SAM port is in read mode when the previous data transfer cycle is read transfer cycle. Access is synchronized with SC rising, and SAM data is output from SI/O. When  $\overline{SE}$  is set high, SI/O becomes high impedance, and the internal pointer is incremented by the SC rising. After indicating the last address (address 511), the internal pointer indicates address 0 at the next access.

#### Serial Write Cycle

If previous data transfer cycle is pseudo transfer cycle or write transfer cycle, SAM port goes into write mode. In this cycle, SI/O data is fetched into data register at the SC rising edge like in the serial read cycle. If  $\overline{SE}$  is high, SI/O data isn't fetched into data register. Internal pointer is incremented by the SC rising, so  $\overline{SE}$  high can be used as mask data for SAM. After indicating the last address (address 511), the internal pointer indicates address 0 at the next access.

#### Refresh

#### **RAM Refresh**

RAM, which is composed of dynamic circuits, requires refresh to retain data. Refresh is executed by accessing all 512 row addresses within 8 ms. There are three refresh cycles: (1)  $\overline{RAS}$ -only refresh cycle, (2)  $\overline{CAS}$ -before- $\overline{RAS}$  (CBR) refresh cycle, and (3) Hidden refresh cycle. Besides them, the cycles which activate  $\overline{RAS}$  such as read/write cycles or transfer cycles can refresh the row address. Therefore, no refresh cycle is required when all row addresses are accessed within 8 ms.

- (1)  $\overline{RAS}$ -Only Refresh Cycle:  $\overline{RAS}$ -only refresh cycle is executed by activating only  $\overline{RAS}$  cycle with  $\overline{CAS}$  fixed to high after inputting the row address (= refresh address) from external circuits. To distinguish this cycle from data transfer cycle,  $\overline{DT}/\overline{OE}$  must be high at the falling edge of  $\overline{RAS}$ .

- (2) CBR Refresh Cycle: CBR refresh cycle is set by activating  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$ . In this cycle, refresh address need not to be input through external circuits because it is input through an internal refresh counter. In this cycle, output is in high impedance and power dissipation is lowered because  $\overline{\text{CAS}}$  circuits don't operate.

- (3) Hidden Refresh Cycle: Hidden refresh cycle executes CBR refresh with the data output by reactivating RAS when DT/OE and CAS keep low in normal RAM read cycles.

#### SAM Refresh

SAM parts (data register, shift register and selector), organized as fully static circuitry, require no refresh.

# **Absolute Maximum Ratings**

| Parameter                      | Symbol          | Value        | Unit |   |

|--------------------------------|-----------------|--------------|------|---|

| Terminal voltage <sup>*1</sup> | V <sub>T</sub>  | −1.0 to +7.0 | V    |   |

| Power supply voltage*1         | V <sub>cc</sub> | −0.5 to +7.0 | V    |   |

| Short circuit output current   | lout            | 50           | mA   |   |

| Power dissipation              | P <sub>T</sub>  | 1.0          | W    |   |

| Operating temperature          | Topr            | 0 to +70     | °C   | - |

| Storage temperature            | Tstg            | −55 to +125  | °C   |   |

Note: 1. Relative to V<sub>ss</sub>.

# **Recommended DC Operating Conditions** ( $Ta = 0 \text{ to } +70^{\circ}\text{C}$ )

| Parameter                       | Symbol          | Min         | Тур | Max | Unit |  |

|---------------------------------|-----------------|-------------|-----|-----|------|--|

| Supply voltage <sup>*1</sup>    | V <sub>cc</sub> | 4.5         | 5.0 | 5.5 | V    |  |

| Input high voltage*1            | $V_{\text{IH}}$ | 2.4         | _   | 6.5 | ٧    |  |

| Input low voltage <sup>*1</sup> | $V_{\text{IL}}$ | $-0.5^{*2}$ | _   | 0.8 | ٧    |  |

Notes: 1. All voltages referred to  $V_{\rm ss}$ .

2. -3.0 V for pulse width  $\leq 10 \text{ ns}$ .

# DC Characteristics (Ta = 0 to +70°C, $V_{\rm CC}$ = 5 V $\pm$ 10%, $V_{\rm SS}$ = 0 V)

### HM534251B

| _                 | •                | -6  |     | -7  | •   | -8  |     | -10 |     | •    | <b>Test Conditions</b>                                     |                                                            |

|-------------------|------------------|-----|-----|-----|-----|-----|-----|-----|-----|------|------------------------------------------------------------|------------------------------------------------------------|

| Parameter         | Symbol           | Min | Max | Min | Max | Min | Max | Min | Max | Unit | RAM Port                                                   | SAM Port                                                   |

| Operating current | I <sub>cc1</sub> | _   | 75  | _   | 70  | _   | 60  | _   | 55  | mA   | $\overline{RAS}$ , $\overline{CAS}$ cycling $t_{RC}$ = min | $\frac{SC}{SE} = V_{IL},$                                  |

|                   | I <sub>CC7</sub> | _   | 125 | _   | 120 | _   | 100 | _   | 95  | mA   |                                                            | $\overline{SE} = V_{IL},$<br>SC cycling<br>$t_{SCC} = min$ |

| Standby current   | I <sub>CC2</sub> | _   | 7   | _   | 7   | _   | 7   | _   | 7   | mA   | $\overline{RAS}$ , $\overline{CAS} = V_{IH}$               | $\frac{SC}{SE} = V_{IL},$                                  |

|                   | I <sub>CC8</sub> | _   | 50  |     | 50  |     | 40  |     | 40  | mA   |                                                            | $\overline{SE} = V_{IL},$<br>SC cycling<br>$t_{SCC} = min$ |

DC Characteristics (Ta = 0 to +70°C,  $V_{\text{CC}}$  = 5 V  $\pm$  10%,  $V_{\text{SS}}$  = 0 V) (cont)

### HM534251B

|                                        |                   | -6  |     | -7  |     | -8  |     | -10 |     |      | Test Conditions                                                   |                                                            |

|----------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|------|-------------------------------------------------------------------|------------------------------------------------------------|

|                                        | Symbol            |     | Max | Min | Max |     | Max |     | Max | Unit | RAM Port                                                          | SAM Port                                                   |

| RAS -only refresh current              | I <sub>CC3</sub>  | _   | 75  | _   | 70  | _   | 60  | _   | 55  | mA   | $\overline{RAS}$ cycling $\overline{CAS} = V_{IH}$ $t_{RC} = min$ | $\frac{SC}{SE} = V_{IL},$                                  |

|                                        | I <sub>CC9</sub>  | _   | 125 | _   | 120 | _   | 100 | _   | 95  | mA   |                                                                   | $\overline{SE} = V_{IL},$<br>SC cycling<br>$t_{SCC} = min$ |

| Page mode current                      | I <sub>CC4</sub>  | _   | 80  |     | 80  | _   | 70  | _   | 65  | mA   | $\frac{\overline{CAS}}{\overline{RAS}} = V_{IL}$ $t_{PC} = \min$  | $\frac{SC}{SE} = V_{IL},$                                  |

|                                        | I <sub>CC10</sub> | _   | 130 |     | 130 | _   | 110 | _   | 105 | mA   |                                                                   | $\overline{SE} = V_{IL},$<br>SC cycling<br>$t_{SCC} = min$ |

| CAS -before-<br>RAS refresh<br>current | I <sub>CC5</sub>  | _   | 50  |     | 45  |     | 40  | _   | 35  | mA   | RAS cycling t <sub>RC</sub> = min                                 | $\frac{SC}{SE} = V_{IL},$                                  |

|                                        | I <sub>CC11</sub> | _   | 100 |     | 95  | _   | 80  | _   | 75  | mA   |                                                                   | $\overline{SE} = V_{IL},$<br>SC cycling<br>$t_{SCC} = min$ |

| Data transfer current                  | I <sub>CC6</sub>  | _   | 80  | _   | 75  | _   | 65  |     | 60  | mA   | $\overline{RAS}$ , $\overline{CAS}$ cycling $t_{RC}$ = min        | $\frac{SC}{SE} = V_{IL},$ $\overline{SE} = V_{IH}$         |

|                                        | I <sub>CC12</sub> | _   | 130 | _   | 125 | _   | 105 | _   | 100 | mA   |                                                                   | $\overline{SE} = V_{IL},$<br>SC cycling<br>$t_{SCC} = min$ |

| Input leakage current                  | ILI               | -10 | 10  | -10 | 10  | -10 | 10  | -10 | 10  | μΑ   |                                                                   |                                                            |

| Output leakage current                 | I <sub>LO</sub>   | -10 | 10  | -10 | 10  | -10 | 10  | -10 | 10  | μΑ   |                                                                   |                                                            |

| Output high voltage                    | V <sub>OH</sub>   | 2.4 | _   | 2.4 |     | 2.4 |     | 2.4 |     | V    | $I_{OH} = -2 \text{ mA}$                                          |                                                            |

| Output low voltage                     | V <sub>oL</sub>   | _   | 0.4 | _   | 0.4 |     | 0.4 |     | 0.4 | V    | I <sub>oL</sub> = 4.2 mA                                          |                                                            |

Notes: 1. I<sub>cc</sub> depends on output loading condition when the device is selected. I<sub>cc</sub> max is specified at the output open condition.

2. Address can be changed once while  $\overline{RAS}$  is low and  $\overline{CAS}$  is high.

Capacitance (Ta = 25°C,  $V_{CC}$  = 5 V, f = 1 MHz, Bias: Clock, I/O =  $V_{CC}$ , address =  $V_{SS}$ )

| Parameter | Symbol           | Min | Тур | Max | Unit |  |

|-----------|------------------|-----|-----|-----|------|--|

| Address   | C <sub>I1</sub>  | _   | _   | 5   | pF   |  |

| Clock     | C <sub>I2</sub>  | _   | _   | 5   | pF   |  |

| I/O, SI/O | C <sub>I/O</sub> | _   | _   | 7   | pF   |  |

AC Characteristics (Ta = 0 to +70°C,  $V_{\rm CC}$  = 5 V  $\pm 10\%$ ,  $V_{\rm SS}$  = 0 V) $^{*1,\,*16}$

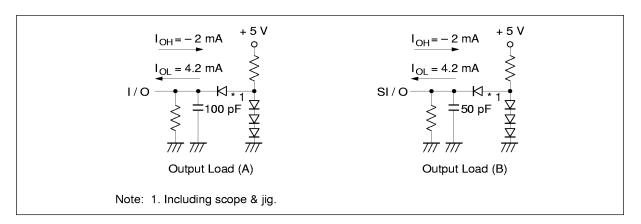

### **Test Conditions**

Input rise and fall time: 5 ns

Input pulse levels: V<sub>SS</sub> to 3.0 V

Input timing reference levels: 0.8 V, 2.4 V

Output timing reference levels: 0.8 V, 2.0 V

• Output load: See figures

### **Common Parameter**

|                                              |                   | HM5 | 34251E | 3   |       |     |       |     |       |      |       |

|----------------------------------------------|-------------------|-----|--------|-----|-------|-----|-------|-----|-------|------|-------|

|                                              |                   | -6  |        | -7  |       | -8  |       | -10 |       |      |       |

| Parameter                                    | Symbol            | Min | Max    | Min | Max   | Min | Max   | Min | Max   | Unit | Notes |

| Random read or write cycle time              | t <sub>RC</sub>   | 125 | _      | 135 | _     | 150 | _     | 180 | _     | ns   |       |

| RAS precharge time                           | t <sub>RP</sub>   | 55  | _      | 55  | _     | 60  | _     | 70  | _     | ns   |       |

| RAS pulse width                              | t <sub>RAS</sub>  | 60  | 10000  | 70  | 10000 | 80  | 10000 | 100 | 10000 | ns   |       |

| CAS pulse width                              | t <sub>CAS</sub>  | 20  | _      | 20  | _     | 20  | _     | 25  | _     | ns   |       |

| Row address setup time                       | t <sub>ASR</sub>  | 0   | _      | 0   | _     | 0   |       | 0   | _     | ns   |       |

| Row address hold time                        | t <sub>rah</sub>  | 10  | _      | 10  | _     | 10  | _     | 10  | _     | ns   |       |

| Column address setup time                    | t <sub>ASC</sub>  | 0   | _      | 0   | _     | 0   | _     | 0   | _     | ns   |       |

| Column address hold time                     | t <sub>cah</sub>  | 15  | _      | 15  | _     | 15  |       | 15  | _     | ns   |       |

| RAS to CAS delay time                        | t <sub>RCD</sub>  | 20  | 40     | 20  | 50    | 20  | 60    | 20  | 75    | ns   | 2     |

| RAS hold time referred to CAS                | t <sub>RSH</sub>  | 20  | _      | 20  | _     | 20  | _     | 25  | _     | ns   |       |

| CAS hold time referred to RAS                | t <sub>csh</sub>  | 60  | _      | 70  | _     | 80  | _     | 100 | _     | ns   |       |

| CAS to RAS precharge time                    | t <sub>CRP</sub>  | 10  | _      | 10  | _     | 10  | _     | 10  | _     | ns   |       |

| Transition time (rise to fall)               | t <sub>T</sub>    | 3   | 50     | 3   | 50    | 3   | 50    | 3   | 50    | ns   | 3     |

| Refresh period                               | t <sub>REF</sub>  |     | 8      |     | 8     | _   | 8     | _   | 8     | ms   |       |

| DT to RAS setup time                         | t <sub>DTS</sub>  | 0   | _      | 0   | _     | 0   | _     | 0   | _     | ns   |       |

| DT to RAS hold time                          | t <sub>DTH</sub>  | 10  | _      | 10  | _     | 10  | _     | 10  | _     | ns   |       |

| Data-in to CAS delay time                    | t <sub>DZC</sub>  | 0   | _      | 0   | _     | 0   |       | 0   | _     | ns   | 4     |

| Data-in to OE delay time                     | t <sub>DZO</sub>  | 0   | _      | 0   | _     | 0   | _     | 0   | _     | ns   | 4     |

| Output buffer turn-off delay referred to CAS | t <sub>OFF1</sub> |     | 20     |     | 20    |     | 20    |     | 20    | ns   | 5     |

| Output buffer turn-off delay referred to OE  | t <sub>OFF2</sub> | _   | 20     | _   | 20    | _   | 20    | _   | 20    | ns   | 5     |

# Read Cycle (RAM), Page Mode Read Cycle

|                                        |                   | HM5 | 34251B |     |        |     |        |     |        |      |       |

|----------------------------------------|-------------------|-----|--------|-----|--------|-----|--------|-----|--------|------|-------|

|                                        |                   | -6  |        | -7  |        | -8  |        | -10 |        |      |       |

| Parameter                              | Symbol            | Min | Max    | Min | Max    | Min | Max    | Min | Max    | Unit | Notes |

| Access time from RAS                   | t <sub>RAC</sub>  | _   | 60     | _   | 70     | _   | 80     | _   | 100    | ns   | 6, 7  |

| Access time from CAS                   | t <sub>cac</sub>  | _   | 20     | _   | 20     | _   | 20     |     | 25     | ns   | 7, 8  |

| Access time from OE                    | toac              | _   | 20     | _   | 20     | _   | 20     | _   | 25     | ns   | 7     |

| Address access time                    | t <sub>AA</sub>   |     | 35     | _   | 35     | _   | 40     | _   | 45     | ns   | 7, 9  |

| Read command setup time                | t <sub>RCS</sub>  | 0   |        | 0   |        | 0   | _      | 0   | _      | ns   |       |

| Read command hold time                 | t <sub>RCH</sub>  | 0   |        | 0   | _      | 0   | _      | 0   | _      | ns   | 10    |

| Read command hold time referred to RAS | t <sub>RRH</sub>  | 10  |        | 10  | _      | 10  | _      | 10  | _      | ns   | 10    |

| RAS to column address delay time       | t <sub>RAD</sub>  | 15  | 25     | 15  | 35     | 15  | 40     | 15  | 55     | ns   | 2     |

| Column address to RAS lead time        | t <sub>RAL</sub>  | 35  | _      | 35  | _      | 40  | _      | 45  | _      | ns   |       |

| Column address to CAS lead time        | t <sub>CAL</sub>  | 35  | _      | 35  | _      | 40  | _      | 45  | _      | ns   |       |

| Page mode cycle time                   | t <sub>PC</sub>   | 45  | _      | 45  | _      | 50  | _      | 55  | _      | ns   |       |

| CAS precharge time                     | t <sub>CP</sub>   | 10  | _      | 10  | _      | 10  | _      | 10  | _      | ns   |       |

| Access time from CAS precharge         | t <sub>ACP</sub>  | _   | 40     | _   | 40     | _   | 45     | _   | 50     | ns   |       |

| Page mode RAS pulse width              | t <sub>rasp</sub> | 60  | 100000 | 70  | 100000 | 80  | 100000 | 100 | 100000 | ns   |       |

# Write Cycle (RAM), Page Mode Write Cycle

|                                |                   | HM5 | 34251 <b>B</b> |     |        |     |        |     |        |      |       |

|--------------------------------|-------------------|-----|----------------|-----|--------|-----|--------|-----|--------|------|-------|

|                                |                   | -6  |                | -7  |        | -8  |        | -10 |        |      |       |

| Parameter                      | Symbol            | Min | Max            | Min | Max    | Min | Max    | Min | Max    | Unit | Notes |

| Write command setup time       | t <sub>wcs</sub>  | 0   |                | 0   |        | 0   |        | 0   |        | ns   | 11    |

| Write command hold time        | t <sub>wch</sub>  | 15  | _              | 15  |        | 15  | _      | 15  |        | ns   |       |

| Write command pulse width      | t <sub>wP</sub>   | 15  |                | 15  | _      | 15  |        | 15  | _      | ns   |       |

| Write command to RAS lead time | t <sub>RWL</sub>  | 20  | _              | 20  | _      | 20  | _      | 20  | _      | ns   |       |

| Write command to CAS lead time | t <sub>cwL</sub>  | 20  | _              | 20  | _      | 20  | _      | 20  | _      | ns   |       |

| Data-in setup time             | t <sub>DS</sub>   | 0   | _              | 0   | _      | 0   | _      | 0   | _      | ns   | 12    |

| Data-in hold time              | t <sub>DH</sub>   | 15  | _              | 15  | _      | 15  | _      | 15  | _      | ns   | 12    |

| WE to RAS setup time           | t <sub>ws</sub>   | 0   | _              | 0   | _      | 0   | _      | 0   | _      | ns   |       |

| WE to RAS hold time            | t <sub>wH</sub>   | 10  | _              | 10  | _      | 10  | _      | 10  | _      | ns   |       |

| Mask data to RAS setup time    | t <sub>MS</sub>   | 0   | _              | 0   | _      | 0   | _      | 0   | _      | ns   |       |

| Mask data to RAS hold time     | t <sub>MH</sub>   | 10  | _              | 10  | _      | 10  | _      | 10  | _      | ns   |       |

| OE hold time referred to WE    | t <sub>OEH</sub>  | 20  | _              | 20  | _      | 20  | _      | 20  | _      | ns   |       |

| Page mode cycle time           | t <sub>PC</sub>   | 45  | _              | 45  |        | 50  | _      | 55  | _      | ns   |       |

| CAS precharge time             | t <sub>CP</sub>   | 10  | _              | 10  | _      | 10  | _      | 10  | _      | ns   |       |

| CAS to data-in delay time      | t <sub>CDD</sub>  | 20  | _              | 20  | _      | 20  | _      | 20  | _      | ns   | 13    |

| Page mode RAS pulse width      | t <sub>RASP</sub> | 60  | 100000         | 70  | 100000 | 80  | 100000 | 100 | 100000 | ns   |       |

# Read-Modify-Write Cycle

|                                           |                  | HM5 | 34251B |     |       |     |       |     |       |      |       |

|-------------------------------------------|------------------|-----|--------|-----|-------|-----|-------|-----|-------|------|-------|

|                                           |                  | -6  |        | -7  |       | -8  |       | -10 |       |      |       |

| Parameter                                 | Symbol           | Min | Max    | Min | Max   | Min | Max   | Min | Max   | Unit | Notes |

| Read-modify-write cycle time              | t <sub>RWC</sub> | 175 | _      | 185 | _     | 200 | _     | 230 | _     | ns   |       |

| RAS pulse width (read-modify-write cycle) | t <sub>RWS</sub> | 110 | 10000  | 120 | 10000 | 130 | 10000 | 150 | 10000 | ns   |       |

| CAS to WE delay time                      | t <sub>cwD</sub> | 45  |        | 45  | _     | 45  | _     | 50  | _     | ns   | 14    |

| Column address to WE delay time           | t <sub>AWD</sub> | 60  | _      | 60  | _     | 65  | _     | 70  | _     | ns   | 14    |

| OE to data-in delay time                  | t <sub>odd</sub> | 20  |        | 20  | _     | 20  | _     | 20  |       | ns   | 12    |

| Access time from RAS                      | t <sub>RAC</sub> | _   | 60     | _   | 70    | _   | 80    | _   | 100   | ns   | 6, 7  |

| Access time form CAS                      | t <sub>cac</sub> | _   | 20     | _   | 20    |     | 20    | _   | 25    | ns   | 7, 8  |

| Access time from OE                       | toac             | _   | 20     |     | 20    |     | 20    | _   | 25    | ns   | 7     |

| Address access time                       | t <sub>AA</sub>  | _   | 35     |     | 35    |     | 40    | _   | 45    | ns   | 7, 9  |

| RAS to column address delay time          | t <sub>RAD</sub> | 15  | 25     | 15  | 35    | 15  | 40    | 15  | 55    | ns   |       |

| Read command setup time                   | t <sub>RCS</sub> | 0   | _      | 0   | _     | 0   | _     | 0   | _     | ns   |       |

| Write command to RAS lead time            | t <sub>RWL</sub> | 20  | _      | 20  | _     | 20  | _     | 20  | _     | ns   |       |

| Write command to CAS lead time            | t <sub>cwL</sub> | 20  | _      | 20  | _     | 20  | _     | 20  | _     | ns   |       |

| Write command pulse width                 | t <sub>wP</sub>  | 15  | _      | 15  | _     | 15  | _     | 15  | _     | ns   |       |

| Data-in setup time                        | t <sub>DS</sub>  | 0   | _      | 0   | _     | 0   | _     | 0   | _     | ns   | 12    |

| Data-in hold time                         | t <sub>DH</sub>  | 15  | _      | 15  | _     | 15  | _     | 15  | _     | ns   | 12    |

| OE hold time referred to WE               | t <sub>oeн</sub> | 20  | _      | 20  | _     | 20  | _     | 20  | _     | ns   |       |

# Refresh Cycle

|                                         |                  | HM534251B |     |     |     |     |     |     |     |      |       |  |

|-----------------------------------------|------------------|-----------|-----|-----|-----|-----|-----|-----|-----|------|-------|--|

|                                         |                  | -6        |     | -7  |     | -8  |     | -10 |     |      |       |  |

| Parameter                               | Symbol           | Min       | Max | Min | Max | Min | Max | Min | Max | Unit | Notes |  |

| CAS setup time (CAS-before-RAS refresh) | t <sub>CSR</sub> | 10        | _   | 10  | _   | 10  |     | 10  | _   | ns   |       |  |

| CAS hold time (CAS-before-RAS refresh)  | t <sub>CHR</sub> | 10        | _   | 10  | _   | 10  | _   | 10  | _   | ns   |       |  |

| RAS precharge to CAS hold time          | t <sub>RPC</sub> | 10        |     | 10  |     | 10  |     | 10  |     | ns   |       |  |

# **Read Transfer Cycle**

|                                         | 1                 | HM5 | 34251B |     |       |     |       |     |       |      |       |

|-----------------------------------------|-------------------|-----|--------|-----|-------|-----|-------|-----|-------|------|-------|

|                                         |                   | -6  |        | -7  |       | -8  |       | -10 |       |      |       |

| Parameter                               | Symbol            | Min | Max    | Min | Max   | Min | Max   | Min | Max   | Unit | Notes |

| DT hold time referred to RAS            | t <sub>RDH</sub>  | 50  | 10000  | 60  | 10000 | 65  | 10000 | 80  | 10000 | ns   |       |

| DT hold time referred to CAS            | t <sub>cDH</sub>  | 20  | _      | 20  | _     | 20  | _     | 25  | _     | ns   |       |

| DT hold time referred to column address | t <sub>ADH</sub>  | 25  | _      | 25  | _     | 30  | _     | 30  | _     | ns   |       |

| DT precharge time                       | t <sub>DTP</sub>  | 20  |        | 20  |       | 20  |       | 30  | _     | ns   |       |

| DT to RAS delay time                    | t <sub>DRD</sub>  | 65  |        | 65  | _     | 70  | _     | 80  | _     | ns   |       |

| SC to RAS setup time                    | t <sub>srs</sub>  | 25  |        | 25  |       | 30  |       | 30  | _     | ns   |       |

| 1st SC to RAS hold time                 | t <sub>srh</sub>  | 60  |        | 70  | _     | 80  |       | 100 | _     | ns   |       |

| 1st SC to CAS hold time                 | t <sub>scн</sub>  | 25  | _      | 25  | _     | 25  | _     | 25  | _     | ns   |       |

| 1st SC to column address hold time      | t <sub>sah</sub>  | 40  | _      | 40  | _     | 45  | _     | 50  | _     | ns   |       |

| Last SC to DT delay time                | t <sub>sdd</sub>  | 5   |        | 5   | _     | 5   | _     | 5   | _     | ns   |       |

| 1st SC to DT hold time                  | t <sub>sdh</sub>  | 10  | _      | 10  |       | 15  |       | 15  | _     | ns   |       |

| Serial data-in to 1st SC delay time     | t <sub>szs</sub>  | 0   | _      | 0   | _     | 0   | _     | 0   | _     | ns   |       |

| Serial clock cycle time                 | t <sub>scc</sub>  | 25  |        | 25  | _     | 30  | _     | 30  | _     | ns   |       |

| SC pulse width                          | t <sub>sc</sub>   | 5   |        | 5   | _     | 10  |       | 10  | _     | ns   |       |

| SC precharge time                       | t <sub>scp</sub>  | 10  |        | 10  |       | 10  |       | 10  | _     | ns   |       |

| SC access time                          | t <sub>sca</sub>  | _   | 20     | _   | 22    | _   | 25    | _   | 25    | ns   | 15    |

| Serial data-out hold time               | t <sub>soн</sub>  | 5   |        | 5   | _     | 5   |       | 5   | _     | ns   |       |

| Serial data-in setup time               | t <sub>sis</sub>  | 0   |        | 0   |       | 0   |       | 0   | _     | ns   |       |

| Serial data-in hold time                | t <sub>siн</sub>  | 15  | _      | 15  | _     | 15  |       | 15  | _     | ns   |       |

| RAS to column address delay time        | t <sub>RAD</sub>  | 15  | 25     | 15  | 35    | 15  | 40    | 15  | 55    | ns   |       |

| Column address to RAS lead time         | t <sub>RAL</sub>  | 35  | _      | 35  | _     | 40  | _     | 45  | _     | ns   |       |

| DT high hold time from RAS precharge    | t <sub>DTHH</sub> | 10  | _      | 10  |       | 10  |       | 10  |       | ns   |       |

# Pseudo Transfer Cycle, Write Transfer Cycle

|                                                      |                  | HM53 | 4251B |     |     |     |     |     |     |      |       |

|------------------------------------------------------|------------------|------|-------|-----|-----|-----|-----|-----|-----|------|-------|

|                                                      |                  | -6   |       | -7  |     | -8  |     | -10 |     |      |       |

| Parameter                                            | Symbol           | Min  | Max   | Min | Max | Min | Max | Min | Max | Unit | Notes |

| SE setup time referred to RAS                        | t <sub>ES</sub>  | 0    | _     | 0   | _   | 0   | _   | 0   | _   | ns   |       |

| SE hold time referred to RAS                         | t <sub>eH</sub>  | 10   | _     | 10  | _   | 10  | _   | 10  | _   | ns   |       |

| SC setup time referred to RAS                        | t <sub>srs</sub> | 25   |       | 25  | _   | 30  |     | 30  |     | ns   |       |

| RAS to SC delay time                                 | t <sub>SRD</sub> | 20   | _     | 20  | _   | 25  | _   | 25  | _   | ns   |       |

| Serial output buffer turn-off time referenced to RAS | t <sub>srz</sub> | 10   | 40    | 10  | 40  | 10  | 45  | 10  | 50  | ns   |       |

| RAS to serial data-in delay time                     | t <sub>SID</sub> | 40   | _     | 40  | _   | 45  | _   | 50  | _   | ns   |       |

| Serial clock cycle time                              | t <sub>scc</sub> | 25   | _     | 25  | _   | 30  | _   | 30  | _   | ns   |       |

| SC pulse width                                       | t <sub>sc</sub>  | 5    | _     | 5   | _   | 10  | _   | 10  | _   | ns   |       |

| SC precharge time                                    | t <sub>SCP</sub> | 10   | _     | 10  | _   | 10  | _   | 10  | _   | ns   |       |

| SC access time                                       | t <sub>sca</sub> | _    | 20    | _   | 22  | _   | 25  | _   | 25  | ns   | 15    |

| SE access time                                       | t <sub>SEA</sub> | _    | 20    | _   | 22  | _   | 25  | _   | 25  | ns   | 15    |

| Serial data-out hold time                            | t <sub>soн</sub> | 5    | _     | 5   | _   | 5   | _   | 5   | _   | ns   |       |

| Serial write enable setup time                       | t <sub>sws</sub> | 5    |       | 5   |     | 5   |     | 5   |     | ns   |       |

| Serial data-in setup time                            | t <sub>sis</sub> | 0    |       | 0   |     | 0   |     | 0   |     | ns   |       |

| Serial data-in hold time                             | t <sub>sih</sub> | 15   | _     | 15  |     | 15  | _   | 15  | _   | ns   |       |

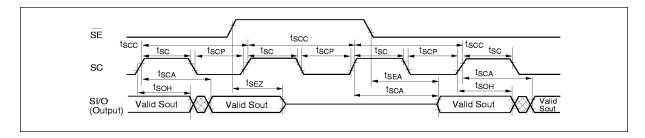

#### Serial Read Cycle, Serial Write Cycle

|                                                                |                   | HM53 | 4251B |     |     |     |     |     |     |      |       |

|----------------------------------------------------------------|-------------------|------|-------|-----|-----|-----|-----|-----|-----|------|-------|

|                                                                |                   | -6   |       | -7  |     | -8  |     | -10 |     |      |       |

| Parameter                                                      | Symbol            | Min  | Max   | Min | Max | Min | Max | Min | Max | Unit | Notes |

| Serial clock cycle time                                        | t <sub>scc</sub>  | 25   | _     | 25  | _   | 30  | _   | 30  | _   | ns   |       |

| SC pulse width                                                 | t <sub>sc</sub>   | 5    | _     | 5   | _   | 10  | _   | 10  | _   | ns   |       |

| SC precharge width                                             | t <sub>scp</sub>  | 10   | _     | 10  | _   | 10  | _   | 10  | _   | ns   |       |

| Access time from SC                                            | t <sub>SCA</sub>  | _    | 20    | _   | 22  |     | 25  |     | 25  | ns   | 15    |

| Access time from SE                                            | t <sub>SEA</sub>  | _    | 20    | _   | 22  |     | 25  |     | 25  | ns   | 15    |

| Serial data-out hold time                                      | t <sub>soн</sub>  | 5    | _     | 5   | _   | 5   |     | 5   |     | ns   |       |

| Serial output buffer turn-off time referred to $\overline{SE}$ | t <sub>SEZ</sub>  | _    | 20    | _   | 20  | _   | 20  | _   | 20  | ns   | 5     |

| Serial data-in setup time                                      | t <sub>sis</sub>  | 0    | _     | 0   | _   | 0   |     | 0   | _   | ns   |       |

| Serial data-in hold time                                       | t <sub>sih</sub>  | 15   | _     | 15  | _   | 15  |     | 15  | _   | ns   |       |

| Serial write enable setup time                                 | t <sub>sws</sub>  | 5    | _     | 5   |     | 5   | _   | 5   | _   | ns   |       |

| Serial write enable hold time                                  | t <sub>swн</sub>  | 15   |       | 15  | _   | 15  | _   | 15  | _   | ns   |       |

| Serial write disable setup time                                | t <sub>swis</sub> | 5    | _     | 5   |     | 5   | _   | 5   | _   | ns   |       |

| Serial write disable hold time                                 | t <sub>swiH</sub> | 15   | _     | 15  | _   | 15  | _   | 15  | _   | ns   |       |

Notes: 1. AC measurements assume  $t_T = 5$  ns.

- 2. When  $t_{RCD} > t_{RCD}$  (max) or  $t_{RAD} > t_{RAD}$  (max), access time is specified by  $t_{CAC}$  or  $t_{AA}$ .

- 3.  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals. Transition time  $t_T$  is measured between  $V_{IH}$  and  $V_{IL}$ .

- Data input must be floating before output buffer is turned on. In read cycle, read-modify-write cycle and delayed write cycle, either t<sub>DZC</sub> (min) or t<sub>DZC</sub> (min) must be satisfied.

- 5.  $t_{OFF1}$  (max),  $t_{OFF2}$  (max) and  $t_{SEZ}$  (max) are defined as the time at which the output acheives the open circuit condition ( $V_{OH}$  –100 mV,  $V_{OL}$  +100 mV).

- 6. Assume that  $t_{\text{RCD}} \le t_{\text{RCD}}$  (max) and  $t_{\text{RAD}} \le t_{\text{RAD}}$  (max). If  $t_{\text{RCD}}$  or  $t_{\text{RAD}}$  is greater than the maximum recommended value shown in this table,  $t_{\text{RAC}}$  exceeds the value shown.

- 7. Measured with a load circuit equivalent to 2 TTL loads and 100 pF.

- 8. When  $t_{RCD} \ge t_{RCD}$  (max) and  $t_{RAD} \le t_{RAD}$  (max), access time is specified by  $t_{CAC}$ .

- 9. When  $t_{\text{RCD}} \le t_{\text{RCD}}$  (max) and  $t_{\text{RAD}} \ge t_{\text{RAD}}$  (max), access time is specified by  $t_{\text{AA}}$ .

- 10. If either t<sub>RCH</sub> of t<sub>RBH</sub> is satisfied, operation is guaranteed.

- 11. When  $t_{wcs} \ge t_{wcs}$  (min), the cycle is an early write cycle, and I/O pins remain in an open circuit (high impedance) condition.

- 12. These parameters are specified by the later falling edge of  $\overline{\text{CAS}}$  or  $\overline{\text{WE}}$ .

- 13. Either t<sub>CDD</sub> (min) or t<sub>ODD</sub> (min) must be satisfied because output buffer must be turned off by  $\overline{\text{CAS}}$  or  $\overline{\text{OE}}$  prior to applying data to the device when output buffer is on.

- 14. When  $t_{AWD} \ge t_{AWD}$  (min) and  $t_{CWD} \ge t_{CWD}$  (min) in read-modify-write cycle, the data of the selected address outputs to an I/O pin and input data is written into the selected address.  $t_{ODD}$  (min) must be satisfied because output buffer must be turned off by  $\overline{OE}$  prior to applying data to the device.

- 15. Measured with a load circuit equivalent to 2 TTL loads and 50 pF.

- 16. After power-up, pause for 100  $\mu s$  or more and execute at least 8 initialization cycle (normal memory cycle or refresh cycle), then start operation.

- 17.  $\square$  H or L (H:  $V_{IH}$  (min)  $\leq V_{IN} \leq V_{IH}$  (max), L:  $V_{IL}$  (min)  $\leq V_{IN} \leq V_{IL}$  (max)) Invalid Dout

# Timing Waveforms \*17

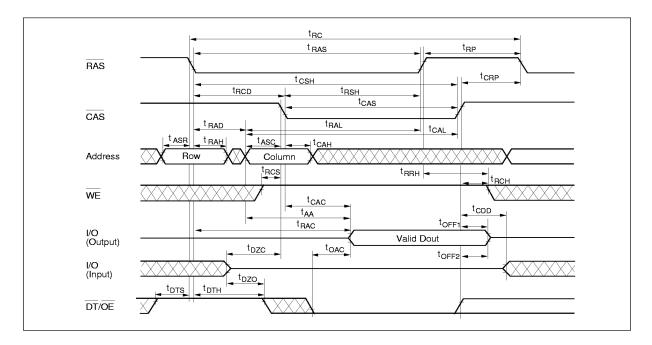

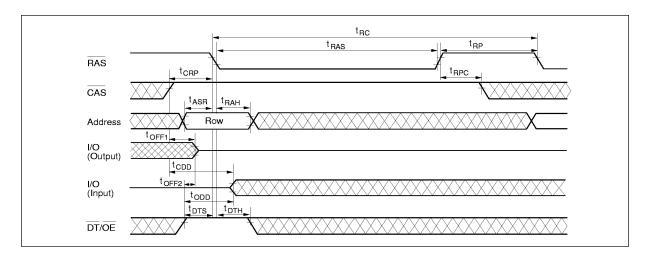

### **Read Cycle**

### **Early Write Cycle**

### **Delayed Write Cycle**

### Read-Modify-Write Cycle

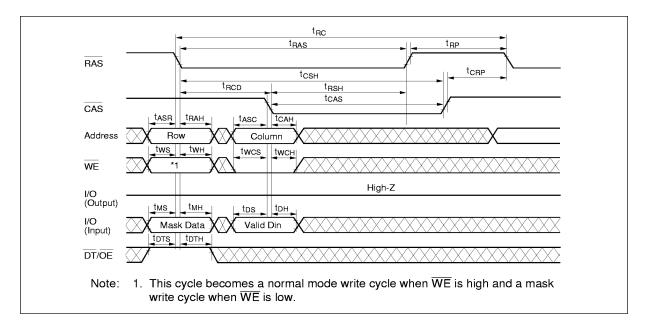

### Page Mode Read Cycle

### Page Mode Write Cycle (Early Write)

### Page Mode Write Cycle (Delayed Write)

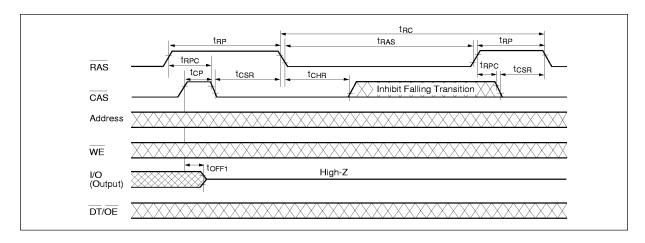

### **RAS**-Only Refresh Cycle

# $\overline{\text{CAS}}\text{-Before-}\overline{\text{RAS}}$ Refresh Cycle

### **Hidden Refresh Cycle**

### Read Transfer Cycle (1)

### Read Transfer Cycle (2)

### Pseudo Transfer Cycle

# Write Transfer Cycle

# **Serial Read Cycle**

### **Serial Write Cycle**

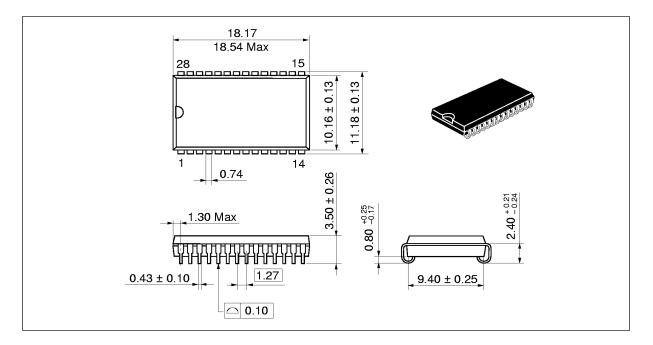

# **Package Dimensions**

### **HM534251BJ Series** (CP-28D)

Unit: mm

### **HM534251BZ Series** (ZP-28)

Unit: mm