# HM62A2016 Series

## Dual 8,192-Word x 20-Bit Static Cache Memory

#### **■ DESCRIPTION**

The HM62A2016 is a high speed 327,680-bit cache memory organized as two banks of 8,192 words by 20-bits. The device includes dual address latches, dual chip select latches, data multiplexer with multiple chip enables and output enables. It can be used in a cache memory system adopting Harvard architecture which requires separate instruction and data storages.

#### **FEATURES**

- High speed: up to 33 MHz operation Address access time: 17/20/25/30 ns Output enable access time: 7/7/8/8 ns

- Dual 8k x 20 memory arrays with data multiplexer

- · Dual latches for address and chip select inputs

- Expandable both in width and depth Two separate chip selects

- 52-pin PLCC

## **■ ORDERING INFORMATION**

| Type No.                                           | Access Time             | Package                   |

|----------------------------------------------------|-------------------------|---------------------------|

| HM62A2016CP-17<br>HM62A2016CP-20<br>HM62A2016CP-25 | 17 ns<br>20 ns<br>25 ns | 52-pin<br>PLCC<br>(CP-52) |

| HM62A2016CP-30                                     | 30 ns                   | (Ct -32)                  |

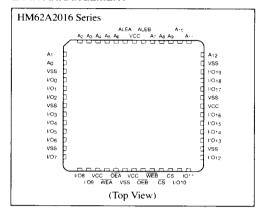

#### ■ PIN ARRANGEMENT

## **■ PIN DESCRIPTION**

| Pin Name                            | Function            |

|-------------------------------------|---------------------|

| A0-A12                              | Address Inputs      |

| ALEA, ALEB                          | Latch Enables       |

| OEA, OEB                            | Output Enables      |

| WEA, WEB                            | Write Enable        |

| I/O <sub>0</sub> -I/O <sub>19</sub> | Data Inputs Outputs |

| CS, CS                              | Chip Selects        |

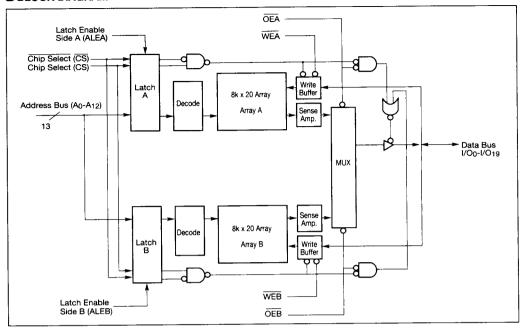

#### **■ BLOCK DIAGRAM**

## **Signal Description**

| Signal Name                          | Pin Number    | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A12                               | 3–9           | Shared address inputs to both Memory Array A and Memory Array B. Current A0-A12                                                                                                                                                                                                                                                                                                                                                                                   |

|                                      | 46–51         | values are latched into Latch A or Latch B by the falling edge of ALEA or ALEB.                                                                                                                                                                                                                                                                                                                                                                                   |

| ALEA, ALEB                           | 2, 52         | Latch enable inputs. When ALEA or ALEB is high, Latch A or Latch B is transparent to address and chip select input values. The falling edge of ALEA and ALEB latches current inputs at A0-A12 and current states of CS and $\overline{CS}$ . These latched values remain applied to the respective memory arrays until ALEA or ALEB transition to a high state                                                                                                    |

| CS, CS                               | 30, 31        | Active low and active high chip select inputs. The current states of CS and $\overline{CS}$ are latched by the falling edge of ALEA and ALEB. When $\overline{CS}$ is low and CS is high read and write access to both arrays is possible. $\overline{CS}$ should be grounded and CS should be tied to $VCC$ in applications where no device depth expansion takes place. See the Depth Expansion Section for a detailed description of the chip select function. |

| WEA, WEB                             | 24, 29        | Active low write enable inputs. $\overline{WEA}$ controls writing into Array A and $\overline{WEB}$ controls writing into Array B. Both $\overline{WEA}$ and $\overline{WEB}$ must not be both low simultaneously.                                                                                                                                                                                                                                                |

| OEA, OEB                             | 25, 28        | Active low output enable inputs. $\overline{OEA}$ and $\overline{OEB}$ are used to control driving of stored data from Array A or Array B onto the I/O lines during read operations. $\overline{OEA}$ and $\overline{OEB}$ must not be both low simultaneously.                                                                                                                                                                                                   |

| I/O <sub>0</sub> , I/O <sub>19</sub> | 11–13, 15–18  | Data inputs and outputs. These are three-state lines that provide data access to both                                                                                                                                                                                                                                                                                                                                                                             |

|                                      | 20–22, 32–34, | memory arrays.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                      | 36-39, 42-44  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### **FUNCTION TABLE**

| CS | CS | ALEA | ALEB | WEA | WEB | ŌĒĀ | OEB | Operation                                | I/O Status     |

|----|----|------|------|-----|-----|-----|-----|------------------------------------------|----------------|

| L  | Х  | *1   | *1   | X   | Х   | X   | Х   | Not Selected                             | Outputs High-Z |

| X  | Н  | *1   | *1   | X   | Х   | X   | X   | Not Selected                             | Outputs High-Z |

| Н  | L  | Х    | X    | Н   | Н   | Н   | Н   | Data I/O's Disabled                      | Outputs High-Z |

| Н  | L  | Н    | х    | Н   | Н   | L   | Н   | Read from Array A<br>(Current Addresses) | Data Out       |

| н  | L  | L    | Х    | Н   | Н   | L   | Н   | Read from Array A<br>(Latched Addresses) | Data Out       |

| н  | L  | х    | Н    | Н   | Н   | Н   | L   | Read from Array B<br>(Current Addresses) | Data Out       |

| Н  | L  | х    | L    | н   | Н   | Н   | L   | Read from Array B<br>(Latched Addresses) | Data Out       |

| Н  | L  | х    | Х    | Х   | х   | L*2 | L*2 | Not Allowed in<br>Same Phase             | _              |

| Н  | L  | Н    | Х    | L   | Н   | Н   | Н   | Write to Array A<br>(Current Addresses)  | Data In        |

| Н  | L  | L    | х    | L   | Н   | Н   | Н   | Write to Array A<br>(Latched Addresses)  | Data In        |

| Н  | L  | Х    | Х    | L*3 | Н   | L*3 | Н   | Not Allowed in<br>Same Phase             |                |

| н  | L  | х    | Х    | L*4 | Н   | Н   | L*4 | Not Allowed in<br>Same Phase             |                |

| Н  | L  | х    | Н    | Н   | L   | Н   | Н   | Write to Array B<br>(Current Addresses)  | Data In        |

| Н  | L  | х    | L    | Н   | L   | Н   | Н   | Write to Array B<br>(Latched Addresses)  | Data In        |

| Н  | L  | х    | х    | Н   | L*4 | L*4 | Н   | Not Allowed in<br>Same Phase             | _              |

| Н  | L  | х    | х    | Н   | L*3 | Н   | L*3 | Not Allowed in<br>Same Phase             | _              |

| Н  | L  | х    | Х    | L*5 | L*5 | х   | x   | Not Allowed in Same Phase                | <u> </u>       |

X = Don't care, H = High, L = Low, High-Z = High Impedance

Notes: 1. CS and CS values shown in the table must have propagated through transparent latches and meet specified chip select setup times before a deselect operation can occur.

- 2. If data are read simultaneously from both arrays, an undefined data outputs. Specified AC and DC parameters are not guaranteed in this state.

- 3. Simultaneous reading and writing of a single array or of both arrays is not permitted.

- 4. Simultaneous reading from one array while writing to the other array is not possible.

- 5. Simultaneous writing to both arrays is not permitted during normal R3000 based cache operation.

#### **■ FUNCTIONAL DESCRIPTION**

The HM62A2016 is a highly-integrated memory device with several performance-enhancing features which allow direct interfacing to a MIPS R3000 or R3000A RISC processor. Two independent address latches, with fast setup times, are provided on-chip to allow faster addressing of two 8k x 20 memory arrays, Array A and Array B. Address inputs and data I/O lines are shared between the two arrays.

Two sets of OE and WE inputs, coupled with an onboard multiplexer control read and write access to each of the arrays. Integrating a 2:1 output data multiplexer onchip reduces the problem of data bus contention that may occur when using discrete SRAMs and multiplexers, and allows easier synchronization of output enable signals.

OEA and OEB inputs directly control the driving of stored data at the outputs of the HM62A2016 during read operations. Fast (7 ns) output enable and disable times are matched and permit data to be quickly taken off the data bus as well as driven on. This high level of device feature integration demonstrated by the HM62A2016 allows construction of a dual 32-kbyte cache memory subsystem by combining only three devices together to reach the full 60-bit tag plus data width requirements of the MIPS R3000(a) processor.

The HM62A2016 is designed to permit storage and retrieval of tag address and cache data information to and from the two memory arrays in a direct-mapped, split data/instruction cache format. It is functionally compatible to and meets all MIPS R3000(A) cache memory timing requirements. The HM62A2016 fully supports "pipelined" reads and writes, as described below.

Valid addresses that appear at A<sub>0</sub>—A<sub>12</sub> inputs are recognized by on-chip Latches A or B when they are transparent (i.e. when ALEA or ALEB inputs are high). Current address input values are latched by the falling edge of ALEA and ALEB.

For an R3000(A) to HM62A2016 cache interface, addresses are latched during the first phase of a 2-phase read operation cycle, and valid data appears at outputs (I/O<sub>0</sub>-I/O<sub>19</sub>) during the second phase. These addresses will remain latched and applied to Array A or Array B as long as ALEA or ALEB remains low. Similarly, for a write operation, valid addresses are also latched during the first phase, while data is actually written into the addressed location during the second phase.

These sequential reads occur in a pipe-lined manner, where data or instructions are read from one array during the same phase when addresses for a subsequent read from the other array are latched. Similarly, alternating consecutive writes to the two memory arrays are possible as long as the minimum 2-phase write operation cycle is met with correct timings.

A write operation to a memory array can occur in the phase that immediately precedes or follows a read operation from the other array.

It is not possible to write to or read from both arrays at the same time. Nor is it possible to do more than one read or write per phase. It is not possible to read from or write to the same array in consecutive phases because of the minimum 2-phase read/write operation cycle requirements. See the Function Table for a detailed listing of prohibited operations, as well as legitimate read and write modes.

Array A and B are interchangeable and can arbitrarily be designated as for data or instruction storage.

### **Depth Expansion**

### Overview

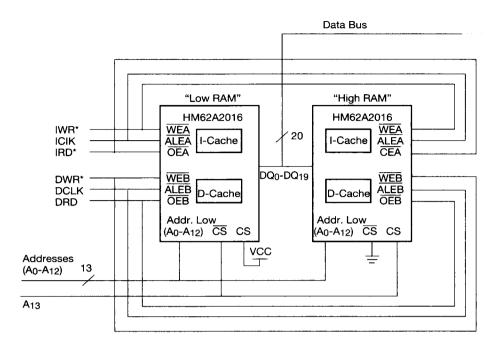

Each HM62A2016 has a latched active high chip select input (CS) as well as an active low input (CS). Depth expansion is achieved by connecting address line (A13) into CS and CS inputs of two HM62A2016's and grounding or tying to VCC the other remaining chip select of each device, as shown in figure 1. Corresponding (A or B) control inputs (OE, WE, and ALE) of depth-expanded HM62A2016's should be tied together.

The latched chip select function of the HM62A2016 is designed to permit one array to be latched "on" (active for read or write access) while the other corresponding array of a different davice is turned "off".

## **Detailed Description**

The current states of CS and  $\overline{CS}$  are latched on-chip by the falling edge of ALEA or ALEB. An "array select" state (both  $\overline{CS}=1$  and  $\overline{CS}=0$ ), that passes through a single transparent Latch (A or B) and meets tCSL timing, will permit that particular array (A or B) to be active for read and write access. An array in a selected state will remain active as long as its ALE input remains low. If an array select state is recognized by both transparent latches (A and B), then both arrays for that HM62A2016 device will be active.

A "deselect" state (either  $\overline{CS} = 0$  or  $\overline{CS} = 1$ ) that propagates through a single transparent latch (A or B) and meets the minimum specified chip select setup time will disable both read and write access to that respective array (Array A or Array B). If a deselecting input state passes through both transparent latches A and B, then read and write access to both arrays is disabled.

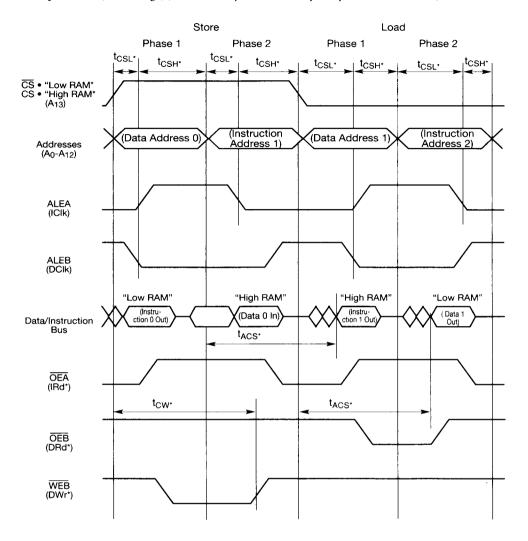

#### Example

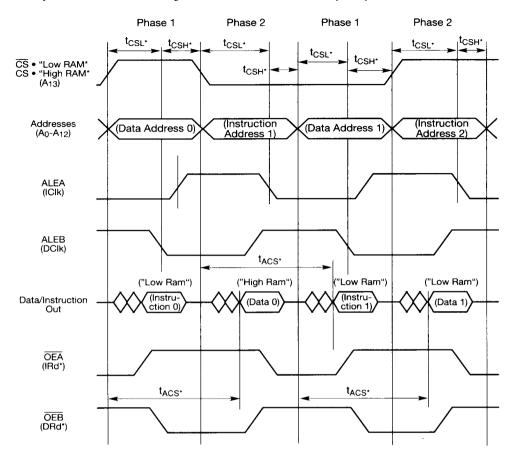

An example of consecutive reads from two depthexpanded HM62A2016's is shown in Read Cycle No. 2. In the first phase, an instruction is read from the I-cache of the "low RAM". At the beginning of this phase, A13 transitions from low to high and causes the selection of the D-cache array of the "high RAM" for a read operation in the following phase. This high A13 state also deselects the D-cache array of the "low RAM" for the following phase.

Consecutive operations are possible because the latching of A13 to select or deselect an array can occur in the same phase as a read or write operation from another array of a different HM62A2016.

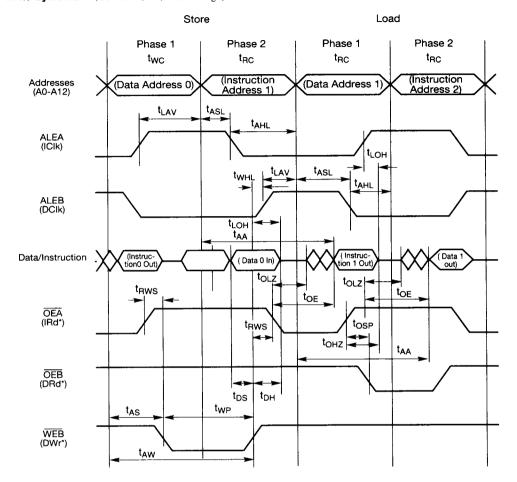

As a further example, the timings for a depthexpanded store-load sequence are shown in Write Cycle No. 2.

Figure 1. 16k x 20 x 2 Cache SRAM from two 8K x 20 x 2 Cache SRAMs

#### **■ ABSOLUTE MAXIMUM RATINGS**

| Item                                 | Symbol | Value              | Unit |

|--------------------------------------|--------|--------------------|------|

| Supply Voltage relative to VSS       | Vcc    | -0.5*1 to +7.0     | V    |

| Voltage on any pin relative to VSS   | Vin    | -0.5*1 to VCC +0.3 | V    |

| Power Dissipation                    | PT     | 2.0                | w    |

| Operating Temperature Range          | Topr   | 0 to +70           | °C   |

| Storage Temperature Range            | Tstg   | -55 to +125        | °C   |

| Storage Temperature Range Under Bias | Tbias  | -10 to +85         | °C   |

Note: 1.  $V_{in} min = -2.5 V$  for pulse width 10 ns.

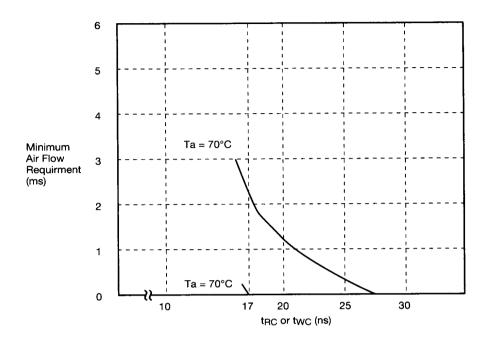

## ■ RECOMMENDED DC OPERATING CONDITIONS (Ta = 0 to +70°C, exceeding minimum air flow requirement)

| Parameter                    | Symbol       | Min.   | Тур | Max.      | Unit |

|------------------------------|--------------|--------|-----|-----------|------|

| Supply Voltage               | Vcc          | 4.5    | 5.0 | 5.5       | V    |

|                              | VSS          | 0      | 0   | 0         | V    |

| Input High (Logic 1) Voltage | VIH          | 2.2    |     | Vcc + 0.3 | V    |

| Input Low (Logic 0) Voltage  | $V_{\rm IL}$ | -0.5*1 |     | 0.8       | V    |

Note: 1. VIL min = -2.0V for pulse width 10 ns.

- 2. The supply voltage with all VCC pins must be on the same level.

- 3. The supply voltage with all VSS pins must be on the same level.

## ■ DC CHARACTERISTICS (T<sub>a</sub> = 0 to 70°C, V<sub>CC</sub> = 5V ± 10%, V<sub>SS</sub> = 0V, exceeding minimum air flow requirement)

| Parameter                             | Symbol | Min. | Тур | Max. | Unit | Test Conditions                                                                                                                                                    |

|---------------------------------------|--------|------|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Leakage Current                 | ILI    | 1 —  |     | 2.0  | μA   | VCC = Max., Vin = VSS to VCC                                                                                                                                       |

| Output Leakage Current                | ILO    |      | _   | 2.0  | μА   | Output Disable<br>VI/O = VSS to VCC                                                                                                                                |

| Active Operating Power Supply Current | Icc    | _    | _   | 220  | mA   | $V_{in} = V_{SS}$ to $V_{CC}$ , Outputs Open<br>Load, $I_{out} = 0$ mA, $t_{cycle} = Min$ . Cycle,<br>$\overline{CS} = V_{IL}$ Max., $\overline{CS} = V_{IH}$ Min. |

| Output Low Voltage                    | Vol    | _    | _   | 0.4  | V    | IOL =8 mA                                                                                                                                                          |

| Output High Voltage                   | Voh    | 2.4  |     | _    | V    | IOH = -4 mA                                                                                                                                                        |

Note: 1. Typical limits are at VCC = 5.0V, Ta = +25°C and specified loading

## ■ CAPACITANCE $(T_a = 25^{\circ}C, f = 1 \text{ MHz.})^{*1}$

| Parameter                | Symbol           | Min | Max | Unit | Test Conditions |

|--------------------------|------------------|-----|-----|------|-----------------|

| Input Capacitance        | Cin              | _   | 5   | pF   | $V_{in} = 0V$   |

| Input/Output Capacitance | C <sub>I/O</sub> |     | 10  | pF   | VI/O = 0V       |

Note: 1. This parameter is sampled and not 100% tested.

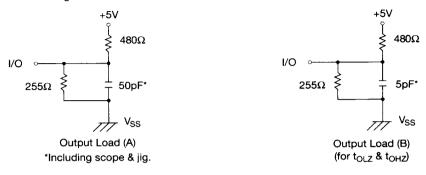

## **AC CHARACTERISTICS** ( $V_{CC} = 5V \pm 10\%$ , $T_a = to 70$ °C, exceeding minimum air flow requirement)

#### **Test Conditions**

• Input and Output timing reference levels: 1.5V

Input pulse levels: Vss to 3V

· Output load: See figures

#### **■ READ CYCLE**

|                                        | Frequency | 33 MHz<br>HM62A2016-17 |     | 25 MHz<br>HM62A2016-20 |         | 20 MHz<br>HM62A2016-25 |     | 16.67 MHz<br>HM62A2016-30 |     | Unit |

|----------------------------------------|-----------|------------------------|-----|------------------------|---------|------------------------|-----|---------------------------|-----|------|

| Parameter                              | Symbol    |                        |     |                        |         |                        |     |                           |     |      |

|                                        |           | Min                    | Max | Min                    | Max     | Min                    | Max | Min                       | Max |      |

| Read Cycle Time                        | tRC       | 17                     |     | 20                     |         | 25                     |     | 30                        | -   | ns   |

| Address Valid to Output Valid          | tAA       |                        | 17  |                        | 20      |                        | 25  |                           | 30  | ns   |

| Chip Select Access Time                | tACS*1    | _                      | 17  |                        | 20      | _                      | 25  |                           | 30  | ns   |

| Output Enable Low to Output Valid      | tOE       |                        | 7   |                        | 7       | _                      | 8   |                           | 8   | ns   |

| Output Enable Low to Output Low-Z      | tOLZ      | 1                      |     | 2                      | _       | 2                      | -   | 2                         |     | ns   |

| Output Enable High to Output High-Z    | tOHZ      | 0                      | 7   | 0                      | 7       | 0                      | 8   | 0                         | 8   | ns   |

| Output Hold from Latch Enable          | ŧLОН      | 3                      |     | 3                      | _       | 3                      |     | 3                         |     | ns   |

| Address Setup to Latch Enable Low      | tASL      | 5                      |     | 5                      |         | 5                      |     | 5                         |     | ns   |

| Address Hold from Latch Enable Low     | tAHL      | 2                      | _   | 2                      | energe. | 2                      | _   | 2                         |     | ns   |

| Chip Select Setup to Latch Enable Low  | tCSL*1    | 5                      | _   | 5                      | _       | 5                      |     | 5                         |     | ns   |

| Chip Select Hold from Latch Enable Low |           | 2                      |     | 2                      | _       | 2                      |     | 2                         |     | ns   |

| Output Enable Separation Time          | tOSP      | 2                      | _   | 2                      | _       | 2                      |     | 2                         |     | ns   |

| Latch High to Address Valid            | tLAV      | 3                      | _   | 3                      |         | _3                     |     | 3                         |     | ns   |

Note: 1. Indicates depth expansion parameter only. These parameters apply for both CS and  $\overline{\text{CS}}$ .

#### **■ WRITE CYCLE**

|                                        | Frequency | 33 MHz       |     | 25 MHz       |     | 20 MHz       |     | 16.67 MHz    |     | Unit |

|----------------------------------------|-----------|--------------|-----|--------------|-----|--------------|-----|--------------|-----|------|

| Parameter                              | Symbol    | HM62A2016-17 |     | HM62A2016-20 |     | HM62A2016-25 |     | HM62A2016-30 |     |      |

|                                        | -,        | Min          | Max | Min          | Max | Min          | Max | Min          | Max |      |

| Write Cycle Time                       | twc       | 17           | _   | 20           |     | 25           |     | 30           |     | ns   |

| Address Valid to End of Write          | tAW       | 12           |     | 15           | -   | 20           | _   | 25           |     | ns   |

| Data Valid to End of Write             | tDS       | 6            | _   | 8            |     | 8            |     | 10           |     | ns   |

| Data Hold from End of Write            | tDH       | 0            | _   | 0            | _   | 0            |     | 0            | _   | ns   |

| Write Pulse Width                      | tWP       | 10           |     | 15           |     | 17           | -   | 22           |     | ns   |

| Chip Enable to End of Write            | tcw*1     | 12           | _   | 15           | _   | 20           |     | 25           | _   | ns   |

| Address Setup Time Before Write Start  |           | 0            |     | 0            | _   | 0            | _   | 0            | _   | ns   |

| Latch Enable Hold from End of Write    | tWHL      | 0            |     | 0            |     | 0            |     | 0            |     | ns   |

| Address Setup to Latch Enable Low      | tASL      | 5            |     | 5            | _   | 5            | _   | 5            |     | ns   |

| Address Hold from Latch Enable Low     | tAHL      | 2            |     | 2            | _   | 2            | _   | 2            |     | ns   |

| Chip Select Setup to Latch Enable Low  | tCSL*1    | 5            | _   | 5            |     | 5            | _   | 5            |     | ns   |

| Chip Select Hold from Latch Enable Low | tCSH*1    | 2            |     | 2            |     | 2            | _   | 2            |     | ns   |

| Read/Write Separation Time             | tRWS      | 2            | _   | 2            | _   | 2            |     | 2            |     | ns   |

| Latch High to Address Valid            | tLAV      | 3            | _   | 3            |     | 3            | _   | 3            | _   | ns   |

Note: 1. Indicates depth expansion parameter only. These parameters apply for both CS and  $\overline{\text{CS}}$ .

### **■ TIMING WAVEFORMS**

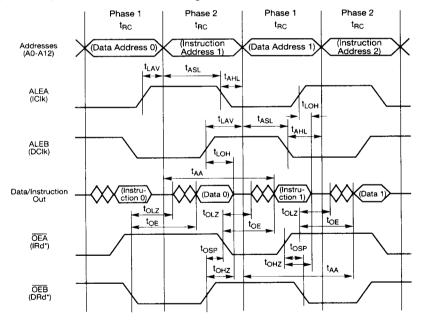

**Read Cycle No. 1** ( $\overline{CS}$  = Low, CS,  $\overline{WEA}$ ,  $\overline{WEB}$  = High)

Notes:

- 1. All timing parameters are measured with output Load A unless otherwise noted.

- Read cycle time (tRC) refers to read operations with current addresses applied to a transparent (high) latch. Read timing parameters are referenced from the last valid address to the first transition address.

- Transition is measured ±200 mV from steady state voltage with output Load B for tOLZ and tOHZ.

These parameters are sampled and not 100% tested.

# **@**HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 341

Read Cycle No. 2 (WEA, WEB = High) (Consecutive Reads from Two Depth-Expanded HM62A2016's)

Note: 1. All other non depth-expansion parameters shown in Read Cycle No. 1 still apply, and are not shown for simplicity.

Write Cycle No. 1 ( $\overline{CS} = Low, CS, \overline{WEA} = High)$

Notes:

- 1. All timing parameters are measured with output Load A unless otherwise noted.

- 2. Write cycle time refers to write operations with current addresses applied to a transparent (high) latch.

- Transition is measured ± 200 mV from steady state voltage with output Load B for toLZ and toHZ. These parameters are sampled and not 100% tested.

Write Cycle No. 2 (WEA = High) (Store-Load Sequence of Two Depth-Expanded HM62A2016's)

Note: 1. All other non depth-expansion parameters shown in Write Cycle No. 1 still apply, and are not shown for simplicity.

## **Air Flow Requirements**