# General Purpose PIR Controller

#### **Features**

- Operating voltage: 5V~12V

Standby current: 100μA (Typ.)

- · On-chip regulator

- · Adjustable output duration

- CDS input

- 40 second warm-up

- ON/AUTO/OFF selectable by MODE pin

- Override function

- Auto-reset if the ZC signal disappears over 3 seconds

- 16-pin DIP package

#### **Applications**

- PIR light controllers

- · Motion detectors

- · Alarm systems

- · Auto door bells

### **General Description**

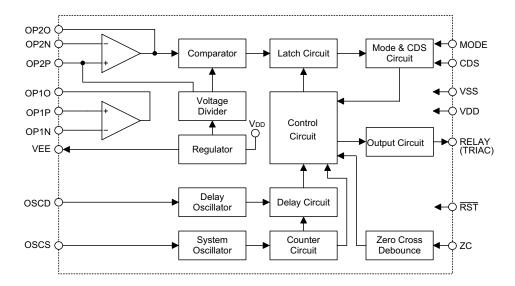

The HT761X is a CMOS LSI chip designed for use in automatic PIR lamp control. It can operate with a 2-wire configuration for triac applications or with a 3-wire configuration for relay applications. The chip is equipped with operational amplifiers, a comparator, timer, a zero crossing detector, control circuit, a voltage regulator, a system oscillator, and an output timing oscillator.

Its PIR sensor detects infrared power variations induced by the motion of a human body and transforms it to a voltage variation. If the PIR output voltage variation conforms to the criteria (refer to the functional description), the lamp is turned on with an adjustable duration.

The HT761X offers three operating modes (ON, AUTO, OFF) which can be set through the MODE pin. While the chip is working in the AUTO mode the user can override it and switch to the TEST mode, or manual ON mode, or return to the AUTO mode by switching the power switch.

#### **Selection Table**

| Part No.           | ZC Off/On<br>for Override | Flash on Mde<br>Auto-change | Override ON<br>Duration | Comparator<br>Window                          | Effective Trigger<br>Width |

|--------------------|---------------------------|-----------------------------|-------------------------|-----------------------------------------------|----------------------------|

| HT7610A<br>HT7610B | 2 times                   | Flash                       | 8 hrs                   | $\frac{1}{16} \left( V_{DD} - V_{EE} \right)$ | >24ms                      |

| HT7611A<br>HT7611B | 1 time                    | No flash                    | 8 hrs                   | $\frac{1}{16} \left( V_{DD} - V_{EE} \right)$ | >24ms                      |

Note: Part numbers suffixed with A are for Relay application while those suffixed with B are for Triac application.

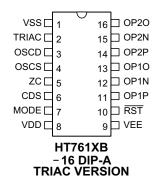

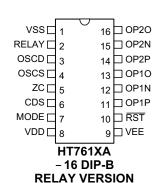

#### **Pin Assignment**

# **Block Diagram**

# **Pin Description**

| Pin Name | I/O | Internal<br>Connection | Description                                                                                                                                                                             |  |

|----------|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VSS      | _   | _                      | Negative power supply, ground                                                                                                                                                           |  |

| RELAY    | 0   | CMOS                   | RELAY drive output through an external NPN transistor, active high.                                                                                                                     |  |

| TRIAC    | 0   | CMOS                   | TRIAC drive output The output is a pulse output when active.                                                                                                                            |  |

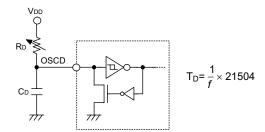

| OSCD     | I/O | PMOS IN<br>NMOS OUT    | Output timing oscillator I/O It is connected to an external RC to adjust output duration.                                                                                               |  |

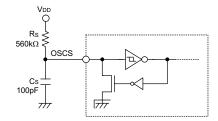

| oscs     | I/O | PMOS IN<br>NMOS OUT    | System oscillator I/O OSCS is connected to an external RC to set the system frequency. The system frequency is at 16kHz for normal application.                                         |  |

| ZC       | ı   | CMOS                   | Input for AC zero crossing detection                                                                                                                                                    |  |

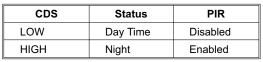

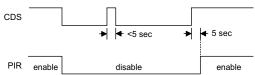

| CDS      | I   | CMOS                   | CDS is connected to a CDS voltage divider for daytime/nig auto-detection. Low input to this pin can disable the PIR input. CDS Schmitt Trigger input with 5-second input debounce time. |  |

| MODE     | I   | CMOS                   | Operating mode selection input: VDD: Output is always ON VSS: Output is always OFF Open: Auto detection                                                                                 |  |

| VDD      | _   |                        | Positive power supply                                                                                                                                                                   |  |

| VEE      | 0   | NMOS                   | Regulated voltage output The output voltage is –4V with respect to VDD.                                                                                                                 |  |

| RST      | ı   | Pull-High              | Chip reset input, active low                                                                                                                                                            |  |

| OP1P     | ı   | PMOS                   | Noninverting input of OP1                                                                                                                                                               |  |

| OP1N     | ı   | PMOS                   | Inverting input of OP1                                                                                                                                                                  |  |

| OP10     | 0   | NMOS                   | Output of OP1                                                                                                                                                                           |  |

| OP2P     | ı   | PMOS                   | Noninverting input of OP2                                                                                                                                                               |  |

| OP2N     | ı   | PMOS                   | Inverting input of OP2                                                                                                                                                                  |  |

| OP2O     | 0   | NMOS                   | Output of OP2                                                                                                                                                                           |  |

Rev. 1.10 2 September 18, 2002

# **Absolute Maximum Ratings**

| Supply Voltage0.3V to 13V                              | Storage Temperature50°C to 125°C   |

|--------------------------------------------------------|------------------------------------|

| Input VoltageV <sub>SS</sub> $-0.3V$ to $V_{DD}$ +0.3V | Operating Temperature–25°C to 70°C |

| Zero Crossing CurrentMax. 300μA                        |                                    |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

#### **Electrical Characteristics**

| Committee of     | Dawanatan                               |                 | Test Condition                                       |                    | T    | N4                 | 11:4 |

|------------------|-----------------------------------------|-----------------|------------------------------------------------------|--------------------|------|--------------------|------|

| Symbol           | Parameter                               | V <sub>DD</sub> | Condition                                            | Min.               | Тур. | Max.               | Unit |

| $V_{DD}$         | Operating Voltage                       |                 | _                                                    | 5                  | 9    | 12                 | V    |

| V <sub>EE</sub>  | Regulator Output Voltage                | 12V             | V <sub>DD</sub> -V <sub>EE</sub>                     | 3.5                | 4    | 4.5                | V    |

| I <sub>DD</sub>  | Operating Current                       | 12V             | No load, OSC on                                      | _                  | 100  | 350                | μА   |

| I <sub>OH1</sub> | OUTPUT Source Current<br>(RELAY, TRIAC) | 12V             | V <sub>OH</sub> =10.8V                               | -6                 | 12   | _                  | mA   |

| I <sub>OL1</sub> | OUTPUT Sink Current<br>(RELAY, TRIAC)   | 12V             | V <sub>OL</sub> =1.2V                                | 40                 | 80   | _                  | mA   |

| I <sub>OL2</sub> | VEE Sink Current                        | 12V             | V <sub>DD-VEE</sub> =4V                              | _                  | _    |                    | mA   |

| V <sub>IH</sub>  | "H" Input Voltage                       | _               | _                                                    | 0.8V <sub>DD</sub> | _    | _                  | V    |

| V <sub>IL</sub>  | "L" Input Voltage                       | _               | _                                                    | _                  | _    | 0.2V <sub>DD</sub> | V    |

| V <sub>TH1</sub> | CDS "H" Transfer Voltage                | 12V             | _                                                    | 6.4                | 8    | 9.6                | V    |

| V <sub>TL1</sub> | CDS "L" Transfer Voltage                | 12V             | _                                                    | 3.7                | 4.7  | 5.6                | V    |

| V <sub>TH2</sub> | ZC "H" Transfer Voltage                 | 12V             | _                                                    | 4.7                | 6.7  | 8.7                | V    |

| V <sub>TL2</sub> | ZC "L" Transfer Voltage                 | 12V             | _                                                    | 1.3                | 1.8  | 2.3                | V    |

| Vos              | OP Amp Input Offset Voltage             | 12V             | No load                                              | _                  | 10   | 35                 | mV   |

| f <sub>SYS</sub> | System Oscillator Frequency             | 12V             | R <sub>OSCS</sub> =560kΩ<br>C <sub>OSCS</sub> =100pF | 12.8               | 16   | 19.2               | KHz  |

| f <sub>d</sub>   | Delay Oscillator Frequency              | 12V             | R <sub>OSCD</sub> =560kΩ<br>C <sub>OSCD</sub> =100pF | 12.8               | 16   | 19.2               | KHz  |

| A <sub>VO</sub>  | OP Amp Open Loop Gain                   | 12V             | No load                                              | 60                 | 80   | _                  | dB   |

# **Functional Description**

### VEE

VEE supplies power to the analog front end circuit with a normally stabilized voltage of -4V with respect to VDD.

#### oscs

OSCS is a system oscillator input pin. When it is connected to an external RC, a system frequency of 16kHz can be generated.

System oscillator

Rev. 1.10 3 September 18, 2002

#### **OSCD**

OSCD is an output timing oscillator input pin. It is connected to an external RC to obtain the desired output turn-on duration. Variable output turn-on durations can be achieved by selecting various values of RC or using a variable resistor.

Output timing oscillator

#### **RELAY (TRIAC)**

RELAY is an output pin set as a RELAY driving (active high) output for the HT761XA, or as a TRIAC driving (active low) output for the HT761XB.

The output active duration is controlled by the OSCD oscillating period.

|        | HT761XA | HT761XB |

|--------|---------|---------|

| OUTPUT | RELAY   | TRIAC   |

#### CDS

CDS is a CMOS Schmitt Trigger input structure. It is used to distinguish between day time and night time. When the input voltage of CDS is high the PIR input is enabled. On the other hand, when CDS is low the PIR input is disabled. The input disable to enable debounce time is 5 seconds. Connect this pin to VDD when this function is not used. The CDS input is ignored when the output is active.

#### **MODE**

MODE is a tristate input pin used to select the operating mode.

| MODE<br>Status | Operating<br>Mode | Description                                                                                                                                                                      |

|----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD            | ON                | Output is always ON:<br>RELAY outputs high for relay driving.<br>TRIAC pulse train output is syn-<br>chronized by ZC for triac driving.                                          |

| VSS            | OFF               | Output is always OFF:<br>RELAY outputs low for relay driving.<br>TRIAC outputs high for triac driving.                                                                           |

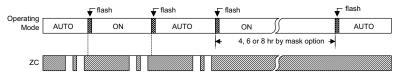

| Open           | AUTO              | Outputs remain in the off state until activated by a valid PIR input trigger signal. When working in the AUTO mode, the chip allows override control by switching the ZC signal. |

<sup>#:</sup> flash 3 times at a 2Hz rate flash or not by mask option

#### ZC

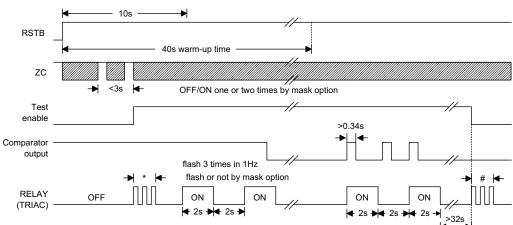

ZC is a CMOS input structure. It receives AC line frequency and generates zero crossing pulses to synchronize the triac driver. By effective ZC signal switching (switch OFF/ON 1 or 2 times within 3 seconds by mask option), the chip provides the following additional functions:

#### • Test mode control

Within 10 seconds after power-on, effective ZC switching will force the chip to enter the test mode. During the test mode, the outputs will be active for a duration of 2 seconds each time a valid PIR trigger signal is received. If a time interval exceeds 32 seconds without a valid trigger input, the chip will automatically enter the AUTO mode.

#### · Override control

When the chip is working in an AUTO mode (MODE=open), the output is activated by a valid PIR trigger signal and the output active duration is controlled by an OSCD oscillating period. The lamp can be switched always to "ON" from the AUTO mode by either switching the MODE pin to VDD or switching the ZC signal by an OFF/ON operation of the power switch (OFF/ON once or twice within 3 seconds by mask option). The term "override" refers to the change of operating mode by switching the power switch. The chip can be toggled from ON to AUTO by an override operation. If the chip is overridden to ON and there is no further override operation, it will automatically return to AUTO after an internal preset ON time duration has elapsed. This override ON time duration can be set to 4 or 6 or 8 hours by mask option. The default is 8 hours.

The chip provides a mask option to determine the output flash times (3 times) when changing the operating mode. It will flash 3 times at a 1Hz rate each time the chip changes from an AUTO mode to another mode or flash 3 times at a 2Hz rate when returning to the AUTO mode. But if the AUTO mode is changed by switching the MODE switch it will not flash.

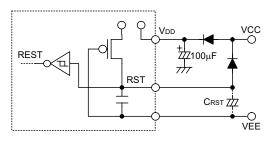

#### RST

RST is used to reset the chip. It is internal pull-high and active low.

The use of  $C_{RST}$  can extend the power-on initial time. If the  $\overline{RST}$  pin is an open circuit (without  $C_{RST}$ ), the initial time is the default (40 secs).

Fig.1 RST application example

#### Power on initial

The PIR signal amplifier requires a warm up period after power-on. The input should be disabled during this period.

In the AUTO mode within the first 10 seconds of power-on initialization, the chip allows override control to enter the test mode. After 40 seconds of the initial time the chip allows override control between ON and AUTO. It will remain in the warm up period if the total initial time has not elapsed after returning to AUTO.

In case that the ZC signal disappears for more than 3 seconds, the chip will restart the initialization operation. However, the restart initial time is always 40 seconds and cannot be extended by adding  $C_{RST}$  to the  $\overline{RST}$  pin as shown in the Fig.1.

#### Mask options

The HT761X offers mask options to select the output flash (3 times) when changing the operating mode. The chip will flash 3 times at a 1Hz rate each time it changes from AUTO to another mode and flash 3 times at a 2Hz rate when it returns to the AUTO mode. However the chip will not flash if the mode is changed by switching the MODE switch.

- 4, 6, or 8 hour options to return to AUTO from override ON. The default is 8 hours.

- Options for effective override: Once or twice OFF/ON operation of power switch within 3 seconds. The default is OFF/ON twice.

- Options for output flash to indicate effective override operation. The default is to flash.

- Options for effective PIR trigger pulse width: >24mS, >32mS or >48mS. The default is 24ms.

ZC override timing

Rev. 1.10 5 September 18, 2002

• Options for setting the comparator window to be  $\frac{1}{16}$ :  $\frac{1}{11.3}$  or  $\frac{1}{9}$  (V<sub>DD</sub>-V<sub>EE</sub>).

The default is  $\frac{1}{16}$  (V<sub>DD</sub>-V<sub>EE</sub>).

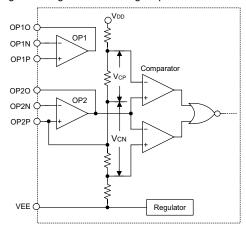

#### PIR amplifier

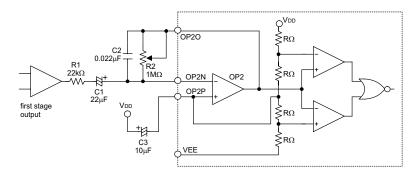

Consult the diagram below for details on the PIR front end amplifier.

In the Fig.2 below there are 2 op-amps with different applications. OP1 can be used independently as a first stage inverting or non-inverting amplifier for the PIR.

Fig.2 PIR amplifier

As the output of OP2 is directly connected to the input of the comparator, it is used as a second stage amplifying device. The non-inverting input of OP2 is connected to the comparator's window center point and can be used to check this voltage and to provide a bias voltage that is equal to the center point voltage of the comparator. In Fig.2 the comparator can have 3 window levels set by mask option. 1.  $\frac{1}{16}$  ( $V_{DD}-V_{EE}$ ), 2.  $\frac{1}{11.3}$  ( $V_{DD}-V_{EE}$ ), 3.  $\frac{1}{0}$  ( $V_{DD}-V_{EE}$ ).

If the window level fails to be specified the default window is set to  $\frac{1}{16}~(V_{DD}-V_{EE}).$  The preset voltage of  $V_{DD}-V_{EE}$  is 4V. The default values of  $V_{CP}$  and  $V_{CN}$  are therefore 0.25V, (  $\frac{4}{16}~V$  ).

#### Second stage amplifier

Usually the second stage PIR amplifier is a simple capacitively coupled inverting amplifier with a low pass configuration. The noninverting input terminal is biased to the center point of the comparator window and the output of the second stage amplifier is directly coupled to the comparator center point.

In Fig.3 OP2P is directly connected to the comparator window center, and with the C3 filter it can act as the bias for OP2. For this configuration  $A_V = \frac{R1}{R2}$ , low cutoff

frequency

$$f_L = \frac{1}{2\pi R1C1}$$

, high cutoff frequency

$$f_H = \frac{1}{2\pi R2C2}$$

. By changing the value of R2 the sensitivity

can be varied. C1 and C3 should be of low leakage types to prevent the DC operating point from changing due to current leakage.

Each op-amp current consumption is approximately  $5\mu A$  with the op-amps and comparator's working voltage all provided by the regulator.

Consult the following diagrams for typical PIR front end circuit.

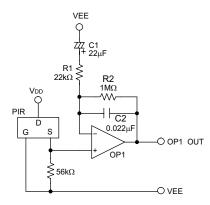

### First stage of PIR amplifier

Fig.4 shows a typical first stage amplifier. C2 and R2 form a simple low pass filter with cut off frequency at 7Hz. The low frequency response is governed by R1 and C1 with cut-off frequency at 0.33Hz.

$$A_V = \frac{(R1 + R2)}{R1}$$

Fig.3 Typical second stage amplifier

Rev. 1.10 6 September 18, 2002

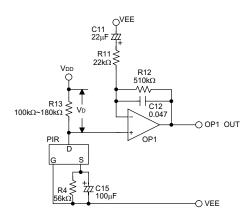

Fig.4 and Fig.5 are similar but in Fig.5 the input signal of amplifier is taken from the drain of the PIR. This has higher gain than that in Fig.4. Since OP1 is a PMOS input VD, it has to be greater than 1.2V for adequate operation.

Fig. 4 Typical first-stage PIR

Fig.5 High gain first stage

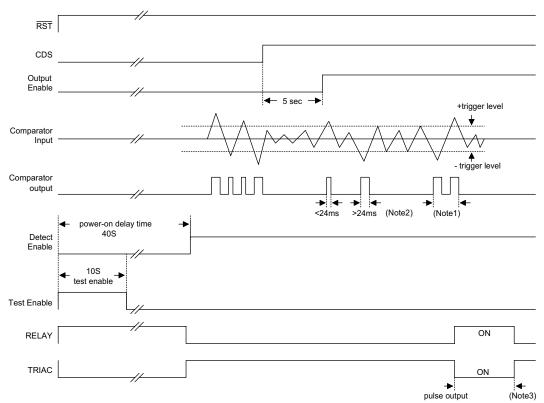

# **Timing Diagram**

Note: The output is activated if the trigger signal conforms to the following criteria:

- More than 3 triggers within 2 seconds

- $\bullet~$  A trigger signal sustain duration  $\geq 0.34~\text{secs}$

- 2 trigger signals within 2 secs with one of the trigger signal sustain ≥ 0.16 secs.

The effective comparator output width can be selected to be 24ms or 32ms or 48ms by mask option. The default is 24ms (system frequency=16kHz).

The output duration is set by an external RC that is connected to the OSCD pin.

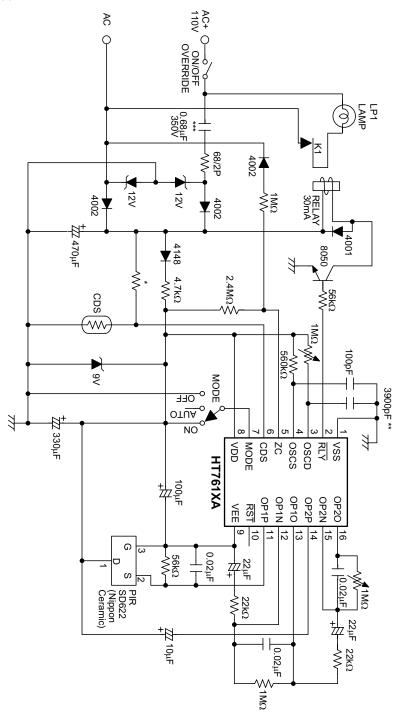

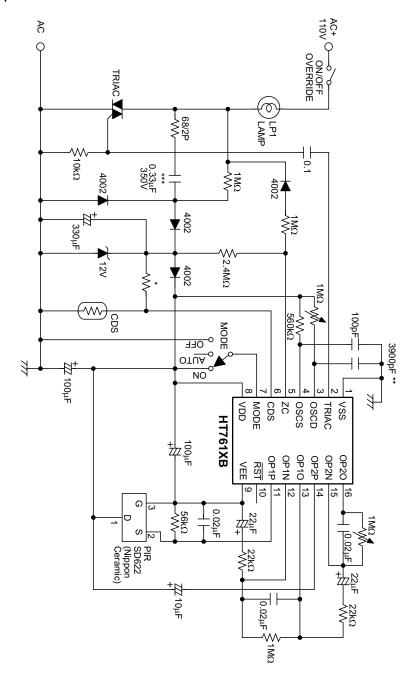

# **Application Circuit**

# HT761XA relay application

Note: Adjust "\*" to fit various CDS.

Change "\*\*" to obtain the desired adjusting range of output duration.

Change the value of "\*\*\*" to  $0.33 \mu \text{F}/600 \text{V}$  for AC 220V application.

# HT761XB triac application

Note: Adjust "\*" to fit various CDS.

Change  $^{\prime\prime\star\prime\prime\prime}$  to obtain the desired adjusting range of output duration.

Change the value of  $^{\prime\prime\star\star\star\prime\prime}$  to  $0.15\mu\text{F}/$  600V for AC 220V application.

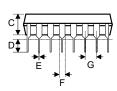

# **Package Information**

# 16-pin DIP (300mil) outline dimensions

| Symbol | Dimensions in mil |      |      |  |

|--------|-------------------|------|------|--|

|        | Min.              | Nom. | Max. |  |

| Α      | 745               | _    | 775  |  |

| В      | 240               | _    | 260  |  |

| С      | 125               | _    | 135  |  |

| D      | 125               | _    | 145  |  |

| Е      | 16                | _    | 20   |  |

| F      | 50                | _    | 70   |  |

| G      | _                 | 100  | _    |  |

| Н      | 295               | _    | 315  |  |

| I      | 335               | _    | 375  |  |

| α      | 0°                | _    | 15°  |  |

Holtek Semiconductor Inc. (Headquarters) No.3, Creation Rd. II, Science-based Industrial Park, Hsinchu, Taiwan

Tel: 886-3-563-1999 Fax: 886-3-563-1189 http://www.holtek.com.tw

#### Holtek Semiconductor Inc. (Sales Office)

11F, No.576, Sec.7 Chung Hsiao E. Rd., Taipei, Taiwan

Tel: 886-2-2782-9635 Fax: 886-2-2782-9636

Fax: 886-2-2782-7128 (International sales hotline)

# Holtek Semiconductor (Shanghai) Inc.

7th Floor, Building 2, No.889, Yi Shan Rd., Shanghai, China

Tel: 021-6485-5560 Fax: 021-6485-0313 http://www.holtek.com.cn

### Holtek Semiconductor (Hong Kong) Ltd.

RM.711, Tower 2, Cheung Sha Wan Plaza, 833 Cheung Sha Wan Rd., Kowloon, Hong Kong

Tel: 852-2-745-8288 Fax: 852-2-742-8657

#### Holmate Semiconductor, Inc.

48531 Warm Springs Boulevard, Suite 413, Fremont, CA 94539

Tel: 510-252-9880 Fax: 510-252-9885 http://www.holmate.com

#### Copyright © 2002 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com.tw.

Rev. 1.10 11 September 18, 2002