## **IA-D1 Series Area Image Sensor Arrays**

T.41.55

#### **FEATURES**

# DALZA INC

- Up to 10,000 frames / second

- 32x32, 64x64, 128x128, 256x256 Elements

- 16 MHz Output Data Rate

- TURBOSENSOR<sup>TM</sup> technology

- 16μm (H) x 16μm (V) Pixel Size

- 3,000:1 Dynamic Range

- 2 Phase BCCDs for Simple Operation

#### DESCRIPTION

The IA-D1 series of area array image sensors use DALSA's TURBOSENSOR<sup>TM</sup> technology to provide high output data rates of 16 MHz. The series is ideally suited for applications requiring maximum operating speed and medium resolution, and employs two phase buried channel CCD shift registers to maximize output speed and reduce noise. The IA-D1 sensors use square pixels and a square imaging area in sizes of 32x32, 64x64, 128x128, and 256x256. The dynamic range of the photoelements exceeds 3,000:1 and provides an output which is linear for all light levels.

All sensors in the IA-D1 series are functionally equivalent and can be easily interchanged in systems with only a few minor adjustments.

#### **APPLICATIONS**

The IA-D1 series sensors are ideally suited for applications requiring maximum operating speed, medium resolution and high sensitivity.

DALSA also offers the CA-D1 camera series which uses the IA-D1 series of image sensors for:

- image processing

- machine vision

- surveillance

For mechanical information regarding package size and tolerance, refer to package #50-01-24002 in **Optical and Mechanical Considerations of Sensors** on pp. 101-104 of this databook.

| PIN       | SYMBOL | NAME                            |      |     |          |     |

|-----------|--------|---------------------------------|------|-----|----------|-----|

| 1,4,7,8,9 | NC     | No Connection                   |      |     |          |     |

| 2         | VSET   | Output Node Set Voltage         |      |     |          |     |

| 3         | CR2    | Readout Clock, Phase 2          | NC   | 1   | <u> </u> | VSS |

| 5         | VBB    | Substrate Bias Voltage          | VSET | 2   | 23       | os  |

| 6         | CR1    | Readout Clock, Phase 1          | CR2  | 3   | 22       | VDD |

| 10        | CS2    | Storage Region Clock, Phase 2   | NC   | 4   | 21       | NC  |

| 11        | CS1    | Storage Region Clock, Phase 1   | VBB  | 5   | 20       | VOD |

| 12,16,21  | NC     | No connection                   | CR1  | 6   | 19       | RST |

| 13        | VSS    | Ground Reference                | NC   | 7   | 18       | TCK |

| 14        | CI1    | Image Region Clock, Phase 1     |      | 8   | 17       |     |

| 15        | Cl2    | Image Region Clock, Phase 2     | NC   | 1 - | ' '      | TOP |

| 17        | TOP    | Not Used; Do not connect        | NC   | 9   | 16       | NC  |

| 18        | TCK    | Storage to Readout Transfer Clk | CS2  | 10  | 15       | CI2 |

| 19        | RST    | Output Node Reset Clock         | CS1  | 11  | 14       | CI1 |

| 20        | VOD    | Output Node Drain Bias          | NC   | 12  | 13       | VSS |

| 22        | VDD    | Amplifier Supply Voltage        |      |     |          |     |

| 23        | os     | Output Signal                   |      |     |          |     |

| 24        | VSS    | Ground Reference                |      |     |          |     |

NOTE: Pinout shown here applies to Rev. C and Rev. D pinouts only.

DALSA TNO

#### FUNCTIONAL DESCRIPTION

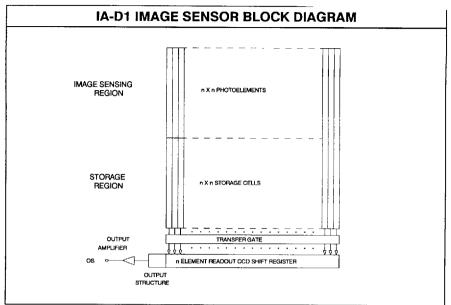

#### **ORGANIZATION**

This series of area array image sensors employ a frame transfer organization with photogate photoelements. During exposure, signal is collected under phase 1 of the imaging region CCD. At the end of the exposure time, the entire frame is transferred at high speed into the storage region CCD. During this time invalid data is transferred out of the readout CCD. Exposure then starts for the next frame; during this time the data from the storage region is transferred line by line to the readout shift register and then to the output.

#### **PHOTOELEMENTS**

The area array consists of a square matrix of 32. 64, 128 or 256 photoelements for imaging, plus an additional square matrix of the same size for frame storage. Each pixel has a photosensitive area of 256 square micrometers and center to center spacing of 16 micrometers in both directions.

The photoelements (in the imaging region) are controlled by the image region clocks Cl1 and Cl2 and are organized to allow parallel transfer into the storage region, which is controlled by CS1 and CS2. Specifically, Cl1 transfers into CS2.

The TURBOSENSOR<sup>TM</sup> photogate photoelement offers ultra high speed operation and responds linearly with respect to input light intensity.

#### TRANSFER GATE

This gate controls the flow of light generated signal charge from the storage region CCD (CS1 and CS2) into the readout CCD shift register (CR1 and CR2). Specifically, TCK interfaces between CS1 of the storage region and CR1 of the readout shift register.

Electrons from the storage region are transferred when a high potential (equal to the high clock voltage) is applied to the transfer gate.

#### **OUTPUT STRUCTURE**

The signal charge packets from the readout shift register are transferred serially, over the SET gate. to a floating sensing diffusion. As the signal charge is received, the corresponding potential on the diffusion is applied to the input of a two stage low noise amplifier structure, producing an output signal voltage (OS). The floating sensing diffusion is cleared of signal charge by the reset gate, driven by the reset clock (RST) in preparation for the subsequent signal charge packet.

The output data stream includes invalid data which is transferred out during the high speed transfer from imaging to storage region.

#### DALSA INC

#### RECOMMENDED DC OPERATION

#### SIGNAL NAMES

The signal names assigned to the package pins describe both the function of the pin as well as the sense of input signals. DC (unclocked) bias and supply voltages are designated with signal names beginning with "V". Clocked signals begin with any other letter and are representative of the function of the pin.

#### SUPPLY VOLTAGES

VDD provides operating current to the on chip output amplifier and hence should be well regulated. The substrate, or bulk bias voltage, VBB, is negative with respect to ground in some applications. This low current bias should be well requlated. Since protection diodes are provided between many clock lines and the substrate, no clocks can be permitted to go below VBB. In most cases, VBB can be maintained at 0 volts (equal to VSS), although a negative VBB can reduce charge injection.

#### **OUTPUT BIAS**

A very low current DC gate bias, VSET, controls transfer of signal charge onto the output sensing diffusion. This voltage should be adjusted with a resistive divider to optimize output structure operation. If VSET is not optimized, single bright pixels will appear to "bleed" into adjacent pixels and could be mistaken for very poor CTE or crosstalk.

The shift register output drain voltage, VOD, is a bias provided to the output structure to discharge signal electrons after sensing. It should be well filtered to reduce output noise.

#### GROUND REFERENCE

VSS is provided as the ground reference for the output amplifier. All other bias, supply and clock voltages are specified relative to VSS.

#### **OUTPUT SIGNAL**

The output signal is an AC waveform on a DC offset. It is recommended that the video signal be buffered for current gain. It is also recommended that the video signal be AC coupled.

#### IA-D1 DC OPERATING CONDITIONS

Recommended Operating Conditions at Tp = 25°C. (See notes)

| SYMBOL | DESCRIPTION                  | MIN  | TYP  | MAX  | UNIT |

|--------|------------------------------|------|------|------|------|

| VDD    | Amplifier supply voltage     | 12.0 | 15.0 | 16.0 | ٧    |

| VBB    | Substrate voltage            | -3.0 | 0.0  | 0.0  | ٧    |

| VOD    | Shift register drain voltage | 10.0 | 13.0 | 16.0 | ٧    |

| VSET   | Set Voltage                  | 3.0  | 5.0  | 8.0  | ٧    |

#### NOTES:

- Voltages with respect to ground (VSS).

- 2. Tp is defined as the package temperature.

## DALSA INC

## RECOMMENDED CLOCK **OPERATION**

#### PHOTOELEMENTS (IMAGE CLOCKS)

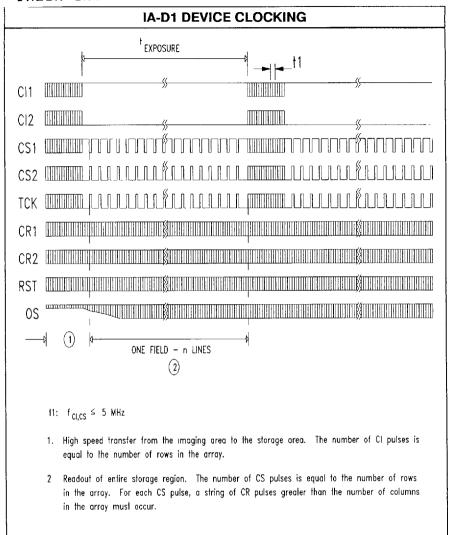

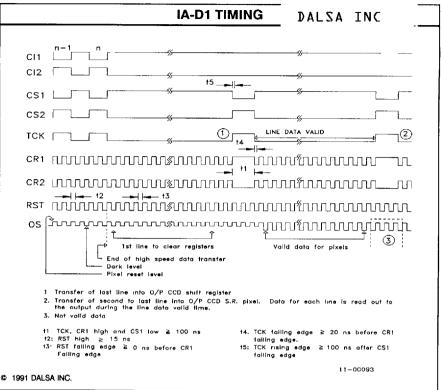

The two phase image clocks are the photosensitive elements in this device. These clocks, CI1 and CI2, control exposure and transfer signal charge from the image region to the storage region.

Signal charge electrons are photogenerated during the exposure period, which is set by the time CI1 is maintained high and CI2 is maintained low.

Following exposure, Cl1 and Cl2 are clocked at high speed (approximately 1/4 the readout frequency of CR1 and CR2) to move the signal charge in parallel into the storage region. Charge transfers from Cl1 into CS2. During this time Cl1 and Cl2 can be operated at 50% duty cycle and are complementary.

#### STORAGE CLOCKS

During integration or exposure, the storage clocks (CS1 and CS2) transfer signal data from the storage region, through the transfer gate (controlled by TCK), to the readout shift register. CS1 transfers over TCK into CR1. During this time CS2 is the same as TCK, and CS1 is the inverse of CS2.

High speed transfer follows integration. During this time CS1 is driven by the same signal as Cl1 and CS2 is driven by the same signal as Cl1. Invalid data is transferred from the storage region into the readout shift register and to the output at this time.

#### TRANSFER CLOCK

The transfer gate is controlled by the TCK signal. When TCK is pulsed high the pixel data is transferred into the first phase (CR1) of the CCD readout shift register.

During integration, TCK pulses occur once per line. and transfer each line of the previous frame into the readout shift register.

During high speed transfer, TCK and CS2 should be driven by the same signal in order to transfer invalid data out of the storage region.

#### READOUT CLOCKS

Two phase transport clocks (CR1, CR2) are used to transfer data to the output structure. The clocks can be operated at 50% duly cycle continuously and are complementary, non-overlapping.

#### **OUTPUT CONTROL CLOCKS**

One output structure clock (RST) is required to clear the output node after sensing. This clock should go to a high voltage equal to the transport clock (CR) high voltages, and to a low of VSS. During RST high, the output will go to a reset level as shown in the clock diagrams.

## **IA-D1 CLOCK CHARACTERISTICS**

Recommended Operating Conditions at Tp = 25°C.

| SYMBOL              | DESCRIPTION                      | MIN | TYP | MAX  | UNIT |

|---------------------|----------------------------------|-----|-----|------|------|

| VH(C)               | Transport clock 1 HIGH           | 4.0 | 7.0 | 16.0 | ٧    |

| V <sub>L(C)</sub>   | Transport clock 1 LOW            | 0.0 | 0.0 | 0.5  | V    |

| Vн(тск)             | Transfer clock HIGH              | 4.0 | 7.0 | 16.0 | ٧    |

| VL(TCK)             | Transfer clock LOW               | 0.0 | 0.0 | 0.5  | V    |

| VH(RST)             | Reset clock HIGH                 | 4.0 | 8.0 | 16.0 | V    |

| V <sub>L(RST)</sub> | Reset clock LOW                  | 0.0 | 0.0 | 0.5  | ٧    |

| f(RST)              | Reset frequency                  |     | 15  | 20   | MHz  |

| f(DATA)             | Data freq. (effective data rate) |     | 15  | 20   | MHz  |

|                     |                                  |     |     |      |      |

#### NOTE:

Transport clocks include Cl1, Cl2, CS1, CS2, CR1, and CR2.

### DALSA INC

© 1991 DALSA INC.

11-00092

| IA-D1 PERFORMANCE CHARACTERISTICS                                     |              |              |               |                      |  |  |

|-----------------------------------------------------------------------|--------------|--------------|---------------|----------------------|--|--|

| PARAMETER                                                             | MIN          | ТҮР          | MAX           | UNIT                 |  |  |

| Recommended Operating Conditions at Tp = $25^{\circ}$ C. (See notes). |              |              |               |                      |  |  |

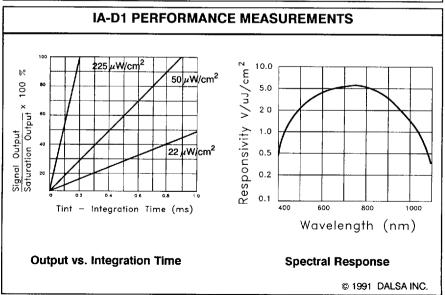

| Dynamic range <sup>1</sup>                                            |              | 3,000:1      |               | _                    |  |  |

| Noise Equivalent Exposure (NEE)                                       |              | 15           |               | pJ/cm <sup>2</sup>   |  |  |

| Saturation Equivalent Exposure (SEE) <sup>2</sup>                     |              | 45           |               | nJ/cm <sup>2</sup>   |  |  |

| Responsivity 2                                                        |              | 6.6          |               | V/μJ/cm <sup>2</sup> |  |  |

| Saturation Output Amplitude (VSAT)3                                   |              | 300          |               | mV                   |  |  |

| V <sub>NOISE</sub> <sup>4</sup> Peak-Peak RMS                         |              | 0.50<br>0.10 |               | mV<br>mV             |  |  |

| FPN                                                                   |              | 10.0         |               | mV                   |  |  |

| PRNU <sup>5</sup>                                                     |              | 10           |               | % VSAT               |  |  |

| CTE 6                                                                 | 0.9999       | 0.99999      | 0.999999      |                      |  |  |

| DC Output Offset                                                      |              | 8            |               | ٧                    |  |  |

| Storage Temperature (Tp) 7<br>Operating Temperature (Tp) 7            | - 70<br>- 60 |              | + 125<br>+ 90 | °C                   |  |  |

#### Notes:

- Ratio of VSAT to RMS Noise with reset noise eliminated through correlated double sampling (CDS)

- 2. Responsivity at peak Quantum Efficiency (near 700 nm).

- 3. Output amplitude with respect to dark reference level.

- 4. Amplifier noise measured with reset noise eliminated through correlated double sampling (CDS).

- PRNU is measured at approximately 50% VSAT and is the difference between the pixels with the lowest and highest outputs, expressed as a percentage of VSAT.

- 6. CTE is the measurement for a one stage transfer, measured at fRST = 3.75 MHz

- 7. Tp is package temperature

- 8. See cosmetic specifications for this device.

#### **Test Conditions:**

- 1. All tests are done at fRST = 3.75 MHz

- 2. Light Source QTH lamp with WBHM, unless otherwise noted

- VDD, VOD = 15 V, VBB = 0 V; Clock high voltage 12 V, tow voltage 0 V, (includes CRx, Clx, CSx, TCK, RST as applicable); VSET as required for maximum VSAT and CTE

- 4. All measurements exclude first and last 2 rows and columns of frame

| IA-D1 ELECTRICAL CHARACTERISTICS                                                               |                  |                |     |                |  |

|------------------------------------------------------------------------------------------------|------------------|----------------|-----|----------------|--|

| PARAMETER                                                                                      | MIN              | TYP            | MAX | UNIT           |  |

| Recommended Operating Cond                                                                     | itions at Tp = 2 | :5°C.          |     |                |  |

| Output impedance                                                                               |                  | 200            |     | Ω              |  |

| Amplifier supply current                                                                       |                  | 15             |     | mA             |  |

| DC Bias Currents (VOD, VSET, VE                                                                | 3B)              |                | 1   | mA             |  |

| Amplifier power dissipation                                                                    | 150              | 225            | 300 | mW             |  |

| Resistance to VBB<br>Transport gate (CRx)<br>Transfer gate<br>Reset, Set gate                  |                  | 5<br>5<br>5    |     | MΩ<br>MΩ<br>MΩ |  |

| Capacitance to VBB Transport clocks (CRx) Transfer clocks (TCK) Imaging and Storage clocks (CS | Sx, Clx)         | 75<br>8<br>500 |     | pF<br>pF<br>pF |  |

| Reset (RST), Set (VSET) gate                                                                   |                  | 12             |     | pF             |  |

#### Notes:

Capacitance given for 128x128 element array For other sensors in this series, apply the following factors: 32 element (0.3), 64 element (0.6), 256 element (1.8).

# **Optical and Mechanical Considerations of Sensors**

## Optical and Mechanical Considerations of DALSA CCD Image Sensors

DALSA INC

7-90-70

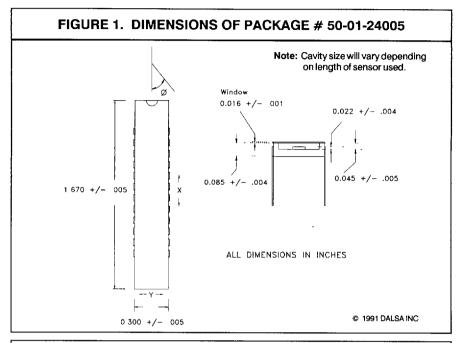

This applications note provides packaging information for the sensors listed in this databook. Please refer to the tables on the following pages for the critical dimensions of each image sensor series. For more information on a particular image sensor, please refer to the specific datasheet.

| Package #   | Part       | X              | Y              | Ø                           |

|-------------|------------|----------------|----------------|-----------------------------|

| 50-01-24005 | IL-C3-0128 | $0.55 \pm .09$ | $0.15 \pm .02$ | $0^{\circ} \pm 3.0^{\circ}$ |

| 50-01-24005 | IL-C3-0256 | $0.55 \pm .08$ | $0.15 \pm .02$ | $0^{\circ} \pm 2.5^{\circ}$ |

| 50-01-24005 | IL-C3-0512 | $0.55 \pm .07$ | $0.15 \pm .02$ | $0^{\circ} \pm 2.0^{\circ}$ |

| 50-01-24005 | IL-C2-0512 | $0.55 \pm .07$ | $0.15 \pm .02$ | $0^{\circ} \pm 2.0^{\circ}$ |

| 50-01-24005 | IL-C9-0512 | $0.55 \pm .07$ | $0.15 \pm .02$ | $0^{\circ} \pm 2.0^{\circ}$ |

| 50-01-24005 | IL-C4-1024 | $0.55 \pm .05$ | $0.15 \pm .02$ | 0° ± 1.5°                   |

| 50-01-24005 | IL-C4-2048 | $0.55 \pm .04$ | $0.15 \pm .02$ | 0° ± 1.0°                   |

| 50-01-24005 | IL-C5-2048 | $0.55 \pm .05$ | $0.15 \pm .02$ | 0° ± 1.5°                   |

| 50-01-24005 | IL-C5-4096 | $0.55 \pm .04$ | $0.15 \pm .02$ | 0° ± 1.0°                   |

| 50-01-24005 | IL-C6-2048 | $0.55 \pm .04$ | $0.15 \pm .02$ | 0° ± 1.0°                   |

| 50-01-24005 | IL-E1-0512 | $0.55 \pm .07$ | $0.15 \pm .02$ | $0^{\circ} \pm 2.0^{\circ}$ |

| 50-01-24005 | IL-E1-1024 | $0.55 \pm .05$ | $0.15 \pm .02$ | 0° ± 1.5°                   |

| 50-01-24005 | IL-E1-2048 | 0.55 ± .04     | $0.15 \pm .02$ | 0° ± 1.0°                   |

| 50-01-24005 | IL-F2-0512 | $0.55 \pm .07$ | $0.15 \pm .02$ | $0^{\circ} \pm 2.0^{\circ}$ |

| 50-01-24005 | IL-F2-1024 | $0.55 \pm .05$ | $0.15 \pm .02$ | 0° ± 1.5°                   |

| 50-01-24005 | IL-F2-2048 | $0.55 \pm .04$ | $0.15 \pm .02$ | $0^{\circ} \pm 1.0^{\circ}$ |

# Optical and Mechanical Considerations of Sensors

## DALSA INC

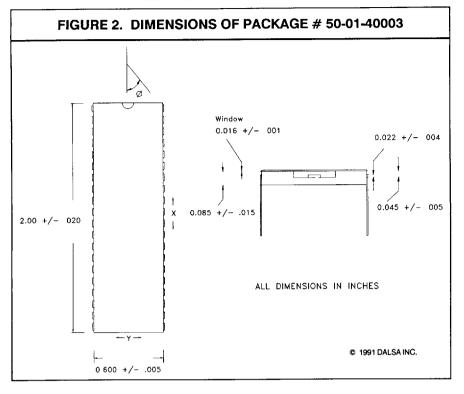

| Package #   | Part       | X               | Y              | Ø                           |

|-------------|------------|-----------------|----------------|-----------------------------|

| 50-01-40003 | IT-C5-2048 | $0.95 \pm 0.1$  | $0.3 \pm 0.05$ | 0° ± 2.5°                   |

| 50-01-40003 | IT-C5-4096 | $0.95 \pm 0.08$ | $0.3 \pm 0.03$ | $0^{\circ} \pm 1.5^{\circ}$ |

| 50-01-40003 | IT-E1-1536 | $0.95 \pm 0.08$ | $0.3 \pm 0.05$ | 0° ± 2.0°                   |

| 50-01-40003 | IT-E1-2048 | $0.95 \pm 0.06$ | $0.3 \pm 0.05$ | 0° ± 1.5°                   |

| 50-01-40003 | IT-F2-2048 | $0.95 \pm 0.06$ | $0.3 \pm 0.03$ | $0^{\circ} \pm 1.5^{\circ}$ |

# **Optical and Mechanical Considerations of Sensors**

# DALSA INC

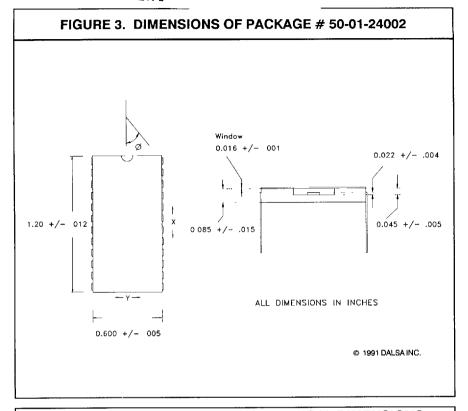

## TABLE 3. PACKAGE # 50-01-40002 TYPICAL DIMENSIONS

| Package #   | Part       | х               | Υ              | Ø                           |

|-------------|------------|-----------------|----------------|-----------------------------|

| 50-01-40002 | IA-D1-0032 | $0.56 \pm 0.12$ | $0.3 \pm 0.05$ | $0^{\circ} \pm 5.0^{\circ}$ |

| 50-01-40002 | IA-D1-0064 | $0.57 \pm 0.09$ | $0.3 \pm 0.04$ | $0^{\circ} \pm 4.0^{\circ}$ |

| 50-01-40002 | IA-D1-0128 | $0.59 \pm 0.12$ | $0.3 \pm 0.03$ | 0° ± 2.5°                   |

| 50-01-40002 | IA-D1-0256 | $0.71 \pm 0.10$ | $0.3 \pm 0.03$ | $0^{\circ} \pm 1.5^{\circ}$ |

Note: X = center imaging area to center pin 1 along package. Y = center imaging area to center pin 1 across package. Ø = off-axis rotation

### DALSA INC

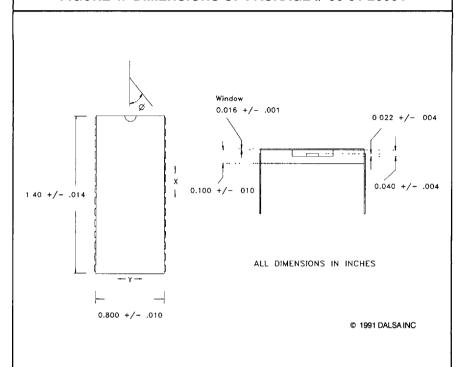

#### FIGURE 4. DIMENSIONS OF PACKAGE # 50-01-28004

### TABLE 4. PACKAGE # 50-01-28004 TYPICAL DIMENSIONS

| Package #   | Part       | X               | Υ              | Ø                           |

|-------------|------------|-----------------|----------------|-----------------------------|

| 50-01-28004 | IA-D2-0512 | $0.65 \pm 0.08$ | $0.4 \pm 0.04$ | $0^{\circ} \pm 3.0^{\circ}$ |

Note: X = center imaging area to center pin 1 along package. Y = center imaging area to center pin 1 across package. Ø = off-axis rotation