#### **Features**

- 256K x 16 DRAM

- · Performance:

|                  | Parameter                       | -40  | -50  | -60   |

|------------------|---------------------------------|------|------|-------|

| t <sub>RP</sub>  | RE Precharge                    | 20ns | 25ns | 30ns  |

| t <sub>CAC</sub> | Access Time from CE             | 12ns | 14ns | 15ns  |

| t <sub>AA</sub>  | Column Address Access<br>Time   | 20ns | 25ns | 30ns  |

| t <sub>RC</sub>  | Read or Write Cycle Time        | 75ns | 90ns | 110ns |

| t <sub>PC</sub>  | Fast Page Mode Cycle Time       | 20ns | 25ns | 30ns  |

| tHPC             | Extended Data Out Cycle<br>Time | 15ns | 20ns | 25ns  |

- 66MHz EDO performance

- Non-Persistent WPBM mode

- Power Supply:  $5.0V \pm 0.5V$  and  $3.3V \pm 0.3V$

- High Performance, CMOS 0.45μm process

- SOJ-40 JEDEC Standard

- TTL compatible

### **Description**

This 4Mb DRAM is organized as 256K x 16. The parts are available in three speed sorts:40, 50and 60ns. Fast page (FP) as well as Extended Data Out (EDO) devices are available in 5V and 3.3V. The 40ns parts have an EDO performance of 66MHz which can improve performance of graphics applications. Refresh may be accomplished by a  $\overline{\text{CE}}$  before  $\overline{\text{RE}}$  refresh cycle (CBR) that internally generates the

refresh address.  $\overline{RE}$  - only refresh cycles will also refresh all memory locations. However,  $\overline{RE}$  - only refresh requires row address to be provided externally. CBR cycles are required to clear any modes that might be inadvertently set during power up.

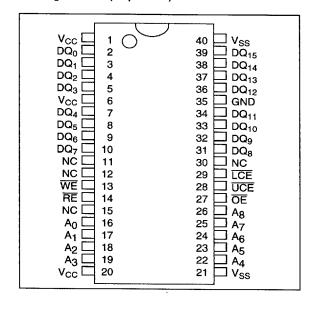

#### Pin Assignments (Top View)

### **Pin Description**

| RE                                 | Row Enable                                                                                                    |

|------------------------------------|---------------------------------------------------------------------------------------------------------------|

| LCE, UCE                           | Lower & Upper Column Enable                                                                                   |

| ₩                                  | Write                                                                                                         |

| ŌĒ                                 | Output Enable                                                                                                 |

| A <sub>8</sub> -A <sub>0</sub>     | Address Inputs                                                                                                |

| DQ <sub>15</sub> - DQ <sub>0</sub> | Random Port Data Input/Output                                                                                 |

| V <sub>CC</sub>                    | Voltage (5.0V $\pm$ 0.5V or 3.3V $\pm$ 0.3V). All voltages are referenced to the nearest V <sub>SS</sub> pin. |

| V <sub>SS</sub>                    | Ground. V <sub>SS</sub> =0V                                                                                   |

| NC                                 | No Connect                                                                                                    |

27H6280 SA14-4243-01 Revised 04/96

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 1 of 27

## **Detailed Pin Description**

#### RE - Row Enable; also known as RAS

This pin is functionally equivalent to a chip enable signal in that whenever it is activated, 8192 storage cells of the selected row are sensed simultaneously and the sense amplifiers restore all data. The falling edge of  $\overline{RE}$  latches data on address pins  $A_0$  - $A_8$ .  $\overline{CE}$ ,  $\overline{OE}$ , and  $\overline{W}$  are simultaneously latched to invoke the DRAM port operations.

### LCE, UCE - Lower and Upper Column Enable (Dual CE parts only).

These pins enable lower and upper byte respectively of the selected column for Read/Write. The falling edge of either LCE or UCE latches the column address.

#### W - Write

This pin enables the DRAM port write circuitry.

### OE - Output Enable

This pin enables the DRAM data outputs.

#### A<sub>0</sub> - A<sub>8</sub> - Address Inputs

These pins are multiplexed as row and column address inputs. Row addresses are first used to select one of the possible 512 rows for a Read, Write, or Refresh cycles. Column addresses are then supplied to select one of the possible 512 columns for a Read or a Write cycle.

### DQ<sub>0</sub> - DQ<sub>15</sub> - Random Port Data Input/Output

In a Read cycle, these pins serve as outputs for the selected storage cells. In a Write cycle, data input on these pins is latched by the falling edge of  $\overline{CE}$  or  $\overline{W}$  whichever occurs later. Data will not appear at the outputs until after both  $\overline{CE}$  and  $\overline{OE}$  have been brought low. At  $\overline{RE}$  falling edge, the data input at these pins can be used for loading the Write-per-Bit Mask (WPBM).

### $\mbox{V}_{\mbox{\scriptsize cc}}$ - (5.0V $\pm$ 0.5V) or (3.3V $\pm$ 0.3V) voltage.

All voltages are referenced to the nearest V<sub>ss</sub> pin.

$V_{ss}$  - Circuit ground.  $V_{ss} = 0V$ .

#### NC - No Connect.

NC implies that the pin(s) should not be grounded or connected to any other signal. These pins might be used for testing some modes at factory. Consult factory before using any one of NC pins.

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

27H6280 SA14-4243-01 Revised 04/96

Page 2 of 27

**-** 9006146 0001779 593 **-**

# **Ordering Information**

| Part Number       | Features           | Voltage                 | Speed | Package           | Notes |

|-------------------|--------------------|-------------------------|-------|-------------------|-------|

| IBM 015160LJ3A-40 | Dual CE, Fast Page | 5.0V                    | 40ns  |                   | 1     |

| IBM 015160NJ3A-40 | Dual CE, Fast Page | 3.0V                    | 40ns  |                   | 1     |

| IBM 015161LJ3A-40 | Dual CE, EDO Page  | 5.0V                    | 40ns  | 1                 | 1     |

| IBM 015161NJ3A-40 | Dual CE, EDO Page  | 3.0V                    | 40ns  | 1                 | 1     |

| IBM 015160LJ3A-50 | Dual CE, Fast Page | 5.0V                    | 50ns  | 1                 |       |

| IBM 015160NJ3A-50 | Dual CE, Fast Page | 3.0V                    | 50ns  |                   |       |

| IBM 015161LJ3A-50 | Dual CE, EDO Page  | 5.0V                    | 50ns  | SOJ-40<br>400 mil |       |

| IBM 015161NJ3A-50 | Dual CE, EDO Page  | 3.0V                    | 50ns  | 1                 |       |

| IBM 015160LJ3A-60 | Dual CE, Fast Page | 5.0V                    | 60ns  | 1                 |       |

| IBM 015160NJ3A-60 | Dual CE, Fast Page | 3.0V                    | 60ns  |                   |       |

| IBM 015161LJ3A-60 | Dual CE, EDO Page  | ual CE, EDO Page 5.0V € | 60ns  |                   |       |

| IBM 015161NJ3A-60 | Dual CE, EDO Page  | 3.0V                    | 60ns  |                   |       |

<sup>40</sup>parts are high performance parts with an EDO performance of 66MHz.

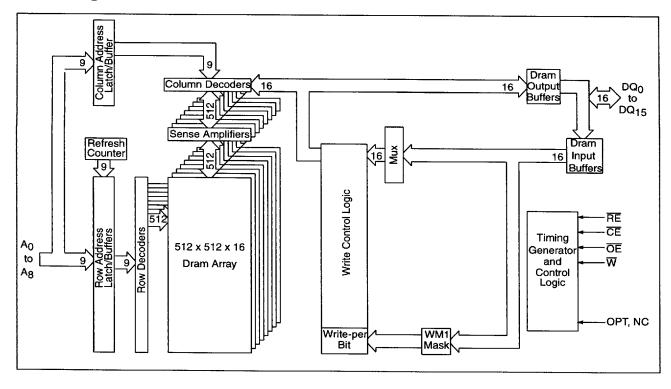

### **Block Diagram**

27H6280 SA14-4243-01 Revised 04/96

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 3 of 27

#### **Truth Table**

| Function         |    |     |     |    |    | Add            | ress | DO                |                    |             |

|------------------|----|-----|-----|----|----|----------------|------|-------------------|--------------------|-------------|

| Function         | RE | LCE | ÜCE | WE | ŌĒ | t <sub>R</sub> | tc   | DQ <sub>0-7</sub> | DQ <sub>8-15</sub> | Notes       |

| Standby          | Н  | Х   | Х   | Х  | Х  | х              | Х    | High-Z            | High-Z             | <del></del> |

| Row Refresh Only | L  | н   | н   | Х  | Х  | Row            | -    | High-Z            | High-Z             |             |

| CE-before-RE     | L  | L.  | L   | Н  | Х  | х              | х    | High-Z            | High-Z             | 2           |

| Lower Byte Read  | L  | L   | Н   | Н  | L  | Row            | Col. | Output            | High-Z             |             |

| Upper Byte Read  | L  | н   | L   | Н  | L  | Row            | Col. | High-Z            | Output             |             |

| Word Read Cycle  | L  | L   | L   | н  | L  | Row            | Col. | Output            | Output             |             |

| Lower Byte Write | L  | L   | Н   | L  | Н  | Row            | Col. | Input             | High-Z             | 1           |

| Upper Byte Write | L  | Н   | L   | L  | Н  | Row            | Col. | High-Z            | Input              | 1           |

| Word Write Cycle | L  | L   | L   | L  | Н  | Row            | Col. | Input             | Input              | 1 1         |

<sup>1.</sup> Write of the input data will be dependent on the mask provided at  $\overline{RE}$  fall time. If  $\overline{WE}$  is high at  $\overline{RE}$  fall time, no mask will be applied to the data input. However, if  $\overline{WE}$  is low at  $\overline{RE}$  fall time, DQs latched at  $\overline{RE}$  fall time acts as Write-per-Bit (WPB)mask for the input data provided at  $\overline{CE}$  fall time for page cycles for the whole  $\overline{RAS}$  cycle.

## **Absolute Maximum Ratings**

| Symbol           | Item                         | Ra           |              |       |       |

|------------------|------------------------------|--------------|--------------|-------|-------|

| - Symbol         |                              | 5.0 Volt     | 3.3 Volt     | Units | Notes |

| Vcc              | Power Supply Voltage         | -1.0 to +6.0 | -0.5 to +4.6 | V     | 1     |

| TA               | Operating Temperature        | 0 to +70     | 0 to +70     | °C    | 1     |

| T <sub>STG</sub> | Storage Temperature          | -55 to +150  | -55 to +150  | °C    | 1     |

| P <sub>D</sub>   | Power Dissipation            | 1.0          | 1.0          | w     | 1     |

| lout             | Short Circuit Output Current | 50           | 50           | mA    | 1     |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# Recommended DC Operating Conditions ( $T_A=0$ to +70°C)

| Symbol Parame   | Paramotor          | 5.0 Volt |      |                      |      | 3.3 Volt | Linito               | Notes |       |

|-----------------|--------------------|----------|------|----------------------|------|----------|----------------------|-------|-------|

|                 | 1 diameter         | Min.     | Тур. | Max.                 | Min. | Тур.     | Max.                 | Units | Notes |

| V <sub>CC</sub> | Supply Voltage     | 4.5      | 5.0  | 5.5                  | 3.0  | 3.3      | 3.6                  | V     | 1     |

| $V_{IH}$        | Input High Voltage | 2.4      |      | V <sub>cc</sub> +0.5 | 2.0  |          | V <sub>cc</sub> +0.3 | ٧     | 1     |

| V <sub>IL</sub> | Input Low Voltage  | -0.5     |      | 0.8                  | -0.3 |          | 0.8                  | V     | 1     |

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

27H6280 SA14-4243-01 Revised 04/96

Page 4 of 27

**-** 9006146 0001781 141 **-**

<sup>2.</sup> Truth table for  $\overline{\text{CE}}$  before  $\overline{\text{RE}}$  (CBR) is slightly different than Micron, NEC etc.

### Capacitance (T<sub>A</sub>= 25°C, f= 1.0 MHz)

| Symbol          | Parameter                     | Min. | Max. | Units | Notes |

|-----------------|-------------------------------|------|------|-------|-------|

| C <sub>I1</sub> | Input Capacitance (Addresses) |      | 5    | pF    |       |

| C <sub>I2</sub> | RE, CE, W, OE                 | _    | 7    | pF    |       |

| Co              | Output Capacitance (DQi)      |      | 7    | pF    |       |

## **Output Drivers**

| Driver        | Impedance | Output Voltage, Low (Max)       | Output Voltage, High (Min)     |

|---------------|-----------|---------------------------------|--------------------------------|

| Parallel Port | 45±15 Ω   | I <sub>OUT</sub> =2.0 mA, V=0.4 | I <sub>OUT</sub> =-1 mA, V=2.4 |

### **AC Measurement Conditions**

| Port                              | Detect      | Load         |

|-----------------------------------|-------------|--------------|

| Parallel Port Output Detect Level | 2.0V / 0.8V | _            |

| Parallel Port Output Load         |             | 1 TTL + 50pF |

# DC Electrical Characteristics (TA= 0 to +70°C, $V_{cc}$ = 3.3V $\pm$ 0.3V or $V_{cc}$ = 5.0V $\pm$ 0.5V)

| Symbol            | ymbol Parameter                                                                                                         |     | 5.0  | Volt | 3.3 Volt |      | Units  | Notes   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------|-----|------|------|----------|------|--------|---------|

|                   | Talameter                                                                                                               |     | Min. | Max. | Min.     | Max. | Office | Notes   |

|                   | Operating Current (Random)                                                                                              | -40 | _    | 135  | _        | 135  |        |         |

| I <sub>CC1</sub>  | Average Power Supply Operating Current (RE and CE Cycling, t <sub>RC</sub> =90ns for -40and -50, t <sub>RC</sub> =110ns | -50 |      | 135  |          | 135  | mA     | 1,2,3,5 |

|                   | for -60ns)                                                                                                              | -60 |      | 130  | _        | 130  |        |         |

|                   | Fast Page Mode Current<br>Average Power Supply Current, Fast Page Mode                                                  | -40 | _    | 80   | _        | 80   |        |         |

| I <sub>CC2</sub>  | (RE = V <sub>IL</sub> Min., CE Cycling, tpC = 20ns for -40and -50,                                                      | -50 |      | 80   | _        | 80   | mA     | 1,2,4,5 |

|                   | t <sub>PC</sub> =25ns for -60)                                                                                          | -60 | _    | 70   | _        | 70   | 70     |         |

| lcc3              | Standby Supply Current Power Supply Standby Current (RE = CE = V <sub>CC</sub> )                                        |     |      | 1    | _        | 1    | mA     |         |

| 1 <sub>I(L)</sub> | Input Leakage Current, any input $(0.0 \le V_{IN} \le (V_{CC} + 1.0V))$ , All Other Pins Not Under Test = 0V            | ,   | -10  | +10  | -10      | 10   | μА     | ****    |

| I <sub>O(L)</sub> | Output Leakage Current (DOUT is disabled, $0.0 \le V_{OUT} \le V_{CC}(max)$ )                                           |     | -10  | +10  | -10      | 10   | μА     |         |

| V <sub>OH</sub>   | Output Level (TTL) Output "H" Level Voltage (I <sub>OUT</sub> = -1mA, Random)                                           |     | 2.4  | _    | 2.4      | _    | ٧      | 4       |

| V <sub>OL</sub>   | Output Level (TTL)<br>Output "L" Level Voltage (I <sub>OUT</sub> = +2.0mA, Random)                                      |     |      | 0.4  | _        | 0.4  | ٧      | 4       |

- 1.  $I_{CC1}$ ,  $I_{CC2}$ , and  $I_{CC3}$  depend on cycle rate.

- 2. I<sub>CC1</sub>, I<sub>CC2</sub>, and I<sub>CC3</sub> depend on output loading. Specified values are obtained with the output open.

- 3. Measured with one address change per RE cycle.

- 4. Measured with one column address change per page cycle.

- 5. Measured with  $\overline{OE} = V_{IH}$  when  $\overline{CE} = V_{IL}$ .

27H6280 SA14-4243-01 Revised 04/96

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 5 of 27

**-** 9006146 0001782 088 **-**

## AC Characteristics (T<sub>A</sub>= 0 to +70°C)

# Read, Write, Read-Modify-Write and Refresh. Cycles (Common Parameters)

| Symbol               | Parameter                                    | -40  |      | -50  |      | -60  |             | l lada | Notes |

|----------------------|----------------------------------------------|------|------|------|------|------|-------------|--------|-------|

|                      | Faranteter                                   | Min. | Max. | Min. | Max. | Min. | Max.        | Units  | Notes |

| t <sub>ASC</sub>     | Column address setup time                    | 0    |      | 0    | _    | 0    | _           | ns     |       |

| t <sub>ASR</sub>     | Row address setup time                       | 0    |      | 0    |      | 0    | _           | ns     |       |

| t <sub>AR</sub>      | Column address hold time after RE low        | 20   | _    | 20   |      | 20   |             | ns     |       |

| t <sub>CAH</sub>     | Column address hold time after CE low        | 5    |      | 7    | _    | 10   | _           | ns     | 5     |

| t <sub>CAS</sub>     | CE pulse width                               | 8    | 16K  | 10   | 16K  | 15   | 16K         | ns     |       |

| t <sub>CHCL</sub>    | First CE to return high to last CE going low | 6    | _    | 6    | _    | 6    | _           | ns     | -     |

| t <sub>CLCH</sub>    | Last CE going low to first CE to return high | 6    |      | 6    | _    | 6    | _           | ns     |       |

| t <sub>CP</sub>      | CE precharge time                            | 5    | _    | 7    | _    | 10   | _           | ns     |       |

| t <sub>CRP</sub>     | CE high before RE low precharge              | 10   | _    | 12   |      | 15   | _           | ns     | 8     |

| t <sub>СSH</sub>     | CE hold time                                 | 40   | _    | 50   |      | 60   | _           | ns     |       |

| t <sub>MH</sub>      | Write mask hold time after RE low            | 5    | _    | 7    | _    | 10   | _           | ns     |       |

| t <sub>MS</sub>      | Data-in setup before RE low                  | 0    | _    | 0    | _    | 0    | _           | ns     |       |

| t <sub>RAD</sub>     | RE to column address delay time              | 12   | 20   | 14   | 25   | 15   | 30          | ns     | 4     |

| t <sub>RAH</sub>     | Row address hold time after RE low           | 5    | _    | 7    |      | 10   | _           | ns     |       |

| t <sub>RAS</sub>     | RE pulse width                               | 40   | 100K | 50   | 100K | 60   | 100K        | ns     |       |

| t <sub>RC</sub> ,twc | Random read or write cycle time              | 75   | _    | 90   | _    | 110  | _           | ns     | 1,2   |

| t <sub>RCD</sub>     | Delay from RE low to CE low                  | 17   | 28   | 19   | 35   | 20   | 40          | ns     | 3,5   |

| t <sub>RP</sub>      | RE precharge time                            | 20   | _    | 25   | _    | 30   | <del></del> | ns     | 1,6,  |

| t <sub>RSH</sub>     | RE hold time                                 | 12   | _    | 14   | _    | 15   | _           | ns     |       |

| t <sub>T</sub>       | Transition time (rise and fall)              | 3    | 50   | 3    | 50   | 3    | 50          | ns     |       |

| twsR                 | Write setup time before RE low               | 0    |      | 0    | _    | 0    |             | ns     |       |

| twcn                 | Write hold time after RE low                 | 25   | _    | 30   |      | 35   | _           | ns     |       |

- 1. An initial pause of 100μs is required after power-up followed by 8  $\overline{\text{CE}}$  before  $\overline{\text{RE}}$  refresh cycles for proper device operation

- 2. AC measurements assume  $t_T = 5$ ns.

- 3. Operation within the t<sub>RCD</sub>(max) limit ensures that t<sub>RAC</sub>(max.) can be met. t<sub>RCD</sub>(max.) is specified as a reference point only: If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max) limit, then access time is controlled by t<sub>CAC</sub>.

- Operation within the t<sub>RAD</sub>(max) limit ensures that t<sub>RAC</sub>(max.) can be met. t<sub>RAD</sub>(max.) is specified as a reference point only: If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub>(max) limit, then access time is controlled by t<sub>AA</sub>.

- 5.  $t_{RCD}$  and  $t_{CAH}$  cannot be at minimum values simultaneously.  $t_{RCD} + t_{CAH} \ge 40$ ns (40ns  $t_{RAC}$  product),  $t_{RCD} + t_{CAH} \ge 45$ ns (50ns  $t_{RAC}$  product),  $t_{RCD} + t_{CAH} \ge 50$ ns (60ns  $t_{RAC}$  product)

- 6.  $t_{RWL}$  and  $t_{RP}$  cannot be at minimum values simultaneously.  $t_{RWL} + t_{RP} \ge 40$ ns (40ns  $t_{RAC}$  product),  $t_{RWL} + t_{RP} \ge 50$ ns (50ns  $t_{RAC}$  product),  $t_{RWL} + t_{RP} \ge 60$ ns (60ns  $t_{RAC}$  product)

- 7.  $t_{CWL}$  and  $t_{RP}$  cannot be at minimum values simultaneously.  $t_{CWL} + t_{RP} \ge 40$ ns (40ns  $t_{RAC}$  product),  $t_{CWL} + t_{RP} \ge 50$ ns (50ns  $t_{RAC}$  product),  $t_{CWL} + t_{RP} \ge 60$ ns (60ns  $t_{RAC}$  product)

- 8. t<sub>CRP</sub> must be 10ns (40ns t<sub>RAC</sub>) or 12ns (50ns t<sub>RAC</sub>) or 15ns (60ns t<sub>RAC</sub>) if a write-per-bit mask is used on the following RE cycle due to the fact that t<sub>OFF</sub> must be met.

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

27H6280 SA14-4243-01 Revised 04/96

Page 6 of 27

■ 9006146 0001783 T14 **■**

## **Write Cycle**

| Symbol           | Parameter                                                                                       |      | 40   | -50  |      | -60  |          |       | Notes |

|------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|------|----------|-------|-------|

| Cyrribor         | Falalletel                                                                                      | Min. | Мах. | Min. | Max. | Min. | Max.     | Units | Notes |

| t <sub>CWL</sub> | Write Command setup before CE high                                                              | 12   |      | 14   |      | 15   | _        | ns    | 4     |

| t <sub>DH</sub>  | Data-in hold time after $\overline{\text{CE}}$ or $\overline{\text{W}}$ low, whichever is later | 5    |      | 8    |      | 10   | _        | ns    | 1     |

| t <sub>DHR</sub> | Data-in hold time after RE low                                                                  | 20   |      | 25   |      | 30   | _        | ns    |       |

| tosc             | Data-in setup before CE low                                                                     | 0    |      | 0    |      | 0    |          | ns    |       |

| t <sub>DSW</sub> | Data-in setup before $\overline{\mathbf{W}}$ low                                                | 0    |      | 0    |      | 0    | _        | ns    |       |

| t <sub>GHD</sub> | OE high before data-in applied on primary port data pins                                        | 10   |      | 12   |      | 15   | <b>—</b> | ns    |       |

| t <sub>RWL</sub> | Write setup time before RE high                                                                 | 12   |      | 14   |      | 15   | _        | ns    | 3     |

| twch             | Write hold time after CE low                                                                    | 5    |      | 7    |      | 10   | 1 –      | ns    |       |

| twcs             | Early write command setup before $\overline{\text{CE}}$ Low                                     | 0    |      | 0    | 1    | 0    | _        | ns    | 1,2   |

| t <sub>WP</sub>  | Write command pulse width                                                                       | 5    |      | 7    |      | 10   | l —      | ns    |       |

- 1. Data-in setup and hold is measured from the later of the two timings CE / UCE / LCE

- 2. t<sub>RWD</sub>, t<sub>CWD</sub>, t<sub>AWD</sub> and t<sub>CPW</sub> are not restrictive parameters. They are included as electrical characteristics only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub>(min) the cycle is an early write cycle and the data pin will remain open circuit (high impedance) through the entire cycle; if t<sub>RWD</sub> ≥ t<sub>RWD</sub>(min), t<sub>CWD</sub> ≥ t<sub>CWD</sub>(min), and t<sub>CPW</sub> ≥ t<sub>CPW</sub> (min) (Fast Page) mode, the cycle is a Read-Modify-Write cycle and the data out will contain data read from the selected cell; if neither of the above sets of conditions are satisfied, the condition of the data out (at access time) is indeterminate.

- 3. t<sub>RWL</sub> and t<sub>RP</sub> cannot be at minimum values simultaneously. t<sub>RWL</sub> + t<sub>RP</sub> ≥ 40ns (40ns t<sub>RAC</sub> product), t<sub>RWL</sub> + t<sub>RP</sub> ≥ 50ns (50ns t<sub>RAC</sub> product), t<sub>RWL</sub> + t<sub>RP</sub> ≥ 60ns (60ns t<sub>RAC</sub> product

- 4.  $t_{CWL}$  and  $t_{RP}$  cannot be at minimum values simultaneously.  $t_{CWL} + t_{RP} \ge 40$ ns (40ns  $t_{RAC}$  product),  $t_{CWL} + t_{RP} \ge 50$ ns (50ns  $t_{RAC}$  product),  $t_{CWL} + t_{RP} \ge 60$ ns (60ns  $t_{RAC}$  product),

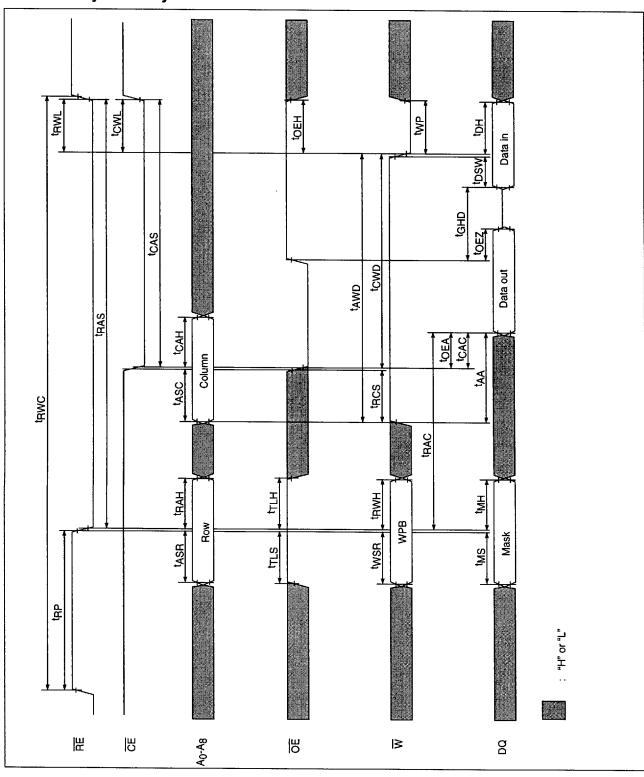

# **Read-Modify-Write Cycle**

| Symbol           | Parameter                                     | -40  |      | -50  |                                       | -60  |      |       |       |

|------------------|-----------------------------------------------|------|------|------|---------------------------------------|------|------|-------|-------|

|                  |                                               | Min. | Max. | Min. | Max.                                  | Min. | Max. | Units | Notes |

| t <sub>AWD</sub> | Column address to W low                       | 38   |      | 45   | · · · · · · · · · · · · · · · · · · · | 50   |      | ns    | 1     |

| tcwp             | CE low before W low                           | 30   |      | 35   |                                       | 40   | _    | ns    | 1     |

| t <sub>OEH</sub> | Output disable (OE high) hold time from W low | 0    |      | 0    |                                       | 0    | _    | ns    |       |

| t <sub>RWC</sub> | Read-modify-write cycle time                  | 110  |      | 130  |                                       | 165  |      | ns    |       |

1. t<sub>RWD</sub>, t<sub>CWD</sub>, t<sub>AWD</sub> and t<sub>CPW</sub> are not restrictive parameters. They are included as electrical characteristics only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub>(min) the cycle is an early write cycle and the data pin will remain open circuit (high impedance) through the entire cycle; if t<sub>RWD</sub> ≥ t<sub>RWD</sub>(min), t<sub>CWD</sub> ≥ t<sub>CWD</sub>(min), and t<sub>CPW</sub> ≥ t<sub>CPW</sub> (min) (Fast Page) mode, the cycle is a Read-Modify-Write cycle and the data out will contain data read from the selected cell; if neither of the above sets of conditions are satisfied, the condition of the data out (at access time) is indeterminate.

27H6280 SA14-4243-01 Revised 04/96

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 7 of 27

**9006146 0001784 950**

### **Read Cycle**

| Symbol           | Parameter                                   | -40 |      | -50  |      | -60       |    |       |       |

|------------------|---------------------------------------------|-----|------|------|------|-----------|----|-------|-------|

|                  | raiametei                                   |     | Max. | Min. | Max. | Min. Max. |    | Units | Notes |

| t <sub>AA</sub>  | Access time from column address             |     | 20   |      | 25   |           | 30 | ns    | 2,3   |

| tCAC             | Access time from CE                         |     | 12   |      | 14   |           | 15 | ns    | 1,2,3 |

| t <sub>OEA</sub> | Access time from OE                         |     | 12   |      | 14   | _         | 15 | ns    |       |

| toes             | Output enable setup (OE low) before RE high | 1   |      | 1    |      | 1         | _  | ns    |       |

| t <sub>OEZ</sub> | Primary output disable from OE high         |     | 10   |      | 12   |           | 15 | ns    |       |

| toff             | Primary output disable from CE              |     | 10   |      | 12   | 0         | 15 | ns    | 5     |

| t <sub>RAC</sub> | Access time from RE                         |     | 40   |      | 50   | _         | 60 | ns    | 1,2,3 |

| t <sub>RAL</sub> | Column address to RE high                   | 22  |      | 25   |      | 30        | _  | ns    |       |

| t <sub>RCH</sub> | Read hold time after CE goes high           | 0   |      | 0    |      | 0         | _  | ns    | 4     |

| t <sub>RCS</sub> | Read command setup time                     | 0   |      | 0    |      | 0         | _  | ns    |       |

| t <sub>RRH</sub> | Read command hold time to RE high           | 0   |      | 0    |      | 0         | _  | ns    | 4     |

- Operation within the t<sub>RCD</sub>(max.) limit ensures that t<sub>RAC</sub>(max.) can be met. t<sub>RCD</sub>(max.) is specified as a reference point only: If t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub>(max.) limit, then access time is controlled by t<sub>CAC</sub>.

- Operation within the t<sub>RAD</sub>(max.) limit ensures that t<sub>RAC</sub>(max.) can be met t<sub>RAD</sub>(max.) is specified as a reference point only: If t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub>(max.) limit, then access time is controlled by t<sub>AA</sub>.

- 3. Measured with the specified current and 50 pF load for the primary port. Output referenced levels:  $V_{OH} = 2.0V$  and  $V_{OL} = 0.8V$ .

- 4. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a read cycle.

- 5. t<sub>OFF</sub>(max.) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

## Page Mode Cycle

| Symbol           | Parameter                     |      | -40  |      | -50  |      | -60      |       |       |

|------------------|-------------------------------|------|------|------|------|------|----------|-------|-------|

|                  |                               | Min. | Max. | Min. | Max. | Min. | Max.     | Units | Notes |

| t <sub>ACP</sub> | Access time from CE precharge |      | 20   |      | 25   | _    | 30       | ns    |       |

| t <sub>HPC</sub> | Extended data out cycle time  | 15   |      | 20   |      | 25   | _        | ns    |       |

| t <sub>PC</sub>  | Fast page mode cycle time     | 20   |      | 25   |      | 30   | <u> </u> | ns    |       |

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

27H6280 SA14-4243-01 Revised 04/96

Page 8 of 27

**--** 9006146 0001785 897 **--**

# **Refresh Cycle**

| Symbol           | Parameter                                         |      | -40  |      | -50  |      | -60  |       |                                         |

|------------------|---------------------------------------------------|------|------|------|------|------|------|-------|-----------------------------------------|

|                  |                                                   | Min. | Max. | Min. | Мах. | Min. | Max. | Units | Notes                                   |

| t <sub>CHR</sub> | CE held low after RE low (CE before RE refresh)   | 12   |      | 14   |      | 15   | _    | ns    |                                         |

| tcsR             | CE low setup before RE low (CE before RE refresh) | 5    |      | 5    |      | 7    | _    | ns    | , , , , , , , , , , , , , , , , , , , , |

| t <sub>REF</sub> | Refresh period                                    |      | 32   |      | 32   | _    | 32   | ms    |                                         |

| t <sub>RPC</sub> | RE high to CE low precharge                       | 0    |      | 0    |      | 0    | _    | ns    |                                         |

27H6280 SA14-4243-01 Revised 04/96 ©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 9 of 27

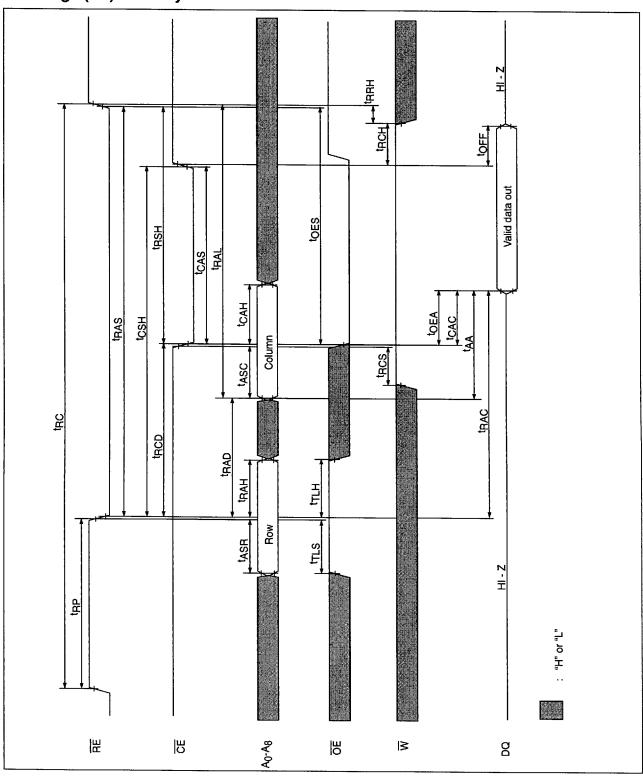

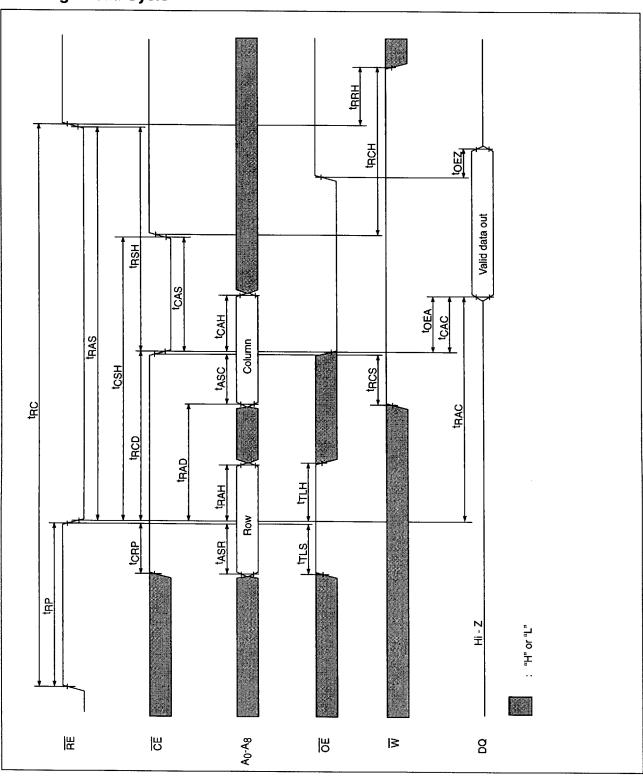

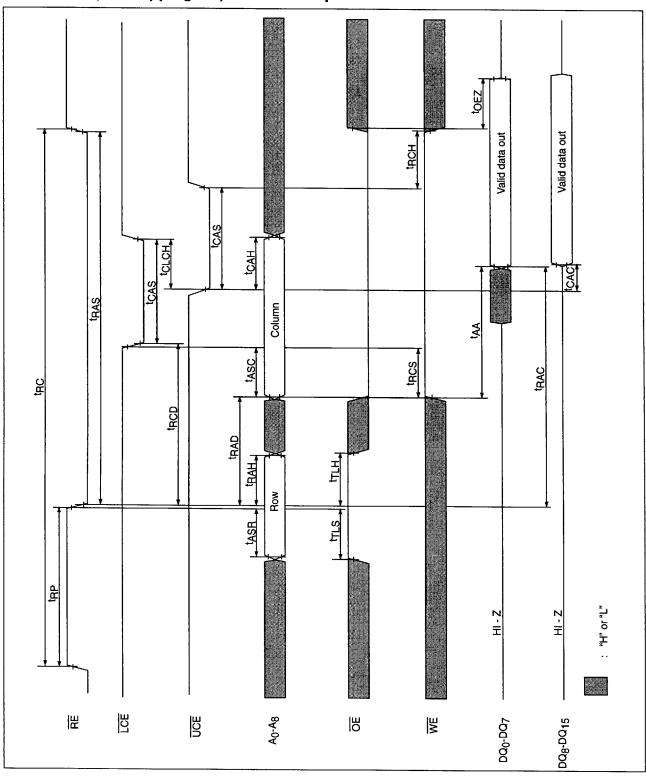

# Fast Page (FP) Read Cycle

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 10 of 27

9006146 0001787 66T **=**

# **Fast Page Read Operation**

27H6280 SA14-4243-00 Revised 11/95 ©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 11 of 27

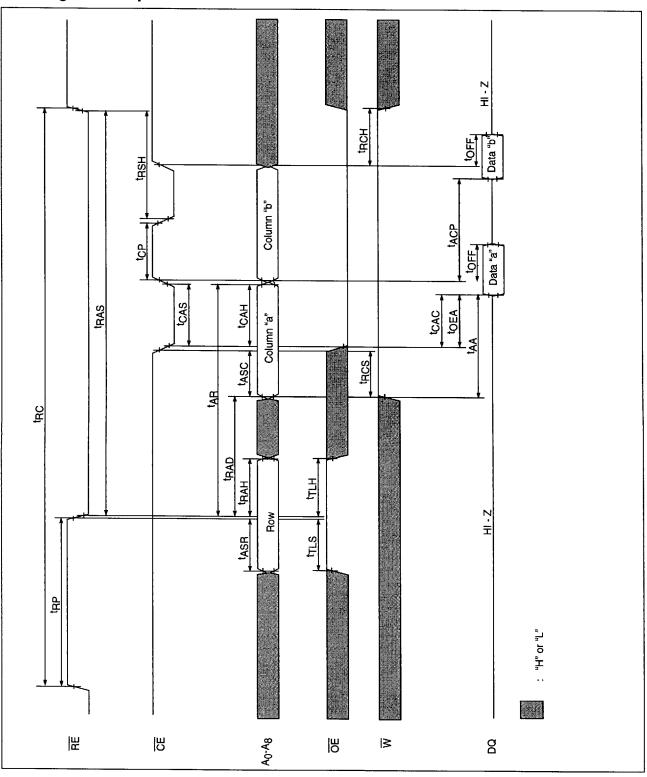

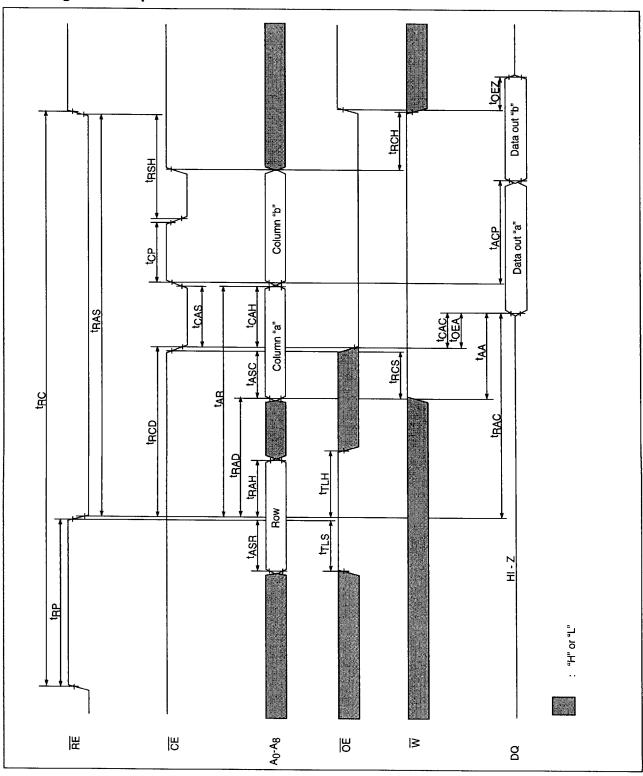

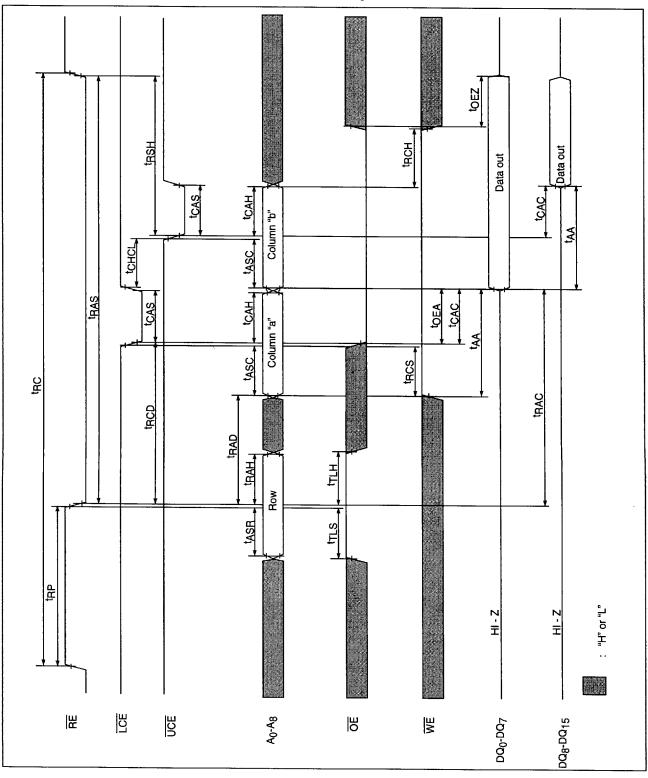

# **EDO Page Read Cycle**

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 12 of 27

9006146 0001789 432

# **EDO Page Read Operation**

27H6280 SA14-4243-00 Revised 11/95

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 13 of 27

**-** 9006146 0001790 154 **-**

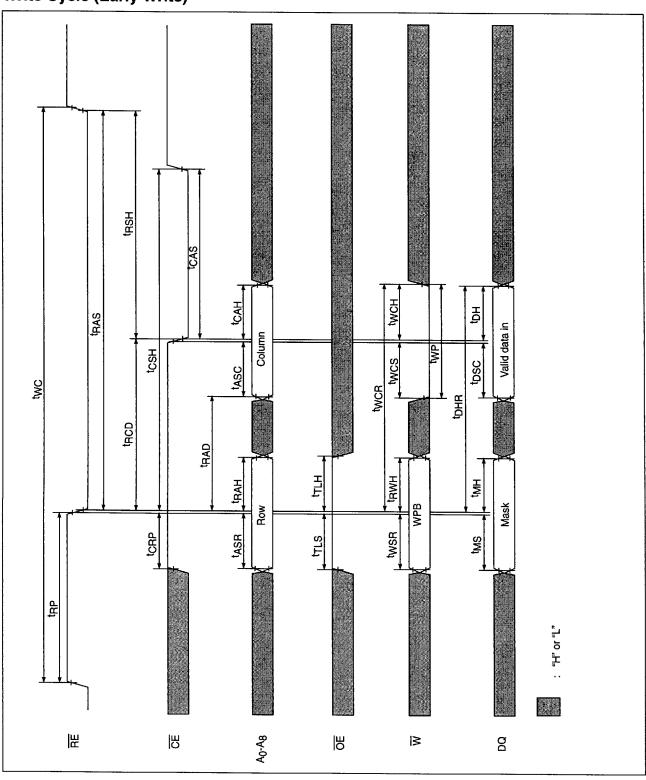

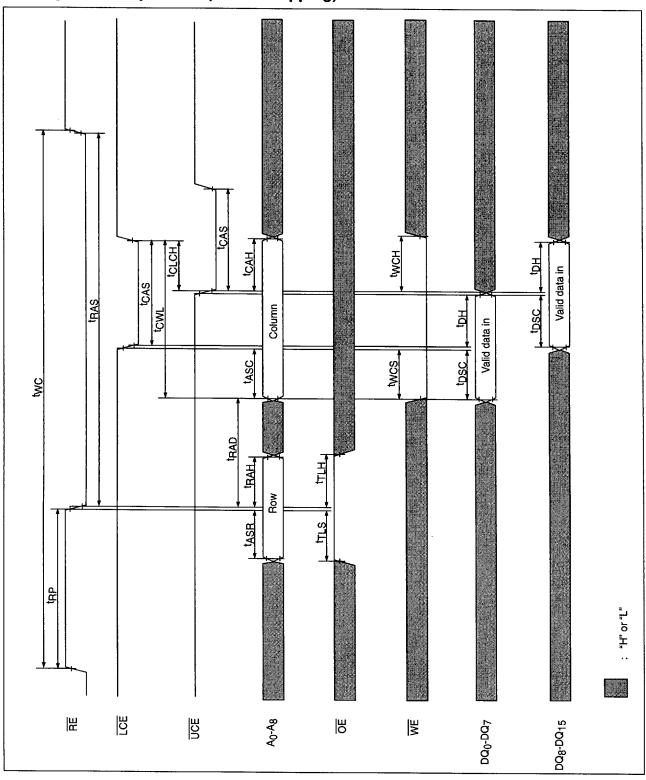

# Write Cycle (Early Write)

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 14 of 27

9006146 0001791 090

# Fast Page Mode (Early Write)

27H6280 SA14-4243-00 Revised 11/95

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 15 of 27

■ 9006146 0001792 T27 🖿

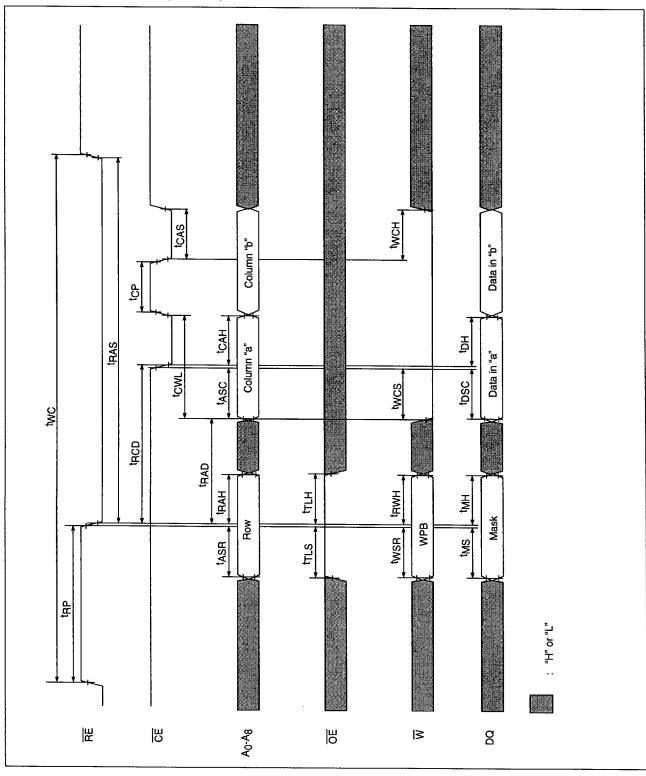

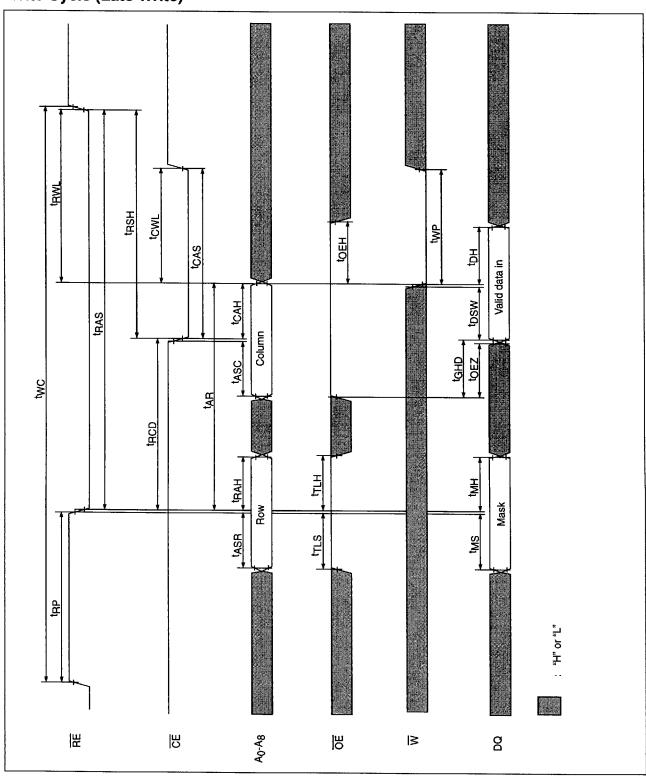

# Write Cycle (Late Write)

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 16 of 27

**--** 9006146 0001793 963 **--**

# **Read-Modify-Write Cycle**

27H6280 SA14-4243-00 Revised 11/95

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 17 of 27

🖿 9006146 0001794 8TT 🖿

# Skewed CE (Overlapping CE) EDO Read Operation

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 18 of 27

**9**006146 0001795 736 **=**

# Skewed CE (Non-Overlapping CE) EDO Read Operation

27H6280 SA14-4243-00 Revised 11/95

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 19 of 27

**9006146 0001796 672**

# 2 CE Byte Write Operation (CE Overlapping)

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 20 of 27

9006146 0001797 509

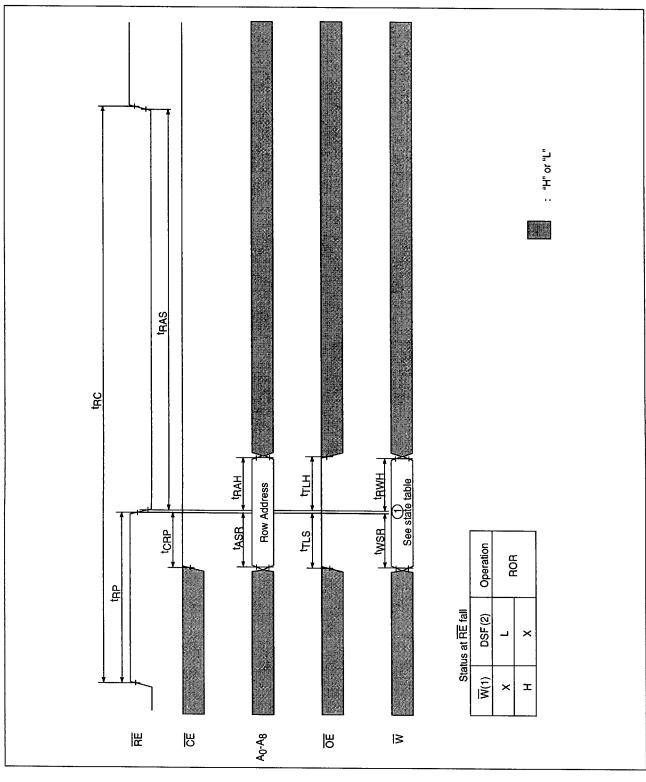

# RE Only Refresh (ROR)

27H6280 SA14-4243-00 Revised 11/95

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 21 of 27

**=** 9006146 0001798 445 **==**

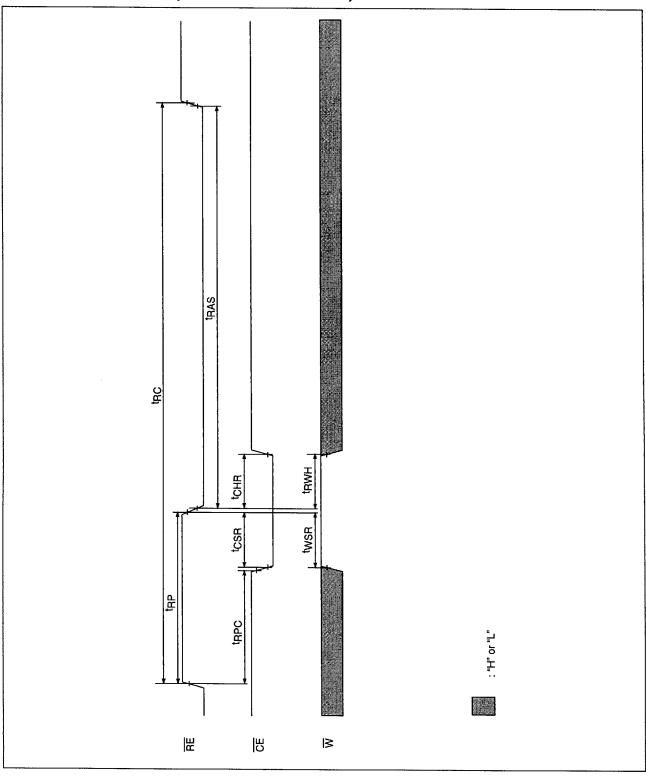

# CE Before RE Refresh (CBR-With Mode Reset)

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 22 of 27

**--** 9006146 0001799 381 **--**

### **Functional Description**

The DRAM array is organized as 512 rows x 512 columns x 16 bit wide. The device is capable of performing normal Read/Write operations.

### **Power Up or DRAM Initialize Process**

After  $V_{cc}$  has reached its regulated value, allow at least 100 $\mu$ s for build up of N-well voltage inside the chip. Perform at least 8  $\overline{\text{CAS}}$ -Before- $\overline{\text{RAS}}$  (CBR) refresh cycles to reset unwanted mode(s) which may be set during power up.

### **DRAM Refresh Operation**

DRAM array consists of volatile cells, therefore, these cells need to be refreshed periodically. The minimum rate for DRAM is 512 refresh cycles every 8ms. Every cell therefore gets a chance to be refreshed every 8ms.

### The following refresh modes are available in IBM's 4-Mb DRAM:

### RE Only Refresh (ROR)

A cycle having only  $\overline{\text{RE}}$  active refreshes all cells in one row of the storage array. A high  $\overline{\text{CE}}$  is maintained while  $\overline{\text{RE}}$  is active to keep DQs in high impedance. This method is preferred for refreshing, especially when the host system consists of multiple rows of random access devices. The data outputs may be OR-tied with no bus contention when  $\overline{\text{RE}}$  only refresh cycles are executed.

Note that the row address for refresh is supplied by the user. RE only Refresh mode will not clear any unknown modes at powerup. Therefore, CBR cycles at powerup must be performed to clear any unknown modes. The timing diagram on page 21 shows a RE only Refresh mode.

### CE before RE Refresh (CBR)

The CBR Refresh mode is selected by bringing the  $\overline{CE}$  low before  $\overline{RE}$  is brought low as shown in the timing diagram on page 22. An internal address counter selects the row to be refreshed. Note that DQs are in high-Z state during CBR cycle.

#### **Recommended CBR Cycle**

To ensure that the device has not entered unwanted register modes at power up, at least *eight CBR cycles must be executed before normal operation of the device is resumed*. A CBR after each vertical retrace is recommended. This fail-safe routine is for cases where a system misoperation causes entry into an unwanted mode.

#### **Byte Control**

The 4-Mb DRAM is available with Dual  $\overline{\text{CE}}$ . A dual  $\overline{\text{CE}}$  part has lower and upper byte control. The  $\overline{\text{LCE}}$  controls the DQ<sub>0</sub> -DQ<sub>7</sub> while  $\overline{\text{UCE}}$  controls DQ<sub>8</sub> - DQ<sub>15</sub>. Individual byte control can be applied during read and write operations on the primary port.

27H6280 SA14-4243-00 Revised 11/95

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 23 of 27

#### **Read Cycle**

A Read cycle is executed by activating  $\overline{RE}$ ,  $\overline{CE}$ , and  $\overline{OE}$  and by maintaining  $\overline{W}$  high while  $\overline{CE}$  is active. The DQs remain in high-Z until valid data appears at the output at access time. Device access time,  $t_{ACC}$ , will be the longest of the four calculated intervals:

- t<sub>RAC</sub>- Access time from RE falling edge

- t<sub>RCD</sub> (RE to CE delay) + t<sub>CAC</sub> (Access time from CE falling edge)

- t<sub>RAD</sub> (RE to Column Address delay) + t<sub>AA</sub> (Access time from column Address)

- RE to OE delay + t<sub>OEA</sub> (Access time from OE)

Device dependent parameters are:  $t_{RAC}$ ,  $t_{CAC}$ ,  $t_{AA}$  and  $t_{OEA}$ . System dependent parameters are:  $t_{RCD}$ ,  $t_{RAD}$  and  $\overline{RE}$  to  $\overline{OE}$  delay. Output becomes valid after the access time has elapsed. It remains valid while  $\overline{CE}$  and  $\overline{OE}$  are low (Fast Page parts only). It remains valid while  $\overline{OE}$  is low (EDO parts only). Either  $\overline{CE}$  or  $\overline{OE}$  high returns the output pins to high-Z (EDO parts).

#### **Write Cycle**

A Write cycle is executed by bringing  $\overline{W}$  low during  $\overline{RE}/\overline{CE}$  cycle. The falling edge of  $\overline{CE}$  or  $\overline{W}$  whichever occurs later strobes the data on DQ pins into the on-chip data latch.

#### **Early Write Cycle**

An early Write cycle is executed by bringing  $\overline{W}$  low before  $\overline{CE}$  falls. Data is strobed by  $\overline{CE}$  with setup and hold times referenced to this signal. This is the mode that is generally used for graphics applications.  $\overline{OE}$  can be in any state while  $\overline{W}$  is active.

#### **Late Write Cycle**

A late Write is executed by bringing  $\overline{W}$  low after  $\overline{CE}$  goes low. The input data is strobed by  $\overline{W}$  with setup and hold times referenced to  $\overline{W}$  signal. The late Write cycle is used for Read-Modify-Write operations.

### Write-Per-Bit Mask (WPBM) Cycle

A Write-Per-Bit cycle uses an I/O mask function to allow the system designer the flexibility of writing or not writing any combinations of  $DQ_0$  through  $DQ_{15}$ .

#### · Non-persistent Mask or New mask

**Note:** This mask has to be loaded at each  $\overline{RE}$  fall time as shown in the timing diagram on page 14.  $\overline{W}$  must be low as  $\overline{RE}$  falls. The DQs latched at  $\overline{RE}$  fall time are used as mask bits for Write cycle(s) for the particular  $\overline{RE}$  cycle. If mask bit is "1", the corresponding DQ input bit is written. If mask bit is "0", the corresponding DQ input is not written.

#### Read-Write/Read-Modify-Write Cycle

A Read-Modify-Write is performed by first performing a normal Read, then tri-stating the DQ pins with  $\overline{OE}$ , placing data to be written on the DQ pins, and then executing a Write operation. A WPBM can be loaded at the falling edge of  $\overline{RE}$ . The input data is strobed in reference to  $\overline{W}$ . This operation is illustrated in the timing diagram on page 17.

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

27H6280 SA14-4243-00 Revised 11/95

Page 24 of 27

🖿 9006146 0001801 86T 🖼

#### **Fast Page Cycle Operation**

Fast page mode cycles allow faster memory access by using the same row address while successive column addresses are strobed onto the chip. The RE signal is kept low while successive CE cycles are executed. The data rate is faster because row addresses are maintained internally and do not have to be reapplied. In fast page mode operation, Read, Write, Read - modify - Write cycles may be executed. During a fast-page read cycle, the DQ pins stay in high-Z until valid data appears at the output pins at access time. The access time in this cycle will be the longest of the following intervals.

$t_{ACP}$  = Access time from start of column precharge  $t_{CP}$  +  $t_T$  +  $t_{CAC}$ = Column precharge time + transition time + Access time from  $\overline{CE}$  fall time =  $\overline{CE}$  high to column address delay +  $t_{AA}$

#### Extended Data Out (EDO)

In extended data out mode, the primary port output drivers are not turned off by the rising edge of  $\overline{CE}$ . As rising edge of  $\overline{CE}$  does not turn off the data, the resulting longer data valid time allows speed up of the fast page cycle time. Fast page mode applications that try to run at minimum cycle times find that timing skews and propagation delays make the data valid time so narrow that reliable sampling is impossible. EDO solves this problem by providing longer data valid time. The device access time is the longest of the following intervals:

- tACP

- t<sub>AA</sub>

- tcac

27H6280 SA14-4243-00 Revised 11/95

©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 25 of 27

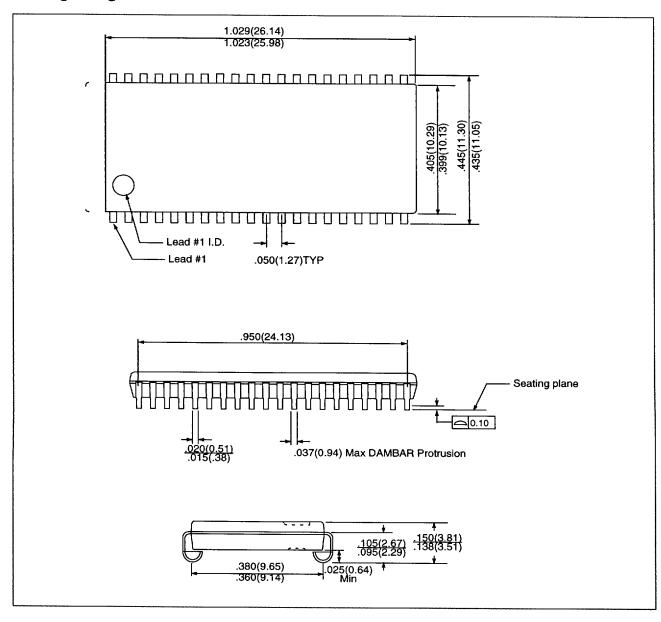

### **Package Diagram**

©IBM Corporation, 1995. All rights reserved.

Use is further subject to the provisions at the end of this document.

Page 26 of 27

■ 9006146 0001803 632 **■**

# **Revision Log**

| Rev   | Contents of Modification                                                |

|-------|-------------------------------------------------------------------------|

| 11/95 | Initial Release                                                         |

| 04/96 | Major revision. Added -40 and -50 options. Removed -6H and -70 options. |

27H6280 SA14-4243-01 Revised 04/96 ©IBM Corporation, 1995. All rights reserved. Use is further subject to the provisions at the end of this document.

Page 27 of 27