### **Features**

- 256K, 512K, and 1MB secondary cache module family using Synchronous and Asynchronous SRAMs.

- Organized as a 32K, 64K, or 128K x 72 package on a 4.3" x 1.1", 160-lead, Dual Read-out DIMM for SSRAM and 64K x 72 package for ASRAM

- Available in both interleaved (i486/Pentium<sup>TM</sup>) and linear (PowerPC<sup>TM</sup>) burst modes

- Operation for 50MHz to 66MHz supported

- Fast access times: 9 and 11ns using SSRAM; 12ns using ASRAM

- Byte Parity

- Individual Byte Write control

- Low capacitive address, control, clock, and data bus loading

- Single +3.3V or 5V, +/- 5% power supply

- 5V-tolerant common data I/O

### Description

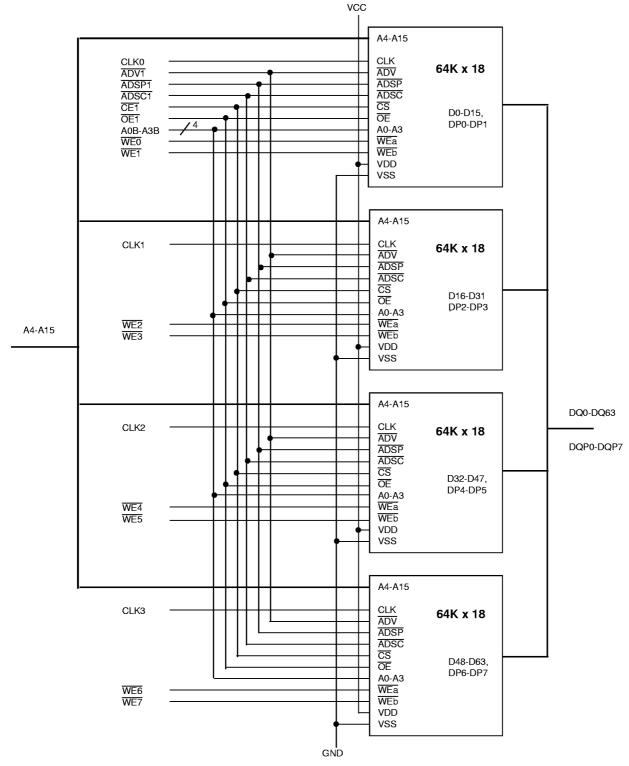

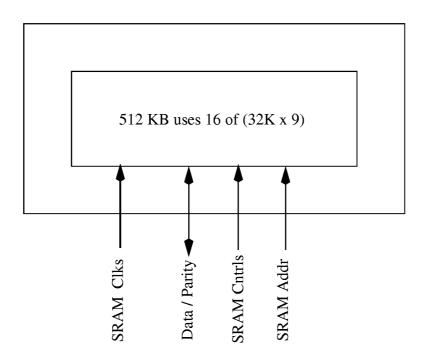

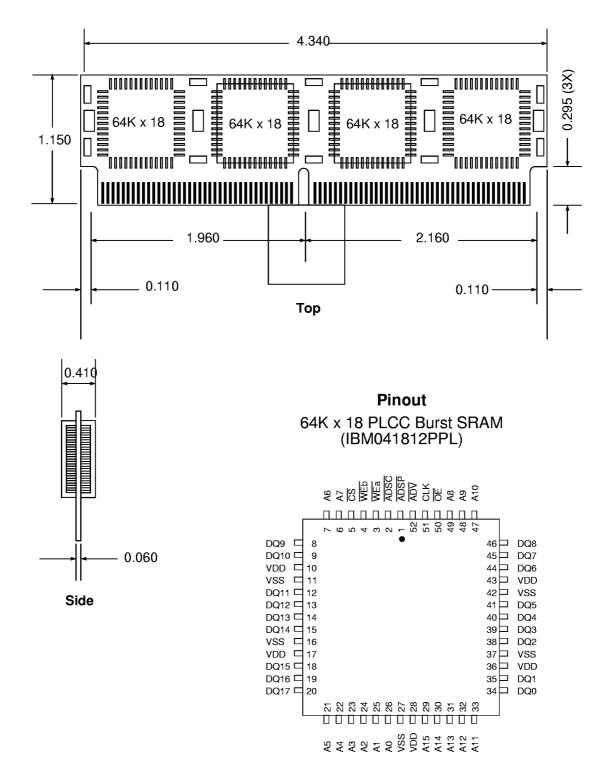

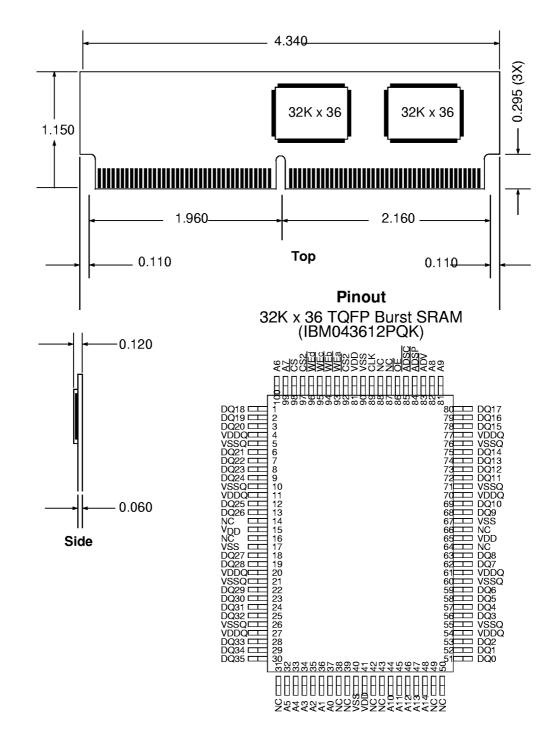

The IBM family of 256KB, 512KB, and 1MB synchronous SRAM modules uses IBM's burstable, highperformance 0.5-micron CMOS Static RAMs that are versatile and can achieve up to 9ns access. The 512KB modules integrate four 64K x 18 burst SRAMs. The burst-mode operation of these modules supports PowerPC-based systems and is available for either +3.3V or +5V applications. The 512KB ASRAM module offers a cost/performance optimization for +5V applications.

This IBM family of Cache modules supports operation up to 66MHZ. Outputs are 5V tolerant and LVTTL compatible. The Cache family is presently designed to support either Pentium or PowerPCbased controllers.

#### **Connector Pin Assignment**

| mont                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND<br>D63C5<br>D61C5<br>D597<br>D531D<br>D51D<br>D531D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D51D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D475<br>D50D<br>D50D<br>D50D<br>D50D5<br>D50D5<br>D50D5<br>D50D5<br>D500D5<br>D50D5<br>D50D5<br>D500D500 | 81<br>82<br>83<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97<br>98<br>99<br>90<br>101<br>102<br>103<br>104<br>105<br>106<br>107<br>108<br>100<br>110<br>111<br>112<br>113<br>114<br>115<br>116<br>117<br>118<br>1120<br>121<br>122 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>3<br>14<br>15<br>6<br>17<br>8<br>9<br>21<br>22<br>3<br>24<br>25<br>22<br>7<br>8<br>9<br>30<br>31<br>23<br>34<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>3<br>34<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>3<br>14<br>15<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>3<br>14<br>15<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>3<br>14<br>15<br>6<br>17<br>7<br>8<br>9<br>20<br>12<br>21<br>22<br>3<br>24<br>25<br>26<br>27<br>28<br>9<br>30<br>31<br>22<br>3<br>34<br>33<br>34<br>5<br>6<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>6<br>17<br>7<br>8<br>9<br>20<br>12<br>22<br>24<br>25<br>26<br>27<br>28<br>9<br>30<br>31<br>22<br>33<br>34<br>5<br>5<br>6<br>37<br>8<br>9<br>30<br>31<br>22<br>33<br>34<br>5<br>5<br>6<br>37<br>8<br>9<br>30<br>31<br>22<br>22<br>24<br>25<br>26<br>7<br>7<br>8<br>9<br>30<br>31<br>22<br>22<br>24<br>25<br>26<br>7<br>7<br>8<br>9<br>30<br>31<br>22<br>33<br>34<br>5<br>5<br>6<br>37<br>8<br>33<br>34<br>5<br>5<br>6<br>7<br>7<br>8<br>9<br>20<br>21<br>22<br>24<br>25<br>27<br>28<br>9<br>30<br>31<br>2<br>33<br>34<br>5<br>5<br>6<br>6<br>7<br>7<br>8<br>9<br>30<br>31<br>2<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3 | GND<br>D62<br>VCC3.3<br>D60<br>VCC3.3<br>D58<br>D56<br>GND<br>D76<br>D54<br>D52<br>D50<br>GND<br>D48<br>D46<br>D44<br>D42<br>GND<br>D44<br>D42<br>GND<br>D40<br>D74<br>D38<br>D36<br>D34<br>GND<br>D32<br>D30<br>D28<br>D28<br>D26<br>D24<br>GND<br>D28<br>D28<br>D26<br>D24<br>GND<br>D22<br>D20<br>VCC3.3<br>D18<br>GND<br>D72<br>D20<br>VCC3.3<br>D18<br>GND<br>D72<br>D20<br>D24<br>GND<br>D72<br>D20<br>D24<br>GND<br>D72<br>D20<br>D24<br>GND<br>D72<br>D20<br>D24<br>GND<br>D72<br>D20<br>D24<br>GND<br>D72<br>D20<br>D24<br>GND<br>D72<br>D20<br>D24<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D26<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D26<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D30<br>D28<br>D26<br>D29<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D28<br>D20<br>D29<br>D20<br>D20<br>D20<br>D20<br>D20<br>D20<br>D20<br>D20<br>D20<br>D20 |

| VCC5<br>D91<br>VCC5<br>D5<br>D3<br>DGND<br>A0B<br>A3B<br>A3B<br>A3B<br>A3B<br>A3B<br>A3B<br>A3B<br>A3B<br>A3B<br>A3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{c} 123\\ 124\\ 125\\ 126\\ 127\\ 128\\ 139\\ 131\\ 135\\ 136\\ 137\\ 138\\ 139\\ 141\\ 142\\ 143\\ 145\\ 146\\ 147\\ 148\\ 151\\ 152\\ 155\\ 156\\ 157\\ 158\\ 159\\ 160\\ \end{array}$                                                                   | $\begin{array}{c} 43\\ 44\\ 45\\ 46\\ 47\\ 48\\ 49\\ 50\\ 51\\ 52\\ 53\\ 55\\ 56\\ 57\\ 58\\ 59\\ 60\\ 62\\ 63\\ 66\\ 66\\ 66\\ 66\\ 66\\ 67\\ 71\\ 72\\ 73\\ 74\\ 75\\ 76\\ 77\\ 78\\ 79\\ 80\\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VCC3.3<br>D8<br>DP0<br>VCC3.3<br>D6<br>D4<br>D2<br>D0<br>GND<br>A0A<br>A1A<br>A2A<br>A3A<br>A5<br>GND<br>A7<br>A9<br>A11<br>A13<br>A15<br>GND<br>PD2<br>CLK1<br>CLK3<br>GND<br>PD2<br>CLK1<br>CLK3<br>GND<br>WE6<br>WE4<br>WE2<br>WE0<br>GND<br>ADV0<br>OE0<br>VCC3.3<br>ADSP0<br>GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Pins 146, 147, 154, 156, 159, 66, 67, 74, 76, 79 are no connect for the asynchronous module version.

IBM Corporation. All rights reserved.

Use is further subject to the provisions at the end of this document.

## **Pin Definition**

| Address                   |

|---------------------------|

| Data I/O                  |

| Parity I/O                |

| Chip Enable               |

| Byte Write Enable         |

| Output Enable             |

| Address Status Processor  |

| Address Status Controller |

| Address Advance           |

| Clock                     |

| Presence Detect           |

| Ground                    |

| Power Supply              |

|                           |

# **Pin Description**

| Signal         | I/O | Level | Description                                                                                                                                                                                                                                                                                                        |

|----------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A15         | I   | N/A   | Address inputs. These inputs are registered at the rising edge of CLK if $\overline{\text{ADSP}}$ or $\overline{\text{ADSC}}$ is LOW.                                                                                                                                                                              |

| D0-D15         | I/O | N/A   | Data I/O. The 64 bit data bus is divided into 8 bytes: D(0:7), D(8:15), D(16:23), D(24:31), D(32:39), D(40:47), D(48:55), D(56:63). D(0:7) is the least significant byte and D(56:63) is the most significant byte. The direction of the data pins is controlled by OE.                                            |

| DP0-DP7        | I/O | N/A   | Data Parity I/O. These are the data parity bits for the data bus. DQP0 applies to D(0:7) and DQP7 applies to D(56:63).                                                                                                                                                                                             |

| CE0-CE1        | 1   | LOW   | Chip enable. These lines are used to enable or disable the module. They can also be used to block ADSP.                                                                                                                                                                                                            |

| WEO-WE7        | I   | LOW   | Byte write enables. These lines allow individual bytes to be written to the module. WE0 controls DQ0-DQ7 and DQP0, WE1 controls DQ8-DQ15 and DQP1, etc.                                                                                                                                                            |

| OE0-OE1        | I   | LOW   | Output enable. These are asynchronous inputs which enable the data I/O drivers when active.                                                                                                                                                                                                                        |

| ADSP0-ADSP1    | I   | LOW   | Address Status Processor. When this input and/or ADSC is active, <u>a new external</u><br>address will be latched thus interrupting any ongoing bur <u>st. If both ADSP and ADSC are</u><br>active at the same time (at the rising edge of CLK), only ADSP will be recognized. ADSP<br>is ignored when CE is HIGH. |

| ADSC0-ADSC1    | I   | LOW   | Address Status Controller. When this input and/or ADSP is active, a new external address will be latched thus interrupting any ongoing burst. A read or write is performed using the new address if all chip enables are active.                                                                                   |

| ADV0-ADV1      | I   | LOW   | Address Advance. The input is used to automatically increment the internal burst address counter. Depending on the module type, the burst sequence can be either linear (Power-PC based) or interleaved (Pentium/486) based.                                                                                       |

| CLK(0:3)       | I   | N/A   | Clock. This signal is used to latch the address, data (store), ADSP, ADSC, CE, WE, and ADV. All synchronous inputs must meet setup and hold times around the clock's rising edge.                                                                                                                                  |

| GND            | Ι   | N/A   | Ground.                                                                                                                                                                                                                                                                                                            |

| VCC3.3 or VCC5 | I   | N/A   | Power Supply: +3.3V (Synchronous modules) or +5.0V (Asynchronous module)                                                                                                                                                                                                                                           |

# **Ordering Information**

| Part Number       | Organization | Speed                      | Availability | Туре    |

|-------------------|--------------|----------------------------|--------------|---------|

| IBM14N32722FPA-9  | 32K x 72     | 9 ns Access / 15 ns Cycle  | On Request   | Pentium |

| IBM14N32722FPA-11 | 32K x 72     | 11 ns Access / 15 ns Cycle | On Request   | Pentium |

| IBM14N64722DPA-9  | 64K x 72     | 9 ns Access / 15 ns Cycle  | On Request   | Pentium |

| IBM14N64722DPA-11 | 64K x 72     | 11 ns Access / 15 ns Cycle | On Request   | Pentium |

| IBM14N13722DPA-9  | 128K x 72    | 9 ns Access / 15 ns Cycle  | On Request   | Pentium |

| BM14N13722DPA-11  | 128K x 72    | 11 ns Access / 15 ns Cycle | On Request   | Pentium |

| BM14N32724FPA-9   | 32K x 72     | 9 ns Access / 15 ns Cycle  | On Request   | PowerPC |

| BM14N32724FPA-11  | 32K x 72     | 11 ns Access / 15 ns Cycle | On Request   | PowerPC |

| BM14N64724DPA-9   | 64K x 72     | 9 ns Access / 15 ns Cycle  | Now          | PowerPC |

| BM14N64724DPA-11  | 64K x 72     | 11 ns Access / 15 ns Cycle | Now          | PowerPC |

| BM14N13724DPA-9   | 128K x 72    | 9 ns Access / 15 ns Cycle  | Now          | PowerPC |

| BM14N13724DPA-11  | 128K x 72    | 11 ns Access / 15 ns Cycle | Now          | PowerPC |

| BM14N13722DPB-9   | 128K X 72    | 9 ns Access / 15 ns Cycle  | On Request   | Pentium |

| BM14N13722DPB-11  | 128K X 72    | 11 ns Access / 15 ns Cycle | On Request   | Pentium |

| BM14N13724DPB-9   | 128K X 72    | 9 ns Access / 15 ns Cycle  | On Request   | PowerPC |

| BM14N13724DPB-11  | 128K X 72    | 11 ns Access / 15 ns Cycle | On Request   | PowerPC |

| BM14N64726GAA-12  | 64K x 72     | 12 ns Access / 15 ns Cycle | On Request   | Asynch. |

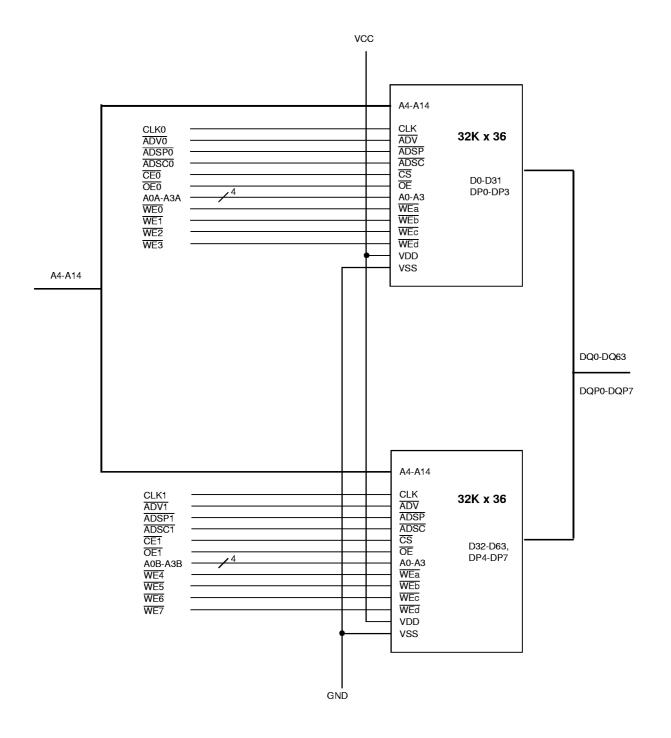

#### Block Diagram: Synchronous module 32K x 72

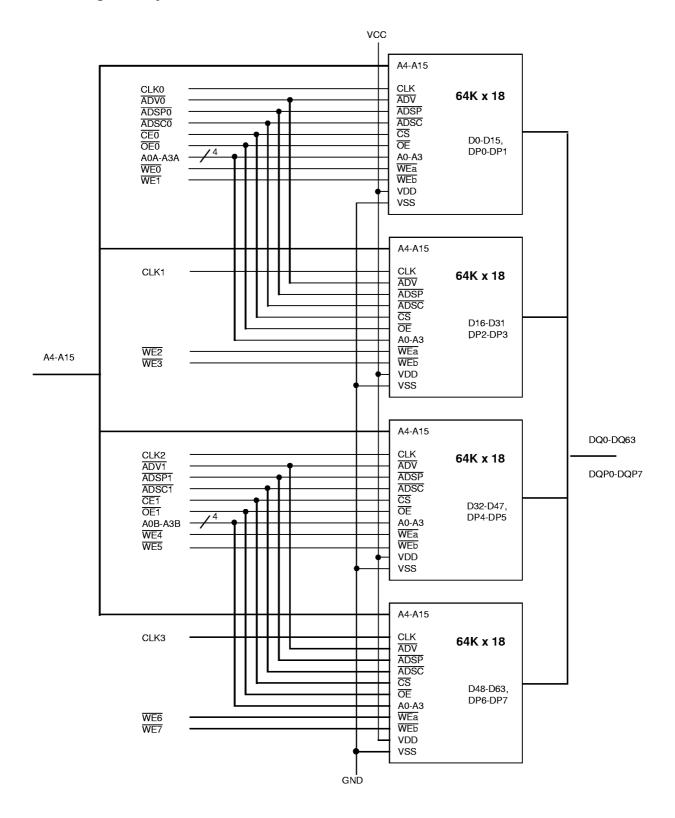

#### Block Diagram: Synchronous module 64K x 72

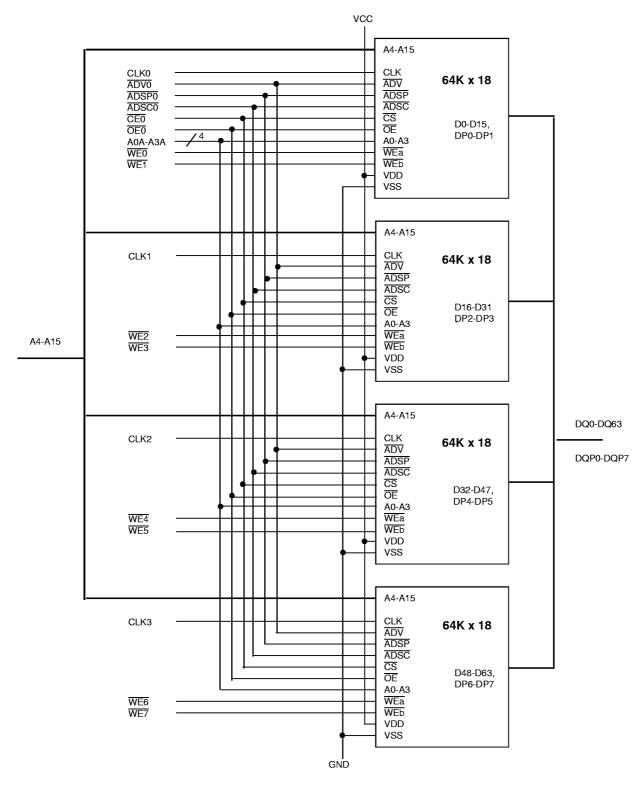

#### Block Diagram: Synchronous module 128K x 72 - Front Side

Note: The following nets are dotted front to back: WE0 through WE7, CLK0 through CLK3, DQ0 through DQ63, DQP0 through DQP7

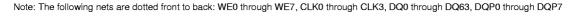

#### Block Diagram: Synchronous module 128K x 72 - Back Side

#### Block Diagram: Asynchronous module 64K x 72

# Asynchronous module (512KB)

## Burst Sequence Truth Table Synchronous modules, interleave burst

| External Address | A15-A2 | (A1,A0) |       |       |       |  |

|------------------|--------|---------|-------|-------|-------|--|

|                  | AIJAZ  | (0,0)   | (0,1) | (1,0) | (1,1) |  |

| 1st Access       | A15-A2 | (0,0)   | (0,1) | (1,0) | (1,1) |  |

| 2nd Access       | A15-A2 | (0,1)   | (0,0) | (1,1) | (1,0) |  |

| 3rd Access       | A15-A2 | (1,0)   | (1,1) | (0,0) | (0,1) |  |

| 4th Access       | A15-A2 | (1,1)   | (1,0) | (0,1) | (0,0) |  |

#### Burst Sequence Truth Table Synchronous modules, linear burst

| External Address | A15-A2 | (A1,A0) |       |       |       |  |

|------------------|--------|---------|-------|-------|-------|--|

| External Address | AT5-AZ | (0,0)   | (0,1) | (1,0) | (1,1) |  |

| 1st Access       | A15-A2 | (0,0)   | (0,1) | (1,0) | (1,1) |  |

| 2nd Access       | A15-A2 | (0,1)   | (1,0) | (1,1) | (0,0) |  |

| 3rd Access       | A15-A2 | (1,0)   | (1,1) | (0,0) | (0,1) |  |

| 4th Access       | A15-A2 | (1,1)   | (0,0) | (0,1) | (1,0) |  |

## **Presence Detect Table**

| Part Number    | Module Burst Type |       |      | PD1  |      |

|----------------|-------------------|-------|------|------|------|

| IBM14N32722FPA | Interleaved       | 256KB | N.C. | GND  | GND  |

| IBM14N64722DPA | Interleaved       | 512KB | GND  | GND  | GND  |

| IBM14N13722DPA | Interleaved       | 1MB   | GND  | N.C. | GND  |

| BM14N32724FPA  | Linear            | 256KB | N.C. | GND  | N.C. |

| BM14N64724DPA  | Linear            | 512KB | GND  | GND  | N.C. |

| BM14N13724DPA  | Linear            | 1MB   | GND  | N.C. | N.C. |

| BM14N64726GAA  | Asynch            | 512KB | GND  | GND  | NC   |

### **Absolute Maximum Ratings**

| Parameter                    | Symbol           | Rating                        | Units | Notes |

|------------------------------|------------------|-------------------------------|-------|-------|

| Power Supply Voltage (3.3V)  | V <sub>CC3</sub> | -0.5 to 4.6                   | V     | 1, 2  |

| Power Supply Voltage (5.0V)  | V <sub>CC5</sub> | -0.5 to 7                     | V     | 1, 3  |

| Input Voltage                | V <sub>IN</sub>  | -0.5 to 6.0                   | V     | 1     |

| Output Voltage               | V <sub>OUT</sub> | -0.5 to V <sub>CC3</sub> +0.5 | V     | 1     |

| Operating Temperature        | T <sub>OPR</sub> | 0 to +70                      | °C    | 1     |

| Storage Temperature          | T <sub>STG</sub> | -55 to +125                   | °C    | 1     |

| Power Dissipation            | P <sub>D</sub>   | 6.0                           | W     | 1, 2  |

| Power Dissipation            | PD               | 8.0                           | w     | 1, 3  |

| Short Circuit Output Current | I <sub>OUT</sub> | 50                            | mA    | 1     |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

2. For synchronous modules only.

3. For asynchronous module only.

#### Recommended DC Operating Conditions (TA=0 to 70 C) : Synchronous modules

|                    | Symbol             | Min.  | Тур. | Max.  | Units | Notes   |

|--------------------|--------------------|-------|------|-------|-------|---------|

| Supply Voltage     | V <sub>CC3.3</sub> | 3.135 | 3.3  | 3.465 | V     | 1, 4    |

| Input High Voltage | V <sub>IH</sub>    | 2.2   | —    | 5.5   | v     | 1, 2, 4 |

| Input Low Voltage  | VIL                | -0.3  | —    | 0.8   | V     | 1, 3, 4 |

| Output Current     | Ι <sub>ουτ</sub>   |       | 5    | 8     | mA    | 4       |

1. All voltages referenced to  $V_{\text{SS}}.$  All  $V_{\text{DD}}$  and  $V_{\text{SS}}$  pins must be connected.

2.  $V_{IH}(Max)DC = 5.5 \text{ V}, V_{IH}(Max)AC = 6.0 \text{ V} \text{ (pulse width} \le 4.0 \text{ns})$

3.  $V_{IL}(Min)DC = -0.3 \text{ V}, V_{IL}(Min)AC = -1.5 \text{ V} \text{ (pulse width } \leq 4.0 \text{ ns)}$

4. Input Voltage levels are tested to the following DC conditions: 1 microsecond cycle and 200 nanosecond set-up and hold times.

#### Capacitance (TA=0 to +70 C, VDD=3.3V 5%, f=1MHz) Maximum values: Synchronous modules

| Parameter                           | Symbol           | Test Condition        | 256KB | 512KB | 1MB | Units |

|-------------------------------------|------------------|-----------------------|-------|-------|-----|-------|

| Input Capacitance (Address)         | C <sub>IN1</sub> | $V_{IN} = 0V$         | 15    | 25    | 45  | pF    |

| Input Capacitance (Control, CE, OE) | C <sub>IN2</sub> | $V_{IN} = 0V$         | 10    | 15    | 25  | pF    |

| Input Capacitance (WE, CLK)         | C <sub>IN3</sub> | $V_{IN} = 0V$         | 10    | 10    | 15  | pF    |

| Data I/O Capacitance (DQ0-DQ71)     | C <sub>OUT</sub> | V <sub>OUT</sub> = 0V | 10    | 10    | 15  | pF    |

#### DC Electrical Characteristics (TA= 0 to +70 C, VDD=3.3V 5%): Synchronous modules

| Parameter                                                                                                                                                                                          | Symbol                                 | Min. | Max. | Units | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|------|-------|-------|

| Operating Current<br>Average Power Supply Operating Current<br>(OE = V <sub>IH</sub> , I <sub>OUT</sub> = 0)                                                                                       | I <sub>DD10</sub><br>I <sub>DD12</sub> |      | 900  | mA    | 1     |

| Standby Current<br>Power Supply Standby Current<br>(CS2 = V <sub>IH</sub> , CS2 = V <sub>IL</sub> All other inputs = V <sub>IH</sub> or V <sub>IL</sub> , I <sub>OUT.</sub> = 0, CLK at<br>100MHz) | I <sub>SB</sub>                        |      | 100  | mA    | 1     |

| Input Leakage Current<br>Input Leakage Current, any input<br>(V <sub>IN</sub> = 0 &V <sub>DD</sub> )                                                                                               | lu                                     |      | 8    | μΑ    |       |

| Output Leakage <u>Current</u><br>(V <sub>OUT</sub> =0 &V <sub>DD</sub> , <del>OE</del> = V <sub>IH</sub> )                                                                                         | I <sub>LO</sub>                        |      | 8    | μA    |       |

| Output High Level<br>Output "H" Level Voltage (I <sub>OH</sub> =-8mA @ 2.4V)                                                                                                                       | V <sub>OH</sub>                        | 2.4  |      | v     |       |

| Output Low Level<br>Output "L" Level Voltage (I <sub>OL</sub> =+8mA @ 0.4V)                                                                                                                        | V <sub>OL</sub>                        |      | 0.4  | v     |       |

| 1. I <sub>OUT</sub> = Chip Output Current                                                                                                                                                          |                                        |      |      |       |       |

#### **Recommended DC Operating Conditions** (TA=0 to 70 C): Asynchronous Module

| Parameter             |                 |      | Тур. |         | Units |      |

|-----------------------|-----------------|------|------|---------|-------|------|

| Supply Voltage (5.0V) | V <sub>CC</sub> | 4.75 | 5.0  | 5.25    | V     | 1    |

| Input High Voltage    | V <sub>IH</sub> | 2.2  | —    | Vcc+0.3 | V     | 1, 2 |

| Input Low Voltage     | VIL             | -0.5 | —    | 0.8     | V     | 1, 3 |

| Output Current        | Гонт            |      | -5   | 5       | mA    |      |

2.  $V_{\rm H}({\rm Max}) = VCC + 0.5$

3.  $V_{IL}(Min)DC$  = - 0.3 V,  $V_{IL}(Min)AC$ = -2.0V (pulse width  $\leq$  20.0 ns.)

Capacitance (TA=0 to 70 C, VCC5=5V 5%, f=1MHz) Maximum values: Asynchronous Module

| Parameter                       |            | Symbol           | Test Condition                          | 512KB | Units |  |

|---------------------------------|------------|------------------|-----------------------------------------|-------|-------|--|

|                                 | A0 A3      | C.               | $V_{IN} = 0V$                           | 50    | ъС    |  |

| Input Capacitance (Address)     | All others | U <sub>IN1</sub> | $\mathbf{v}_{\text{IN}} = 0 \mathbf{v}$ | 100   | p⊢    |  |

| Input Capacitance (CE, OE)      |            | C <sub>IN2</sub> | $V_{IN} = 0V$                           | 65    | pF    |  |

| Input Capacitance (WE)          |            | C <sub>IN3</sub> | $V_{IN} = 0V$                           | 18    | pF    |  |

| Data I/O Capacitance (DQ0-DQ71) |            | С <sub>оит</sub> | V <sub>OUT</sub> = 0V                   | 10    | pF    |  |

#### DC Electrical Characteristics TA= 0 to +70 C, VCC5=5V 5%) : Asynchronous Module

| Parameter                                                                                                                                                                                                  | Symbol            | Min. | Max. | Units | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|-------|-------|

| Operating Current @ 5.0V<br>Maximum Power Supply Operating Current<br>(Maximum V <sub>CC5</sub> , I <sub>out</sub> = 0)                                                                                    | I <sub>CC12</sub> |      | 1140 | mA    | 1     |

| Standby Current @ 5.0V<br>Power Supply Standby Current<br>(Maximum V <sub>CC5</sub> , V <sub>IH</sub> $\leq$ <del>CS</del> ; All other inputs = V <sub>IH</sub> or V <sub>IL</sub> ; I <sub>out</sub> = 0) | I <sub>SB</sub>   |      | 640  | mA    | 1     |

| Input Leakage Current<br>Input Leakage Current, any input<br>(V <sub>IN</sub> = 0 &V <sub>CC</sub> )                                                                                                       | lu                |      | 40   | μA    |       |

| Output Leakage Current<br>(V <sub>OUT</sub> =0 &V <sub>CC</sub> , OE = V <sub>IH</sub> )                                                                                                                   | ILO               |      | 40   | μA    |       |

| Output High Level<br>Output "H" Level Voltage (I <sub>OH</sub> =-8mA @ 2.4V)                                                                                                                               | V <sub>OH</sub>   | 2.4  |      | v     |       |

| Output Low Level<br>Output "L" Level Voltage (I <sub>OL</sub> =+8mA @ 0.4V)                                                                                                                                | V <sub>OL</sub>   |      | 0.4  | v     |       |

| 1. I <sub>OUT</sub> = Chip Output Current                                                                                                                                                                  |                   |      |      |       |       |

| Parameter                            | Symbol             | -9   |          | -11  |          | Notes   |

|--------------------------------------|--------------------|------|----------|------|----------|---------|

| Faidhletei                           | Symbol             | Min. | Max.     | Min. | Max.     | NOLES   |

| Cycle Time                           | t <sub>CYCLE</sub> | 15.0 | —        | 15.0 | —        |         |

| Clock Pulse High                     | t <sub>сн</sub>    | 3.0  | —        | 3.0  | —        |         |

| Clock Pulse Low                      | t <sub>c∟</sub>    | 3.0  | —        | 3.0  | —        |         |

| Clock to Output Valid                | tca                | —    | 9.0      | —    | 11.0     | 1       |

| Address Status Controller Setup Time | t <sub>ADSCS</sub> | 2.5  | —        | 2.5  | —        |         |

| Address Status Controller Hold Time  | tadsch             | 0.5  | —        | 0.5  | —        |         |

| Address Status Processor Setup Time  | t <sub>adsps</sub> | 2.5  | <b>—</b> | 2.5  | —        |         |

| Address Status Processor Hold Time   | t <sub>adsph</sub> | 0.5  | -        | 0.5  | —        |         |

| Advance Setup Time                   | t <sub>ADVS</sub>  | 2.5  | ÷ —      | 2.5  | —        |         |

| Advance Hold Time                    | t <sub>ADVH</sub>  | 0.5  | <u> </u> | 0.5  | —        |         |

| Address Setup Time                   | t <sub>AS</sub>    | 2.5  | <u> </u> | 2.5  | —        |         |

| Address Hold Time                    | t <sub>AH</sub>    | 0.5  | —        | 0.5  | —        |         |

| Chip Selects Setup Time              | t <sub>CSS</sub>   | 2.5  | —        | 2.5  | —        |         |

| Chip Selects Hold Time               | t <sub>сsн</sub>   | 0.5  | —        | 0.5  | —        |         |

| Write Enables Setup Time             | t <sub>wes</sub>   | 2.5  | —        | 2.5  | —        |         |

| Write Enables Hold Time              | t <sub>wEH</sub>   | 0.5  | —        | 0.5  | —        |         |

| Data In Setup Time                   | t <sub>DS</sub>    | 2.5  | —        | 2.5  | —        |         |

| Data In Hold Time                    | t <sub>DH</sub>    | 0.5  | —        | 0.5  | —        |         |

| Data Out Hold Time                   | t <sub>CQX</sub>   | 3.0  |          | 3.0  | <u> </u> | 1       |

| Clock High to Output High Z          | t <sub>CHZ</sub>   | —    | 5.0      | —    | 5.5      | 1, 2, 3 |

| Clock High to Output Active          | t <sub>CLZ</sub>   | 2.5  | —        | 2.5  | —        | 1, 2, 3 |

| Output Enable to High Z              | t <sub>онz</sub>   | 2.0  | 5.5      | 2.0  | 6.5      | 1, 2    |

| Output Enable to Low Z               | t <sub>oLZ</sub>   | 0.25 | —        | 0.25 | —        | 1, 2    |

| Output Enable to Output Valid        | t <sub>oq</sub>    | -    | 5.0      | —    | 6.0      | 1       |

#### AC Characteristics (TA=0 to +70 C, VDD=3.3V 5%, Units in nsec) Synchronous modules

1. See AC Test Loading figure on the next page.

2. Transitions are measured  $\pm$  200 mV from steady state voltage.

3. At any given voltage and temperature, T<sub>CHZ</sub> max is always less than T<sub>CLZ</sub> min for a given device and from device to device. For any read cycle preceded by a write or deselect cycle, the data bus will transition glitch-free from HIZ to new RAM data.

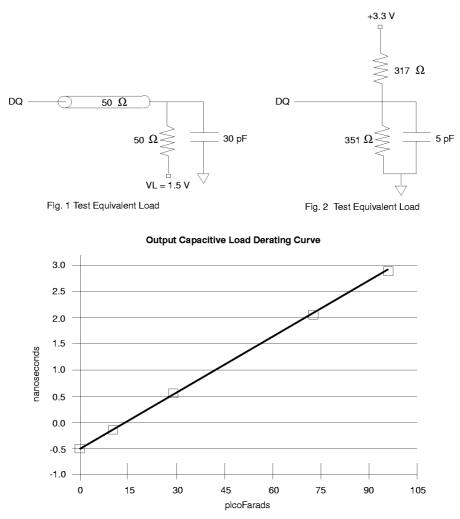

## **AC Test Loading**

The derating curve above is for a purely capacitive load on the output driver. For example, a part specified at 8ns access time will behave as though it has an 8.5 ns access time if a 30 pF load with no DC component was attached to the output driver. The access time guaranteed in the datasheets are based on a 50 ohm terminated test load. For unterminated loads the derating curve should be used. This curve is based on nominal process conditions with worst case parameters  $V_{CC} = 3.14$  V,  $T_a = 70$  °C.

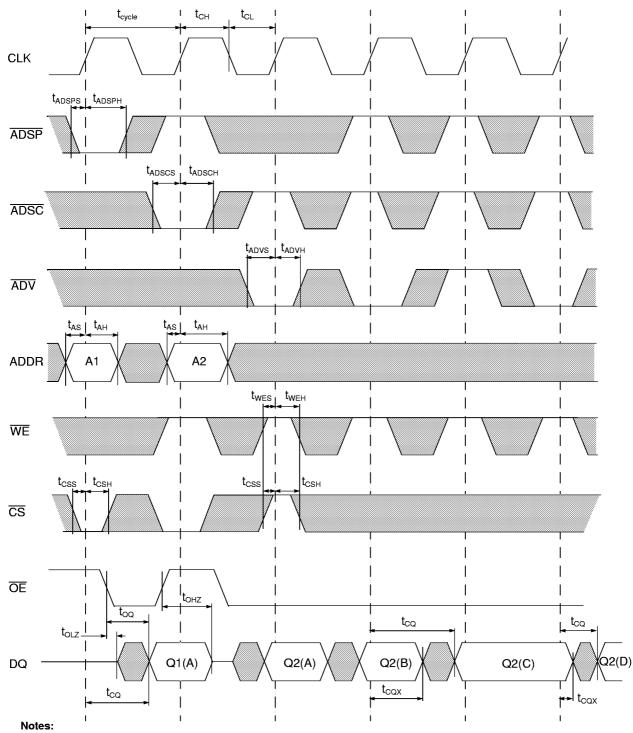

## Synchronous SRAM Timing Diagram (Burst Read)

1. Q1(A) and Q2(A) refer to output for Address A1 and A2 respectively.

2. Q2(B),Q2(C) and Q2(D) refer to output from subsequent internal burst counter addresses.

©IBM Corporation. All rights reserved. Use is further subject to the provisions at the end of this document.

#### I t<sub>cycle</sub> $t_{CH}$ $t_{CL}$ CLK tadsps | tadsph ADSP tADSCS | tADSCH ADSC t<sub>advh</sub> t<sub>ADVS</sub> t<sub>advh</sub> ADV 1 $t_{\text{ADVS}}$ tas tah t<sub>AS</sub> t<sub>AH</sub> A1 A2 ADDR t<sub>wen</sub> t<sub>wes</sub> WE t<sub>css</sub> | t<sub>csH</sub> t<sub>css</sub> | t<sub>csн</sub> $\overline{CS}$ ŌĒ t<sub>onz</sub> t<sub>DS</sub> | t<sub>DH</sub> t<sub>DS</sub> | t<sub>DH</sub> t<sub>DS</sub> | t<sub>DH</sub> t<sub>DS</sub> I t<sub>DH</sub> DQ D1(A) D2(A) D2(B) D2(B) t<sub>CLZ</sub> □ t<sub>oHZ</sub> ı I I

## Synchronous SRAM Timing Diagram (Burst Write)

Notes:

1.D1(A) and D2(A) refer to data written to addresses A1 and A2.

2. D2(B) refers to data written to a subsequent internal burst counter address.

3.  $\overline{\text{WE}}$  is a Don't Care when  $\overline{\text{ADSP}}$  is sampled LOW.

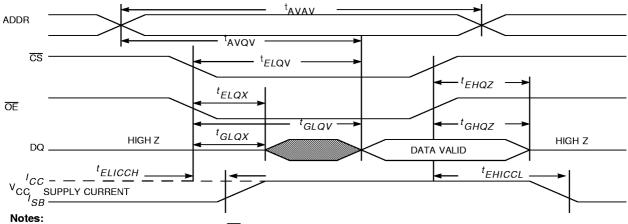

## Asynchronous SRAM Timing Diagram (Read)

Addresses valid prior to or coincident with TE going low. .1.

## **Read Cycle**

| Parameter                           | Symbol              | DA   | TA   |      | Notes   |  |

|-------------------------------------|---------------------|------|------|------|---------|--|

|                                     |                     | Min. | Max. | Unit |         |  |

| Read Cycle Time                     | t <sub>AVAV</sub>   | 12   |      | ns   | 2       |  |

| Address Cycle Time                  | t <sub>AVQV</sub>   |      | 12   | ns   |         |  |

| Enable Access Time                  | t <sub>ELQV</sub>   |      | 12   | ns   | 3       |  |

| Output Enable Access Time           | t <sub>GLQV</sub>   |      | 6    | ns   |         |  |

| Output Hold from Address Change     | t <sub>AXQX</sub>   | 3    |      | ns   | 4, 5, 6 |  |

| Enable Low to Output Active         | t <sub>ELQX</sub>   | 4    |      | ns   | 4, 5, 6 |  |

| Enable High to Output High-Z        | t <sub>EHQZ</sub>   | 0    | 7    | ns   | 4, 5, 6 |  |

| Output Enable Low to Output Active  | t <sub>GLQX</sub>   | 0    |      | ns   | 4, 5, 6 |  |

| Output Enable High to Output High-Z | t <sub>GHQZ</sub>   | 0    | 6    | ns   | 4, 5, 6 |  |

| Power Up Time                       | t <sub>ELICCH</sub> | 0    |      | ns   |         |  |

| Power Down Time                     | t <sub>EHICCL</sub> |      | 12   | ns   |         |  |

WE(0:7) is high for read cycle.

All timings are referenced from the last valid address to the first transitioning address.

3. Addresses valid prior to or coincident with  $\overline{CE}$  going low

4. At any given voltage and temperature,  $t_{EHQZ}$  (max) <  $t_{ELQX}$  (min), and  $t_{GHQZ}$  (max) <  $t_{GLQX}$  (min), both for a given device and from device to device.

5. Transition is measured ±500 mv from steady-state voltage.

6. This parameter is sampled and not 100% tested.

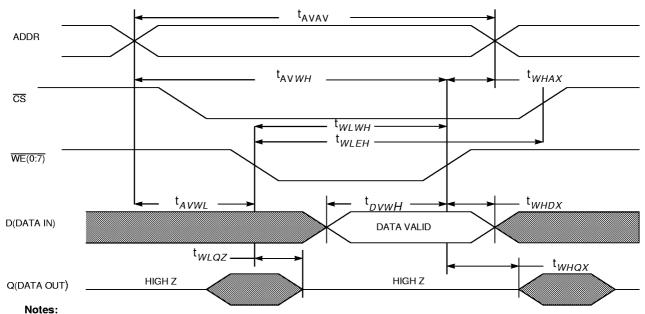

# Asynchronous SRAM Timing Diagram (Write Cycle 1)

1. 2.

A write occurs during the overlap of  $\overline{OE}$  low and  $\overline{WE}$  low.. If  $\overline{OE}$  goes low coincident with or after  $\overline{WE}$  goes low, the output will remain in a high impedance state.

# Write Cycle 1 (WE Controlled)

| Parameter                     | Cumb al                                | DATA |      |      |         |

|-------------------------------|----------------------------------------|------|------|------|---------|

|                               | Symbol                                 | Min. | Max. | Unit | Notes   |

| Write Cycle Time              | t <sub>AVAV</sub>                      | 12   |      | ns   | 1       |

| Address Setup Time            | t <sub>AVWL</sub>                      | 0    |      | ns   |         |

| Address Valid to End of Write | t <sub>avwh</sub>                      | 10   |      | ns   |         |

| Write Pulse Width             | t <sub>WLWH</sub><br>t <sub>WLEH</sub> | 10   |      | ns   |         |

| Write Pulse Width G High      | t <sub>WLWH</sub><br>t <sub>WLEH</sub> | 9    |      | ns   | 2       |

| Data Valid to End of Write    | t <sub>ovwн</sub>                      | 6    |      | ns   |         |

| Data Hold Time                | t <sub>whox</sub>                      | 0    |      | ns   |         |

| Write Low to Output High-Z    | t <sub>wLQZ</sub>                      | 0    | 6    | ns   | 3, 4, 5 |

| Write High to Output Active   | t <sub>WHQX</sub>                      | 2    |      | ns   | 3, 4, 5 |

| Write Recovery Time           | t <sub>WHAX</sub>                      | 0    |      | ns   |         |

1. All timings are referenced from the last valid address to the first transitioning address.

2. If  $V_{IH} \leq \overline{OE}$ , the output will remain in a high impedance state

3. At any given voltage and temperature , t<sub>WLOZ</sub> (max) < t<sub>WHQX</sub> (min), both for a given device and from device to device.

4. Transition is measured  $\pm$ 500 mv from steady state voltage.

5. This parameter is sampled and not 100% tested.

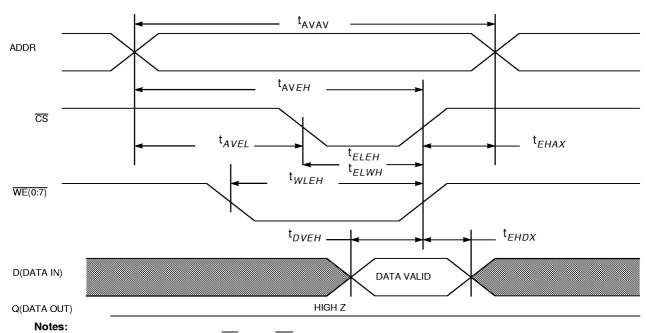

#### Asynchronous SRAM Timing Diagram (Write Cycle 2)

A write occurs during the overlap of  $\overline{OE}$  low and  $\overline{WE}$  low. 1.

## Write Cycle 2 (OE Controlled)

| Parameter                     | Cymhol                                 |      | DATA |      | N     |

|-------------------------------|----------------------------------------|------|------|------|-------|

|                               | Symbol                                 | Min. | Max. | UIII | Notes |

| Write Cycle Time              | t <sub>avav</sub>                      | 12   |      | ns   |       |

| Address Setup Time            | t <sub>AVEL</sub>                      | 0    |      | ns   |       |

| Address Valid to End of Write | t <sub>AVEH</sub>                      | 10   |      | ns   |       |

| Enable to End of Write        | t <sub>ELEH</sub><br>t <sub>ELWH</sub> | 9    |      | ns   | 3, 4  |

| Data Valid to End of Write    | t <sub>DVEH</sub>                      | 6    |      | ns   |       |

| Data Hold Time                | t <sub>EHDX</sub>                      | 0    |      | ns   |       |

| Write Recovery Time           | t <sub>EHAX</sub>                      | 0    |      | ns   |       |

- A write occurs during the overlap of OE low and WE low

All timings are referenced from the last valid address to the first transitioning address.

If OE goes low coincident with or after WE goes low, the output will remain in a high impedance state.

If OE goes high coincident with or before WE goes high, the output will remain in a high impedance state.

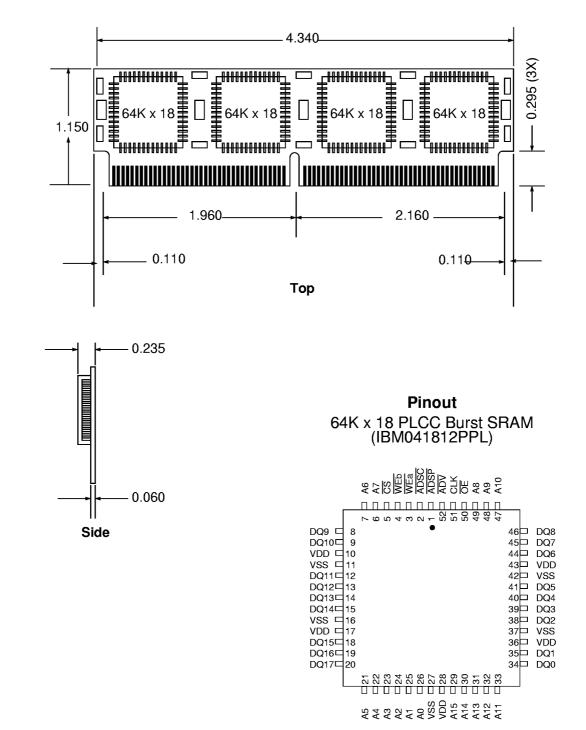

#### Layout Drawing: 512KB (64K x 72), 160-pin, Synchronous module

#### Layout Drawing: 1MB (128K x 72), 160-pin, Synchronous module

#### Layout Drawing: 256KB (32K x 72), 160-pin, Synchronous module

Front View:

#### Layout Drawing 512KB (64K x 72), 160-pin, Asynchronous module

#### 4.340 (3X) Δ المعالمة المحالية المح محالية المحالية ý t þ t \$ ↓ \$ + ¥ + ╈ + Þ • **9** + 0.295 P Ψ 1.150 Lւ L. БŢ 0,0 Δ 1.960 2.160 0.110 — - 0.110 \_\_\_\_

#### Back View:

# **Revision Log**

| Rev   | Contents of Modification                                      |

|-------|---------------------------------------------------------------|

| 10/94 | Initial Release                                               |

| 2/95  | Added x36 module info., updated text and added part numbers   |

| 5/95  | Added pin capacitance values and defined PD bits.             |

| 11/95 | Updated DIMM speed offerings and other pertinent information. |

| 12/95 | Official release.                                             |

| 2/96  | Update part numbers (added 1MB SE design).                    |

| 4/98  | re-release of document.                                       |