# CPC710-133 PCI Bridge and SDRAM Memory Controller

### Highlights

- Provides a high-performance single-chip system controller for PowerPC<sup>®</sup> processor designs geared to high-throughput applications

- Features an integrated 133MHz SDRAM controller with support for industry-standard memory and a 133MHz 2.5V CPU bus interface with an internal arbiter that supports multiple processors

- Dual PCI interfaces can ease board design and provide design flexibility

- Multiple internal data paths support high-speed data transfers between interfaces

## Robust features support diverse high-speed designs

The CPC710-133 PCI Bridge SDRAM Memory Controller is a single-chip solution for applications requiring high throughput, including networking devices such as access routers, gateways, VPN equipment and switches, and real-time-data and signal-processing applications. The CPC710-133 controller's highly integrated, full-featured design enables a wide range of configurations geared to diverse requirements. Implemented in IBM's SA-12e process technology, the CPC710-133 controller takes advantage of IBM's advanced ASIC capabilities to deliver exceptional price/performance to satisfy price-sensitive applications.

#### PowerPC Processor Interface

Offering speeds of up to 133MHz (at 2.5V), the CPC710-133 CPU interface implements a 64-bit data bus and a 32-bit address bus with internal arbitration logic that supports up to four PowerPC 7xx processors and pipelining of up to six outstanding transactions. Additionally, separate dual 32-byte load buffers for the CPU bus and each PCI bus, along with multiple data paths, allow concurrent non-blocking transfers to support fast-access designs.

#### **SDRAM Memory Controller**

The versatile CPC710-133 memory controller supports a wide range of industry-standard memories, enabling customers to choose cost-effective solutions for their applications. The memory controller supports 133MHz SDRAMs, PC133-compliant SDRAM modules and DIMMs, and registered SDRAM DIMMs. Designers can use 16, 64, or 256Mb memories in 2- to 4-bank configurations or design for up to 3.5GB in 6 DIMMs. The CPC710-133 provides high reliability, without a performance penalty, using an

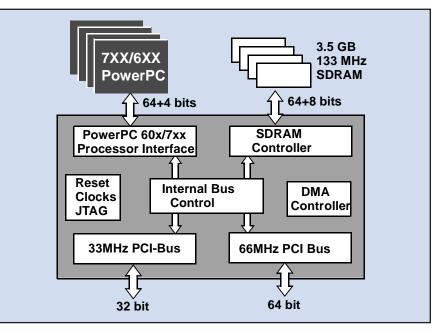

CPC710-133 block diagram

## CPC710-133 PCI Bridge and SDRAM Memory Controller Specifications

| Technology          | 0.25um CMOS SA-12e                                                                                                         |

|---------------------|----------------------------------------------------------------------------------------------------------------------------|

| Peak performance    | Up to 132MBps on the 32-bit PCI bus@33MHz<br>Up to 528MBps on the 64-bit PCI bus@66MHz<br>Up to 1,064MBps memory bandwidth |

| Clocking            | PCI-32 Interface clock: 33MHz<br>PCI-64 Interface clock: 33 to 66MHz<br>PowerPC bus: 133MHz, 100MHz                        |

| Power dissipation   | 2.1W@133MHz typical (estimate)                                                                                             |

| Power supply        | 3.3V +/-5% (I/O logic)<br>2.5V +/-2.5% (core and CPU bus logic)                                                            |

| Temperature range   | -40°C to 70°C ambient (85°C junction)                                                                                      |

| Storage temperature | -65°C to 150°C                                                                                                             |

| Signal I/Os         | 480                                                                                                                        |

| Packaging           | 728-contact, 1.27mm pitch, 35x35mm, FC-PBGA with direct lid attach (DLA)                                                   |

| Partnumber          | IBM25CPC710CF3B133                                                                                                         |

8-bit ECC capability for single-bit error correct on double-bit error detection.

# Dual PCI Interfaces and other chip features

Two PCI Interfaces and a range of other features can enhance design flexibility and help enable manufacturers to take advantage of new faster PCI 64-bit devices as well as widely available 32-bit PCI peripherals.

- Dual PCI Interfaces

- Fully compliant with PCI bus Revision 2.1

- One 32-bit, 33MHz PCI bus (3.3V I/O, supports +5V signaling)

- One 64-bit, 33 to 66MHz PCI bus (3.3V, supports only 3V signaling)

- Programmable base address register, providing memorymapping flexibility

- PCI master/slave with burst operation

- Programmable Little/Big Endian byte order conversion

- Support for internal or external PCI bus arbitration

- Up to 2MB of boot ROM and 256MB of extended FLASH support on 32-bit PCI bus

- Additional features

- Single-channel, chained DMA Controller

- Ability to address and program all features and configuration registers from the processor

IEEE 1149.1 JTAG port

For more information, visit our Web site at: www.**ibm.com**/powerpc

© Copyright IBM Corporation 2002

All Rights Reserved

Printed in the United States of America 4-02

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both: IBM the IBM Logo PowerPC

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Division 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at **ibm.com**. The IBM Microelectronics Division home page can be found at **ibm.com**/chips.

To receive the latest updates to PowerPC technical information from IBM Microelectronics, subscribe to tech e-mail at: **ibm.com**/chips/newsbriefs.