PRELIMINARY February 1995

# ICSS1001, ICSS1002, and ICSS1003 IC/SS Power Line Carrier Local Area Network Chip Set

## **General Description**

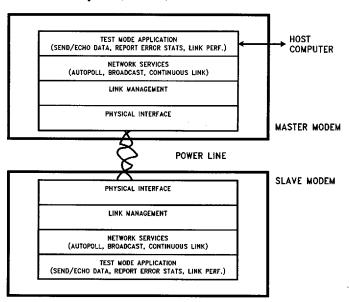

Integrated Circuit/Spread Spectrum (IC/SSTM) is a power line carrier local area network system implemented in a three chip solution, using power line carrier technology developed by Itron and Cyplex. It is designed to operate with high reliability over the full range of power line conditions. IC/SS is offered with an integral local area network protocol, designed specifically for supervisory control and data acquisition applications.

## **Features**

- Spread spectrum, adaptive frequency hopping modulation provides high immunity to power line noise.

- Network/transparent option offers the user the ability to carry proprietary protocols transparently, or to use the built-in link layer protocol.

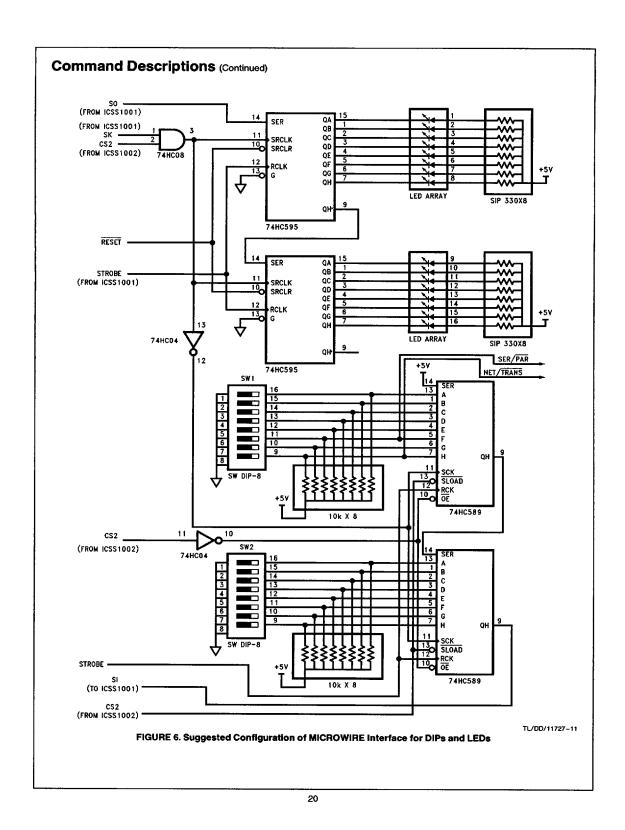

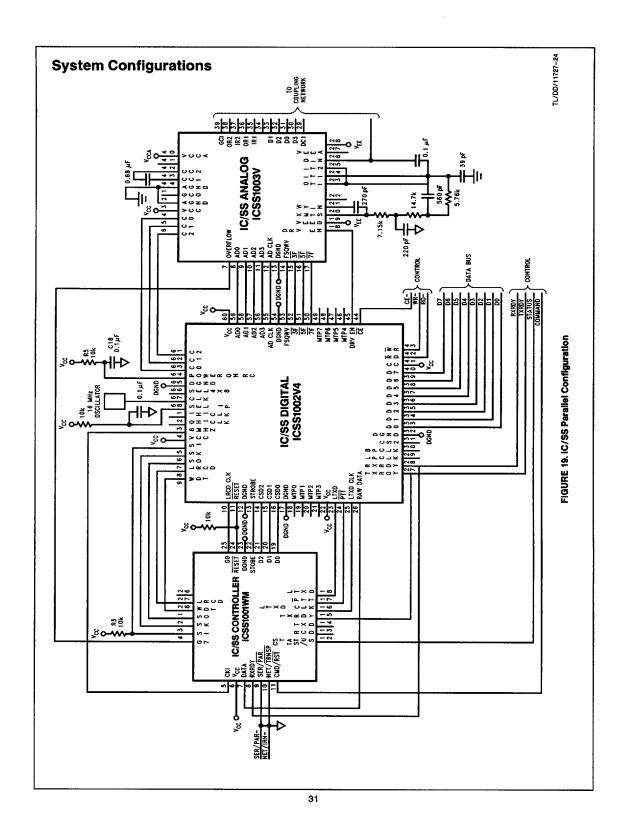

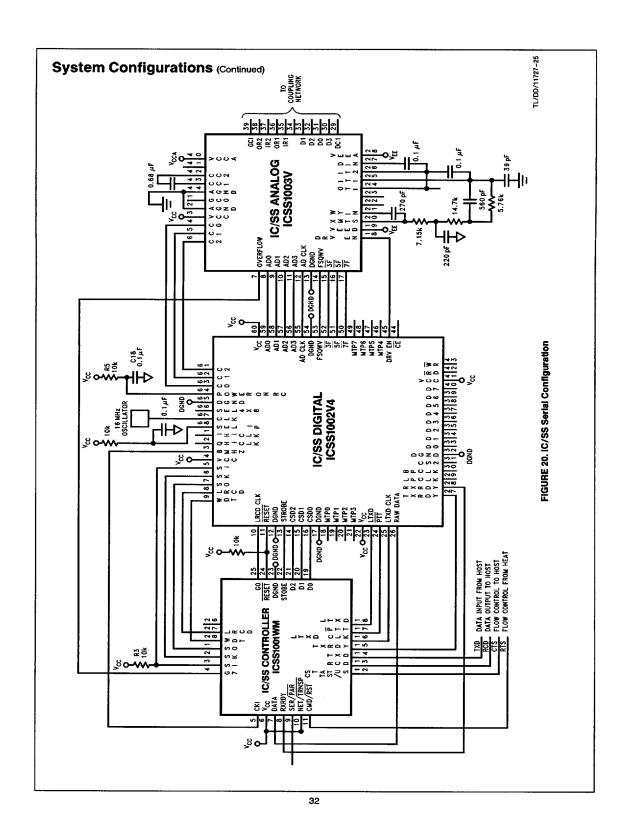

- A very flexible interface to the user's circuit is provided, configurable either to accept serial data or to accept data from an 8-bit parallel bus. Handshake lines are provided to facilitate interface to common microprocessors in parallel mode.

- When used with the specified coupling networks, the modem operates in conformance with both the CENELEC standard for electric utility application (9 kHz-95 kHz), and with FCC Class A requirements.

- Data rate is variable, based on line conditions, from 300 bps to 3200 bps.

- When used with the specified coupling networks, the system provides 93 dB of dynamic range, appropriate for line loading and attenuation effects common on power lines.

- The modem's bit error rate performance in additive white noise approaches the theoretical maximum, and in addition it provides excellent immunity to the impulsive noise characteristic of power lines.

## **Applications**

- Automated meter reading (AMR)

- Demand side management

- Distribution automation

- Environmental control systems

- Other power line carrier applications requiring high reliability

## **Block Diagram** TO HOST DATA RECEIVE CARRIER AD DATA DATA CONTROL AD CLOCK TRANSMIT 8 MHz CLOCK CARRIER I SQUARE WAV ANAL OG POWER LINE COUPLER DIGITAL FILTER AND FILTER, GAIN CONTROL A/D HARMONICS PROTOCOL SELECT SYSTEM CONTROLLER LI[0..6] CONTROL D[0..2] OVERFLOW DRIVER ENABLE MICROWIRE CHIP SET TL/DD/11727-1 TRI-STATE® is a registered trademark of National Se MICROWIRE™ and WATCHDOG™ are trademarks of IC/SS™ is a trademark of Cyplex. are trademarks of National Semiconductor Corpor

©1995 National Semiconductor Corporation

TL/DD11727

RRD-B30M105/Printed in U. S. A.

## **Modem Operation**

A block diagram of the modem is shown on page 1. It includes four major elements:

- 1. Coupling network to the power line.

- 2. Analog filter, gain control, and A/D.

- 3. Digital filter and control logic.

- 4. System controller.

Each of these is described in more detail below.

## **COUPLING NETWORK**

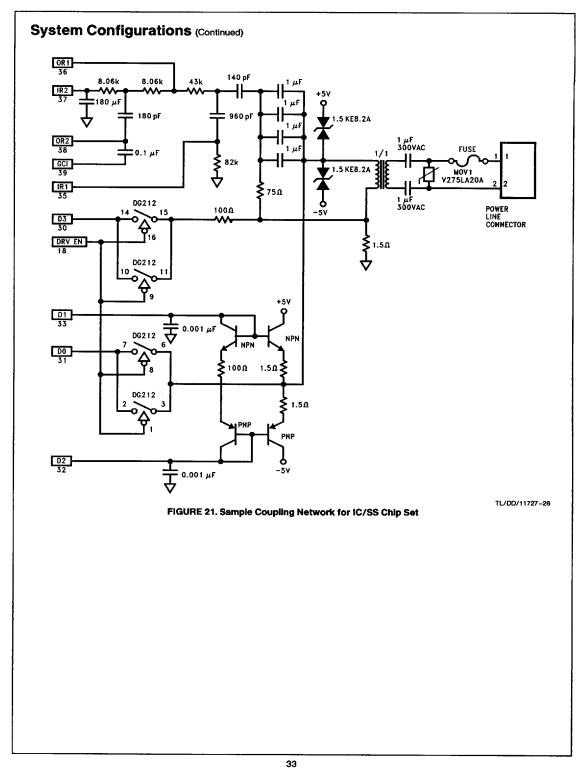

The coupling network provides protection against the AC power line 60 Hz/50 Hz energy, and initial filtering of power line noise. It provides a match of impedances to the power line, and also contains a power amplification stage for the transmitter. A variety of coupling networks are available from Cyplex, suitable for:

220 VAC ungrounded operation (meters and 220 VAC load control).

110 VAC/neutral operation (110 VAC load control).

Three-terminal operation (intended for gateways and master units which must communicate with both of the above).

The coupling networks require  $\pm 5V$  power, ground, and interface to the analog section of the system.

## ICSS1001—Controller

The controller provides the adaptive frequency hopping, the user interface, and link layer protocol.

#### ICSS1002—Digital Chip

The digital section of the system provides additional receive filtering and received signal detection functions. It generates the necessary internal clocks and interface signals to the microcontroller.

## ICSS1003---Analog Chip

The analog section of the system provides receive signal filtering, and also generates the transmit carrier based on control and clock signals from the digital section.

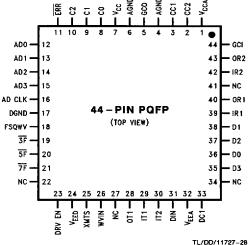

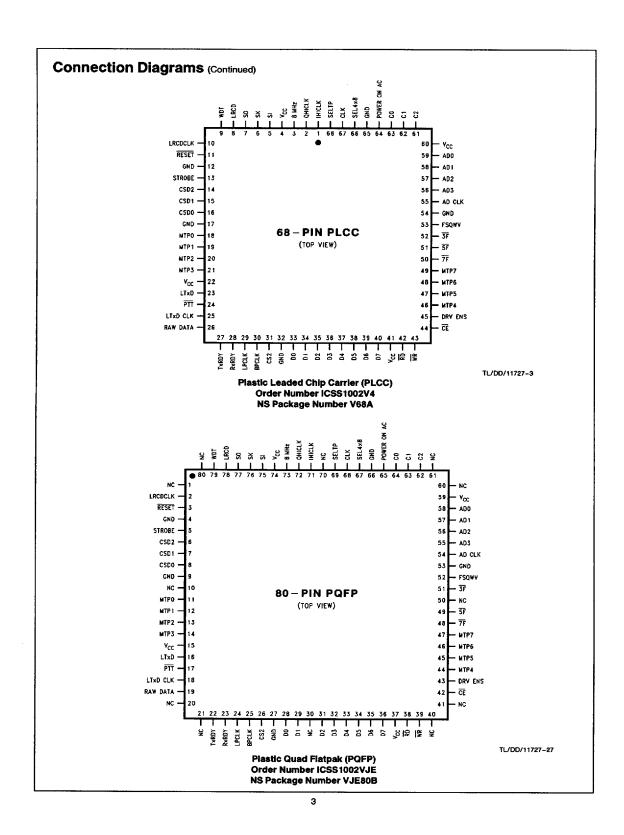

# **Connection Diagrams**

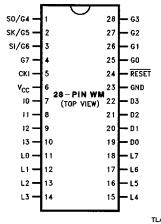

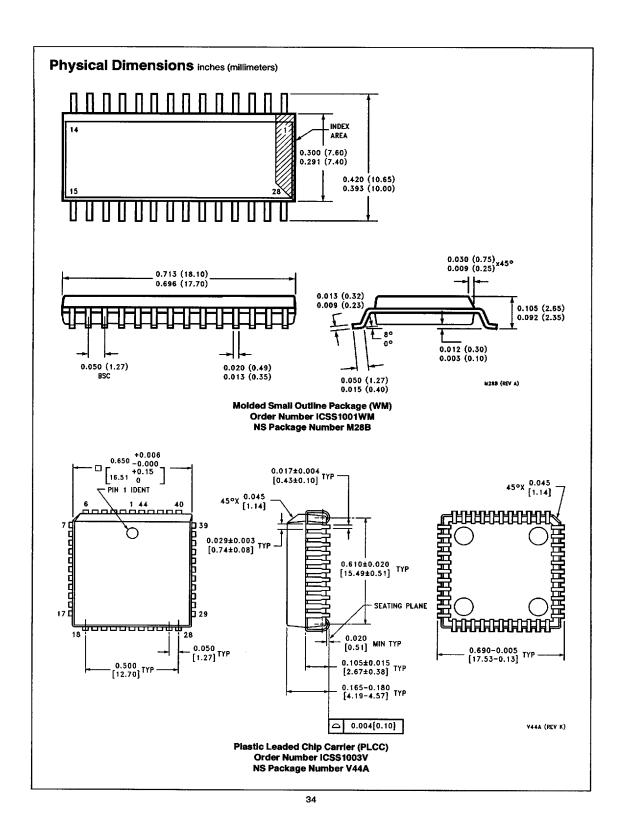

Wide Molded Small Outline Package (WM)

Order Number ICSS1001WM

NS Package Number M28B

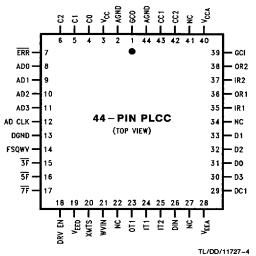

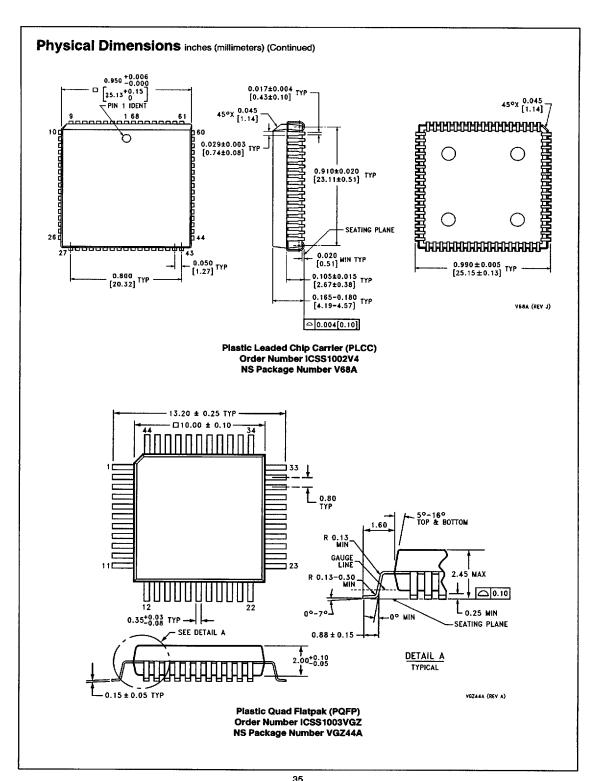

Plastic Leaded Chip Carrier (PLCC) Order Number ICSS1003V NS Package Number V44A

Plastic Quad Flatpak (PQFP) Order Number ICSS1003VGZ NS Package Number VGZ44A

# **Pin Descriptions**

Tables I, II and III describe the various pins that are used for external connections outside of the chip set. These pins are shown in the Connection Diagrams.

Type One of the following:

I Input

Output

T TRI-STATE®

P Power

Function A brief description of each signal's function.

## TABLE I. ICSS1001 Pin Descriptions

| Pin Name        | Pin No. | Type | Function                                                                                                                                                                                                                                                              |

|-----------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SO/G4           | 1       | 0    | MICROWIRE™ SO to digital ASIC                                                                                                                                                                                                                                         |

| SK/G5           | 2       | 0    | MICROWIRE clock to digital ASIC                                                                                                                                                                                                                                       |

| SI/G6           | 3       | 1    | MICROWIRE SI from digital ASIC                                                                                                                                                                                                                                        |

| G7              | 4       | 0    | Overflow of A/D converter from analog ASIC                                                                                                                                                                                                                            |

| CKI             | 5       | 1    | 8 MHz clock input from digital ASIC                                                                                                                                                                                                                                   |

| V <sub>CC</sub> | 6       | Р    | Input power                                                                                                                                                                                                                                                           |

| 10              | 7       | 1    | RAW DATA input from digital ASIC                                                                                                                                                                                                                                      |

| 11              | 8       | 0    | RxRDY handshake line for parallel port                                                                                                                                                                                                                                |

| 12              | 9       | 1    | SER/PAR-input read after reset determines whether firmware will use serial or parallel host port. HIGH = serial                                                                                                                                                       |

| 13              | 10      | 1    | NET/TRN-input read continuously. If HIGH and serial port is selected commands are processed; if LOW, all received characters are treated as transparent data. If parallel port is selected, this pin has no effect.                                                   |

| ГО              | 11      | •    | RTS flow control from host. If serial port is selected (pin 9 = HIGH), LOW enables output of data on RCD and HIGH prevents output on RCD. A byte in the process of being output when RTS goes HIGH will be completed. RTS has no effect if parallel port is selected. |

|                 |         |      | If parallel is selected (pin 9 = LOW), COMMAND HIGH denotes the presence of a command in the parallel port input buffer. LOW denotes the presence of data.                                                                                                            |

| L1              | 12      | 0    | CTS flow control to host. Normally LOW. If serial port is selected (pin 9 = HIGH) then HIGH indicates host should not send data to TXD. A maximum of three bytes will be accepted after a transition from LOW to HIGH.                                                |

| :               |         |      | If parallel port is selected (pin 9 = LOW), then STATUS HIGH denotes that the byte available for the host to read is a status code. A LOW denotes that the available byte is data.                                                                                    |

| L2              | 13      | 0    | RCD receive data output to host, in byte asynchronous format, 8 data bits, parity one start and one stop bit. Active baud rate and parity default is 1200 baud, no parity. Other settings may be selected by DIP switch. Active only if serial port is selected.      |

| L3              | 14      | 1    | TXD transmit data input from host                                                                                                                                                                                                                                     |

| L4              | 15      | 0    | LTXD CLK serial data clock for data to be transmitted by the digital ASIC, not Manchester-<br>encoded                                                                                                                                                                 |

| L5              | 16      | 0    | TxRDY handshake line for parallel port                                                                                                                                                                                                                                |

| L6              | 17      | 0    | PTT Active LOW places digital chip in transmit mode                                                                                                                                                                                                                   |

| L7              | 18      | 0    | LTXD serial data to be transmitted by digital ASIC, not Manchester-encoded. Active HIGH. ASIC Manchester-encodes the data using LTXD CLK.                                                                                                                             |

| D0              | 19      | 0    | CSD digital ASIC internal MICROWIRE register address selection                                                                                                                                                                                                        |

| D1              | 20      | 0    | CSD1 digital ASIC internal MICROWIRE register address selection                                                                                                                                                                                                       |

| D2              | 21      | 0    | CSD2 digital ASIC internal MICROWIRE register address selection                                                                                                                                                                                                       |

| D3              | 22      | 0    | STROBE MICROWIRE output to digital ASIC                                                                                                                                                                                                                               |

| GROUND          | 23      | Р    | Ground                                                                                                                                                                                                                                                                |

| RESET           | 24      | ı    | RESET from digital chip                                                                                                                                                                                                                                               |

# TABLE I. ICSS1001 Pin Descriptions (Continued)

| Pin Name | Pin No. | Туре | Function                                                                                                                                           |

|----------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| G0       | 25      | 1    | LRCD CLK recovered clock from demodulated data input from digital ASIC                                                                             |

| G1       | 26      |      | No connection                                                                                                                                      |

| G2       | 27      | ı    | LRCD recovered data from demodulated data input from digital ASIC, after Manchester decoding                                                       |

| G3       | 28      | 0    | WDT firmware outputs a square wave to digital chip, maintaining a one-shot. If WDT output stops, digital ASIC will force a system reset on pin 24. |

## TABLE II. ICSS1002 Pin Descriptions

| Pin Name  | Pin No.<br>(V Pkg.) | Туре | Function                                                                                                                                                                                                                                     |

|-----------|---------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IHICLK    | 1                   | 0    | Output Test Point: A test point.                                                                                                                                                                                                             |

| QHICLK    | 2                   | 0    | Output Test Point: A test point.                                                                                                                                                                                                             |

| 8 MHz     | 3                   | 0    | 8 MHz Output: This is the CLK divided by 2. This output goes low while RESET is LOW.                                                                                                                                                         |

| SI        | 5                   | Т    | MICROWIRE Serial Input: This pin drives the MICROWIRE SI Input on the controller.                                                                                                                                                            |

| SK        | 6                   | τ    | MICROWIRE Shift Clock: This pin accepts the MICROWIRE shift clock to the Controller interface on the IC/SS digital ASIC.                                                                                                                     |

| so        | 7                   | Т    | MICROWIRE Serial Output: This pin accepts the MICROWIRE serial data to the Controller interface on the IC/SS digital ASIC.                                                                                                                   |

| LRCD      | 8                   | 0    | Recovered Data: This is the serial data received from the power line after Manchester decoding.                                                                                                                                              |

| WDT       | 9                   | Т    | WATCHDOG™ Timer Disable: This input from the controller keeps the digital ASIC active. If it goes away, the digital ASIC will generate RESET pulse after the WATCHDOG timers times out. This RESET pulse will reset the entire PLC chip set. |

| LRCDCLK   | 10                  | 0    | Recovered Clock: This is the clock received from the power line after Manchester decoding.                                                                                                                                                   |

| RESET     | 11                  | _    | Reset: Active LOW reset for the entire IC/SS chip set.                                                                                                                                                                                       |

| STROBE    | 13                  | т    | MICROWIRE Strobe input: This pin accepts the MICROWIRE strobe to the controller interface on the IC/SS digital ASIC.                                                                                                                         |

| CSD2-CSD0 | 14-16               | Т    | Controller Interface Mode Select: These inputs are used to select the operation modes of the controller interface circuitry on the IC/SS digital ASIC.                                                                                       |

| MTP0-MTP3 | 18-21               | 0    | <b>Test Points:</b> These output pins provide access to one of the filter outputs on the detector integration bus.                                                                                                                           |

| LTXD      | 23                  | 0    | Serial Data to be transmitted: This input is the serial data to be transmitted. It is not Manchester encoded.                                                                                                                                |

| PTT       | 24                  | Т    | Push to talk: This is an active low signal that puts the digital ASIC into the transmit mode.                                                                                                                                                |

| LTXD CLK  | 25                  | Т    | Serial Data Transmit Clock: This input is the clock for the serial data (LTXD) that is used to Manchester encode the data prior to transmission.                                                                                             |

| RAW DATA  | 26                  | 0    | Raw Data: This output is the raw data received by the IC/SS circuit after de-multiplex prior to Manchester decode.                                                                                                                           |

| TxRDY     | 27                  | 0    | Transmit Data Ready: When this signal is HIGH the parallel port is ready to accept a new byte from the user data bus.                                                                                                                        |

| RxRDY     | 28                  | 0    | Receive Data Ready: When this signal is HIGH there is a byte available in the parallel port to be read by the user data bus.                                                                                                                 |

| LPCLK     | 29                  | 0    | LPCLK: This is an internal test point.                                                                                                                                                                                                       |

| BPCLK     | 30                  | 0    | BPCLK: This is an internal test point.                                                                                                                                                                                                       |

| CS2       | 31                  | 0    | Chip Select: This is the MICROWIRE chip select output. It is used to enable read/write of external MICROWIRE data ports.                                                                                                                     |

# TABLE II. ICSS1002 Pin Descriptions (Continued)

| Pin Name        | Pin No<br>(V Pkg.)    | Туре | Function                                                                                                                                                                                                            |

|-----------------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7           | 33-40                 | 1/0  | Data Bus: This is the parallel port data bus.                                                                                                                                                                       |

| RD              | 42                    | т    | Read: This is the parallel port read control. Used with Chip Enable it allows the parallel port to be read.                                                                                                         |

| WR              | 43                    | Т    | Write: This is the parallel port write control. Used with Chip Enable it allows the parallel port to be written.                                                                                                    |

| CE              | 44                    | Т    | Chip Enable: This is the parallel port enable to read or write. It is active low.                                                                                                                                   |

| DRV EN          | 45                    | 0    | Drive Enable: This is the transmit enable signal used by the Analog chip to disable the receiver mode and enable the transmitter mode                                                                               |

| MTP4-MTP7       | 46–49                 | 0    | Test Points: These output pins provide access to one of the filter outputs of the detector integration bus                                                                                                          |

| 7F              | 50                    | 0    | Seventh Harmonic Overtone Cancellation Signal: This is the seventh harmonic overtone cancellation signal used to convert FSQWV to a sine wave in the Analog chip D/A                                                |

| 5F              | 51                    | 0    | Fifth Harmonic Overtone Cancellation Signal: This is the fifth harmonic overtone cancellation signal used to convert FSQWV to a sine wave in the Analog chip D/A                                                    |

| 3F              | 52                    | 0    | Third Harmonic Overtone Cancellation Signal: This is the Third harmonic overtone cancellation signal used to convert FSQWV to a sine wave in the Analog chip D/A                                                    |

| FSQWV           | 53                    | 0    | Square Wave Transmit Signal: This is the Manchester-encoded frequency mixed signal, ready for transmission to the power line                                                                                        |

| AD CLK          | 55                    | 0    | A/D Clock: This is the clock for the Analog chip AID converter. It is used to latch the AD output. It is the A/D sample rate. This is the CLK divided by 16. This output goes HIGH while RESET is LOW.              |

| AD3-AD0         | 56-59                 | Т    | Received Data: These pins are the digital four bit bus from the Analog chip which contains the ones complement A/D converted signal from the power line                                                             |

| C2-C0           | 61-63                 | 0    | Analog Gain Control: These signals are used to set the gain of the Analog chip gain controlled amplifier                                                                                                            |

| Power on AC     | 64                    | 0    | Power on Reset RC Node: This is the power on reset Resistor/Capacitor connect point. An external RC network charges up to the gate threshold to release the RESET signal. When this pin is LOW the RESET is active. |

| SEL4X8          | 66                    | т    | Select 4X or 8X: This is the select line used to set the digital filter clock sample rate                                                                                                                           |

| CLK             | 67                    | Т    | Clock: This is the 16 MHz clock input                                                                                                                                                                               |

| SEL TP          | 68                    | Т    | Select Test Points: This signal selects which internal nodes are brought out on the Test Point Bus and whether Raw Data is inverted or not                                                                          |

| V <sub>CC</sub> | 4, 22, 41, 60         | Р    | V <sub>CC</sub> : These are positive voltage power supply pins to the part                                                                                                                                          |

| GND             | 12, 17, 32,<br>54, 65 | Р    | GND: These are the negative (or 0V) power supply pins to the part                                                                                                                                                   |

## TABLE III. ICSS1003 Pin Descriptions

| Pin Name | Pin No.<br>(V Pkg.) | Туре | Function                                                                                                                                                                 |

|----------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCO      | 1                   |      | Gain Control Amplifier Test Point: A test point to monitor the gain of the gain amplifier                                                                                |

| AGND     | 2                   | Р    | Analog Ground: The ground reference pin for the gain control amplifier                                                                                                   |

| Vcc      | 3                   | P    | Digital Positive Power Supply Pin: The V <sub>CC</sub> pin for the digital portion of the ASIC                                                                           |

| C0-C2    | 4-6                 | ı    | Gain Control Amplifier Gain Setting: These pins set the gain of the gain control amplifier. These signals are generated by the digital ASIC.                             |

| ERR      | 7                   | 0    | A/D Overflow Signal: This signal goes HIGH if the Analog signal from the gain control amplifier to the Analog to Digital Converter is being clipped by the A/D converter |

# TABLE III. ICSS1003 Pin Descriptions (Continued)

| Pin Name   | Pin No.<br>(V Pkg.) | Туре | Function                                                                                                                                                                                                                                         |

|------------|---------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0-AD3    | 8-11                | 0    | A/D Digital Output: These signals are the ones complement digital output of the signal received from the power line. It is the output of the flash A/D sampled at the AD CLK rate.                                                               |

| AD CLK     | 12                  | ı    | Clock For The Flash A/D Converter: This is the clock used by the A/D converter to sample the signal received from the power line. It is normally 1 MHz and is generated by the digital ASIC.                                                     |

| DGND       | 13                  | Р    | Digital Ground Power Supply Pin: This is the ground (0V) power supply for the digital portion of the ASIC                                                                                                                                        |

| FSQWV      | 14                  | 1    | Square Wave Transmit Signal: This is the Manchester-encoded, frequency mixed signal                                                                                                                                                              |

| 3F         | 15                  | I    | Third Harmonic Overtone Cancellation Signal: This is the third harmonic overtone cancellation signal used to convert FSQWV to a sine wave in the Analog chip D/A                                                                                 |

| 5F         | 16                  | _    | Fifth Harmonic: Overtone Cancellation Signal: This is the fifth harmonic overtone cancellation signal used to convert FSQWV to a sine wave in the Analog chip D/A                                                                                |

| 7 <b>F</b> | 17                  | ı    | Seventh Harmonic: Overtone Cancellation Signal: This is the seventh harmonic overtone cancellation signal used to convert FSQWV to a sine wave in the Analog chip D/A                                                                            |

| DRV EN     | 18                  | ı    | <b>Drive Enable:</b> This is the transmit enable signal used by the Analog chip to disable the receiver mode and enable the transmitter mode                                                                                                     |

| VEED       | 19                  | Р    | Digital Negative Power Supply Pin: This is the negative (-5V) power supply for the digital portion of the ASIC                                                                                                                                   |

| XMTS       | 20                  | 0    | Digital To Analog Converter Integrator Output: This is the analog output of the D/A converter integrator                                                                                                                                         |

| WVIN       | 21                  |      | Digital To Analog Converter Integrator Input: This is the analog input of the D/A converter integrator. It is connected internally to the D/A converter output. It is used to connect the external integrator capacitor to the integrator input. |

| OT1        | 23                  | 0    | Amplifier Output: Buffer amplifier between the D/A converter and the power driver amplifie output                                                                                                                                                |

| IT1        | 24                  | F    | Amplifier Positive input: Buffer amplifier between the D/A converter and the power driver amplifier positive input                                                                                                                               |

| IT2        | 25                  | I    | Amplifier Negative Input: Buffer amplifier between the D/A converter and the power driver amplifier negative input                                                                                                                               |

| DIN        | 26                  | 1    | Power Amplifier Input: This is the power amplifier input                                                                                                                                                                                         |

| VEEA       | 28                  | Р    | Analog Negative Power Supply Pin: This is the negative ( $-5V$ ) power supply for the analoportion of the ASIC                                                                                                                                   |

| DC1        | 29                  | 0    | Power Amplifier Divided Input: This is the power amplifier resistor divided input                                                                                                                                                                |

| D3         | 30                  | 1    | Power Amplifier Feedback Input: This is one of the switched power amplifier feedback points                                                                                                                                                      |

| D0         | 31                  | 1    | Power Amplifier Feedback Input: This is one of the switched power amplifier feedback points                                                                                                                                                      |

| D2         | 32                  | 0    | Power Amplifier Negative Output: This is the power amplifier negative output driver output                                                                                                                                                       |

| D1         | 33                  | 0    | Power Amplifler Positive Output: This is the power amplifier positive output driver output                                                                                                                                                       |

| IR1        | 35                  | 0    | Unity Gain Amplifier Input: First stage receiver filter input                                                                                                                                                                                    |

| OR1        | 36                  | 0    | Unity Gain Amplifier Output: First stage receiver filter output                                                                                                                                                                                  |

| IR2        | 37                  | 1    | Unity Gain Amplifier Input: Second stage receiver filter input                                                                                                                                                                                   |

## TABLE III. ICSS1003 Pin Descriptions (Continued)

| Pin Name          | Pin No.<br>(V Pkg.) | Туре | Function                                                                                                                                 |

|-------------------|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| IR2               | 38                  | 0    | Unity Gain Amplifier Output: Second stage receiver filter output                                                                         |

| GCI               | 39                  | 1    | Gain Control Amplifier Input: This is the gain control amplifier input                                                                   |

| V <sub>CC</sub> A | 40                  | Р    | Analog Positive Power Supply Pin: The V <sub>CC</sub> pin for the analog portion of the ASIC                                             |

| CC2               | 42                  |      | Gain Control Amplifier Offset Compensation Input: This is the gain control amplifier offset compensation input capacitor connect point   |

| CC1               | 43                  |      | Gain Control Amplifier Offset Compensation Output: This is the gain control amplifier offset compensation output capacitor connect point |

| AGND              | 44                  |      | Analog Gain Control: This is the ground (0V) power supply for the analog portion of the ASIC                                             |

| NC                | 22, 27, 34, 41      |      | No Connect: These pins are not connected                                                                                                 |

7V

100 mA

110 mA

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage

Total Current into V<sub>CC</sub> Pin (Source)

Total Current out of GND Pin (Sink)

Storage Temperature Range

-65°C to +150°C

Note: Absolute maximum ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.

# ICSS1001 DC Electrical Characteristics ( $-40^{\circ}C \le T_{A} \le +85^{\circ}C$ )

| Parameter                                                                                                                                 | Conditions                                                         | Min                 | Тур                  | Max                        | Units    |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------|----------------------|----------------------------|----------|

| Operating Voltage Power Supply Ripple (Note 1)                                                                                            | Peak to Peak                                                       | 2.5                 |                      | 5.5<br>0.1 V <sub>CC</sub> | v        |

| Supply Current<br>CKI = 10 MHz (Note 2)<br>CKI = 4 MHz                                                                                    | $V_{CC} = 6V, t_C = 1 \mu s$<br>$V_{CC} = 2.5V, t_C = 2.5 \mu s$   |                     |                      | 15<br>2                    | mA       |

| HALT (Note 3)                                                                                                                             | $V_{CC} = 6V, CKI = 0 MHz$                                         |                     | <1                   | 10                         | μΑ       |

| IDLE<br>CKI = 10 MHz<br>CKI = 4 MHz                                                                                                       | $V_{CC} = 6V, t_C = 1 \mu s$<br>$V_{CC} = 2.5V, t_C = 2.5 \mu s$   |                     |                      | 2.2<br>0.6                 | mA<br>mA |

| Input Levels (V <sub>IH</sub> , V <sub>IL</sub> )<br>Reset, CKI<br>Logic HIGH<br>Logic LOW<br>All Other Inputs<br>Logic HIGH<br>Logic LOW |                                                                    | 0.8 V <sub>CC</sub> |                      | 0.2 V <sub>CC</sub>        | ٧        |

| Hi-Z Input Leakage Input Pull-Up Current                                                                                                  | V <sub>CC</sub> = 6V<br>V <sub>CC</sub> = 6V, V <sub>IN</sub> = 0V | -2<br>40            |                      | +2<br>250                  | μΑ       |

| G Port Input Hysteresis                                                                                                                   | (Note 6)                                                           |                     | 0.05 V <sub>CC</sub> | 0.35 V <sub>CC</sub>       | V        |

| Parameter                                      | Conditions                     | Min  | Тур | Max   | Units |

|------------------------------------------------|--------------------------------|------|-----|-------|-------|

| Output Current Levels                          |                                |      |     |       |       |

| D Outputs                                      |                                |      |     |       |       |

| Source                                         | $V_{CC} = 4.0V, V_{OH} = 3.3V$ | 0.4  |     |       | mA    |

| $V_{CC} = 2.5V, V_{OH} = 1.8V$                 |                                | 0.2  |     |       | mA    |

| Sink                                           | $V_{CC} = 4.0V, V_{OL} = 1.0V$ | 10   |     |       | mA    |

| $V_{CC} = 2.5V, V_{OL} = 0.4V$                 |                                | 0.2  |     |       | mA    |

| All Others                                     | 1                              |      |     |       |       |

| Source (Weak Pull-Up)                          | $V_{CC} = 4.0V, V_{OH} = 2.7V$ | 10   |     | 110   | μΑ    |

| $V_{CC} = 2.5V, V_{OH} = 1.8V$                 |                                | 2.5  |     | 33    | μΑ    |

| Source (Push-Pull)                             | $V_{CC} = 4.0V, V_{OH} = 3.3V$ | 0.4  |     |       | mA    |

| $V_{CC} = 2.5V, V_{OH} = 1.8V$                 | <u> </u>                       | 0.2  |     |       | mA    |

| Sink (Push-Pull)                               | $V_{CC} = 4.0V, V_{OL} = 0.4V$ | 1.6  |     |       | mA    |

| $V_{CC} = 2.5V, V_{OL} = 0.4V$                 |                                | 0.7  |     |       | mA    |

| TRI-STATE Leakage                              | $V_{CC} = 6.0V$                | -2.0 |     | + 2.0 | μА    |

| Allowable Sink/Source Current per Pin          | i                              |      |     |       |       |

| D Outputs (Sink)                               |                                |      |     | 15    | ١.    |

| All Other                                      |                                |      |     | 3     | mA    |

| Maximum Input Current without Latchup          | Room Temp                      |      |     |       |       |

| (Notes 4, 6)                                   | <u> </u>                       |      |     | ± 100 | mA    |

| RAM Retention Voltage, V <sub>R</sub> (Note 5) | 500 ns Rise and Fall Time      | 2.0  |     |       | ٧     |

| Input Capacitance                              | (Note 6)                       |      |     | 7     | pF    |

| Load Capacitance                               | (Note 6)                       |      |     | 1000  | ρF    |

Note 1: Maximum rate of voltage change must be less than 0.5V/ms.

Note 3: The HALT mode will stop CKI from oscillating in the RC and the Crystal configurations. HALT test conditions: all inputs tied to V<sub>CC</sub>; L and G port I/Os configured as outputs and programmed low; D outputs programmed low. Parameter refers to HALT mode entered via setting bit 7 of the G Port data register. Part will pull up CKI during HALT in crystal clock mode.

Note 4: Pins G6 and RESET are designed with a high voltage input network. These pins allow input voltages greater than V<sub>CC</sub> and the pins will have sink current to V<sub>CC</sub> when biased at voltages greater than V<sub>CC</sub> (the pins do not have source current when biased at a voltage below V<sub>CC</sub>). The effective resistance to V<sub>CC</sub> is 750Ω (typical). These two pins will not latch up. The voltage at the pins must be limited to less than 14V. Voltages in excess of 14V will cause damage to the pins. This excludes ESD transients.

Note 5: Condition and parameter valid only for part in HALT mode.

Note 6: Parameter characterized but not tested.

Note 2: Supply current is measured after running 2000 cycles with a square wave CKI input, CKO open, inputs at rails, and outputs open.

| Symbol                                 | Parameter                                   | Conditions                   | Min          | Тур | Max                   | Units          |

|----------------------------------------|---------------------------------------------|------------------------------|--------------|-----|-----------------------|----------------|

| (t <sub>c</sub> )                      | Instruction Cycle Time                      |                              |              |     |                       |                |

|                                        | Crystal/Resonator                           | V <sub>CC</sub> ≥ 4.0V       | 1.0          |     | DC DC DC DC 0.7 1 2.5 |                |

|                                        |                                             | 2.5 ≤ V <sub>CC</sub> ≤ 4.0V | 2.5          |     |                       | μs             |

|                                        | R/C Oscillator                              | V <sub>CC</sub> ≥ 4.0V       | 3.0          |     | - '                   | ,,,,           |

|                                        |                                             | 2.5 ≤ V <sub>CC</sub> ≤ 4.0V | 7.5          |     | DC                    |                |

|                                        | CKI Clock Duty Cycle (Note 1)               | f = Max                      | 40           |     | 60                    | %              |

| t <sub>SETUP</sub>                     | Inputs                                      |                              |              |     |                       |                |

| tHOLD .                                |                                             | V <sub>CC</sub> ≥ 4.5V       | 200          |     |                       |                |

|                                        |                                             | 2.5 ≤ V <sub>CC</sub> ≤ 4.0V | 500          | ŀ   | i l                   | ns             |

|                                        |                                             | V <sub>CC</sub> ≥ 4.5V       | 60           |     |                       |                |

|                                        |                                             | 2.5 ≤ V <sub>CC</sub> ≤ 4.0V | 150          |     |                       | ns             |

| (t <sub>PD1</sub> , t <sub>PD0</sub> ) | Output Propagation Delay                    | $C_L = 100  pF, R_L = 2.2k$  |              |     |                       |                |

|                                        | SK, SO                                      | V <sub>CC</sub> ≥ 4.5V       | ŀ            | 0.7 |                       |                |

|                                        |                                             | 2.5 ≤ V <sub>CC</sub> ≤ 4.0V | ļ            |     |                       | μS             |

|                                        | All Others                                  | V <sub>CC</sub> ≥ 4.5V       |              | 1   |                       | •              |

|                                        |                                             | 2.5 ≤ V <sub>CC</sub> ≤ 4.0V | -            |     | 1                     |                |

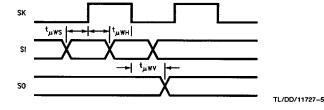

| (tuws)                                 | MICROWIRE                                   |                              |              |     |                       |                |

| (t <sub>UWH</sub> )                    | Setup Time (Note 1)                         |                              | 20           |     |                       |                |

| (t <sub>UPD</sub> )                    | Hold Time (Note 1) Output Propagation Delay |                              | 56           |     | 220                   | ns             |

|                                        |                                             |                              | ļ            |     | 220                   |                |

|                                        | Input Pulse Width (Note 2)                  |                              | ١.,          |     |                       |                |

|                                        | Interrupt High Time Interrupt Low Time      |                              | 1 1          |     |                       |                |

|                                        | Timer 1, 2 High Time                        | ŀ                            | 1 1          |     |                       | t <sub>c</sub> |

|                                        | Timer 1, 2 Low Time                         |                              |              |     |                       |                |

|                                        |                                             |                              | <del> </del> |     |                       |                |

|                                        | Reset Pulse Width (Note 1)                  | İ                            | 1.0          | ı   |                       | μs             |

Note 1: Parameter characterized but not tested. Note 2:  $t_{\rm c} =$  Instruction Cycle Time.

## **ICSS1002 DC Electrical Characteristics**

Specified at  $V_{CC} = 5V \pm 10\%$ ,  $V_{SS} = GND$ , over all temperature ranges unless otherwise specified.

| Symbol           | Parameter                                                                                                          | Conditions                                                              | Min                | Тур | Max        | Units |

|------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------|-----|------------|-------|

| V <sub>IL</sub>  | Low Level Input Voltage (Note 1)<br>TTL Level                                                                      | V <sub>CC</sub> = 4.5V                                                  |                    |     | 0.8        | V     |

| V <sub>IH</sub>  | High Level Input Voltage (Note 1) TTL Level                                                                        | V <sub>CC</sub> = 5.5V                                                  | 2.0                |     |            | ٧     |

| V <sub>T+</sub>  | Positive-Going Threshold Voltage—Schmitt Trigger (Note 1)                                                          | V <sub>CC</sub> = 5.5V                                                  |                    |     | 3.9        | ٧     |

| V <sub>T</sub> - | Negative-Going Threshold Voltage—Schmitt Trigger (Note 1)                                                          | V <sub>CC</sub> = 5.5V                                                  | 1.0                |     |            | ٧     |

| V <sub>H</sub>   | Hysteresis Voltage—Schmitt Trigger (Note 1)                                                                        | V <sub>CC</sub> = 5.5V                                                  | 1.0                | 1.6 |            | ٧     |

| I <sub>IL</sub>  | Low Level Input Leakage Current<br>Without Pull-Down Resistor<br>With Pull-Up Resistor<br>With Pull-Down Resistor  | $V_{IN} = GND, V_{CC} = 5.5V$                                           | -10<br>-200<br>-10 |     |            | μΑ    |

| ļΗ               | High Level Input Leakage Current<br>Without Pull-Down Resistor<br>With Pull-Up Resistor<br>With Pull-Down Resistor | $V_{IN} = V_{CC} = 5.5V$                                                | 10<br>10<br>200    |     |            | μА    |

| V <sub>OL</sub>  | Low Level Output Voltage<br>Reset                                                                                  | $I_{OL} = 4$ mA, $V_{CC} = 4.5$ V<br>$I_{OL} = 12$ mA, $V_{CC} = 4.5$ V |                    |     | 0.5<br>0.5 | ٧     |

| V <sub>OH</sub>  | High Level Output Voltage                                                                                          | $I_{OL} = -4 \text{ mA}, V_{CC} = 4.5 \text{V}$                         | 3.7                |     |            | ٧     |

| lozL             | Low Level Output Leakage Current (Note 2)                                                                          | $V_O = GND, V_{CC} = 5.5V$<br>$V_{IN} = V_{IL}$                         | -160               |     |            | μА    |

| lozн             | High Level Output Leakage Current (Note 2)                                                                         | $V_O = V_{CC} = 5.5V$<br>$V_{IN} = V_{IL}$                              |                    |     | 160        | μА    |

| loc              | Power Supply Current Drain, DC (Note 3)                                                                            | V <sub>CC</sub> = 5.5V                                                  |                    |     | 1          | mA    |

| C <sub>IN</sub>  | Input Capacitance (Note 1)                                                                                         |                                                                         |                    |     | 20         | pF    |

| COUT             | Output Capacitance (Note 1)                                                                                        |                                                                         |                    |     | 20         | pF    |

Note 1: Specification is guaranteed by design. This test cannot be performed unless a hook-up to a special output is defined.

Note 2: IOZ specifications are for output buffers without pull-up or pull-down resistors.

Note 3: DC means at power on with CLK and POWER ON RC inputs low, all other signal pins open.

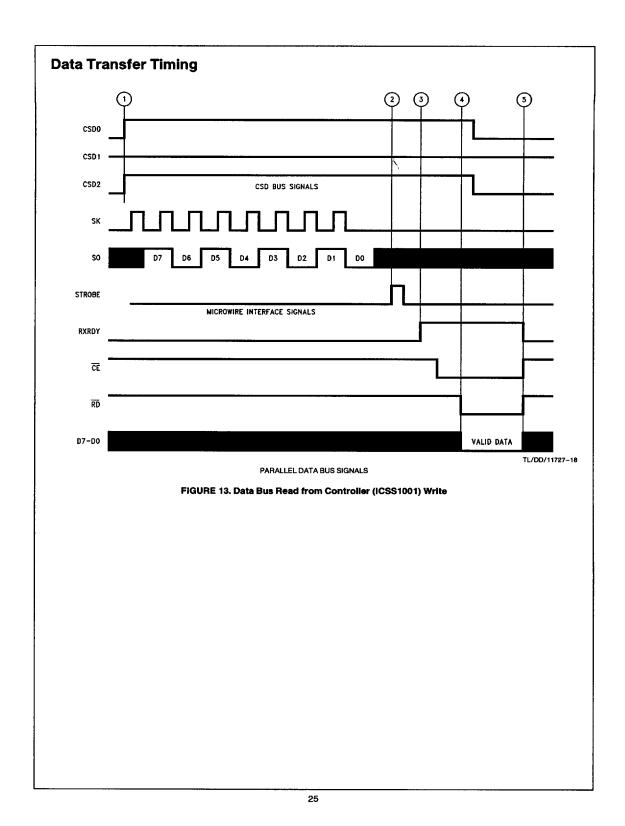

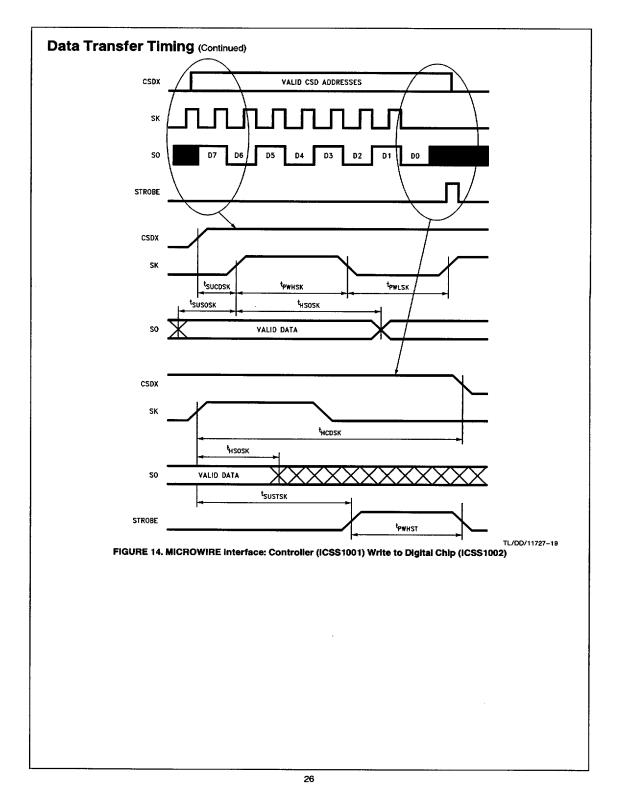

## **ICSS1002 AC Electrical Characteristics**

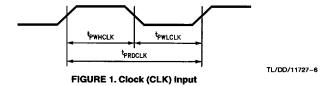

The AC Electrical Characteristics for the ICSS1002 are not measured. They are guaranteed by design, unless otherwise noted. The CLK input should be a 16 MHz signal with a period of 62.5 ns and with tpwLCLK and tpwHCLK of 31.25 ns 6.25 ns. This is equivalent to requiring a 50% 10% duty cycle on the CLK input. See *Figure 2*.

## 8 MHz Output

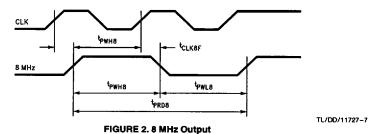

With a 16 MHz input on CLK, the 8 MHz output will be an 8 MHz square wave with a tpRD8 of 125 ns and with tpWH8 and tpWL8 of 62.5 ns. The 8 MHz signal will transition on rising edges of the CLK signal.

## **AD CLK Output**

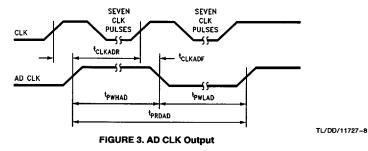

With a 16 MHz input on CLK, the AD CLK output will be a 1.0 MHz square wave with a tpRDAD of 1.0 ms and with tpWHAD and tpWLAD of 0.5 ms. The AD CLK signal will transition on rising edges of the CLK signal.

# ICSS1002 AC Electrical Characteristics (Continued)

All specifications guaranteed by simulation.

| Symbol  | Parameter                                        | Conditions | Min | Тур   | Max  | Units |

|---------|--------------------------------------------------|------------|-----|-------|------|-------|

| TPRDCLK | CLK Period                                       |            |     | 62.5  |      | ns    |

| TPWLCLK | CLK Pulse Width Low                              |            | 25  | 31.25 | 37.5 | ns    |

| TPWHCLK | CLK Pulse Width High                             |            | 25  | 31.25 | 37.5 | ns    |

| TPRD8   | 8 MHz Period                                     |            |     | 125   |      | ns    |

| TPWL8   | 8 MHz Pulse Width Low                            |            |     | 62.5  |      | ns    |

| TPWH8   | 8 MHz Pulse Width High                           |            |     | 62.5  |      | ns    |

| TPWK8R  | Propagation Delay CLK to 8 MHz Going High        |            |     |       | 30   | ns    |

| TCLLK8L | Propagation Delay CLK to 8 MHz Going Low         |            |     |       | 30   | ns    |

| TPRDAD  | AD CLK Period                                    |            |     | 1000  |      | ns    |

| TPWLAD  | AD CLK Pulse Width Low                           |            |     | 500   |      | ns    |

| TPWHAD  | AD CLK Pulse Width High                          |            |     | 500   |      | ns    |

| TCLKADR | Propagation Delay CLK to AD CLK Going High       |            |     |       | 40   | ns    |

| TCLKADL | Propagation Delay CLK to AD CLK Going Low        |            |     |       | 40   | ns    |

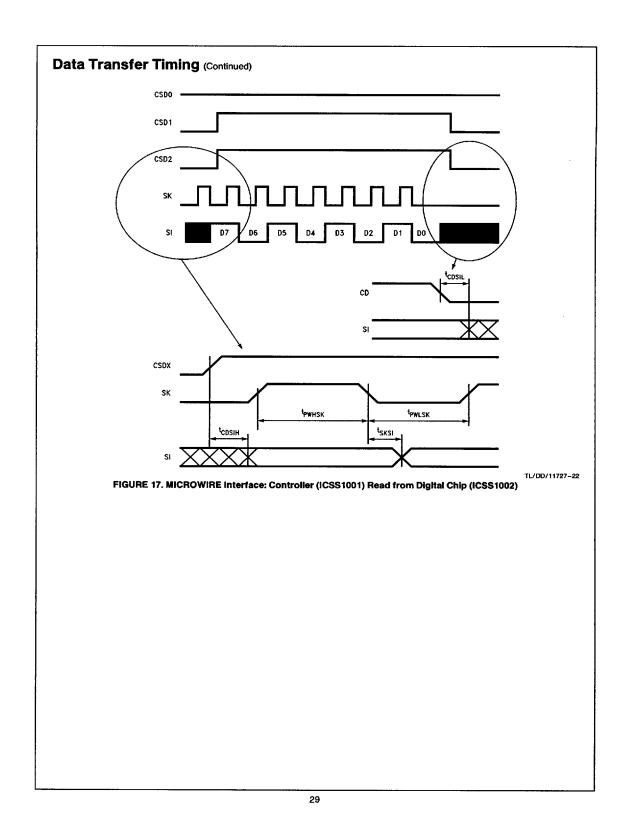

| TCKSIH  | Propagation Delay CSD Bus Valid to SI Valid      |            |     |       | 30   | ns    |

| TSKSI   | Propagation Delay SK Going Low to SI Next Value  |            |     |       | 30   | ns    |

| TPWHSK  | Minimum Pulse Width High for SK                  |            | 50  |       |      | ns    |

| TPWLSK  | Minimum Pulse Width Low for SK                   |            | 50  |       |      | ns    |

| TCDSIL  | Propagation Delay CSD Bus Low to SI TRI-STATE    |            |     |       | 40   | ns    |

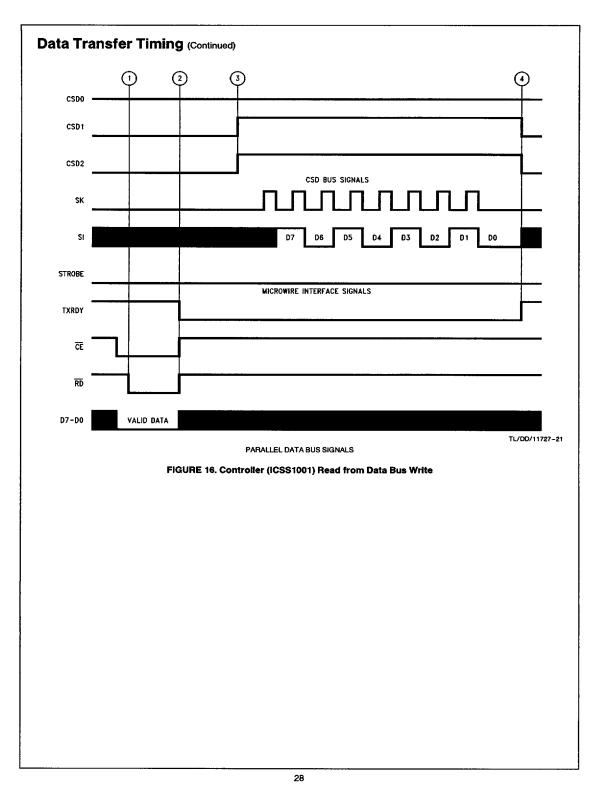

| TSUCDSK | Setup of CSD Bus Valid to SK Going High          |            | 20  |       |      | ns    |

| TSUSOSK | Setup of SO Valid Data to SK Going High          |            | 20  |       |      | ns    |

| THSOSK  | Hold of SO Valid Data after SK Going High        |            | 20  |       |      | ns    |

| THCDSK  | Hold of CSD Bus Valid after SK Going High        |            | 20  |       |      | ns    |

| TSUSTSK | Setup of SK Going High to STROBE Going High      |            | 50  |       |      | ns    |

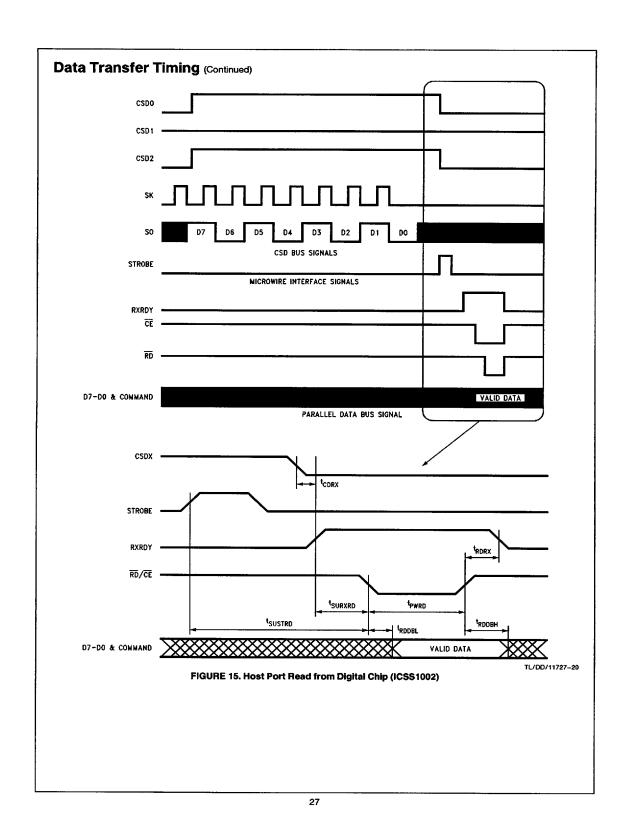

| TCDRX   | Propagation Delay CSD Bus Low to RXRDY High      |            |     |       | 30   | ns    |

| TSURXRD | Setup of RXRDY Going High to RD Going Low        |            | 20  |       |      | ns    |

| TSUSTRD | Setup of STROBE Going High to RD Going Low       |            | 20  |       |      | ns    |

| TRDRX   | Propagation Delay RD High to RXRDY High          |            |     |       | 30   | ns    |

| TRDDBL  | Propagation Delay RD Going Low to Data Bus Valid |            |     |       | 30   | ns    |

| TRDDBH  | Prop. Delay RD Going High to Data Bus TRI-STATE  |            |     |       | 30   | ns    |

| TPWRD   | Minimum Pulse Width Low for RD                   |            | 50  |       |      | ns    |

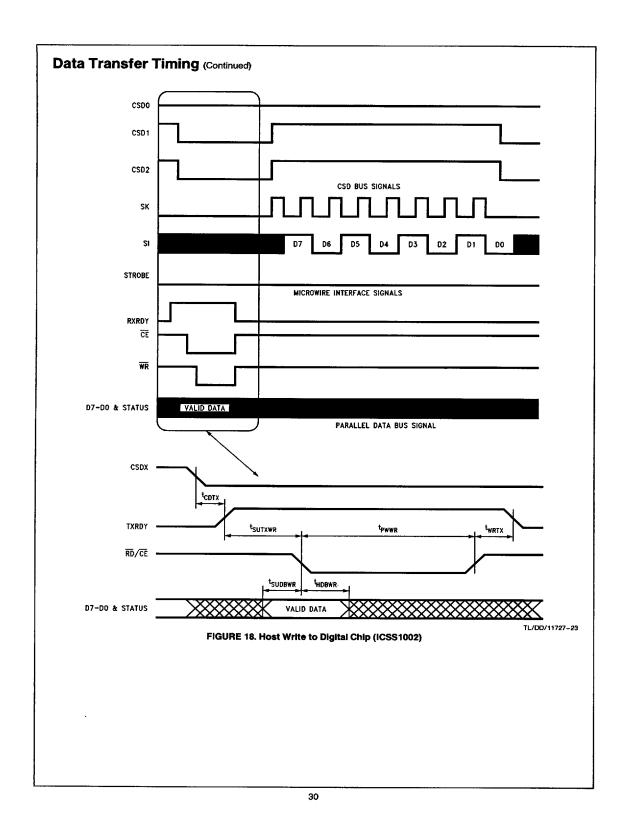

| TCDTX   | Propagation Delay CSD Bus Low to TXRDY High      |            | ļ.  |       | 30   | ns    |

| TSUTXWR | Setup of TXRDY Going High to WR Going Low        |            | 20  |       |      | ns    |

| TSUDBWR | Setup of Data Bus Valid to WR Going Low          |            | 20  |       |      | กร    |

| TWRTX   | Propagation Delay WR High to TXRDY Low           |            |     |       | 30   | ns    |

| THDBWR  | Hold of Data Bus Valid after WR Going Low        |            | 20  |       |      | ns    |

| TPWWR   | Minimum Pulse Width Low for WR                   |            | 50  |       |      | ns    |

| Symbol            | Parameter                                                          | Conditions                                  | Min   | Тур | Max  | Units |

|-------------------|--------------------------------------------------------------------|---------------------------------------------|-------|-----|------|-------|

| lн                | Input Leakage Current High                                         | $V_{IN} = V_{CC} = 5V, V_{EE} = -5V$        |       |     | 10   | μА    |

| l <sub>IL</sub>   | Input Leakage Current Low                                          | $V_{IN} = 0V, V_{CC} = 5V, V_{EE} = -5V$    |       | -10 |      | μА    |

| $V_{IL}$          | Input Low Voltage, TTL Input                                       | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V |       |     | 0.8  | V     |

| $V_{IH}$          | Input High Voltage, TTL Input                                      | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V | 2.0   |     |      | ٧     |

| V <sub>OL</sub>   | Output Low Voltage                                                 | $I_{OL} = 2 \text{ mA}, V_{CC} = 5V$        |       |     | 0.5  | ٧     |

| V <sub>OH</sub>   | Output High Voltage                                                | $l_{OH} = -400 \mu\text{A}, V_{CC} = 5V$    | 2.4   |     |      | ٧     |

| V <sub>OSF</sub>  | Filter Operational Amplifier Offset Voltage                        | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V | -10   |     | 10   | mV    |

| V <sub>OSG</sub>  | Gain Control Amplifier Offset Voltage                              | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V | -20   |     | 20   | mV    |

| IB                | Gain Control Filter Input Bias Current                             | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V | -5    |     | 5    | μА    |

| V <sub>SWP</sub>  | Minimum Output Voltage Swing Positive                              | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V | 2.5   |     |      | ٧     |

| V <sub>SWN</sub>  | Minimum Output Voltage Swing Negative                              | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V |       |     | ~2.5 | ٧     |

| V <sub>SWPD</sub> | Minimum Output Voltage Swing Positive:<br>Driver D1 and D2 Outputs | $V_{CC} = 5V$ , $V_{EE} = -5V$              | 4.0   |     | -    | v     |

| V <sub>SWND</sub> | Minimum Output Voltage Swing Negative:<br>Driver D1 and D2 Outputs | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V | 4     |     |      | ٧     |

| IOUTP             | Minimum Output Current Drive Positive:<br>Driver D1 and D2 Outputs | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V | 30    |     |      | mA    |

| IOUTN             | Minimum Output Current Drive Negative:<br>Driver D1 and D2 Outputs | V <sub>CC</sub> = 5V, V <sub>EE</sub> = -5V |       |     | -30  | mA    |

| lcc               | Positive Power Supply Current (Note 1)                             | V <sub>CC</sub> = 5V                        |       |     | 100  | mA    |

| I <sub>EE</sub>   | Negative Power Supply Current (Note 2)                             | V <sub>CC</sub> = 5V                        | - 100 |     |      | mA    |

| C <sub>IN</sub>   | Input Capacitance (Note 3)                                         |                                             |       |     | 20   | pf    |

| C <sub>OUT</sub>  | Output Capacitance (Note 3)                                        |                                             |       |     | 20   | pf    |

Note 1:  $I_{CC}$  conditions. Note 2:  $I_{EE}$  conditions.

Note 3: Specification is guaranteed by design.

ICSS1003 AC Electrical Characteristics (Continued)

The AC Electrical Characteristics for the ICSS1003 are not measured. They are guaranteed by design, unless otherwise noted.

The AD bus (AD3-AD0) changes on the rising edge of the AD CLK.

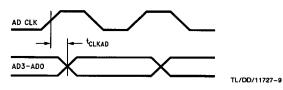

FIGURE 4. AD CLK to AD Bus

| Symbol | Parameter                                                                       | Min | Тур | Max | Units |

|--------|---------------------------------------------------------------------------------|-----|-----|-----|-------|

| FMAXAD | Maximum Clock Frequency AD CLK                                                  | 1.0 |     |     | MHz   |

| TCLKAD | Propagation Delay AD CLK to AD Bus (Note 1)                                     |     |     | 50  | ns    |

| BWF    | Filter Operational Amplifier Small Signal -3 dB Bandwidth                       | 5   |     |     | MHz   |

| SRF    | Filter Operational Amplifler Output Slew Rate                                   | 2.5 |     |     | V/µs  |

| BWGMIN | Gain Control Amplifier Small Signal -3 dB Bandwidth at Maximum Gain Setting     |     | 2.5 |     | MHz   |

| BWGMAX | Gain Control Amplifier Small Signal $-3$ dB Bandwidth at Maximum Gain Setting   |     | 0.3 |     | MHz   |

| SRG    | Gain Control Amplifier Output Slew Rate (V <sub>OUT</sub> = 5 V <sub>PP</sub> ) | 2.5 |     |     | V/µs  |

| GCS    | Gain Control Amplifier Gain Selection Delay                                     |     |     | 1.0 | ms    |

| ROD    | Gain Control Amplifier Overdrive Recovery Time                                  |     |     | 3   | μs    |

| BWD    | Driver Amplifier Small Signal −3 dB Bandwidth                                   |     | 0.5 |     | MHz   |

| SRD    | Driver Amplifier Output Slew Rate (V <sub>OUT</sub> = 5 V <sub>PP</sub> )       | 2.5 |     |     | V/µs  |

| ENDRV  | Enable/Disable Delay of Driver from DRV EN                                      |     |     | 100 | μs    |

Note 1: Estimated, but not tested or guaranteed.

## **Network Operation**

# SYNCHRONIZATION AND NETWORK ACQUISITION BY SLAVES

This section describes the process through which a network is initialized, and through which additional subscribers (Slaves) join the network.

#### Slave Initialization

Upon initialization, a Slave must search for and find the tune and bit rate currently in use. It proceeds as follows:

- 1. All tunes are searched, starting with the highest,

- 2. Within each tune search, bit rate is searched, starting at the highest bit rate.

- 3. Within each bit rate, gain is optimized using the peak search procedure described in 1 and 2.

- If a valid packet is obtained during this process, then the Slave knows the tune and switches to it, entering run mode. The Slave knows a packet is valid when the error code checks correctly.

- If not, the Slave proceeds to search all the possible tunes and bit rates, remaining on each combination for four packet times.

This process is repeated until a valid packet is heard.

#### Master Initialization

The Master starts by performing the Slave initialization sequence to see if a network with the same network address already exists. If so, it will listen and wait for that Master to falter. When it no longer detects the other Master, it will step in and try to take over.

Application software developed for IC/SS must keep track of the number of Masters and their addresses, as the dueling Master situation is impossible to prevent and can be very confusing.

If the Master cannot find a Slave with its own network address, it will proceed to the next frequency channel, and repeat the process.

## **Network Runtime Operation**

In order to keep the system gain and tune selection optimal, the network is always kept active. In network mode, the Master runs autopoil whenever there is no required host

Once a network is established with one or more Slaves, the tune control will be performed as described above.

## **ERROR CODING AND TIME DIVERSITY**

In addition to frequency-dependent noise which is combated by the adaptive frequency hopping described above, power lines suffer from impulsive noise. Impulsive noise bursts occupy all frequency bands for relatively short periods, often less than one bit time. This noise tends to be synchronous at 100 Hz or 120 Hz due to its origin.

In network mode and in the software loopback function of transparent mode, two techniques are employed to reduce sensitivity to impulse noise: error correction and overlay of retries.

## **Error Detection**

Bytes transmitted over the network are 9 bits long, 8 bits of data plus a parity bit. This allows the receiving unit to detect single-bit errors in any byte.

In addition a 27 bit error code is appended to the end of each packet. It consists of three bytes plus byte parity. The three bytes together comprise a CRC-24. This error coding allows implementation in software in real time, meets IEC and CENELEC requirements, and works well with the overlay technique.

### **Overlay of Retries**

Overlay of retries means saving those portions of earlier blocks which were not corrupted, so that on a subsequent retry a complete message can be assembled. A single impulse noise burst should only affect one or two bytes, and, since the timing of retries is arbitrary due to variable block length, it is unlikely that impulsive noise bursts will hit the same portion of a message on successive retry attempts.

If a given byte of a packet has invalid parity, the receiver will continue to collect data for the remainder of the packet, and will store those bytes with valid parity in the receive buffer. However, if the first byte, which contains the packet length, is corrupted, the entire packet must be abandoned.

On subsequent retries, if any byte is invalid, it will not be written to the receive buffer, but the corresponding byte already stored from the previous transmission or transmissions will be used. At the end of the packet, if the 27 bit error code is found to be valid, then a complete packet has been assembled and it will be output as such.

This approach allows the system to communicate successfully even in an environment so noisy that every packet has uncorrectable errors. It is only necessary that each byte get through once.

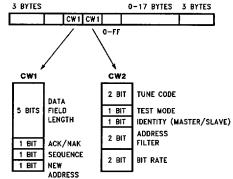

#### **PACKET STRUCTURE**

Data is sent between units in packets of variable length, containing from zero to 17 bytes of data, plus protocol information and error coding. The packet format is shown in Figure 5.

## 1 BYTE 1 BYTE 1 BYTE 1 BYTE

TL/DD/11727-10

FIGURE 5. Packet Structure

For all communication modes between Master and Slaves except broadcast, a block-ahead acknowledgment procedure is used. This ensures that packets are retried if errors cannot be corrected. The number of retries is limited by a retry count parameter. The application program is thus guaranteed that either a packet will be delivered to the far end, or the application program will be notified that this is impossible.

## **Network Operation (Continued)**

Two different maximum retry count levels are stored in firmware. The higher value is used once a link has been established.

In the case of broadcast mode, each packet is simply sent eight times, and correct receipt by all the Slaves is not guaranteed.

#### LINK AND NETWORK LAYERS

This section presents a description of link and network layer operation.

#### **Address Structure**

The Master carries a two-bit network address, set via the initialization command, or by default at 00.

The Slave carries a two-bit network address, and an eight-bit Slave address. The network address is set via the initialization command, or by default at zero. The Slave address is set by the initialization command, by hardware dip switches if connected, or by default to FF (Hex). Slave addresses 00 and FF are reserved; 00 is an illegal attribute for a Slave, and is used internally for broadcast; FF is reserved for a contention channel and for address assignment.

The Slave will only respond to a packet from a Master that bears both network and Slave addresses which match its own.

This structure permits the creation of a network containing 254 Slaves and one Master, up to four such networks can operate concurrently on different frequency-division-multiplexed channels. In this configuration, the benefits of frequency-hopping are not available, but higher aggregate throughput is obtained if the channel quality is relatively good. The Master's host can create one network with 1016 slaves by changing the Master's address field periodically.

#### **General Command Structure**

The system can operate either in transparent mode, where the physical layer is available to the host, or in network mode, where the link layer is available to the host. This choice is determined by the polarity of the NE/TRNSP pin, which is read by the microprocessor during its initialization sequence.

In transparent mode, the data present at the input is transferred to the output of all other modems on the same electrically connected power line bus. Addressing, media access control, error control and error recovery are the responsibility of the user. In this mode, the controller is not in the data path, and is used only to establish bit rate, frequency, and gain.

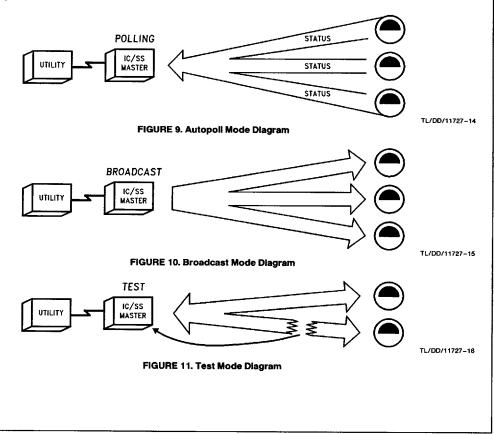

In network mode, a set of commands is provided which implement a Master-Slave local area network protocol, optimized for hierarchical control and data acquisition applications. The network mode includes a host-modem command set which includes:

- · Network Commands, which permit:

- polling of a range of Slave addresses in order to collect data

- broadcast of data to all Slaves

- a continuous, full duplex error-free link to any individual address

- Test Commands, which permit:

- installation

- debugging

- network qualification

· Commands which control physical layer operation.

The detailed syntax of all the commands is described below.

If a modem receives an illegal command code (character following <<ESC>> is not one of the command codes listed for Master or Slave, as the case may be), it will output <<ESC>> <<BELL>>. If the modem is a Master, it will return to default state (autopoll address 1).

Commands are distinguished from data in different ways, depending on whether the chip set is configured for serial or parallel operation.

In serial operation, commands and status responses are prefixed by an <<ESC>> character. The interface reverts to data mode after transfer of a legal command syntax (or a sequence comprising illegal syntax). To transmit an escape character in the application data stream, send <<ESC>><ESC>>.

In parallel mode, commands and responses are distinguished from data by two pins on the parallel interface: COMMAND for input to the chip and STATUS for output from the chip. The respective pin should be placed in HIGH state by the device performing data output prior to the availability of data. A signal on one of these two pins replaces the <<ESC>> characters described for the serial port; <<ESC>> characters are not required to designate commands when operating in parallel mode.

The symbol [CMD] will be used here to indicate the command signal. In serial mode [CMD] stands for an <<ESC>> character. In parallel mode [CMD] means that either the COMMAND or STATUS line was asserted (set LOW). In either case, [CMD] designates the following characters to be a command or a response, not data. The length of each command or response is determined by context.

Every command will generate a response proceeded with a [CMD] and followed by an <<ACK>>, <<NAK>>, <<SI>> or <<SO>>. After issuing a command to its modem, a host should not send anything (neither data nor new command) to the modem until it receives a response to the last command from the modem. Anything sent to the modem after issuing a command but before receiving a response to it will be discarded.

A Flush Buffer Command is provided to handle the following situation: If a Slave's host fails during reception of data from the Slave and leaves the Slave's output inhibited by the flow control lines, the result will be that the Slave's buffer fills with data. The Slave will then stop accepting data, causing the Master's buffers to fill up. The Master in turn signals its host, via flow control, to stop sending data. In this situation the Master's host will not be able to transfer further data to any Slave until the data buffered by the Master is successfully transmitted. In this case, the Master's host can issue the Flush Buffer Command, which will destroy data currently buffered and waiting to be sent, and return the system to default autopoll mode.

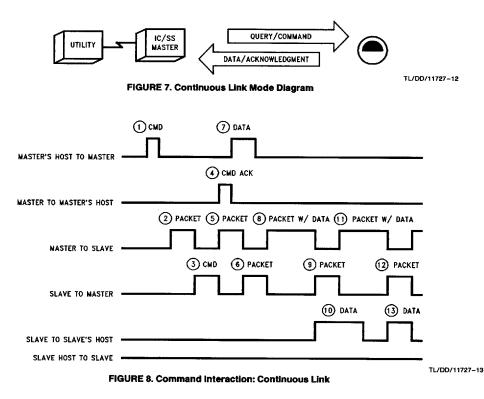

The timing of the interaction between Master's host, Master, Slave, and Slave's host can best be understood by reviewing the examples that follow, which are based on serial mode operation.

## **Command Descriptions**

Command: Autopoli

Syntax: [CMD] < Ctri-C > < Arg 1 > < Arg 2>

Arg 1: Lower limit of the Slave address space (bina-

ry)

Arg 2: Upper limit of the Slave address space (bina-

ry)

Response: (If link was acquired)

[CMD] <SO > < Addr of Slave > < Data >

Response: (If link was not acquired)

[CMD] <SI > < Addr of Slave >

Response: (If link was broken)

[CMD] <SI > < Addr of Slave >

## **Functionality**

Using the address specified, the Master attempts to establish a continuous link to the Slave. If a link is established, [CMD]<SO> are transmitted to the host followed by any data received from the Slave. When the Master receives a packet from the Slave with no data, the Master will assume that the Slave has transmitted all of its data which will prompt the Master to break the link and send [CMD]<SI> to its host and increment the Slave address and repeat the described sequence for the next Slave. When the Slave address range is exhausted, the Master will wrap around the Slave address space and proceed with a new cycle of autopoll.

Command: Broadcast

Syntax: [CMD] < Ctrl-A >

Response: [CMD] < ACK > < 0 >

#### Functionality

Enter broadcast mode of operation at the Master. The Master will remain in broadcast mode until a new command is issued by the host.

Command: Continuous Link

Arg 1: [CMD] < Ctrl-D > < Arg 1 >

Response: (If link was acquired)

[CMD] < ACK > < Addr of Slave > < Data >

Response: (if link was not acquired)

[CMD] < NAK > < Addr of Slave >

Response: (If link was broken)