#### 12-BIT CMOS MICROPROGRAM SEQUENCER

IDT39C10B IDT39C10C

#### **FEATURES:**

- Low-power CMOS

- Icc (max.)

Military: 90mA

- Commercial: 75mA

- Fast

- IDT39C10B matches 2910A speeds

- IDT39C10C 30% speed upgrade

- 33-Deep stack

- Accommodates highly nested loops and subroutines

- · 12-bit address width

- 12-bit internal loop counter

- 16 powerful microinstructions

- Three output enables control 3-way branch

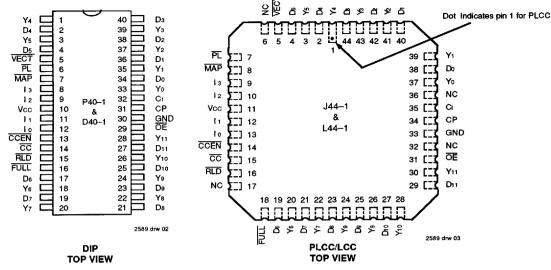

- Available in 40-pin DIP and 44-pin LCC/PLCC

- · Military product compliant to MIL-STD-883, Class B

- Standard Military Drawing #5962-87708 is listed on this function.

#### **DESCRIPTION:**

The IDT39C10 microprogram sequencers are designed for use in high-performance microprogram state machines. These

microprogram sequencers are intended for use in controlling the sequence of microinstructions executed in the microprogram memory. The IDT39C10s provide several conditional branch instructions that allow branching to any microinstruction within the 4K microword address space. A 33-deep last-in/first-out stack provides for a very powerful microprogram subroutine returnlinkage and looping capability. With this depth of a microprogram return stack, the microprogrammer has maximum flexibility in nesting subroutines and loops. The counter contained in the IDT39C10s provides for microinstruction loop counts of up to 4096, in terms of total count length.

The IDT39C10s provide a 12-bit address to the microprogram memory. This microprogram sequencer selects one of four sources for the address. These are (1) the microprogram address register, (2) external direct input, (3) internal register counter and (4) the 33-deep LIFO stack. The microprogram counter usually contains an address that is one greater than the microinstruction currently being executed in the microprogram pipeline register.

The IDT39C10s are fabricated using CEMOS, a CMOS technology designed for high-performance and high-reliability. The devices are pin-compatible, performance-enhanced, functional replacements for the 2910A.

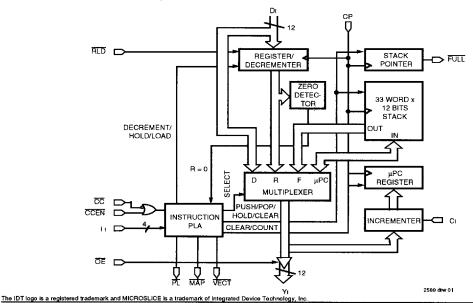

#### **FUNCTIONAL BLOCK DIAGRAM**

MILITARY AND COMMERCIAL TEMPERATURE RANGES

**MAY 1994**

©1994 Integrated Device Technology, Inc.

10.1

DSC-9004/4

**4825771 0016115 723**

### PIN CONFIGURATIONS

#### **PIN DESCRIPTIONS**

| Pin Name | I/O | Description                                                                                      |

|----------|-----|--------------------------------------------------------------------------------------------------|

| Di       | 1   | Direct input to register/counter and multiplexer Do is LSB.                                      |

| li .     | 1   | Selects one-of-sixteen instructions.                                                             |

| CC       |     | Used as test criterion. A LOW on CC indicates "passed" test condition.                           |

| CCEN     | 1   | Whenever the signal is HIGH, CC is ignored and the device operates as though CC were true (LOW). |

| Cı       | 1   | Low order carry input to incrementer for microprogram counter.                                   |

| RLD      | I   | When LOW forces loading of register/<br>counter regardless of instruction or<br>condition.       |

| ŌĒ       | 1   | Three-state control of YI outputs.                                                               |

| СР       | I   | Triggers all internal state changes at LOW-to-HIGH edge.                                         |

| Yı       | 0   | Address to microprogram memory. Yo is LSB, Y11 is MSB.                                           |

| FULL     | 0   | Indicates that 33 items are on the stack.                                                        |

| PL       | 0   | Can select #1 source (usually Pipeline Register) as direct input source.                         |

| MAP      | 0   | Can select #2 source (usually Mapping PROM or PLA) as direct input source.                       |

| VECT     | 0   | Can select #3 source (for example, Interrupt Starting Address) as direct input source.           |

2589 tbl 01

10.1

#### PRODUCT DESCRIPTION

The IDT39C10s are high-performance CMOS microprogram sequencers that are intended for use in very high-speed microprogrammable microprocessor applications. The sequencers allow for direct control of up to 4K words of microprogram.

The heart of the microprogram sequencers is a 4-input multiplexer that is used to select one of four address sources to select the next microprogram address. These address sources include the register/counter, the direct input, the microprogram counter or the stack as the source for the address of the next microinstruction.

The register/counter consists of twelve D-type flip-flops which can contain either an address or a count. These edgetriggered flip-flops are under the control of a common clock enable, as well as the four microinstruction control inputs. When the load control (RLD) is LOW, the data at the D inputs is loaded into this register on the LOW-to-HIGH transition of the clock. The output of the register/counter is available at the multiplexer as a possible next address source for the microcode. Also, the terminal count output associated with the register/counter is available at the internal instruction PLA to be used as condition code input for some of the microinstructions. The IDT39C10s contain a microprogram counter that usually contains the address of the next microinstruction compared to that currently being executed. The microprogram counter actually consists of a 12-bit incrementer followed by a 12-bit register. The microprogram counter will increment the address coming out of the sequencer going to the microprogram memory if the carry-in input to this counter is HIGH; otherwise, this address will be loaded into the microprogram counter. Normally, this carry-in input is set to the logic HIGH state so that the incrementer will be active. Should the carry-in input be set LOW, the same address is loaded into the microprogram counter. This is a technique that can be used to allow execution of the same microinstruction several times.

There are twelve D-inputs on the IDT39C10s that go directly to the address multiplexer. These inputs are used to provide a branch address that can come directly from the microcode or some other external source. The fourth input available to the multiplexer for next address control is the 33-deep, 12-bit wide LIFO stack. The LIFO stack provides return address linkage for subroutines and loops. The IDT39C10s contain a built-in stack pointer that always points to the last stack location written. This allows for stack reference operations, usually called loops, to be performed without popping the stack.

The stack pointer internal to the IDT39C10s is actually an up/down counter. During the execution of microinstructions one, four and five, the PUSH operation may occur depending on the state of the condition code input. This causes the stack pointer to be incremented by one and the stack to be written with the required return linkage (the value contained in the microprogram counter). On the microprogram cycle following the PUSH, this new return linkage data that was in the microprogram counter is now at the new location pointed to by

the stack pointer. Thus, any time the multiplexer looks at the stack, it will see this data on the top of the stack.

During five different microinstructions, a pop operation associated with the stack may occur. If the pop occurs, the stack pointer is decremented at the next LOW-to-HIGH transition of the clock. A pop decrements the stack pointer which is the equivalent of removing the old information from the top of the stack.

The IDT39C10s are designed so that the stack pointer linkage allows any sequence of pushes, pops or stack references to be used. The depth of the stack can grow to a full 33 locations. After a depth of 33 is reached, the FULC output goes LOW. If further PUSHes are attempted when the stack is full, the stack information at the top of the stack will be destroyed but the stack pointer will not end around. It is necessary to initialize the stack pointer when power is first turned on. This is performed by executing a RESET instruction (Instruction 0). This sets the stack pointer to the stack empty position — the equivalent depth of zero. Similarly, a pop from an empty stack may place unknown data on the Y outputs, but the stack pointer is designed not to end around. Thus, the stack pointer will remain at the 0 or stack empty location if a pop is executed while the stack is already empty.

The IDT39C10s' internal 12-bit register/counter is used during microinstructions eight, nine and fifteen. During these instructions, the 12-bit counter acts as a down counter and the terminal count (count = 0) is used by the internal instruction PLA as an input to control the microinstruction branch test capability. The design of the internal counter is such that, if it is preloaded with a number N and then this counter is used in a microprogram loop, the actual sequence in the loop will be executed N + 1 times. Thus, it is possible to load the counter with a count of 0 and this will result in the microcode being executed one time. The 3-way branch microinstruction, Instruction 15, uses both the loop counter and the external condition code input to control the final source address from the Y outputs of the microprogram sequencer. This 3-way branch may result in the next address coming from the D inputs, the stack or the microprogram counter.

The IDT39C10s provide a 12-bit address at the Y outputs that are under control of the OE input. Thus, the outputs can be put in the three-state mode, allowing the writable control store to be loaded or certain types of external diagnostics to be executed.

In summary, the IDT39C10s are the most powerful microprogram sequencers currently available. They provide the deepest stack, the highest performance and the lowest power dissipation for today's microprogrammed machine design.

#### **IDT39C10 OPERATION**

The IDT39C10s are CMOS pin-compatible implementations of the Am2910 and 2910A microprogram sequencers. The IDT39C10's microprogram is functionally identical except that it provides a 33-deep stack to give the microprogrammer more capability in terms of microprogram subroutines and microprogram loops. The definition of each microprogram instruction is shown in the table of instructions. This table

10

shows the results of each instruction in terms of controlling the multiplexer, which determines the Y outputs, and in controlling the signals that can be used to enable various branch address sources (PL, MAP, VECT). The operation of the register/ counter and the 33-deep stack after the next LOW-to-HIGH transition of the clock. The internal multiplexer is used to select which of the internal sources is used to drive the Y outputs. The actual value loaded into the microprogram counter is either identical to the Y output or the Y output value is incremented by 1 and placed in the microprogram counter. This function is under the control of the carry inputs. For each of the microinstruction inputs, only one of the three outputs (PL, MAP, or VECT) will be LOW. Note that this function is not determined by any of the possible condition code inputs. These outputs can be used to control the three-state selection of one of the sources for the microprogram branches.

Two inputs, CC and CCEN, can be used to control the conditional instructions. These are fully defined in the table of instructions. The RLD input can be used to load the internal register/counter at any time. When this input is LOW, the data at the D inputs will be loaded into this register/counter on the LOW-to-HIGH transition of the clock. Thus, the RLD input overrides the internal hold or decrement operations specified by the various microinstructions. The OE input is normally LOW and is used as the three-state enable for the Y outputs. The internal stack in the IDT39C10s is a last-in/first-out memory that is 12-bits in width and 33 words deep. It has a stack pointer that addresses the stack and always points to the value currently on the top of the stack. When instruction 0 (RESET) is executed, the stack pointer is initialized to the top of the stack which is, by definition, the stack empty condition. Thus, the contents of the top of the stack are undefined until the forced PUSH occurs. A pop performed while the stack is empty will not change the stack pointer in any way; however, it will result in unknown data at the Y outputs.

By definition, the stack is full any time 33 more pushes than pops have occurred since the stack was last empty. When this happens, the Full Flag will go LOW. This signal first goes LOW on the microcycle after the 33 pushes occur. When this signal is LOW, no additional pushes should be attempted or the information on the top of the stack will be lost.

#### THE IDT39C10 INSTRUCTION SET

This data sheet contains a block diagram of the IDT39C10 microprogram sequencers. As can be seen, the devices are controlled by a 4-bit microinstruction word (la-lo). Normally, this word is supplied from one 4-bit field of the microinstruction word associated with the entire state machine system. These four bits provide for the selection of one of the sixteen powerful instructions associated with selecting the address of the next microinstruction. Unused Y outputs can be left open; however, the corresponding most significant D inputs should be tied to ground for smaller microwords. This is necessary to make sure the internal operation of the counter is proper should less than 4K of microcode be implemented. As shown in the block diagram, the internal instruction PLA uses the four instruction inputs as well as the  $\overline{CC}$ ,  $\overline{CCEN}$  and the internal counter = 0 line for controlling the sequencer. This internal

instruction PLA provides all of the necessary internal control signals to control each particular part of the microprogram sequencer. The next address at the Y outputs of the IDT39C10s can be from one of four sources. These include the internal microprogram counter, the last-in/first-out stack, the register/counter and the direct inputs.

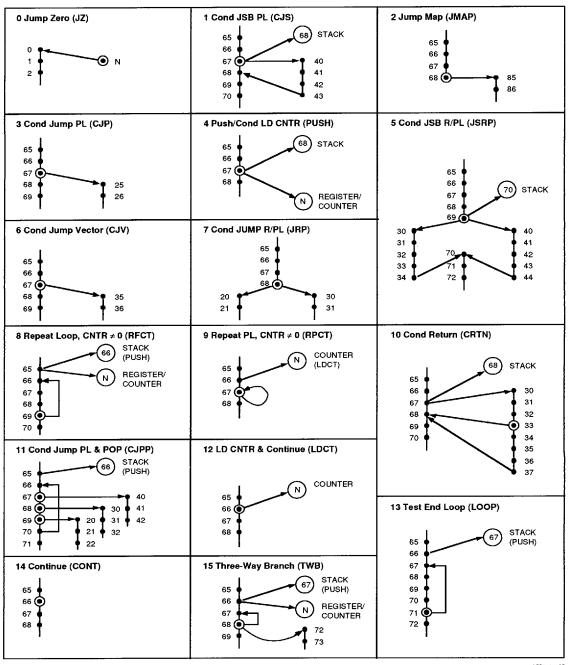

The following paragraphs will describe each instruction associated with the IDT39C10s. As a part of the discussion, an example of each instruction is shown in Figure 1. The purpose of the examples is to show microprogram flow. Thus, in each example the microinstruction currently being executed has a circle around it. That is, this microinstruction is assumed to be the contents of the pipeline register at the output of the microprogram memory. In these drawings, each of the dots refers to the time that the contents of the microprogram memory word would be in the pipeline register and is currently being executed.

#### INSTRUCTION 0 -JUMP 0 (JZ)

This instruction is used at power up time or at any restart sequence when the need is to reset the stackpointer and jump to the very first address in microprogram memory. The Jump 0 instruction does not change the contents of the register/counter.

## INSTRUCTION 1 - CONDITIONAL JUMP TO SUBROUTINE (CJS)

The Conditional Jump to Subroutine Instruction is the one used to call microprogram subroutines. The subroutine address will be contained in the pipeline register and presented at the D inputs. If the condition code test is passed, a branch is taken to the subroutine. Referring to the flow diagram for the IDT39C10s shown in Figure 1, we see that the content of the microprogram counter is 68. This value is pushed onto the stack and the top of stack pointer is incremented. If the test is failed, this Conditional Jump to Subroutine instruction behaves as a simple continue. That is, the content of microinstruction address 68 is executed next.

## INSTRUCTION 2 - JUMP MAP (JMAP)

This sequencer instruction can be used to start different microprogram routines based on the machine instruction opcode. This is typically accomplished by using a mapping PROM as an input to the D inputs on the microprogram sequencer. The JMAP instruction branches to the address appearing on the D inputs. In the flow diagram shown in Figure 1, we see that the branch actually will be the contents of microinstruction 85 and this instruction will be executed next.

## INSTRUCTION 3 – CONDITIONAL JUMP PIPELINE (CJP)

The simplest branching control available in the IDT39C10 microprogram sequencers is that of conditional jump to address. In this instruction, the jump address is usually contained in the microinstruction pipeline register and presented to the D inputs. If the test is passed, the jump is

10.1

4

10

taken. If the test fails, this instruction executes as a simple continue. In the example shown in the flow diagram of Figure 1, we see that if the test is passed, the next microinstruction to be executed is the content of address 25. If the test is failed, the microcode simply continues to the contents of the next instruction.

## INSTRUCTION 4 – PUSH/CONDITIONAL LOAD COUNTER (PUSH)

With this instruction, the counter can be conditionally loaded during the same instruction that pushes the current value of the microprogram counter on to the stack. Under any condition independent of the conditional testing, the microprogram counter is pushed on to the stack. If the conditional test is passed, the counter will be loaded with the value on the D inputs to the sequencer. If the test fails, the contents of the counter will not change. The PUSH/Conditional Load Counter instruction is used in conjunction with the loop instruction (Instruction 13), the repeat file based on the counter instruction (Instruction 9) or the 3-way branch instruction (Instruction 15).

#### INSTRUCTION 5 -CONDITIONAL JUMP TO SUBROUTINE R/PL (JSRP)

Subroutines may be called by a Conditional Jump Subroutine from the internal register or from the external pipeline register. In this instruction, the contents of the microprogram counter are pushed on the stack and the branch address for the subroutine call will taken from either the internal register/counter or the external pipeline register presented to the D inputs. If the conditional test is passed, the subroutine address will be taken from the pipeline register. If the conditional test fails, the branch address is taken from the internal register/counter. An example of this is shown in the flow diagram of Figure 1.

#### INSTRUCTION 6 -CONDITIONAL JUMP VECTOR (CJV)

The Conditional Jump Vector instruction is similar to the Jump Map instruction in that it allows a branch operation to a microinstruction as defined from some external source, except that it is conditional. The Jump Map instruction is unconditional. If the conditional test is passed, the branch is taken to the new address on the D inputs. If the conditional test is failed, no branch is taken but rather the microcode simply continues to the next sequential microinstruction. When this instruction is executed, the VECT output is LOW unconditionally. Thus, an external 12-bit field can be enabled on to the D inputs of the microprogram sequencer.

#### INSTRUCTION 7 – CONDITIONAL JUMP R/PL (JRP)

The Conditional Jump register/counter or external pipeline register always causes a branch in microcode. This jump will be to one of two different locations in the microcode address space. If the test is passed, the jump will be to the address presented on the D inputs to the microprogram sequencer. If the conditional test fails, the branch will be to the address contained in the internal register/counter.

## INSTRUCTION 8 -REPEAT LOOP COUNTER NOT EQUAL TO 0 (RFCT)

This instruction utilizes the loop counter and the stack to implement microprogrammed loops. The start address for the loop would be initialized by using the PUSH/Conditional Load Counter instruction. Then, when the repeat loop instruction is executed, if the counter is not equal to 0, the next microword address will be taken from the stack. This will cause a loop to be executed as shown in the Figure 1 flow diagram. Each time the microcode sequence goes around the loop, the counter is decremented. When the counter reaches 0, the stack will be popped and the microinstruction address will be taken from the microprogram counter. This instruction performs a timed wait or allows a single sequence to be executed the desired number of times. Remember, the actual number of loops performed is equal to the value in the counter plus 1.

# INSTRUCTION 9 – REPEAT PIPELINE COUNTER NOT EQUAL TO 0 (RPCT)

This instruction is another technique for implementing a loop using the counter. Here, the branch address for the loop is contained in the pipeline register. This instruction does not use the stack in any way as a part of its implementation. As long as the counter is not equal to 0, the next microword address will be taken from the D inputs of the microprogram sequencer. When the counter reaches 0, the internal multiplexer will select the address source from the microprogram counter, thus causing the microcode to continue on and leave the loop.

#### INSTRUCTION 10 – CONDITIONAL RETURN (CRTN)

The Conditional Return instruction is used for terminating subroutines. The fact that it is conditional allows the subroutine either to be ended or to continue. If the conditional test is passed, the address of the next microinstruction will be taken from the stack and it will be popped. If the conditional test fails, the next microinstruction address will come from the internal microprogram counter. This is depicted in the flow diagram of Figure 1. It is important to remember that every subroutine call must somewhere be followed by a return from subroutine call in order to have an equal number of pushes and pops on the stack.

#### INSTRUCTION 11 --CONDITIONAL JUMP PIPELINE AND POP (CJPP)

The Conditional Jump Pipeline and Pop instruction is a technique for exiting a loop from within the middle of the loop. This is depicted fully in the flow diagram for the IDT39C10s as shown in Figure 1. The conditional test input for this instruction results in a branch being taken if the test is passed. The address selected will be that on the D inputs to the microprogram sequencer and, since the loop is being terminated, the stack will be popped. Should the test be failed on the conditional test inputs, the microprogram will simply continue to the next address as taken from the microprogram counter. The stack will not be affected if the conditional test input is failed.

10,1 5

#### INSTRUCTION 12 – LOAD COUNTER AND CONTINUE (LDCT)

The Load Counter and Continue instruction is used to place a value on the D inputs in the register/counter and continue to the next microinstruction.

#### INSTRUCTION 13 -TEST END OF LOOP (LOOP)

The Test End of Loop instruction is used as a last instruction in a loop associated with the stack. During this instruction, if the conditional test input is failed, the loop branch address will be that on the stack. Since we may go around the loop a number of times, the stack is not popped. If the conditional test input is passed, then the loop is terminated and the stack is popped. Notice that the loop instruction requires a PUSH to be performed at the instruction immediately prior to the loop return address. This is necessary so as to have the correct address on the stack before the loop operation. It is for this reason that the stack pointer always points to the last thing written on the stack.

## INSTRUCTION 14 - CONTINUE (CONT)

Continue is a simple instruction where the address for the microinstruction is taken from the microprogram counter. This instruction simply causes sequential program flow to the next microinstruction in microcode memory.

#### INSTRUCTION 15 -THREE WAY BRANCH (TWB)

The Three-Way Branch instruction is used for looping while waiting for a conditional event to come true. If the event does not come true after some number of microinstructions, then a branch is taken to another microprogram sequence. This is

depicted in Figure 1 showing the IDT39C10's flow diagram and is also described in full detail in the IDT39C10's instruction operational summary. Operation of the instruction is such that any time the external conditional test input is passed, the next microinstruction will be that associated with the program counter and the loop will be left. The stack is also popped. Thus, the external test input overrides the other possibilities. Should the external conditional test input not be true, the rest of the operation is controlled by the internal counter. If the counter is not equal to 0, the loop is taken by selecting the address on the top of the stack as the address out of the Y outputs of the IDT39C10s. In addition, the counter is decremented. Should the external conditional test input be failed and the counter also have counted to 0, this instruction "times out". The result is that the stack is popped and a branch is taken to the address presented to the Dinputs of the IDT39C10 microprogram sequencers. This address is usually provided by the external pipeline register.

#### CONDITIONAL TEST

Throughout this discussion we have talked about microcode passing the conditional test. There are actually two inputs associated with the conditional test input. These include the CCEN and the CC inputs. The CCEN input is a condition code enable. Whenever the CCEN input is HIGH, the CC input is ginored and the device operates as though the CC input were true (LOW). Thus, a fail of the external test condition can defined as CCEN equals LOW and CC equals HIGH. A pass condition is defined as a CCEN equal to HIGH or a CC equal to LOW. It is important to recognize the full function of the condition code enable and the condition code inputs in order to understand when the test is passed or failed.

6

10.1

#### **IDT39C10 INSTRUCTION OPERATIONAL SUMMARY**

| 13 1 o | Mnemonic | сс                           | Counter<br>Test                  | Stack                   | Address<br>Source      | Register/<br>Counter   | Enable<br>Select |

|--------|----------|------------------------------|----------------------------------|-------------------------|------------------------|------------------------|------------------|

| 0      | JZ       | Х                            | Х                                | CLEAR                   | 0                      | NC                     | PL               |

| 1      | CJS      | PASS<br>FAIL                 | X<br>X                           | PUSH<br>NC              | D<br>PC                | NC<br>NC               | <u>PL</u><br>PL  |

| 2      | JMAP     | Х                            | х                                | NC                      | D                      | NC                     | MAP              |

| . 3    | CJP      | PASS<br>FAIL                 | X<br>X                           | NC<br>NC                | D<br>PC                | NC<br>NC               | <u>PL</u><br>PL  |

| 4      | PUSH     | PASS<br>FAIL                 | X<br>X                           | PUSH<br>PUSH            | PC<br>PC               | LOAD<br>NC             | PL<br>PL         |

| 5      | JSRP     | PASS<br>FAIL                 | X<br>X                           | PUSH<br>PUSH            | D<br>R                 | NC<br>NC               | PL<br>PL         |

| 6      | CJA      | PASS<br>FAIL                 | X<br>X                           | NC<br>NC                | D<br>PC                | NC<br>NC               | VECT VECT        |

| 7      | JRP      | PASS<br>FAIL                 | X<br>X                           | NC<br>NC                | D<br>R                 | NC<br>NC               | <u>PL</u><br>PL  |

| 8      | RFCT     | X<br>X                       | = 0<br>NOT = 0                   | POP<br>NC               | PC<br>STACK            | NC<br>DEC              | PL<br>PL         |

| 9      | RPCT     | X<br>X                       | = 0<br>NOT = 0                   | NC<br>NC                | PC<br>D                | NC<br>DEC              | <u>민</u><br>만    |

| 10     | CRTN     | PASS<br>FAIL                 | X<br>X                           | POP<br>NC               | STACK<br>PC            | NC<br>NC               | PL<br>PL         |

| 11     | CJPP     | PASS<br>FAIL                 | X<br>X                           | POP<br>NC               | D<br>PC                | NC<br>NC               | PL<br>PL         |

| 12     | LDCT     | X                            | X                                | NC                      | PC                     | LOAD                   | PL               |

| 13     | LOOP     | PASS<br>FAIL                 | X<br>X                           | POP<br>NC               | PC<br>STACK            | NC<br>NC               | 린                |

| 14     | CONT     | X                            | X                                | NC                      | PC                     | NC                     | PL               |

| 15     | тwв      | PASS<br>PASS<br>FAIL<br>FAIL | = 0<br>NOT = 0<br>= 0<br>NOT = 0 | POP<br>POP<br>POP<br>NC | PC<br>PC<br>D<br>STACK | NC<br>DEC<br>NC<br>DEC | PL<br>PL<br>PL   |

NC = No Change; DEC = Decrement

2589 tbl 02

Figure 1. IDT39C10B Flow Diagrams

2551 drw 05

#### **IDT39C10 INSTRUCTIONS**

| l3 — lo | Mnemonic | Name                  | Reg/<br>Cntr<br>Con-<br>tents | CCEN: | FAIL<br>= LOW and CC = HIGH | CCEN | PASS<br>= HIGH and CC = LOW | Reg/<br>Cntr | Enable |

|---------|----------|-----------------------|-------------------------------|-------|-----------------------------|------|-----------------------------|--------------|--------|

|         |          |                       |                               | Υ     | Stack                       | Υ    | Stack                       |              |        |

| 0       | JZ       | Jump Zero             | Х                             | 0     | CLEAR                       | 0    | CLEAR                       | HOLD         | PL     |

| 1       | CJS      | Cond JSP PL           | Х                             | PC    | HOLD                        | D    | PUSH                        | HOLD         | 닏      |

| 2       | JMAP     | Jump Map              | Х                             | D     | HOLD                        | ם    | HOLD                        | HOLD         | MAP    |

| 3       | CJP      | Cand Jump PL          | Х                             | PC    | HOLD                        | D    | HOLD                        | HOLD         | PL     |

| 4       | PUSH     | PUSH/Cond Ld Cntr     | Х                             | PC    | PUSH                        | PC   | PUSH                        | (1)          | 닖      |

| 5       | JSRP     | Cond JSB R/PL         | Х                             | R     | PUSH                        | D    | PUSH                        | HOLD         | PL     |

| 6       | CJV      | Cond Jump Vector      | Х                             | PC    | HOLD                        | D    | HOLD                        | HOLD         | VECT   |

| 7       | JRP      | Cond Jump R/PL        | Х                             | R     | HOLD                        | D    | HOLD                        | DEC          | 닖      |

| 8       | RFCT     | Repeat Loop, CNTR ≠ 0 | <b>≠</b> 0                    | F     | HOLD                        | F    | HOLD                        | DEC          | PL     |

| 1       |          |                       | = 0                           | PC    | POP                         | PC   | POP                         | HOLD         | PL     |

| 9       | RPCT     | Repeat PL, CNTR ≠ 0   | ≠0                            | D     | HOLD                        | D    | HOLD                        | DEC          | 닖      |

| 1       |          |                       | = 0                           | PC    | HOLD                        | PC   | HOLD                        | HOLD         | PL     |

| 10      | CRTN     | Cond RTN              | Х                             | PC    | HOLD                        | F    | POP                         | HOLD         | 닏      |

| 11      | CJPP     | Cond Jump PL & POP    | Х                             | PC    | HOLD                        | D    | POP                         | HOLD         | PL     |

| 12      | LDCT     | LD Contr & Continue   | X                             | PC    | HOLD                        | PC   | HOLD                        | LOAD         | PL     |

| 13      | LOOP     | Test End Loop         | ×                             | F     | HOLD                        | PC   | POP                         | HOLD         | PĹ     |

| 14      | CONT     | Continue              | х                             | PC    | HOLD                        | PC   | HOLD                        | HOLD         | PL     |

| 15      | TWB      | Three-Way Branch      | ≠0                            | F     | HOLD                        | PC   | POP                         | DEC          | PL     |

| ŀ       |          |                       | = 0                           | D     | POP                         | PC   | POP                         | HOLD         | PL     |

NOTE:

1. If CCEN = LOW and CC = HIGH, hold; else load. X = Don't Care.

2589 tbl 03

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| Symbol | Rating                                     | Com'l.               | Mil.                 | Unit |

|--------|--------------------------------------------|----------------------|----------------------|------|

| Vcc    | Power Supply<br>Voltage                    | -0.5 to +7.0         | -0.5 to +7.0         | ٧    |

| VTERM  | Terminal Voltage<br>with Respect to<br>GND | -0.5 to<br>Vcc + 0.5 | -0.5 to<br>Vcc + 0.5 | ٧    |

| TA     | Operating<br>Temperature                   | 0 to +70             | -55 to +125          | °Ç   |

| TBIAS  | Temperature<br>Under Bias                  | -55 to +125          | 65 to +135           | ç    |

| TsTG   | Storage<br>Temperature                     | -55 to +125          | -65 to +150          | ç    |

| ₽⊤     | Power Dissipation                          | 1.0                  | 1.0                  | 8    |

| lout   | DC Output Current                          | 30                   | 30                   | mΑ   |

#### NOTE:

2589 tbl 04

#### **CAPACITANCE** (TA = $+25^{\circ}$ C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Тур. | Unit |

|--------|--------------------------|------------|------|------|

| CIN    | Input Capacitance        | VIN = 0V   | 5    | рF   |

| Соит   | Output Capacitance       | Vout = 0V  | 7    | ρF   |

NOTE:

1. This parameter is sampled and not 100% tested.

2589 tbl 05

10.1

■ 4825771 DO16123 8TT **■**

Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### DC ELECTRICAL CHARACTERISTICS

Commercial: TA = 0°C to +70°C, Vcc =  $5.0V \pm 5\%$ ; Military: TA = -55°C to +125°C, Vcc =  $5.0V \pm 10\%$

| Symbol | Parameter                                   | Test Conditions <sup>(1)</sup>                            |                        | Min.   | Typ. <sup>(2)</sup> | Max. | Unit       |            |

|--------|---------------------------------------------|-----------------------------------------------------------|------------------------|--------|---------------------|------|------------|------------|

| ViH    | Input HIGH Level                            | Guaranteed Logic HIGH                                     | l Level <sup>(4)</sup> |        | 2.0                 | 1    | -          | ٧          |

| VIL    | Input LOW Level                             | Guaranteed Logic LOW                                      | Level <sup>(4)</sup>   |        | _                   | -    | 0.8        | ٧          |

| Lin    | Input HIGH Current                          | Vcc = Max., Vin = Vcc                                     |                        |        |                     | 0.1  | 5          | μΑ         |

| l IL   | Input LOW Current                           | Vcc = Max., Vin = GND                                     |                        |        | _                   | -0.1 | <b>-</b> 5 | μA         |

| Vон    | Output HIGH Voltage                         | Vcc = Min.                                                | Юн = -12mA             | Mil.   | 2.4                 | 4.3  | _          | ٧          |

|        |                                             | VIN = VIH or VIL                                          | lон <b>= −15mA</b>     | Com'l. | 2.4                 | 4.3  | -          |            |

| Vol    | Output LOW Voltage                          | Vcc = Min.                                                | loL = 20mA N           | ∕IiI.  | -                   | 0.3  | 0.5        | V          |

|        |                                             | VIN = VIH or VIL                                          | IOL = 24mA 0           | Com'l. | _                   | 0.3  | 0.5        |            |

| loz    | Off State (High Impedance)                  | Vcc = Max.                                                | V0 = 0V                |        | _                   | -0.1 | -10        | μΑ         |

|        | Output Current                              |                                                           | Vo = Vcc (ma           | ax.)   | _                   | 0.1  | 10         |            |

| los    | Output Short Circuit Current                | Vcc = Max., Vout = 0V                                     | (3)                    |        | -30                 | -    | -          | mA         |

| Іссан  | Quiescent Power Supply Current              | Vcc = Max.                                                |                        |        | _                   | 35   | 50         | mA         |

|        | CP = H                                      | $V\text{HC} \leq V\text{IH, } V\text{IL} \leq V\text{LC}$ |                        |        |                     |      |            |            |

|        |                                             | fcP = 0, CP = H                                           |                        |        |                     |      |            |            |

| ICCQL  | Quiescent Power Supply Current              | Vcc = Max.                                                |                        |        | -                   | 35   | 50         | mA         |

|        | CP = L                                      | VHC ≤ VIH, VIL ≤ VLC                                      |                        |        |                     |      |            |            |

|        |                                             | fcP = 0, CP = L                                           |                        |        |                     |      |            |            |

| ICCT   | Quiescent Input Power Supply <sup>(5)</sup> | VCC = Max., VIH = 3.4V,                                   | fcP = 0                |        | - 1                 | 0.3  | 0.5        | mA/        |

|        | Current (per Input @ TTL High)              |                                                           |                        |        |                     |      |            | Input      |

| ICCD   | Dynamic Power Supply Current                | Vcc = Max.                                                |                        | MIL.   |                     | 1.0  | 3.0        | mA/        |

|        |                                             | VHC ≤ VIH, VIL ≤ VLC                                      |                        | COM'L. | -                   | 1.0  | 1.5        | MHz        |

|        | 100                                         | Outputs Open, OE = L                                      |                        |        |                     |      |            |            |

| Icc    | Total Power Supply Current (6)              | Vcc = Max., fcp = 10MH                                    | lz                     | MIL.   | -                   | 45   | 80         | mA         |

|        |                                             | Outputs Open, $\overline{OE} = L$                         |                        | COM'L. | -                   | 45   | 65         | l          |

|        |                                             | CP = 50 % Duty cycle                                      |                        |        |                     |      |            |            |

|        |                                             | VHC ≤ VIH, VIL ≤ VLC                                      |                        |        |                     |      |            |            |

|        |                                             | Vcc = Max., fcp = 10MH                                    | Iz                     | MIL.   |                     | 50   | 90         |            |

|        |                                             | Outputs Open, $\overline{OE} = L$                         |                        | COM'L. | -                   | 50   | 75         |            |

|        |                                             | CP = 50 % Duty cycle                                      |                        |        |                     |      |            | ĺ          |

|        |                                             | VIH = 3.4V, VIL = 0.4V                                    |                        |        |                     |      |            | 2589 tbl 0 |

#### NOTES:

- 1. For conditions shown as Max. or Min. use appropriate value specified under Electrical Characteristics.

- 2. Typical values are at Vcc = 5.0V, + 25°C ambient and maximum loading, not production tested.

- 3. Not more than one output should be shorted at one time. Duration of the circuit test should not exceed one second.

- 4. These input levels should only be static tested in a noise-free environment.

- 5. IccT is derived by measuring the total current with all the inputs tied together at 3.4V, subtracting out IccQH, then dividing by the total number of inputs.

- 6. Total Supply Current is the sum of the Quiescent current and the Dynamic current (at either CMOS or TTL input levels). For all conditions, the Total Supply Current can be calculated by using the following equation:

ICC = ICCQH (CDH) +ICCQL (1 - CDH) + ICCT (NT x DH) + ICCD (fCP /2+foNo)

CDH = Clock duty cycle high period

DH = Data duty cycle TTL high period (VIN = 3.4V) NT = Number of dynamic inputs driven at TTL levels

fcP = Clock input frequency

to = Ouput frequency

No = Number of Outputs switching at fo

10.1

#### **CMOS TESTING CONSIDERATIONS**

There are certain testing considerations which must be taken into account when testing high-speed CMOS devices in an automatic environment. These are:

- 1) Proper decoupling at the test head is necessary. Placement of the capacitor set and the value of capacitors used is critical in reducing the potential erroneous failures resulting from large Vcc current changes. Capacitor lead length must be short and as close to the DUT power pins as possible.

- 2) All input pins should be connected to a voltage potential during testing. If left floating, the device may begin to oscillate causing improper device operation and possible latchup.

- 3) Definition of input levels is very important. Since many inputs may change coincidentally, significant noise at the device pins may cause the VIL and VIH levels not to be met until the noise has settled. To allow for this testing/board induced noise, IDT recommends using VIL ≤ 0V and VIH ≥ 3V for AC tests.

- 4) Device grounding is extremely important for proper device testing. The use of multi-layer performance boards with radial decoupling between power and ground planes is required. The ground plane must be sustained from the performance board to the DUT interface board. All unused interconnect pins must be properly connected to the ground pin. Heavy gauge stranded wire should be used for power wiring and twisted pairs are recommended to minimize inductance.

#### **IDT39C10C AC ELECTRICAL** CHARACTERISTICS

#### I MINIMUM SET-UP AND HOLD TIMES

| I. MINIMONI SET-OF ARD HOLD TIMES |        |      |        |      |      |  |  |  |

|-----------------------------------|--------|------|--------|------|------|--|--|--|

|                                   | t(     | S)   | t(     | Н)   |      |  |  |  |

| Inputs                            | Com'l. | MII. | Com'l. | Mil. | Unit |  |  |  |

| Dı → R                            | 6      | 7    | 0      | 0    | ns   |  |  |  |

| DI → PC                           | 13     | 15   | 0      | 0    | ns   |  |  |  |

| 10-3                              | 23     | 25   | 0      | 0    | ns   |  |  |  |

| CC                                | 15     | 18   | 0      | 0    | ns   |  |  |  |

| CCEN                              | 15     | 18   | 0      | 0    | ns   |  |  |  |

| CI                                | 6      | 7    | 0      | 0    | ns   |  |  |  |

| RLD                               | 11     | 12   | 0      | 0    | ns   |  |  |  |

#### 2589 thi 07

#### IDT39C10B AC ELECTRICAL CHARACTERISTICS

#### I. MINIMUM SET-UP AND HOLD TIMES

|         | t(     | (S) t(H) |        |      |      |

|---------|--------|----------|--------|------|------|

| Inputs  | Com'l. | Mil.     | Com'l. | Mil. | Unit |

| Dı→R    | 16     | 16       | 0      | 0    | ns   |

| Dı → PC | 30     | 30       | 0      | 0    | ns . |

| lo-3    | 35     | 38       | 0      | 0    | ns   |

| CC      | 24     | 35       | 0      | 0    | ns   |

| CCEN    | 24     | 35       | 0      | 0    | ns   |

| CI      | 18     | 18       | 0      | 0    | ns   |

| RLD     | 19     | 20       | 0      | 0    | ns   |

2589 tbl 102589 tbl 07

#### II. MAXIMUM COMBINATIONAL DELAYS

|        | Y      |       | PL, VECT, | MAP  | FUL    | T    |             |

|--------|--------|-------|-----------|------|--------|------|-------------|

| Inputs | Com'l. | Mil.  | Com'l.    | Mil. | Com'l. | Mil. | Unit        |

| D0-11  | 12     | 15    | _         | -    | -      | _    | ns          |

| 10-3   | 20     | 25    | 13        | 15   |        | -    | ns          |

| CC     | 16     | 20    | _         | 1    | _      | -    | ns          |

| CCEN   | 16     | 20    | -         | -    | -      | -    | ns          |

| СР     | 28     | 33    | _         | ı    | 22     | 25   | ns          |

| OE(1)  | 10/10  | 13/13 | -         | -    | -      | _    | ns          |

| NOTE:  |        |       |           |      |        |      | 2589 tbl 08 |

level with CL = 5pF. Tested at CL = 50pF, correlated to 5pF.

Enable/Disable, Disable times measure to 0.5V change on output voltage

#### II. MAXIMUM COMBINATIONAL DELAYS

|        | Y      |       | PL, VECT, MAP |      | FULL   |      |      |

|--------|--------|-------|---------------|------|--------|------|------|

| Inputs | Com'l. | Mil.  | Com'l.        | Mil. | Com'l. | Mil. | Unit |

| D011   | 20     | 25    | _             | -    | -      | -    | ns   |

| lo-3   | 35     | 40    | 30            | 35   | _      | -    | ns   |

| CC     | 30     | 36    |               | -    | -      | 1    | ns   |

| CCEN   | 30     | 36    | _             | -    | _      | ı    | ns   |

| CP     | 40     | 46    | _             | -    | 31     | 35   | ns   |

| OE (1) | 25/27  | 25/30 |               | _    | -      | _    | ns   |

#### NOTE:

1. Enable/Disable. Disable times measure to 0.5V change on output voltage level with CL = 5pF. Tested at CL = 50pF, correlated to 5pF.

#### III. CLOCK REQUIREMENTS

|                         | Com'l. | MII. | Unit        |

|-------------------------|--------|------|-------------|

| Minimum Clock LOW Time  | 18     | 20   | ns          |

| Minimum Clock HIGH Time | 17     | 20   | ns          |

| Minimum Clock Period    | 35     | 40   | ns          |

|                         |        |      | 2589 tbl 09 |

#### III. CLOCK REQUIREMENTS

|                         | Com'i. | MII. | Unit        |

|-------------------------|--------|------|-------------|

| Minimum Clock LOW Time  | 20     | 25   | ns          |

| Minimum Clock HIGH Time | 20     | 25   | ns          |

| Minimum Clock Period    | 50     | 51   | ns          |

|                         |        |      | 2000 #61 12 |

2589 tbl 12

10.1

11

4825771 0016125 672

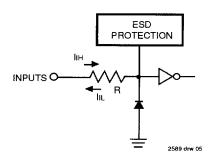

#### IDT39C10B INPUT/OUTPUT INTERFACE CIRCUIT

Figure 2. Input Structure

Figure 3. Output Structure

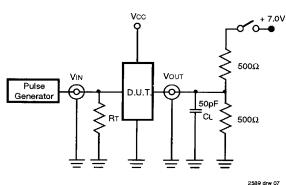

#### **TEST LOAD CIRCUIT**

Figure 4. Switching Test Circuits

DEFINITIONS

CL = Load capacitance: includes jig and probe capacitance

Termination resistance: should be equal to ZouT of the Pulse Generator

#### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 1V/ns        |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure 4 |

2589 tbl 13

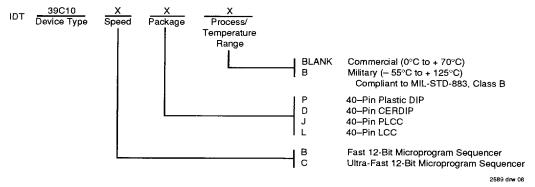

#### **ORDERING INFORMATION**

10.1

4825771 0016126 509 1

12