MICROSLICE™ PRODUCT

#### **FEATURES:**

- Low-power CMOS

- Commercial: 45mA (max.)

- Military: 55mA (max.)

- Fast

- A version meets standard speed

- B version is 20%-50% speed upgrade

- · 9-Deep stack

- Accommodates nested loops and subroutines

- Cascadable

- Infinitely expandable in 4-bit increments

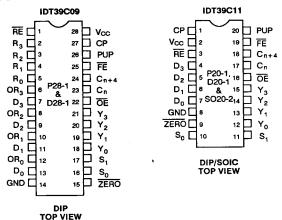

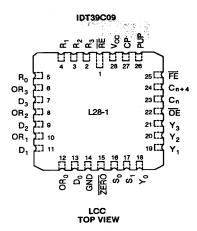

- Available in 28-pin DIP and LCC (IDT39C09) and 20-pin DIP, LCC and SOIC (IDT39C11)

- Pin-compatible, functional enhancement for all versions of the 2909/2911

- Military product compliant to MIL-STD-883, Class B

# **DESCRIPTION:**

The IDT39C09/11 devices are high-speed, 4-bit address sequencers intended for the sequence of microinstructions located in the correct m memory. They are fully cascadable and can be expected any increment of 4 bits.

address from any four sources: 1) The IDT39C09 external data from the R inputs, stored external direct is word deep push-pop stack; or 4) a proin an internal re so included in the stack are additional gram count efficiently execute nested subroutine linkcontrol funct an be ORed with an external input for condiage. Ea tional si instructions. A ZERO input line forces the out-Il outputs are three-state and are controlled by the C utput Enable) pin.

C11s operate identically to the IDT39C09s, except the CNR inputs are removed and the D and R inputs are tied to set its bey are fabricated using CEMOS ™, CMOS technology inner for high-performance and high-reliability. Military grade t is manufactured in compliance with the latest revision of MIL-STD-883, Class B, making them ideally suited to military temperature applications demanding the highest level of performance id reliability.

CEMOS and MICROSLICE are trademarks of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

OCTOBER 1987

© 1987 Integrated Device Technology, Inc.

8-48

DSC-9003/-

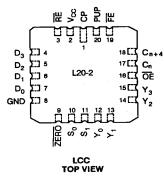

## PIN CONFIGURATIONS

## **PIN DESCRIPTIONS**

| NAME                            | 1/0 | DESCRIPTION                                                                                 |

|---------------------------------|-----|---------------------------------------------------------------------------------------------|

| S <sub>1</sub> , S <sub>0</sub> | 1   | Control lines for address source selection.                                                 |

| FE, PUP                         | - 1 | Control lines for push/pop stack.                                                           |

| RE                              | ı   | Enable line for internal address register.                                                  |

| OR <sub>i</sub>                 | 1   | Logic OR inputs on each address output line. (IDT39C09 ONLY.)                               |

| ZERO                            | ı   | When LOW, forces output lines to zero.                                                      |

| ŌĒ                              | ı   | Output Enable. When $\overline{\text{OE}}$ is HIGH, the Y outputs are OFF (high impedance). |

| C <sub>n</sub>                  | ı   | Carry-in to the incrementer.                                                                |

| Rı                              | ı   | Inputs to the internal address register.<br>(IDT39C09 ONLY.)                                |

| Di                              | ı   | Direct inputs to the multiplexer.                                                           |

| СР                              | ı   | Clock input to the AR, µPC register and Push-Pop stack.                                     |

| Yi                              | 0   | Address outputs from IDT39C09/11. (Address inputs to control memory.)                       |

| Cn + 4                          | 0   | Carry out from the incrementer.                                                             |

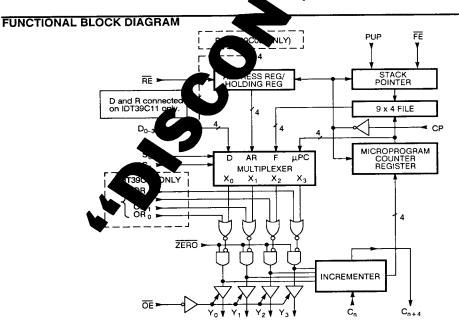

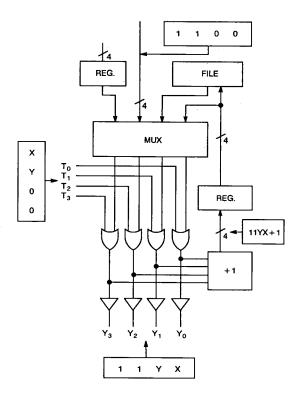

# MICROPROGRAM SEQUENCER ARCHITECTURE

The IDT39C09/11's architecture consists of the following segments:

- Multiplexer

- Direct Inputs

- Address Register

- Microprogram Counter

- Stack

#### MULTIPLEXER

The multiplexer is controlled by the  $S_0$  and  $S_1$  inputs to select the address source. The two inputs control the selection of the address register, direct inputs, microprogram counter or stack as the source of the next microinstruction address.

#### DIRECT INPUTS

This 4-bit field of inputs (D<sub>i</sub>) allows addresses from an external source to be output on the Y outputs. On the IDT39C11s, these inputs are also used as inputs to the register.

## ADDRESS REGISTER

The Address Register (AR) consists of 4 D-type, edge-triggered flip-flops which are controlled by the Register Enable ( $\overline{\text{RE}}$ ) input. With the address register enable LOW, new data will be entered into the register on the clock LOW-to-HIGH transition. The address register is also available as the next microinstruction address to the multiplexer.

# MICROPROGRAM COUNTER

Both devices contain a microprogram counter ( $\mu$ PC), which consists of a 4-bit incrementer followed by a 4-bit register. The incrementer has Carry-In ( $C_n$ ) and Carry-Out ( $C_{n+4}$ ) for easy and simple cascading.

When the least significant carry-in to the incrementer is HIGH, the microprogram register is loaded on the next clock cycle with the current Y output word plus one (Y + 1  $\rightarrow$   $\mu$ PC). If the least significant Cn is LOW, the incrementer passes the Y output word unmodified and the microprogram register is loaded with the same Y word on the next clock cycle (Y  $\rightarrow$   $\mu$ PC).

# STACK

The 9-deep stack, which stores return addresses when executing microinstructions, is an input to the multiplexer. It contains a stack pointer which always points to the last word written. The added stack depth of 9 on the IDT39C09/11 allows for additional microinstruction nesting.

The stack pointer is an up/down counter controlled by File End (FE) and Push/POP (PUP) inputs. When the FE input is LOW and

the PUP input is HIGH, the PUSH operation is enabled. The stack pointer will then increment and the memory array is written with the microinstruction address following the subroutine jump that initiated the PUSH. A POP operation is initiated at the end of a microsubroutine to obtain the return address. A POP will occur when FE and PUP are both LOW, implying a return from a subroutine. The next LOW-to-HIGH clock transition causes the stack pointer to decrement. If the FE input is HIGH, no action is taken by the stack pointer regardless of any other input.

The ZERO is used to force the four outputs to the binary zero state. When LOW, all Y outputs are LOW regardless of any other inputs (except OE). Each Y output bit also has a separate OR input such that a conditional logic one can be forced at each Y output (IDT39C09 only). This allows jumping to different microinstructions on programmed conditions.

The Output Enable  $(\overline{OE})$  input controls the Y outputs. When HIGH, the outputs are programmed to a high impedance condition.

#### OPERATION OF THE IDT39C09/11

Figure 1 lists the select codes for the multiplexer. The two bits applied from the microword register (and additional combinational logic for branching) determine which data source contains the address for the next microinstruction. The contents of the selected source will appear on the Y outputs. Also in Figure 1 is the truth table for the output control and the push/pop stack control. So, S1,  $\overline{\text{FE}}$  and PUP operation is explained in Figure 2. All four define the address appearing on the Y outputs and the state of the internal registers following a clock LOW-to-HIGH transition.

The columns on the left explain the sequence of micro-instructions to be executed. At address J+2, the sequence control portion of the microinstruction contains the command "Jump to Subroutine at A". At the time T2, this instruction is in the  $\mu$ WR and the IDT39C09 inputs are set up to execute the jump and save the return address. The subroutine address A is applied to the D inputs from the  $\mu$ WR and appears on the Y outputs. The first instruction of the subroutine, I (A), is accessed and is at the inputs of the  $\mu$ WR. On the next clock transition, I (A) is loaded into the  $\mu$ WR for execution and the return address J+3 is pushed onto the stack. The return instruction is executed at T5. Figure 4 is a similar timing chart showing one subroutine linking to a second, the latter consisting of only one microinstruction.

Figures 3 and 4 are examples of subroutine execution. The instruction being executed at any given time is the one contained in the microword register ( $\mu WR$ ). The contents of the  $\mu WR$  also controls the four signals  $S_0,S_1$ , FE and PUP. The starting address of the subroutine is applied to the D inputs of the IDT39C09 at the correct time.

# 8

# **ADDRESS SELECTION**

| S <sub>1</sub> | So | SOURCE FOR Y OUTPUTS     | SYMBOL |

|----------------|----|--------------------------|--------|

| 1              | 1  | Microprogram Counter     | μРС    |

| lī             | H  | Address/Holding Register | AR     |

| lн             | L  | Push-Pop Stack           | STK0   |

| н              | н  | Direct Inputs            | Di     |

## **OUTPUT CONTROL**

| OR  | ZERŌ | ŌĒ | Υ <sub>1</sub>                                   |

|-----|------|----|--------------------------------------------------|

| X   | X    | H  | Z                                                |

| X   | L    | Ł  | L                                                |

| I н | н    | L  | H                                                |

| L   | н    | L  | Source selected by S <sub>0</sub> S <sub>1</sub> |

Z = High Impedance

# SYNCHRONOUS STACK CONTROL

| FE | PUP | PUSH-POP STACK CHANGE                                   |

|----|-----|---------------------------------------------------------|

| Н  | Х   | No change                                               |

| L  | н   | Increment stack pointer, then push current PC onto STK0 |

| L  | L   | Pop stack (decrement stack pointer)                     |

H = High

L = Low

X = Don't Care

Figure 1.

| CYCLE      | S <sub>0</sub> , S <sub>1</sub> , FE, PUP | μРС         | REG    | Y <sub>OUT</sub> | COMMENT                            | PRINCIPAL USE    |

|------------|-------------------------------------------|-------------|--------|------------------|------------------------------------|------------------|

| N<br>N + 1 | LLLL<br>-                                 | J<br>J + 1  | K<br>K | J                | Pop Stack                          | End Loop         |

| N<br>N + 1 | LLLH<br>-                                 | J<br>J + 1  | K<br>K | J                | Push µPC                           | Set-up Loop      |

| N<br>N + 1 | LLHX<br>-                                 | J<br>J + 1  | K<br>K | J<br>            | Continue                           | Continue         |

| N<br>N + 1 | LHLL<br>-                                 | J<br>K + 1  | K<br>K | K<br>-           | Pop Stack; Use AR for Address      | End Loop         |

| N<br>N + 1 | LHLH<br>-                                 | J<br>K + 1  | K<br>K | K<br>-           | Push μPC; Jump to Address in AR    | JSR AR           |

| N<br>N + 1 | LHHX<br>-                                 | J<br>K + 1  | K<br>K | K<br>-           | Jump to Address in AR              | JMP AR           |

| N<br>N + 1 | H L L L                                   | J<br>Ra + J | ĸ      | Ra<br>–          | Jump to Address in STK0; Pop Stack | RTS              |

| N<br>N + 1 | HLLH<br>-                                 | J<br>Ra + 1 | K<br>K | Ra<br>-          | Jump to Address in STK0; Push μPC  |                  |

| N<br>N + 1 | HLHX<br>-                                 | J<br>Ra + 1 | K<br>K | Ra<br>-          | Jump to Address in STK0            | Stack Ref (Loop) |

| N<br>N + 1 | H H L L                                   | J<br>D + 1  | K<br>K | D<br>-           | Pop Stack; Jump to Address on D    | End Loop         |

| N<br>N + 1 | HHLH<br>-                                 | J<br>D + 1  | K<br>K | D<br>-           | Jump to Address on D; Push μPC     | JSR D            |

| N<br>N + 1 | нннх                                      | J<br>D + 1  | K<br>K | D<br>            | Jump to Address on D               | JMP D            |

X = Don't Care, 0 = LOW, 1 = HIGH, Assume C<sub>N</sub> = HIGH

Figure 2. Output and Internal Next-Cycle Register States for IDT39C09/11

# CONTROL MEMORY

| 00111110                                           | L MICINION                              | ROPROGRAM                                       |

|----------------------------------------------------|-----------------------------------------|-------------------------------------------------|

| CYCLE                                              | ADDRESS                                 | SEQUENCER<br>INSTRUCTION                        |

| T <sub>0</sub> T <sub>1</sub> T <sub>2</sub>       | J-1<br>J<br>J+1<br>J+2<br>J+3           | -<br>-<br>-<br>JSR A                            |

| Т <sub>6</sub><br>Т <sub>7</sub>                   | J + 4<br><br>-<br>-                     | -<br>-<br>-<br>-                                |

| T <sub>3</sub><br>T <sub>4</sub><br>T <sub>5</sub> | A + 1<br>A + 2<br>-<br>-<br>-<br>-<br>- | -<br>I (A)<br>-<br>RTS<br>-<br>-<br>-<br>-<br>- |

|                                                    | -                                       |                                                 |

In the columns in figures 3 and 4, the sequence of microinstructions to be executed are shown. At address J+2, the command "Jump to Subroutine at A" is contained in the sequence control portion of the microinstruction. At time  $T_2$ , this instruction is in the  $\mu WR$  and the IDT39C09 inputs are set up to execute the jump and save the return address. The subroutine address A is applied to the D inputs from the  $\mu WR$  and appears on the Y outputs. The first instruction of the subroutine, I (A), is accessed and is at the inputs of the  $\mu WR$ . On the next clock transition, I (A) is loaded into the  $\mu WR$  for execution and the return address J+3 is pushed onto the stack. The return instruction is executed at  $T_5$ . Figure 4 shows a similar timing chart of one subroutine linking to a second, the latter consisting of only one microinstruction.

| EXECUTE CYCL                                       | Ē                                                 | T <sub>0</sub>            | T <sub>1</sub>            | T <sub>2</sub>            | T <sub>3</sub>           | T <sub>4</sub>           | T <sub>5</sub>                | T <sub>6</sub>            | Т7                        | T <sub>8</sub> | T <sub>9</sub> |

|----------------------------------------------------|---------------------------------------------------|---------------------------|---------------------------|---------------------------|--------------------------|--------------------------|-------------------------------|---------------------------|---------------------------|----------------|----------------|

| CLOCK<br>SIGNALS                                   |                                                   |                           |                           |                           |                          |                          |                               |                           |                           |                |                |

| IDT39C09/11<br>Inputs<br>(from µWR)                | S <sub>1</sub> , S <sub>0</sub><br>FE<br>PUP<br>D | 0<br>H<br>X<br>X          | 0<br>H<br>X<br>X          | 3<br>L<br>H<br>A          | 0<br>H<br>X<br>X         | 0<br>Н<br>Х<br>Х         | 2<br>L<br>L<br>X              | 0<br>H<br>X<br>X          | 0<br>H<br>X<br>X          |                |                |

| Internal<br>Registers                              | μPC<br>STK0<br>STK1<br>STK2<br>STK3               | J + 1<br>-<br>-<br>-<br>- | J + 2<br>-<br>-<br>-<br>- | J + 3<br>-<br>-<br>-<br>- | A + 1<br>J + 3<br>-<br>- | A + 2<br>J + 3<br>-<br>- | A + 3<br>J + 3<br>-<br>-<br>- | J + 4<br>-<br>-<br>-<br>- | J + 5<br>-<br>-<br>-<br>- |                |                |

| IDT39C09/11<br>Output                              | Y                                                 | J + 1                     | J + 2                     | Α                         | A + 1                    | A + 2                    | J + 3                         | J + 4                     | J + 5                     |                |                |

| ROM Output                                         | (Y)                                               | I (J + 1)                 | JSR A                     | I (A)                     | 1 (A + 1)                | RTS                      | I (J + 3)                     | I (J + 4)                 | I (J + 5)                 |                |                |

| Contents of µWR<br>(Instruction<br>being executed) | μWR                                               | l (J)                     | 1 (J + 1)                 | JSR A                     | I (A)                    | I (A + 1)                | RTS                           | I (J + 3)                 | I (J + 4)                 |                |                |

$C_n = High$

Figure 3. Subroutine Execution

# **CONTROL MEMORY**

|                | MICROPROGRAM |                          |  |  |  |  |  |  |

|----------------|--------------|--------------------------|--|--|--|--|--|--|

| CYCLE          | ADDRESS      | SEQUENCER<br>INSTRUCTION |  |  |  |  |  |  |

|                | J – 1        | -                        |  |  |  |  |  |  |

| To             | J            | _                        |  |  |  |  |  |  |

| T <sub>1</sub> | J + 1        | _                        |  |  |  |  |  |  |

| T <sub>2</sub> | J + 2        | JSR A                    |  |  |  |  |  |  |

| Tg             | J + 3        | -                        |  |  |  |  |  |  |

|                | _            | -                        |  |  |  |  |  |  |

|                | _            | _                        |  |  |  |  |  |  |

|                | _            | _                        |  |  |  |  |  |  |

|                | _            |                          |  |  |  |  |  |  |

| T <sub>3</sub> | A            | _                        |  |  |  |  |  |  |

| T <sub>4</sub> | A + 1        | _                        |  |  |  |  |  |  |

| T <sub>5</sub> | A + 2        | JSR B                    |  |  |  |  |  |  |

| T <sub>7</sub> | A + 3        | -                        |  |  |  |  |  |  |

| T <sub>8</sub> | A + 4        | RTS                      |  |  |  |  |  |  |

| 1              | -            | _                        |  |  |  |  |  |  |

|                | _            | _                        |  |  |  |  |  |  |

|                | _            | -                        |  |  |  |  |  |  |

|                | -            | i –                      |  |  |  |  |  |  |

| T <sub>6</sub> | В            | RTS                      |  |  |  |  |  |  |

| 1              | _            | l –                      |  |  |  |  |  |  |

|                | _            | l                        |  |  |  |  |  |  |

| EXECUTE CYCLI                                      | E                                                 | T <sub>0</sub>            | T <sub>1</sub>            | T <sub>2</sub>            | T <sub>3</sub>                | T <sub>4</sub>                | T <sub>5</sub>           | T <sub>6</sub>                    | Т7                            | T <sub>8</sub>                | Tg                 |

|----------------------------------------------------|---------------------------------------------------|---------------------------|---------------------------|---------------------------|-------------------------------|-------------------------------|--------------------------|-----------------------------------|-------------------------------|-------------------------------|--------------------|

| CLOCK<br>SIGNALS                                   |                                                   |                           |                           |                           |                               |                               |                          |                                   |                               |                               |                    |

| IDT39C09/11<br>Inputs<br>(from μWR)                | S <sub>1</sub> , S <sub>0</sub><br>FE<br>PUP<br>D | 0<br>H<br>X<br>X          | о<br>н<br>х<br>х          | 3<br>L<br>H<br>A          | 0<br>H<br>X<br>X              | 0<br>H<br>X<br>X              | 3<br>L<br>H<br>B         | 2<br>L<br>L<br>X                  | 0<br>H<br>X<br>X              | 2<br>L<br>L<br>X              | 0<br>H<br>X<br>X   |

| Internal<br>Registers                              | μPC<br>STK0<br>STK1<br>STK2<br>STK3               | J + 1<br>-<br>-<br>-<br>- | J + 2<br>-<br>-<br>-<br>- | J + 3<br>-<br>-<br>-<br>- | A + 1<br>J + 3<br>-<br>-<br>- | A + 2<br>J + 3<br>-<br>-<br>- | A + 3<br>J + 3<br>-<br>- | B + 1<br>A + 3<br>J + 3<br>-<br>- | A + 4<br>J + 3<br>-<br>-<br>- | A + 5<br>J + 3<br>-<br>-<br>- | J +<br>-<br>-<br>- |

| IDT39C09/11<br>Output                              | Y                                                 | J+1                       | J + 2                     | А                         | A + 1                         | A + 2                         | В                        | A + 3                             | A + 4                         | J + 3                         | J+                 |

| ROM Output                                         | (Y)                                               | I(J + 1)                  | JSR A                     | I(A)                      | I(A + 1)                      | JSR B                         | RTS                      | I(A + 3)                          | RTS                           | I(J + 3)                      | I(J +              |

| Contents of µWR<br>(Instruction<br>being executed) | μWR                                               | I(J)                      | i(J + 1)                  | JSR A                     | 1 (A)                         | !(A + 1)                      | JSR B                    | RTS                               | I(A + 3)                      | RTS                           | I(J +              |

C<sub>n</sub> = High

Figure 4. Two Nested Subroutines. Routine B is Only One Instruction

# IDT39C09/11 APPLICATIONS

The IDT39C09 and IDT39C11 are four-bit-slice sequencers which are cascaded to form a microprogram memory address generator. Both products make available to the user several lines which are used to directly control the internal holding register, multiplexer and stack. By appropriate control of these lines, the user can implement any desired set of sequence control functions; by cascading parts he can generate any desired address length. These two qualities set the IDT39C09 and IDT39C11 apart from the IDT39C10, which is architecturally similar, but is fixed at 12 bits in length and has a fixed set of 16 sequence control instructions. The IDT39C09 or IDT39C11 should be selected instead of the IDT39C10 under the following conditions: (1) address less than 8 bits and not likely to be expanded; (2) address longer than 12 bits; (3) more complex instruction set needed than is available on IDT39C10.

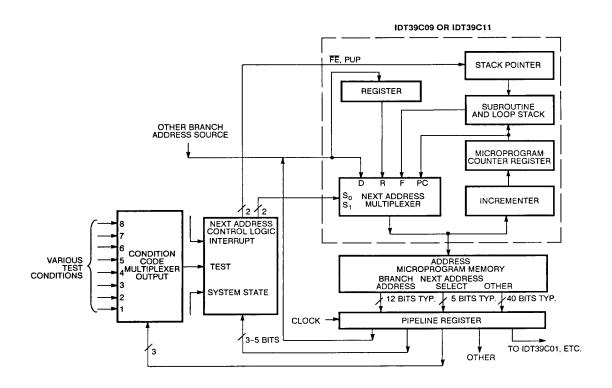

#### CONTROL UNIT ARCHITECTURE

The recommended architecture using the IDT39C09 or IDT39C11 is shown in Figure 5. The path from the pipeline register output through the next address logic, multiplexer and microprogram memory is all combinational. The pipeline register contains the current microinstruction being executed. A portion of that microinstruction consists of a sequence control command such as "continue", "loop", "return from subroutine", etc. The bits representing this sequence command are logically combined with bits representing such things as test conditions and system state to generate the required control signals to the IDT39C09 or IDT39C11.

Figure 5. Recommended Computer Control Unit Architecture Using the IDT39C09A/B and IDT39C11A/B

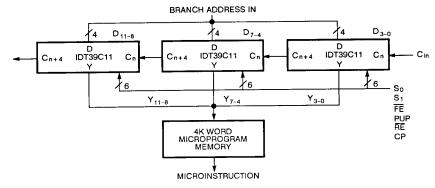

#### IDT39C09/11 EXPANSION

Figure 6 shows the interconnection of three IDT39C11s to forma 12-bit sequencer. Note that the only interconnection between packages, other than the common clock and control lines, is the ripple carry between µPC incrementors. This carry path is not in the critical speed path if the IDT39C11 Y outputs drive the microprogram memory, because the ripple carry occurs in parallel with the memory access time. If, on the other hand, a microaddress register is placed at the IDT39C11 output, then the carry may lie in the critical speed path since the last carry-in must be stable for a set-up time prior to the clock.

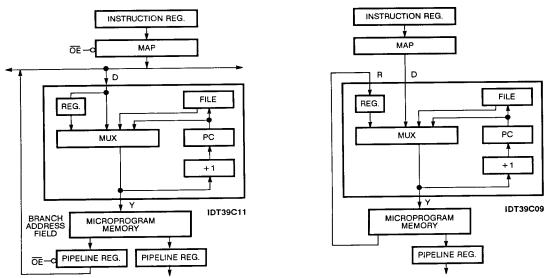

# SELECTING BETWEEN THE IDT39C09 AND IDT39C11

The difference between the IDT39C09 and the IDT39C11 involves two signals: the data inputs to the holding register and the

OR inputs. In the IDT39C09, separate four-bit fields are provided for the holding register and the direct branch inputs to the multiplexer. In the IDT39C11, these fields are internally tied together. This may affect the design of the branch address system, as shown in Figure 7. Using the IDT39C09, the register inputs may be connected directly to the microprogram memory; the internal register replaces part of the pipeline register. The direct (D) inputs may be tied to the mapping logic which translates instruction op codes into microprogram addresses. While the same technique might be used with the IDT39C11, it is more common to connect the IDT39C11's D inputs to a branch address bus onto which various sources may be enabled. Shown in Figure 7 is a pipeline register and a mapping ROM. Other sources might also be applied to the same bus. The internal register is used only for temporary storage of some previous branch address.

Figure 6. Twelve Bit Sequencer

Figure 7. Branch Address Structure

The second difference between the IDT39C09 and IDT39C11 is that the IDT39C09 has OR inputs available on each address output line. These pins can be used to generate multi-way single-cycle branches by simply typing several test conditions into the OR lines (see Figure 8). Typically, a branch is taken to an address with zeros in the least significant bits. These bits are replaced with 1s or 0s by test conditions applied to the OR lines. In Figure 8, the states of the two test conditions X and Y result in a branch to 1100, 1101, 1110 or 1111.

# HOW TO PERFORM COMMON FUNCTIONS WITH THE IDT39C09/11

## 1. CONTINUE

| MUX/Y <sub>OUT</sub> | STACK | C | 'S'1 | s, | FE | PUP |

|----------------------|-------|---|------|----|----|-----|

| PC                   | ного  | Η | L    | L  | н  | Х   |

Contents of PC placed on Y outputs; PC incremented.

#### 2. BRANCH

| MUX/Y <sub>OUT</sub> | STACK | Cn | S <sub>1</sub> | s, | FE | PUP |

|----------------------|-------|----|----------------|----|----|-----|

| D                    | HOLD  | Н  | Н              | н  | н  | Х   |

Feed data on D inputs straight through to memory address lines. Increment address and place in PC.

#### 3. JUMP TO SUBROUTINE

| MUX/Y <sub>OUT</sub> | STACK | Cn | S <sub>1</sub> | S, | FE | PUP |

|----------------------|-------|----|----------------|----|----|-----|

| D                    | PUSH  | Н  | н              | н  | L  | Н   |

Subroutine address fed from D inputs to memory address.

Current PC is pushed onto stack where it is saved for the return.

#### 4. RETURN FROM SUBROUTINE

| MUX/Y <sub>OUT</sub> | STACK | Cn | S <sub>1</sub> | S <sub>0</sub> | FE | PUP |

|----------------------|-------|----|----------------|----------------|----|-----|

| STACK                | POP   | н  | Н              | L              | L  | L   |

The address at the top of the stack is applied to the microprogram memory and is incremented for PC on the next cycle. The stack is popped to remove the return address.

Figure 8. Use of OR Inputs to Obtain 4-Way Branch

# 8

# ABSOLUTE MAXIMUM RATINGS (1)

| SYMBOL            | RATING                                     | COMMERCIAL   | MILITARY     | UNIT |

|-------------------|--------------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect to<br>GND | -0.5 to +7.0 | -0.5 to +7.0 | ٧    |

| TA                | Operating<br>Temperature                   | 0 to +70     | -55 to + 125 | °C   |

| T <sub>BIAS</sub> | Temperature<br>Under Bias                  | -55 to +125  | -65 to +135  | °C   |

| T <sub>STG</sub>  | Storage<br>Temperature                     | -55 to +125  | -65 to + 150 | ů    |

| P <sub>T</sub>    | Power Dissipation                          | 1.0          | 1.0          | W    |

| I <sub>оит</sub>  | DC Output Current                          | 30           | 30           | mA   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# CAPACITANCE (T<sub>A</sub> = +25°C, f = 1.0MHz)

| SYMBOL PARAMETER(1) |                    | CONDITIONS            | TYP. | UNITS |

|---------------------|--------------------|-----------------------|------|-------|

| C <sub>IN</sub>     | Input Capacitance  | V <sub>IN</sub> = 0V  | 5    | рF    |

| C <sub>OUT</sub>    | Output Capacitance | V <sub>OUT</sub> = 0V | 7    | pF    |

#### NOTE:

1. This parameter is sampled and not 100% tested.

# DC ELECTRICAL CHARACTERISTICS

$T_A = 0$ °C to +70°C

$V_{CC} = 5.0V \pm 5\%$  (Commercial)

$T_A = -55^{\circ}C \text{ to } + 125^{\circ}C$

$V_{CC} = 5.0V \pm 10\%$  (Military)

$V_{LC} = 0.2V$   $V_{HC} = V_{CC} - 0.2V$

| SYMBOL          | PARAMETER                    | TEST CONDITIONS (1)                                       |                                | MIN.            | TYP. <sup>(2)</sup> | MAX.            | UNIT |

|-----------------|------------------------------|-----------------------------------------------------------|--------------------------------|-----------------|---------------------|-----------------|------|

| V <sub>IH</sub> | Input HIGH Level             | Guaranteed Logic High L                                   | evel (4)                       | 2.0             | - 1                 | -               | V    |

| V <sub>IL</sub> | Input LOW Level              | Guaranteed Logic Low Lo                                   | evel (4)                       | -               | -                   | 0.8             | V    |

| I <sub>IH</sub> | Input High Current           | V <sub>CC</sub> = Max., V <sub>IN</sub> = V <sub>CC</sub> |                                |                 | 0.1                 | 5               | μА   |

| h <sub>L</sub>  | Input LOW Current            | V <sub>CC</sub> = Max., V <sub>IN</sub> = GND             |                                | -               | -0.1                | -5              | μΑ   |

| "               |                              |                                                           | I <sub>OH</sub> = -300μA       | V <sub>HC</sub> | Vcc                 | -               |      |

| V <sub>OH</sub> | Output HIGH Voltage          | $V_{CC} = Min.$ $V_{IN} = V_{IH} \text{ or } V_{IL}$      | I <sub>OH</sub> = -12mA MIL.   | 2.4             | 4.3                 | _               | ٧    |

| <b>J</b>        |                              |                                                           | I <sub>OH</sub> = -15mA COM'L. | 2.4             | 4.3                 | -               |      |

|                 | Output LOW Voltage           |                                                           | I <sub>OL</sub> = 300μA        | -               | GND                 | V <sub>LC</sub> |      |

| V <sub>OL</sub> |                              | V <sub>CC</sub> = Min.                                    | I <sub>OL</sub> = 20mA MIL.    | _               | 0.3                 | 0.5             |      |

|                 | :<br>!                       | $V_{IN} = V_{IH} \text{ or } V_{IL}$                      | I <sub>OL</sub> = 24mA COM'L.  | _               | 0.3                 | 0.5             |      |

|                 | Off State (High Impedance)   |                                                           | V <sub>O</sub> = 0V            | <del>  -</del>  | -0.1                | -10             | μА   |

| loz             | Output Current               | V <sub>CC</sub> = Max.                                    | $V_O = V_{CC}$ (max.)          | -               | 0.1                 | 10              | 1    |

| los             | Output Short Circuit Current | V <sub>CC</sub> = Max., V <sub>OUT</sub> = 0V             | (3)                            | -30             | -50                 | -               | mA   |

#### NOTES:

- 1. For conditions shown as max. or min., use appropriate value specified under Electrical Characteristics.

- 2. Typical values are at Vcc = 5.0V, +25°C ambient and maximum loading.

- 3. Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed one second.

- 4. These input levels provide zero noise immunity and should only be static tested in a noise-free environment.

# DC ELECTRICAL CHARACTERISTICS (CONT'D)

$T_A = 0$ °C to +70°C

$V_{CC} = 5.0V \pm 5\%$  (Commercial)

$T_A = -55$ °C to +125°C

$V_{CC} = 5.0V \pm 10\%$  (Military)

$V_{LC} = 0.2V$  $V_{HC} = V_{CC} - 0.2V$

| SYMBOL | PARAMETER                                                          | TEST CONDITIONS (1)                                                                                                                              | MIN.     | TYP. <sup>(2)</sup> | MAX. | UNIT         |

|--------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|------|--------------|

| ССОН   | Quiescent Power Supply Current<br>CP = H (CMOS Inputs)             | $ \begin{aligned} &V_{CC} &= \text{Max.} \\ &V_{HC} \leq V_{\text{IN}} , V_{\text{IN}} \leq V_{\text{LC}} \\ &f_{CP} = 0, CP = H \end{aligned} $ | -        | 2.5                 | 5    | mA           |

| Iccal  | Quiescent Power Supply Current<br>CP = L (CMOS Inputs)             | $V_{CC} = Max.$ $V_{HC} \le V_{IN}, V_{IN} \le V_{LC}$ $f_{CP} = 0, CP = L$                                                                      | -4       | 2.5                 | 5    | mA           |

| ССТ    | Quiescent Input Power Supply (5)<br>Current (per Input @ TTL High) | $V_{CC} = Max. V_{IN} = 3.4V, f_{CP} = 0$                                                                                                        |          | 0.3                 | 0.5  | mA/<br>Input |

| Iccp   | Dynamic Power Supply Current                                       | V <sub>CC</sub> = Max.<br>V <sub>HC</sub> $\leq$ V <sub>IN</sub> , V <sub>N</sub> $\leq$ V <sub>LC</sub>                                         | MIL.     | 2.0                 | 4.0  | mA/          |

|        |                                                                    | Outputs Open, $\overline{OE} = L$                                                                                                                |          | 2.0                 | 3.0  | MHz          |

|        | Total Power Supply Current <sup>(6)</sup>                          | $V_{CC} = Max., f_{CP} = 10MHz$<br>Outputs Open, $\overline{OE} = L$                                                                             | -        | 25                  | 45   | 7 41         |

| lcc    |                                                                    | $CP = 50\% \text{ Duty cycle}$ $V_{HC} \le V_{IN} , V_{IN} \le V_{LC}$                                                                           | <b>-</b> | 25                  | 35   | mA           |

|        |                                                                    | Outputs Open, OE = L                                                                                                                             | MIL. –   | 35                  | 55   | IIIA         |

|        |                                                                    | CP = 50% Duty cycle<br>$V_{ H} = 3.4V$ , $V_{ L} = 0.4V$                                                                                         | COM'L    | 35                  | 45   |              |

#### NOTES:

5. I ccr is derived by measuring the total current with all the inputs tied tog at 3.4V, subtracting out I ccoh, then dividing by the total number of inputs.

6. Total Supply Current is the sum of the Quiescent current and the Dynam Carlot (at either CMOS or TTL input levels). For all conditions, the Total Supply Current can be calculated by using the following equation:

$I_{CC} = I_{CCOH}(CD_H) + I_{CCOL} (1 - CD_H) + I_{CCT} (N_T \times D_H) + I_{CCD} (f_C)$  $CD_H = Clock$  duty cycle high period

$D_H$  = Data duty cycle TTL high period ( $V_{IN} = 3.4V$ )

N<sub>T</sub> = Number of dynamic inputs driven at TTL levels

N<sub>T</sub> = Number of dynamic inputs driven at TTI f<sub>CP</sub> = Clock Input frequency

# **CMOS TESTING CONSIDERATION**

There are certain testing consideration while less to be taken into account when testing high-speed wices in an automatic environment. These are:

- 1) Proper decoupling at the test having negative. Placement of the capacitor set and the value of the capacitor used is critical in reducing the potential erropers far a resulting from large Vcc current changes. Capacitor of length must be short and as close to the DUT pour pins a possible.

- All input pins should be contesting. If left floating, it evice may begin to oscillate causing improper device of cration and possible latchup.

- 3) Definition of input levels are very important. Since many inputs may change coincidently, significant noise at the device pins may cause the V<sub>IL</sub> and V<sub>IH</sub> levels not to be met until the noise has settled. To allow for this testing/board induced noise, IDT recommends using V<sub>IL</sub> ≤ 0V and V<sub>IH</sub> ≥ 3V for AC tests.

- 4) Device grounding is extremely important for proper device testing. The use of multi-layer performance boards with radial decoupling between power and ground planes is required. The ground plane must be sustained from the performance board to the DUT interface board. All unused interconnect pins must be properly connected to the ground pin. Heavy gauge stranded wire should be used for power wiring and twisted pairs are recommended to minimize inductance.

# IDT39C09B/IDT39C11B SWITCHING **CHARACTERISTICS OVER OPERATING RANGE**

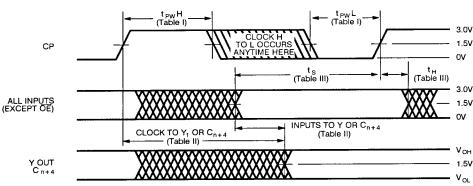

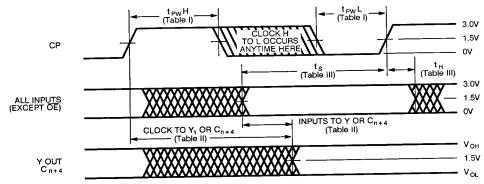

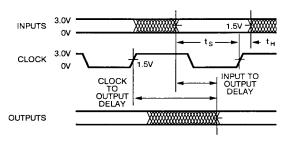

Table I, II and III below define the timing characteristics of the IDT39C09B/11B over the operating voltage and temperature ranges. The tables are divided into three types of parameters: clock characteristics, combinational delays from inputs to outputs and set-up and hold time requirements. The latter table defines the time prior to the end of the cycle (i.e., clock LOW-to-HIGH transition) that each input must be stable to guarantee that the correct data is written into one of the internal registers.

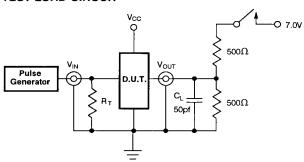

Measurements are made at 1.5V with  $V_{\rm IL}=0V$  and  $V_{\rm IH}=3.0V$ . For three-state disable tests,  $C_L=5.0 pF$  and measurement is to 0.5V change on output voltage level. All outputs have maximum DC loading.

TABLE I CYCLE TIME AND CLOCK CHARACTERISTICS

| TIME                    | COMMERCIAL | MILITARY |

|-------------------------|------------|----------|

| Minimum Clock LOW Time  | 12         | 12       |

| Minimum Clock HIGH Time | 12         | 12       |

# TABLE II MAXIMUM COMBINATIONAL PROPAGATION DELAYS

C<sub>L</sub> = 50pF (except output disable test)

| EDOM INDUT                                 | COMMERCIAL |                  | MIL | UNIT   |      |

|--------------------------------------------|------------|------------------|-----|--------|------|

| FROM INPUT                                 | Υ          | C <sub>n+4</sub> | Υ   | Cn + 4 | UNIT |

| Di                                         | 14         | <b>1</b> 5       | 16  | 17     | ns   |

| S <sub>0</sub> , S <sub>1</sub>            | 13         | 15               | 15  | 17     | ns   |

| ORi                                        | 14         | 14               | 15  | 15     | ns   |

| Cn                                         | -          | 11               | -   | 12     | ns   |

| ZERO                                       | 14         | 14               | 15  | 15     | ns   |

| OE LOW (enable)                            | 14         |                  | 15  |        | ns   |

| OE HIGH (disable) <sup>(1)</sup>           | 14         |                  | 15  |        | ns   |

| Clock $\uparrow S_1 S_0 = LH$              | 17         | 17               | 19  | 19     | ns   |

| Clock † S <sub>1</sub> S <sub>0</sub> = LL | 17         | 17               | 19  | 19     | ns   |

| Clock † S <sub>1</sub> S <sub>0</sub> = HL | 17         | 17               | 19  | 19     | ns   |

#### NOTE: 1. $C_L = 5pF$

TABLE III **GUARANTEED SET-UP AND HOLD TIMES (1)**

|                                | COMMERCIAL     |              | MILI           |              |      |

|--------------------------------|----------------|--------------|----------------|--------------|------|

| FROM INPUT                     | SET-UP<br>TIME | HOLD<br>TIME | SET-UP<br>TIME | HOLD<br>TIME | UNIT |

| RE                             | 6              | 2            | 7              | 3            | ns   |

| R <sub>i</sub> (2)             | 6              | 2            | 7              | 3            | ns   |

| PUP                            | 9              | 2            | 10             | 3            | ns   |

| FE                             | 9              | 2            | 10             | 3            | ns   |

| Cn                             | 6              | 2            | 7              | 3            | ns   |

| Di                             | 8              | 0            | 9              | 0            | ns   |

| OR                             | 8              | 0            | 9              | 0            | ns   |

| S <sub>0</sub> ,S <sub>1</sub> | 11             | 0            | 12             | 0            | ns   |

| ŽERO                           | 7              | 0            | 8              | 0            | ns   |

#### NOTES:

- 1. All times relative to clock LOW-to-HIGH transition.

- 2. On IDT39C11, R<sub>i</sub> and D<sub>i</sub> are internally connected together and labeled  $D_{i}$  . Use  $R_{i}$  set-up and hold times when D inputs are used to load register.

# IDT39C09A/IDT39C11A SWITCHING CHARACTERISTICS OVER OPERATING RANGE

Table I, II and III below define the timing characteristics of the IDT39C09A/11A over the operating voltage and temperature ranges. The tables are divided into three types of parameters: clock characteristics, combinational delays from inputs to outputs and set-up and hold time requirements. The latter table defines the time prior to the end of the cycle (i.e., clock LOW-to-HIGH transition) that each input must be stable to guarantee that the correct data is written into one of the internal registers.

Measurements are made at 1.5V with  $V_{\rm IL}=0V$  and  $V_{\rm IH}=3.0V$ . For three-state disable tests,  $C_{\rm L}=5.0{\rm pF}$  and measurement is to 0.5V change on output voltage level. All outputs have maximum DC loading.

TABLE I CYCLE TIME AND CLOCK CHARACTERISTICS

| TIME                    | COMMERCIAL | MILITARY |  |

|-------------------------|------------|----------|--|

| Minimum Clock LOW Time  | 20         | 20       |  |

| Minimum Clock HIGH Time | 20         | 20       |  |

TABLE II MAXIMUM COMBINATIONAL PROPAGATION DELAYS

C<sub>L</sub> = 50pF (except output disable test)

|                                            | COMMERCIAL |                  | MILI | UNIT   |         |

|--------------------------------------------|------------|------------------|------|--------|---------|

| FROM INPUT                                 | Y          | C <sub>n+4</sub> | Y    | Cn + 4 | L CINIT |

| Di                                         | 17         | 22               | 20   | 25     | ns      |

| S <sub>0</sub> , S <sub>1</sub>            | 29         | 34               | 29   | 34     | ns      |

| OR <sub>1</sub>                            | 17         | 22               | 20   | 25     | ns      |

| Cn                                         |            | 14               | _    | 16     | ns      |

| ZERO                                       | 29         | 34               | 30   | 35     | ns      |

| OE LOW (enable)                            | 25         | _                | 25   |        | ns      |

| OE HIGH (disable) <sup>(1)</sup>           | 25         |                  | 25   |        | ns      |

| Clock † S <sub>1</sub> S <sub>0</sub> = LH | 39         | 44               | 45   | 50     | ns      |

| Clock † S <sub>1</sub> S <sub>0</sub> = LL | 39         | 44               | 45   | 50     | ns      |

| Clock † S <sub>1</sub> S <sub>0</sub> = HL | 44         | 49               | 53   | 58     | ns      |

### NOTE:

1.  $C_L = 5pF$

TABLE III

GUARANTEED SET-UP AND HOLD TIMES (1)

|                                | СОММ           | ERCIAL       | MILI           | i İ          |      |

|--------------------------------|----------------|--------------|----------------|--------------|------|

| FROM INPUT                     | SET-UP<br>TIME | HOLD<br>TIME | SET-UP<br>TIME | HOLD<br>TIME | UNIT |

| RE                             | 19             | 4            | 19             | 5            | ns   |

| R <sub>1</sub> (2)             | 10             | 4            | 12             | 5            | ns   |

| PUP                            | 25             | 4            | 27             | 5            | ns   |

| FE                             | 25             | 4            | 27             | 5            | ns   |

| Cn                             | 18             | 4            | 18             | 5            | ns   |

| Di                             | 25             | 0            | 25             | 0            | ns   |

| OR                             | 25             | 0            | 25             | 0            | ns   |

| S <sub>0</sub> ,S <sub>1</sub> | 25             | 0            | 29             | 0            | ns   |

| ZERO                           | 25             | 0            | 29             | 0            | ns   |

#### NOTES:

- All times relative to clock LOW-to-HIGH transition.

- On IDT39C11, R<sub>1</sub> and D<sub>1</sub> are internally connected together and labeled D<sub>1</sub>. Use R<sub>1</sub> set-up and hold times when D inputs are used to load register.

#### **TEST LOAD CIRCUIT**

Figure 9. Switching Test Circuit (all outputs)

# TEST SWITCH Open Drain Disable Low Closed Enable Low All other Outputs Open

#### DEFINITIONS

$C_L$  = Load capacitance: includes jig and probe capacitance.

R<sub>T</sub> = Termination resistance: should be equal to Z<sub>OUT</sub> of the Pulse Generator.

## **SWITCHING WAVEFORMS**

# **AC TEST CONDITIONS**

| AG 1201 CONDITIONS            |              |  |

|-------------------------------|--------------|--|

| Input Pulse Levels            | GND to 3.0V  |  |

| Input Rise/Fall Times         | 1V/ns        |  |

| Input Timing Reference Levels | 1.5V         |  |

| Output Reference Levels       | 1.5V         |  |

| Output Load                   | See Figure 9 |  |

|                               |              |  |

8

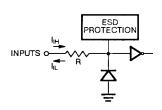

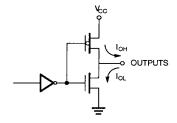

# INPUT/OUTPUT INTERFACE CIRCUITRY

Figure 10. Input Structure

Figure 11. Output Structure

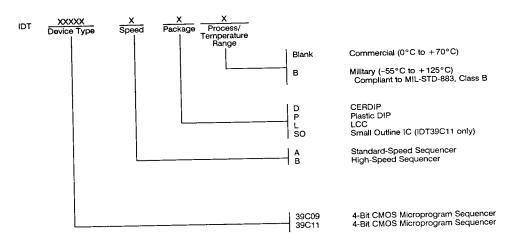

# ORDERING INFORMATION