## 4-BIT CMOS MICROPROCESSOR SLICE

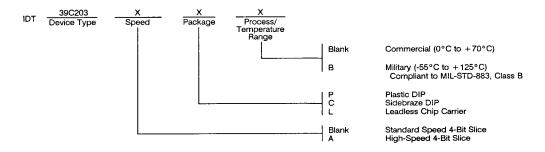

IDT39C203 IDT39C203A

MICROSLICE™ PRODUCT

#### **FEATURES:**

- Fast

- IDT39C203 matches 29203 speeds

- IDT39C203A 20% speed upgrade

- Low-power CMOS

- Military: 55mA (max.)

- Commercial: 50mA (max.)

- Pin-compatible, performance-enhanced functional replacement for the 29203

- Cascadable to 8, 12, 16, etc. bits

- Infinitely expandable register file

- Improved I/O capability

- DA, DB and Y ports are bidirectional

- Performs BCD arithmetic

- Features automatic BCD add, subtract and conversion between binary and BCD

- On-chip parity generation and sign extension logic

- On-chip normalization logic

- On-chip multiplication division logic

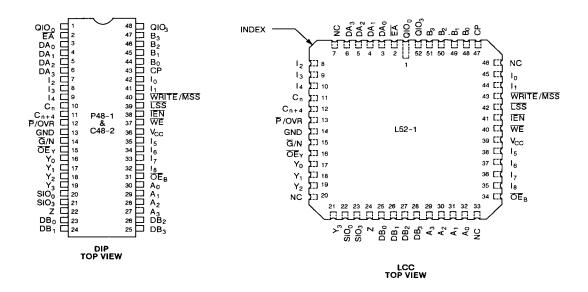

- Packaged in 48-pin plastic and sidebraze DIP, 52-pin LCQ

- Military product available compliant to MIL-STD-883, Class

### **DESCRIPTION:**

The IDT39C203s are four expandable, high-performance CMOS microprocessor slices. All g with the standard features associated with the IDT39C203s also incorporate addition employees are ments for arithmetic-oriented processors.

igh-speed three-port three-ad-These extremely ly ors consist of a 16-word by 4-bit dress architectured on both outputs, high-performance dual-port RAM gister with shifter input, and nine-bit ALU and shifter, a nally, special instructions which allow instruction de of multiplication, division, normalization, the easy imple priversion are standard on the IDT39C203s. BCD arith ly expandable in 4-bit increments. Both device

The tre propagation of the propa

The N=9C203s are fabricated using CEMOS™, CMOS technical designed for high-performance and high-reliability.

Mixery grade product is manufactured in compliance with the latest revision of MIL-STD-883, Class B, making it ideally suited to litary temperature applications demanding the highest level of softenance and reliability.

CEMOS and MICROSLICE are trademarks of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

**DECEMBER 1987**

© 1987 Integrated Device Technology, Inc.

8-74

DSC-9006/-

#### PIN DESCRIPTION

| PIN NAME                             | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> - A <sub>3</sub>      |     | Four address inputs to the RAM containing the address of the RAM word appearing at output port A.                                                                                                                                                                                                                                                                                         |

| B <sub>0</sub> - B <sub>3</sub>      | 1   | Four address inputs to the RAM which selects one of the words in the RAM, the contents of which is displayed through the B port, it also selects the location into which new data can be written when the WE input and CP input are low.                                                                                                                                                  |

| DA <sub>0-3</sub>                    | 1/0 | Four-bit bidirectional data pins for entering external data into the ALU. The DA lines act as either RAM port A output data or as input operand R to the ALU.                                                                                                                                                                                                                             |

| DB <sub>0-3</sub>                    | 1/0 | Four-bit bidirectional data pins for entering external data into the ALU. The DB lines act as either RAM port B output data or as input operand S to the ALU.                                                                                                                                                                                                                             |

| WÉ                                   | ı   | The RAM write enable input which, when LOW, causes the Y I/O port data to be written into the RAM when the CP input is low. When WE is HIGH, writing data into the RAM is inhibited.                                                                                                                                                                                                      |

| ĒĀ                                   | ı   | Enable input which, when HiGH, selects $DA_{0-3}$ as the ALU R operand and, when LOW, selects RAM output A as the ALU loperand and the DA $_{0-3}$ output data.                                                                                                                                                                                                                           |

| OEB                                  | Ī   | Output enable, which, when HIGH selects $DB_{0-3}$ as the ALU S operand, and, when LOW, selects RAM output B as the ALU S operand and the $DB_{0-3}$ output data.                                                                                                                                                                                                                         |

| SIO <sub>0,</sub> - SIO <sub>3</sub> | 1/0 | Bidirectional serial shift inputs/outputs for the ALU shifter. $SIO_0$ is an input $SIO_3$ an output during a shift-up operation. $SIO_3$ is an input and $SIO_0$ an output during a shift-down operation. Refer to Tables 3 and 4 for an exact definition of of these pins.                                                                                                              |

| QIO <sub>0.</sub> – QIO <sub>3</sub> | 1/0 | Bidirectional serial shift inputs/outputs for the ALU shifter. They operate like the SIO <sub>0</sub> and SIO <sub>3</sub> pins. Refer to Tables 3 and 4 for an exact definition of these pins.                                                                                                                                                                                           |

| Cn                                   | 1   | Carry-in input to the ALU.                                                                                                                                                                                                                                                                                                                                                                |

| ĪĒN                                  | I   | Instruction enable input. When LOW, it enables writing into the O register and the Sign Compare flip-flop and RAM. When HIGH, the O register and the Sign Compare flip-flop are in hold mode. On the IDT39C203, EIN does not affect WRIT but internally disables the RAM write enable.                                                                                                    |

| LSS                                  | ı   | Input pin, when held LOW, causes the chip to act as the Least Significant Slice (LSS) of an IDT39C203 array and enable the WRITE output onto the WRITE/MSS pin. When LSS is held HIGH, the chip acts as either an Intermediate or Most Significant Slice (MSS) and the WRITE output buffer is disabled.                                                                                   |

| WRITE/MSS                            | I/O | The write output signal appears at this pin when LSS is held LOW. When an instruction which causes data to be written into the RAM is being executed, the WRITE signal is LOW. When LSS is HIGH, WRITE/MSS is an input pin; holding it HIGH program the chip to operate as an Intermediate Slice (IS) and holding it LOW programs the chip to operate as the Most Significal Slice (MSS). |

| C <sub>n+4</sub>                     | 0   | This output indicates the carry-out of the ALU. Refer to Table 5 for an exact definition of this pin.                                                                                                                                                                                                                                                                                     |

| Z                                    | 1/0 | An open collector input/out pin, When HIGH, it indicates that all outputs are LOW. Z is used as an input pin for some spec functions. Refer to Table 5 for an exact definition of this pin.                                                                                                                                                                                               |

| Ğ/N                                  | 0   | G indicates the carry generate function at the Least Significant and Intermediate slices and indicates the sign (N) of the ALU result at the Most Significant Slice. Refer to Table 5 for an exact definition of this pin.                                                                                                                                                                |

| ŌĒ <sub>Y</sub>                      | '   | A control input pin. When LOW the ALU shifter output data is enabled onto the $Y_{0-3}$ lines. When HIGH the $Y_{0-3}$ three-strouput buffers are disabled.                                                                                                                                                                                                                               |

| СР                                   |     | Clock input to the IDT39C203. The Sign Compare flip-flop and the Q register are clocked on the LOW-to-HIGH transition of the CP signal. When enabled by WE and CP is LOW, data is written in the RAM.                                                                                                                                                                                     |

| P/OVR                                | 0   | P indicates the carry propagate function at the Least Significant and Intermediate slices and indicates the conventional two complement overflow (OVR) signal at the Most Significant Slice. Refer to Table 5 for an exact definition of this pin.                                                                                                                                        |

| Y <sub>0-3</sub>                     | 1/0 | Four data inputs/outputs of the IDT39C203. Controlled by the $\overline{\sf OE}_{\sf Y}$ input, the ALU shifter output data can be enabled or these lines or external data is written directly into the RAM using these lines as data inputs.                                                                                                                                             |

| l <sub>0-8</sub>                     | 1   | The nine instruction inputs used to select the IDT39C203 operation to be performed.                                                                                                                                                                                                                                                                                                       |

#### **DEVICE ARCHITECTURE**

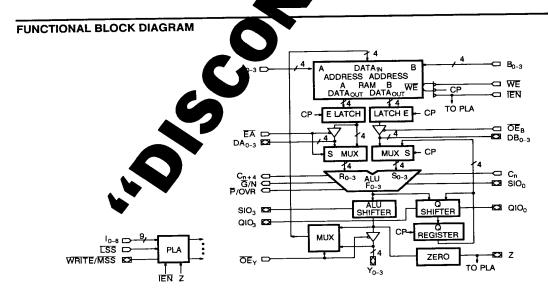

The IDT39C203 is a CMOS high-performance 4-bit microprocessor slice cascadable to any number of bits (8, 12, 16, etc.). Its versatile microinstructions allow emulation of virtually any digital computer. The ALU sources, function and destination can be selected by the 9-bit microinstruction set. Key elements which make up this 4-bit microprocessor slice are: (1) the RAM file (a 16x4 dual-port RAM) with latches on both outputs, (2) high-performance ALU with shifter, (3) a flexible Q register with shifter input and (4) a nine-bit instruction decoder.

#### RAM FILE

RAM data is read from the A port as controlled by the 4-bit A address field input. Simultaneously, data can be read from the B port as defined by the 4-bit B address field input. If the same address is applied at both the A input field and the B input field, identical data will appear at the two respective output ports. Data is written into the RAM when  $\overline{\rm WE}$  and  $\overline{\rm IEN}$  are both LOW and the clock CP is LOW. Both the RAM output data latches are transparent, while the clock pulse CP is HIGH and latches the data when CP is low.

New data is written into the RAM word defined by the B address field. External data at the Y I/O port can be written directly into the RAM or ALU shifter output data can be enabled onto the Y I/O port and written into the RAM. The three-state output enable  $\overline{OE}_B$  allows RAM B port data to be read at the DB I/O port, while  $\overline{EA}$  performs the same function for the A port data the DA I/O port.

#### ALU

The ALU can perform seven arithmetic and nine logic operations on the two 4-bit input words S and R. Multiplexers at the ALU inputs allow selection of various pairs of ALU source operands. The  $\overline{\mathbb{E}}A$  input selects either external DA data or RAM A-port output data as the 4-bit R source operand. The  $\overline{\mathbb{OE}}_B$  and  $I_0$  inputs provide selection of either RAM B port output or external DB data or the Q register output as the 4-bit S source operand. Also, during certain ALU operations, zeros are forced at the ALU operand inputs. Thus, the ALU can operate on data from two external sources, from an external and an internal source or from two internal sources. Table 1 shows all possible pairs of source operands as selected by  $\overline{\mathbb{E}}A$ ,  $\overline{\mathbb{OE}}_B$  and  $I_0$  inputs.

Table 1. ALU Operand Sources (1)

| Table 1. ALO Operand Sources |                |                 |                   |                   |  |  |  |  |  |  |

|------------------------------|----------------|-----------------|-------------------|-------------------|--|--|--|--|--|--|

| EA                           | I <sub>0</sub> | OE <sub>8</sub> | ALU OPERAND R     | ALU OPERAND S     |  |  |  |  |  |  |

| L                            | L              | L               | Ram Output A      | Ram Output B      |  |  |  |  |  |  |

| L                            | L              | н               | Ram Output A      | DB <sub>0-3</sub> |  |  |  |  |  |  |

| L                            | Н              | х               | Ram Output A      | Q Register        |  |  |  |  |  |  |

| Н                            | L              | L               | DA <sub>0-3</sub> | Ram Output B      |  |  |  |  |  |  |

| Н                            | L              | н               | DA <sub>0-3</sub> | DB <sub>0-3</sub> |  |  |  |  |  |  |

| Н                            | Н              | ×               | DA <sub>0-3</sub> | Q Register        |  |  |  |  |  |  |

#### Note:

1. L= LOW, H=HIGH, X=DON'T CARE

The ALU performs special functions when instruction bits  $l_3$ ,  $l_2$ , and  $l_0$  are LOW. Table 4 defines these special functions and the operation which the ALU performs for each. When the ALU executes instructions other than the special functions, the operation is defined by instruction bits  $l_a$ ,  $l_3$ ,  $l_2$  and  $l_1$ . Table 2 defines the operation as a function of these four instruction bits.

The IDT 39C203 may be cascaded in either a ripple carry or lookahead carry fashion. When configured as cascaded ALUs, the IDT39C203s must be programmed to be a Most Significant Slice (MSS), an Intermediate Slice (IS) or a Least Significant Slice (LSS) of the array. The carry generate ( $\overline{G}$ ) and carry propagate ( $\overline{P}$ )

signals that are necessary in a cascaded system are available as outputs on the IDT39C203 Least Significant and Intermediate slices.

The IDT39C203 provides a carry-out signal  $(C_{n+4})$  which is available as an output of each slice. The carry-in  $(C_n)$  and carry-out  $(C_{n+4})$  are both active HIGH. Two other status outputs are generated by the ALU. These are the negative (N) and the overflow (OVR). The N output indicates positive or negative results, while the OVR output indicates that the arithmetic operation performed exceeded the available two's complement range. Thus, the pins  $\overline{G}/N$  and  $\overline{P}/OVR$  indicate carry generate or propagate on the Least Significant and Intermediate slices and sign and overflow on the Most Significant Slice. Refer to Table 5 for an exact definition of these four signals.

Table 2, IDT39C203 ALU Functions(1)

| 14 | 13 | 12 | 11 | I <sub>0</sub> | ALU FUNCTIONS                                    |

|----|----|----|----|----------------|--------------------------------------------------|

| L  | L  | L  | L  | L              | Special Functions                                |

| L  | L  | L  | L  | Н              | F <sub>I</sub> = HIGH                            |

| L  | L  | L  | H  | Х              | F=S-R-1+C <sub>n</sub>                           |

| L  | L  | Η  | L  | Х              | F = R-S-1 + C <sub>n</sub>                       |

| L  | L  | Н  | H  | Х              | F=R+S+C <sub>n</sub>                             |

| L  | H  | L  | L  | х              | F=S+C <sub>n</sub>                               |

| L  | н  | L  | Н  | Х              | $F = \overline{S} + C_n$                         |

| L  | Н  | н  | L  | L              | Reserved Special Functions                       |

| L  | H. | н  | L  | Н              | F = R + C <sub>n</sub>                           |

| L  | н  | Н  | н  | L              | Reserved Special Functions                       |

| L  | н  | н  | н  | н              | F=R+Cn                                           |

| L. | н  | н  | н  | L              | Special Functions                                |

| Н  | L  | L  | Ł  | Н              | F <sub>i</sub> =LOW                              |

| Н  | L  | L  | н  | Х              | F <sub>I</sub> = Ri AND S <sub>I</sub>           |

| Н  | L  | Н  | L  | Х              | F <sub>i</sub> = Ri EXCLUSIVE NOR S <sub>1</sub> |

| Н  | L  | н  | Н  | Х              | F = Ri EXCLUSIVE OR S                            |

| Н  | Н  | L  | L  | Х              | F <sub>1</sub> = Ri AND S <sub>1</sub>           |

| Н  | Н  | L  | Н  | Х              | F <sub>I</sub> = Ri NOR S <sub>i</sub>           |

| н  | Н  | н  | L  | х              | F <sub>i</sub> = Ri NAND S <sub>i</sub>          |

| Н  | Н  | Н  | Н  | Х              | F <sub>i</sub> = Ri OR S <sub>i</sub>            |

#### Note:

1. L= LOW, H=HIGH, i = 0 to 3, X = DON'T CARE

#### **ALU SHIFTER**

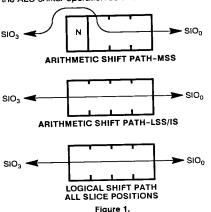

The ALU shifter shifts the ALU output data under instruction control. It can shift up one bit position (2F), shift down one bit position (F/2) or pass the ALU output non-shifted (F). An arithmetic shift operation shifts the data around the Most Significant (sign) Bit of the Most Significant Slice and a logical shift operation shifts the data through the Most Significant Bit. Figure 1 shows these shift patterns. The SlO0 and SlO3 are bidirectional serial shift input/output pins. During a shift-up operation, SlO0 is generally an input while SlO3 is an output; whereas, during a shift-down operation, SlO0 is generally an output while SlO3 acts as an input. Refer to Tables 3 and 4 for an exact definition of these pins.

The ALU shifter also provides sign extension and parity generating/checking capabilities. Under instruction control, the  $SIO_0$  (sign) input can be extended through  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$  and be propagated to the  $SIO_3$  output. A cascadable, five-bit parity generator/checker generates parity for the  $F_0$ ,  $F_1$ ,  $F_2$  and  $F_3$  ALU outputs, the  $SIO_3$  input and, under instruction control, is made

available at the  $SIO_0\,$  output. Table 4 defines the special functions and the operation the ALU shifter performs for each instruction. For instructions other than the special functions, the ALU shifter operation is determined by instruction bits  $l_8$  ,  $l_7$  ,  $l_8$  and  $l_5$  . Table 3 defines the ALU shifter operation as a function of these four bits.

#### Q REGISTER FILE

The Q register is a separate 4-bit file intended primarily for multiplication and division routines and can also be used as an accumulator or holding register for other types of applications. The ALU output (F) can be loaded into the Q register and/or the Q register can be selected as one of the ALU S operands. The shifter at the input to the Q register performs only logical shifts. It can shift-up the data one bit position (2Q) or down one bit position (Q/2). For a shift-up operation,  $QIO_0$  acts as an input while  $QIO_3$  acts as an output; whereas for a shift-down operation QIOo is an output and  ${\rm QIO_3}$  is an input. By connecting  ${\rm QIO_3}$  of the Most Significant Slice to SIOo of the Least Significant Slice, double-length arithmetic and logical shifting is possible with cascaded IDT39C203s.

Table 4 defines the special functions and the operations which the Q register and the shifter performs for selected instruction inputs. While executing instructions other than the special functions, the Q register and the shifter operation is controlled by instruction bits  $\bar{l_8}$ ,  $\bar{l_7}$ ,  $\bar{l_6}$  and  $\bar{l_5}$ . Table 3 defines the Q register and shifter operation as a function of these four bits.

Table 3. ALU Destination Control for I nor I 1 or I 2 or I 3 = HIGH, IEN = LOW (1)

| Ta       | able 3. ALU Destination Control for I or |        |     |                                                  |                                                       |                  |                |                         |                  |                                      |                |                |                  |                |               |                                |                  |                  |

|----------|------------------------------------------------------------------------|--------|-----|--------------------------------------------------|-------------------------------------------------------|------------------|----------------|-------------------------|------------------|--------------------------------------|----------------|----------------|------------------|----------------|---------------|--------------------------------|------------------|------------------|

|          | 1.                                                                     | اء     | i,  | HEX                                              | ALU<br>SHIFTER                                        |                  | OTHER          | MOST SIG.               | OTHER<br>SLICES  | Y <sub>2</sub><br>MOST SIG.<br>SLICE |                | Y,             | ٧,               | sio,           | WRITE<br>/MSS | Q REG &<br>SHIFTER<br>FUNCTION | QIO <sub>3</sub> | QIO <sub>0</sub> |

| Ľ        | Ľ                                                                      | ├-     | -   |                                                  |                                                       | SLICE            | SLICES         | SLICE<br>F <sub>3</sub> | SIO              | SIO <sub>3</sub>                     | F <sub>3</sub> | F <sub>2</sub> | F <sub>1</sub>   | Fo             | L             | Hold                           | z                | z                |

| L        | L                                                                      | 느      | L   | 0                                                | Arith F/2→Y                                           | Input            | Input          |                         |                  |                                      | H              |                | F <sub>1</sub>   | Fo             | L             | Hold                           | z                | z                |

| L        | L                                                                      | L      | Н   | 1                                                | Log. F/2→Y                                            | Input            | Input          | SIO <sub>3</sub>        | SIO <sub>3</sub> | F <sub>3</sub>                       | Fa             | F <sub>2</sub> |                  | _ <u> </u>     |               |                                | Input            | Q <sub>0</sub>   |

| L        | <u> </u> L                                                             | н      | L   | 2                                                | Arith. F/2→Y                                          | Input            | Input          | F <sub>3</sub>          | SIO <sub>3</sub> | SIO <sub>3</sub>                     | F <sub>3</sub> | F <sub>2</sub> | F <sub>1</sub>   | Fo             | L             | Log. Q/2<br>→ Q                | input            | _ <del>4</del> 0 |

| 1        | L                                                                      | Н      | н   | 3                                                | Log. F/2→Y                                            | Input            | Input          | SIO <sub>3</sub>        | SIO <sub>3</sub> | F <sub>3</sub>                       | F <sub>3</sub> | F <sub>2</sub> | F <sub>1</sub>   | F <sub>0</sub> | L             | Log. Q/2<br>→ Q                | Input            | O <sub>0</sub>   |

| 1        | Н                                                                      | t      | L   | 4                                                | F→Y                                                   | Input            | Input          | F <sub>3</sub>          | F <sub>3</sub>   | F <sub>2</sub>                       | F <sub>2</sub> | F <sub>1</sub> | F <sub>0</sub>   | Parity         | L_            | Hold                           | Z                | Z                |

| L        | H                                                                      | L      | +-  | 5                                                | F→Y                                                   | Input            | Input          | F <sub>3</sub>          | F <sub>3</sub>   | F <sub>2</sub>                       | F <sub>2</sub> | F <sub>1</sub> | Fo               | Parity         | н             | Log. Q/2<br>→ Q                | Input            | O <sub>0</sub>   |

| h        | ╁                                                                      | ╁      | 1 L | 6                                                | F-→Y                                                  | Input            | Input          | F <sub>3</sub>          | F <sub>3</sub>   | F <sub>2</sub>                       | F <sub>2</sub> | F <sub>1</sub> | F <sub>0</sub>   | Parity         | Н             | F→Q                            | Z                | Z                |

|          | ╄                                                                      | 1-     | 1 1 | <b>├</b> ─                                       | F→Y                                                   | Input            | Input          | F <sub>3</sub>          | F <sub>3</sub>   | F <sub>2</sub>                       | F <sub>2</sub> | F <sub>1</sub> | Fo               | Parity         | L             | F→Q                            | Z                | Z                |

| -        |                                                                        | t      | ١.  | 8                                                | Arith . 2F→Y                                          | F <sub>2</sub>   | F <sub>3</sub> | F <sub>3</sub>          | F <sub>2</sub>   | F <sub>1</sub>                       | F <sub>1</sub> | F <sub>0</sub> | SIO <sub>0</sub> | Input          | L             | Hold                           | Z                | Z                |

| $\vdash$ | †-                                                                     | 十      | -   | <del>                                     </del> | Log. 2F→Y                                             | F <sub>3</sub>   | F <sub>3</sub> | F <sub>2</sub>          | F <sub>2</sub>   | F <sub>1</sub>                       | Fı             | F <sub>0</sub> | SIO <sub>0</sub> | input          | L             | Hold                           | z_               | Z                |

| $\vdash$ | $^{+}$                                                                 | †-     | L   | T                                                | Arith. F/2→Y                                          |                  | F <sub>3</sub> | F <sub>3</sub>          | F <sub>2</sub>   | F <sub>1</sub>                       | F <sub>1</sub> | F <sub>0</sub> | SIO <sub>0</sub> | Input          | L             | Log. 2Q<br>→ Q                 | C <sub>3</sub>   | Input            |

| -        | 1.                                                                     | <br> - | 1 1 | В                                                | Log. F/2→Y                                            | F <sub>3</sub>   | F <sub>3</sub> | F <sub>2</sub>          | F <sub>2</sub>   | F <sub>1</sub>                       | F <sub>1</sub> | F <sub>0</sub> | SIO <sub>0</sub> | Input          | L             | Log. 2Q<br>→ Q                 | 0,               | Input            |

| L        | 1 1                                                                    | ┸      | 1_  | ↓                                                | F→Y                                                   | F <sub>3</sub>   | F <sub>3</sub> | F <sub>3</sub>          | F <sub>3</sub>   | F <sub>2</sub>                       | F <sub>2</sub> | F <sub>1</sub> | F <sub>0</sub>   | Z              | Н             | Hold                           | Z                | Z                |

| $\vdash$ | , '                                                                    | ╁      | +   | +                                                | F→Y                                                   | F <sub>3</sub>   | F <sub>3</sub> | F <sub>3</sub>          | F <sub>3</sub>   | F <sub>2</sub>                       | F <sub>2</sub> | F <sub>1</sub> | F <sub>0</sub>   | z              | н             | Log. 2Q<br>-→ Q                | Q3               | Input            |

| H        | 1 +                                                                    | +      | ╁   | _ E                                              | $SIO_0 \rightarrow Y_0,$<br>$Y_1 \cdot Y_2 \cdot Y_3$ | SIO <sub>0</sub> | SIO            | SIO                     | SIO              | SIO <sub>0</sub>                     | sio,           | SIO            | SIO              | Input          | L             | Hold                           | z                | z                |

| +        | +                                                                      | +      | Н   | - F                                              | F→Y                                                   | F <sub>3</sub>   | F <sub>3</sub> | F <sub>3</sub>          | F <sub>3</sub>   | F <sub>2</sub>                       | F <sub>2</sub> | F <sub>1</sub> | Fo               | Z              | L             | Hold                           | Z                | Z                |

NOTE:

1. Parity =  $F_3 \nabla F_2 \nabla F_1 \nabla F_0 \nabla SIO_3$ ,

L = LOW

Z = High Impedance

H = HIGH

#### INSTRUCTION DECODER

The internal control signals necessary for the operation of the IDT39C203 are generated by the instruction decoder as a function of the nine instruction inputs, Io-a; the instruction enable input, IEN; the LSS input; and the MSS/WRITE input/output.

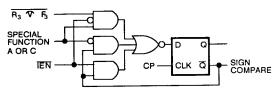

The WRITE output is LOW when an instruction which writes data into the RAM is executed. Refer to Tables 3 and 4 for a definition of the WRITE output as a function of the instruction inputs. When IEN is HIGH, the WRITE output is forced HIGH and the Q register and Sign Compare flip-flop contents are preserved. When IEN is LOW, the WRITE output is enabled and the Q register and Sign Compare flip-flop can be written according to the IDT39C203s instruction. The Sign Compare flip-flop shown in Figure 2 is an on-chip flip-flop which is used during a divide operation.

Figure 2. Sign Compare Flip-Flop

#### SLICE POSITION PROGRAMMING

Holding the LSS pin LOW programs the IDT39C203 slice (LSS) and enables the WRITE output signal onto the MSS/WRITE I/O pin. When LSS is tied HIGH, the MSS/WRITE pin becomes an input tying MSS/WRITE LOW programs the slice to operate as the Most Significant Slice (MSS); tying it HIGH causes the slice to operate as an Intermediate Slice. The MSS/WRITE pin should be tied HIGH through a resistor, independent of the LSS pin.

#### SPECIAL FUNCTIONS

Sixteen special functions are provided on the IDT39C203 which permit the implementation of the following operations:

- Single and double length normalization

- Two's complement division

- Unsigned and two's complement multiplication

- Conversion between two's complement and sign/magnitude representation

- Incrementation and decrementation by one or two

- . BCD add, subtract, and divide by two

- Single and double-precision BCD-to binary and binary-to-BCD conversion

Adjusting a single-precision or double-precision floating-point number in order to bring its mantissa within a specified range can be performed using the single-length and double-length normalization operations. Three special functions can be used to perform a two's complement, non-restoring divide operation. They provide single and double-precision divide operations and can be performed in "n" clock cycles (where "n" is the number of bits in the quotient).

The unsigned multiply special function and the two two's complement multiply special functions can be used to multiply two n-bit, unsigned or two's complement numbers, respectively, in "n" clock cycles. During the last cycle of the two's complement multiplication, a conditional subtraction, rather than addition, is performed due to the fact that the sign bit of the multiplier carries negative weight.

The sign/magnitude two's complement special function can be used to convert number representation systems. A number expressed in sign/magnitude representation can be converted to the two's complement representation, and vice-versa, in one clock cycle. Incrementing an unsigned or two's complement number by one or two is easily accomplished using the increment by one or two special functions.

In addition to BCD arithmetic special functions to add or subtract two BCD numbers, a BCD divide by two adjust instructions can be used to obtain a valid BCD representation after shifting a number down by one bit. The BCD/binary conversion special function instructions permit single and double-precision algorithms to convert from BCD-to-binary and from binary-to-BCD.

Table 4. Special Functions (7,8)

|     | le 4. Special i dilettorio |     |                                                        | <del></del>                                                                 |                          |                     | SIO <sub>3</sub> |                | O REGISTER     |                |                |               |

|-----|----------------------------|-----|--------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------|---------------------|------------------|----------------|----------------|----------------|----------------|---------------|

| HEX | l <sub>a</sub>             | HEX | SPECIAL FUNCTION                                       | ALU<br>FUNCTION                                                             | ALU SHIFTER<br>FUNCTION  | MSS                 | OTHER<br>SLICES  | SIO            |                | QIO₃           | OlO⁰           | WRITE<br>/MSS |

| 0   | L                          | 0   | Unsigned Multiply                                      | F=S+C <sub>n</sub> if Z=L<br>F=R+S+C <sub>n</sub> if Z=H                    | Log F/2→Y <sup>(1)</sup> | х                   | Input            | Fo             | Log Q/2<br>→ Q | Input          | O <sub>O</sub> | L             |

| 1   |                            | 0   | BCD to Binary<br>Conversion                            | Note 4                                                                      | Log F/2→Y                | Input               | Input            | Fo             | Log Q/2<br>→ Q | Input          | a <sub>o</sub> | L             |

| 1   | н                          | 0   | Multiprecision<br>BCD to Binary                        | Note 4                                                                      | Log F/2→Y                | Input               | Input            | Fo             | Hold           | Х              | Q <sub>0</sub> | L             |

| 2   | L                          | 0   | Two's Complement<br>Multiply                           | $F=S+C_n$ if $Z=L$<br>$F=R+S+C_n$ if $Z=H$                                  | Log F/2→Y <sup>(2)</sup> | ×                   | Input            | Fo             | Log Q/2<br>→ Q | Input          | Q <sub>o</sub> | L             |

| 3   | L                          | 0   | Decrement by<br>One or Two                             | F=S-2+C <sub>n</sub>                                                        | F→Y                      | Input               | Input            | Parity         | Hold           | X              | Х              | L             |

| 4   | L                          | 0   | Increment by<br>One or Two                             | F=S+1+C <sub>n</sub>                                                        | F→Y                      | Input               | Input            | Parity         | Hold           | X              | Х              | L             |

| 5   | L                          | 0   | Sign/Magnitude<br>Two's Complement                     | $F=S+C_n$ if $Z=L$<br>$F=S+C_n$ if $Z=H$                                    | F→Y <sup>(3)</sup>       | Input               | Input            | Parity         | Hold           | Х              | ×              | L             |

| 6   | L                          | 0   | Two's Complement<br>Multiply, Last Cycle               | $F=S+C_n$ if $Z=L$<br>$F=S-R-1+C_n$ if $Z=H$                                | L F/2→Y <sup>(2)</sup>   | ×                   | Input            | F <sub>0</sub> | Log Q/2<br>→ Q | Input          | O <sub>0</sub> | L             |

| 7   | L                          | 0   | BCD Divide by Two                                      | Note 4                                                                      | F→Y                      | Input               | Input            | Parity         | Hold           | X              | X              | L             |

| 8   | L                          | 0   | Single Length<br>Normalize                             | F=S+C <sub>n</sub>                                                          | F→Y                      | F <sub>3</sub>      | F <sub>3</sub>   | ×              | Log 2Q<br>→ Q  | 03             | Input          | L             |

| 9   | L                          | 0   | Binary to BCD<br>Conversion                            | Note 5                                                                      | Log 2F→Y                 | F <sub>3</sub>      | F <sub>3</sub>   | Input          | Log 2Q<br>→ Q  | Q <sub>3</sub> | Input          | L             |

| 9   | Н                          | 0   | Multiprecision<br>Binary to BCD                        | Note 5                                                                      | Log 2F→Y                 | F <sub>3</sub>      | F <sub>3</sub>   | Input          | Hold           | X              | Input          | L             |

| Α   | L                          | 0   | Double Length<br>Normalize and<br>First Divide Op      | F=S+C <sub>n</sub>                                                          | Log 2F→Y                 | R <sub>3</sub> ∕∕≻F | F <sub>3</sub>   | Input          | Log 2Q<br>→ Q  | Q <sub>3</sub> | Input          | L.            |

| В   | L                          | 0   | BCD Add                                                | $F = R + S + C_n BCD^{(6)}$                                                 | F→Y                      | 0                   | 0                | x              | Hold           | X              | x              | L             |

| С   | L                          | 0   | Two's Complement<br>Divide                             | F=S+R+C <sub>n</sub> if Z=L<br>F=S-R-1+C <sub>n</sub><br>if Z=H             | Log 2F→Y                 | R <sub>3</sub> ∕VF  | F <sub>3</sub>   | Input          | Log 2Q<br>→ Q  | Q <sub>3</sub> | Input          | L             |

| D   | L                          | 0   | BCD Subtract                                           | F = R-S-1 + C <sub>n</sub> BCD (6                                           | ) F→Y                    | 0                   | 0                | x              | Hold           | ×              | X              | L             |

| E   | L                          | 0   | Two's Complement<br>Divide Correction<br>and Remainder | $F = S + R + C_n \text{ if } Z = L$ $F = S - R - 1 + C_n \text{ if } Z = L$ | F→Y                      | F <sub>3</sub>      | F <sub>3</sub>   | ×              | Log 2Q<br>→ Q  | Q <sub>3</sub> | Input          | L             |

| F   | L                          | 0   | BCD Subtract                                           | F=S-R-1+C <sub>n</sub> BCD (6                                               | F→Y                      | 0                   | 0                | ×              | Hold           | X              | ×              | L             |

- 1. At the Most Significant Slice only, the  $C_{n+4}$  signal is internally gated to the  $Y_3$  output.

- At the Most Significant Slice only, F<sub>3</sub> ♥ OVR is internally gated to the Y<sub>3</sub> output.

- 3. At the Most Significant Slice only,  $S_3 \nabla F_3$  is generated the  $Y_3$  output.

- At the Most algrinicant slice only, 63 × 13 is generated to 13 capeta.

On each slice, F = S if magnitude of S<sub>0-3</sub> is less than 8, and F = S minus three if magnitude of S<sub>0-3</sub> is 8 or greater.

- 5. On each slice, F = S if magnitude of  $S_{0-3}$  is less than 5, and F = S plus three if magnitude of  $S_{0-3}$  is 5 or greater. Addition is modulo 16.

- 6. Additions and Subtractions are BCD adds and subtracts. Results are undefined if R or S are not in valid BCD format.

- 7. The Q register cannot be used explicitly as an operand for any special functions. It is defined implicitly within the functions.

- 8. L = LOW, H = HIGH, X = Don't Care,  $\nabla$  = Exclusive OR, PARITY = SIO  $_3\nabla F_3\nabla F_2\nabla F_1\nabla F_0$

Table 5. IDT39C203 Status Outputs

| abre             | J. 10 | . 39 | C203 Status                                                                        | Juipuis                                                                                |                     | P/OV                                              | R               | Ğ/I                                           | N               |                                                                                                                                                                                                                     | Z (OE <sub>Y</sub> = L)                                                                                                                                                                                                |                                                                                                                                                                                                                     |

|------------------|-------|------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------|---------------------------------------------------|-----------------|-----------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (HEX)            | (HEX) | 10   | Gi<br>(i = 0 to 3)                                                                 | Pi<br>(i = 0 to 3)                                                                     | Cn+4                | MOST SIG.<br>SLICE                                | OTHER<br>SLICES | MOST SIG.<br>SLICE                            | OTHER<br>SLICES | MOST SIG.<br>SLICE                                                                                                                                                                                                  | INTER-<br>MEDIATE<br>SLICE                                                                                                                                                                                             | LEAST SIG.<br>SLICE                                                                                                                                                                                                 |

| X                | 0     | ᆔ    | 0                                                                                  | 1                                                                                      | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\overline{Y_0}$ $\overline{Y_1}$ $\overline{Y_2}$ $\overline{Y_3}$                                                                                                                                                    | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| Х                | 1     | x    | R <sub>i</sub> ∧ S <sub>i</sub>                                                    | R̄₁ V S₁                                                                               | G V PCn             | C <sub>n + 3</sub> ◆<br>C <sub>n + 4</sub>        | P               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| х                | 2     | х    | R₁∧ S₁                                                                             | R <sub>I</sub> V S <sub>I</sub>                                                        | G V PCn             | C <sub>n + 3</sub> <b>7</b><br>C <sub>n + 4</sub> | P               | F <sub>3</sub>                                | ত্র             | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| Х                | 3     | x    | R <sub>i</sub> A S <sub>i</sub>                                                    | R <sub>i</sub> V S <sub>i</sub>                                                        | G V PCn             | C <sub>n + 3</sub>                                | P               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| Х                | 4     | х    | 0                                                                                  | S <sub>i</sub>                                                                         | G V PCn             | Cn + 3 T<br>Cn + 4                                | P               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| X                | 5     | х    | 0                                                                                  | । 🔻                                                                                    | G V PCn             | C <sub>n+3</sub> √<br>C <sub>n+4</sub>            | P               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| х                | 6     | н    | 0                                                                                  | R <sub>I</sub>                                                                         | G V PCn             | C <sub>n+3</sub> • C <sub>n+4</sub>               | P               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| ×                | 7     | Н    | 0                                                                                  | R <sub>i</sub>                                                                         | G V PCn             | C <sub>n+3</sub> <b>₹</b><br>C <sub>n+4</sub>     | P               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| X                | 8     | н    | 0                                                                                  | 1                                                                                      | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | ਫ               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\overrightarrow{\nabla}_0 \overrightarrow{\nabla}_1 \overrightarrow{\nabla}_2 \overrightarrow{\nabla}_3$ $\overrightarrow{\nabla}_0 \overrightarrow{\nabla}_1 \overrightarrow{\nabla}_2 \overrightarrow{\nabla}_3$ |

| X                | 9     | X    | R <sub>1</sub> A S <sub>1</sub>                                                    | 1                                                                                      | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | ত্র<br>ত্র      | $\overrightarrow{\nabla}_0 \overrightarrow{\nabla}_1 \overrightarrow{\nabla}_2 \overrightarrow{\nabla}_3$ $\overrightarrow{\nabla}_0 \overrightarrow{\nabla}_1 \overrightarrow{\nabla}_2 \overrightarrow{\nabla}_3$ | $\overrightarrow{\nabla}_0 \overrightarrow{\nabla}_1 \overrightarrow{\nabla}_2 \overrightarrow{\nabla}_3$<br>$\overrightarrow{\nabla}_0 \overrightarrow{\nabla}_1 \overrightarrow{\nabla}_2 \overrightarrow{\nabla}_3$ | $\overrightarrow{Y_0}$ $\overrightarrow{Y_1}$ $\overrightarrow{Y_2}$ $\overrightarrow{Y_3}$                                                                                                                         |

| X                | A     | X    | R <sub>1</sub> AS <sub>1</sub>                                                     | R <sub>I</sub> V S <sub>I</sub>                                                        | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | G               | $\overline{Y_0}$ $\overline{Y_1}$ $\overline{Y_2}$ $\overline{Y_3}$                                                                                                                                                 | $\overrightarrow{\nabla}_0 \overrightarrow{\nabla}_1 \overrightarrow{\nabla}_2 \overrightarrow{\nabla}_3$                                                                                                              | $\overrightarrow{\nabla}_0 \overrightarrow{\nabla}_1 \overrightarrow{\nabla}_2 \overrightarrow{\nabla}_3$                                                                                                           |

| - <del>X</del> - | 8     | X    | R <sub>I</sub> A S <sub>I</sub>                                                    | R <sub>i</sub> V S <sub>i</sub>                                                        | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | G               | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                              | $7_0 7_1 7_2 7_3$                                                                                                                                                                                                      | $\overline{Y_0}$ $\overline{Y_1}$ $\overline{Y_2}$ $\overline{Y_3}$                                                                                                                                                 |

| X                | пО    | X    | R <sub>1</sub> A S <sub>1</sub>                                                    | 1                                                                                      | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\overline{\nabla_0 \nabla_1 \nabla_2 \nabla_3}$                                                                                                                                                                    |

| X                | E     | X    | R <sub>i</sub> A S <sub>i</sub>                                                    | 1                                                                                      | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | G               | $\overline{Y_0}\overline{Y_1}\overline{Y_2}\overline{Y_3}$                                                                                                                                                          | $\overline{Y_0}$ $\overline{Y_1}$ $\overline{Y_2}$ $\overline{Y_3}$                                                                                                                                                    | $\overline{Y_0}$ $\overline{Y_1}$ $\overline{Y_2}$ $\overline{Y_3}$                                                                                                                                                 |

| X                | F     | X    | R <sub>1</sub> A S <sub>1</sub>                                                    | 1                                                                                      | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | G               | $\overrightarrow{\nabla_0}\overrightarrow{\nabla_1}\overrightarrow{\nabla_2}\overrightarrow{\nabla_3}$                                                                                                              | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | Y <sub>0</sub> Y <sub>1</sub> Y <sub>2</sub> Y <sub>3</sub>                                                                                                                                                         |

| 0                | 0     | L    | O if Z=L<br>R <sub>1</sub> A S <sub>1</sub> if<br>Z=H                              | $S_1$ if $Z=L$<br>$R_1 \vee S_1$ if $Z=H$                                              | G V PC <sub>n</sub> | C <sub>n+3</sub> T<br>C <sub>n+4</sub>            | P               | F <sub>3</sub>                                | G               | Input                                                                                                                                                                                                               | input                                                                                                                                                                                                                  | Q <sub>0</sub>                                                                                                                                                                                                      |

| 1                | 0     | L    | 0                                                                                  | S <sub>i</sub>                                                                         | G V PC <sub>n</sub> | C <sub>n+3</sub> V<br>C <sub>n+4</sub>            | P               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| 1                | 8     | L    | 0                                                                                  | S <sub>I</sub>                                                                         | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\overline{Y_0}$ $\overline{Y_1}$ $\overline{Y_2}$ $\overline{Y_3}$                                                                                                                                                    | $\overrightarrow{Y}_0 \overrightarrow{Y}_1 \overrightarrow{Y}_2 \overrightarrow{Y}_3$                                                                                                                               |

| 2                | 0     | L    | 0 if Z= L<br>R₁ ∧ S₁ if<br>Z= H                                                    | S <sub>i</sub> if Z=L<br>R <sub>i</sub> V S <sub>i</sub> if<br>Z=H                     | G V PC <sub>n</sub> | C <sub>n+3</sub> T<br>C <sub>n+4</sub>            | P               | F <sub>3</sub>                                | G               | Input                                                                                                                                                                                                               | Input                                                                                                                                                                                                                  | O <sub>O</sub>                                                                                                                                                                                                      |

| 3                | 0     | L    | Note 6                                                                             | Note 7                                                                                 | G V PC <sub>n</sub> | C <sub>n+3</sub> $\nabla$<br>C <sub>n+4</sub>     | P               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| 4                | 0     | L    | Note 1                                                                             | Note 2                                                                                 | G V PCn             | C <sub>n+3</sub> 7<br>C <sub>n+4</sub>            | P               | F <sub>3</sub>                                | ত্র             | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| 5                | 0     | L    | 0                                                                                  | S <sub>i</sub> if Z=L<br>S <sub>i</sub> if Z=H                                         | G V PCn             | l                                                 | P               | $F_3$ if $Z=L$<br>$F_3$ $\nabla S_3$ if $Z=H$ | G               | S <sub>3</sub>                                                                                                                                                                                                      | Input                                                                                                                                                                                                                  | Input                                                                                                                                                                                                               |

| 6                | 0     | L    | 0 if Z=L<br>R₁∧ S₁ if<br>Z=H                                                       | S <sub>i</sub> if Z=L<br>R <sub>i</sub> V S <sub>i</sub> if<br>Z=H                     | G V PCn             | C <sub>n+3</sub> 7<br>C <sub>n+4</sub>            | P               | F <sub>3</sub>                                | G               | Input                                                                                                                                                                                                               | Input                                                                                                                                                                                                                  | Q <sub>0</sub>                                                                                                                                                                                                      |

| 7                | 0     | L    | 0                                                                                  | Sı                                                                                     | G V PC              | Un + 4                                            | P               | F <sub>3</sub>                                | ত্র             | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| 8                | 0     | L    | 0                                                                                  | Sı                                                                                     | Note 3              | Q2 VQ1                                            | P               | Q <sub>3</sub>                                | Ğ               | $\overline{Q}_0\overline{Q}_1\overline{Q}_2\overline{Q}_3$                                                                                                                                                          | $\overline{Q}_0\overline{Q}_1\overline{Q}_2\overline{Q}_3$                                                                                                                                                             | $\overline{Q}_0\overline{Q}_1\overline{Q}_2\overline{Q}_3$                                                                                                                                                          |

| 9                | 0     | L    | 0                                                                                  | Sı                                                                                     | G V PC              | Un + 4                                            | P               | F <sub>3</sub>                                | G               | ₫₀₫₁₲₂₲₃                                                                                                                                                                                                            |                                                                                                                                                                                                                        |                                                                                                                                                                                                                     |

| 9                | 8     | ᆫ    | 0                                                                                  | S <sub>1</sub>                                                                         | 0                   | 0                                                 | 0               | F <sub>3</sub>                                | G               | $\overline{Q}_0\overline{Q}_1\overline{Q}_2\overline{Q}_3$                                                                                                                                                          | Q₀Q₁Q₂Q₃                                                                                                                                                                                                               |                                                                                                                                                                                                                     |

| Α                | 0     | L    | 0                                                                                  | Si                                                                                     | Note 4              | F <sub>2</sub> √ F <sub>1</sub>                   | P               | F <sub>3</sub>                                | G               | Note 5                                                                                                                                                                                                              | Note 5                                                                                                                                                                                                                 | Note 5                                                                                                                                                                                                              |

| В                | 0     | ┖    | R <sub>I</sub> A S <sub>I</sub>                                                    | R <sub>I</sub> V S <sub>I</sub>                                                        | G V PCn             | Note 8                                            | Note 8          | Note 9                                        | Note 9          | $\overline{Y_0}\overline{Y_1}\overline{Y_2}\overline{Y_3}$                                                                                                                                                          | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |

| С                | 0     | L    | $R_{i}\Lambda S_{i}$ if $Z=L$ $R_{i}\Lambda S_{i}$ if $Z=H$                        | R <sub>i</sub> V S <sub>i</sub> if<br>Z=L<br>R <sub>i</sub> V S <sub>i</sub> if<br>Z=H | G V PC <sub>n</sub> | C <sub>n+3</sub> <b>7</b><br>C <sub>n+4</sub>     | Þ               | F <sub>3</sub>                                | ਫ               | Sign<br>Compare<br>FF Output                                                                                                                                                                                        | Input                                                                                                                                                                                                                  | Input                                                                                                                                                                                                               |

| D                | 0     | L    | R₁∧ Š₁                                                                             | R₁ V Š₁                                                                                | G V PCn             | C <sub>n+3</sub> 7<br>C <sub>n+4</sub>            | P               | F <sub>3</sub>                                | G               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                                  | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                                                                                                                                               |