# HIGH SPEED 16-BIT REGISTER WITH SPC\*\*

# PRELIMINARY IDT49FCT618 IDT49FCT618A

### **FEATURES:**

- High-speed non-inverting 16-bit parallel data register for any data path, control path or pipelining application

- Read back path from the data output back to the data input allows for convenient interface to a microprocessor as a parallel high-speed/high-output drive I/O port

- · Clock enable and asynchronous clear lines

- High-speed Serial Protocol Channel (SPC<sup>™</sup>) which provides access to 16 bit parallel data register using four pins

- Controllability:

- Serial scan in new machine state

- Load new machine state "on the fly" synchronous with PCI K

- Temporarily force Y output bus

- Temporarily force data out the D input bus (as in loading WCS)

- Observability:

- Directly observe D and Y buses

- Serial scan out current machine state

- Capture machine state "on the fly" synchronous with PCLK

- IoL = 32mA (commercial), 24mA (military)

- CMOS power levels (5µW typ. static)

- . TTL input and output level compatible

- CMOS output level compatible

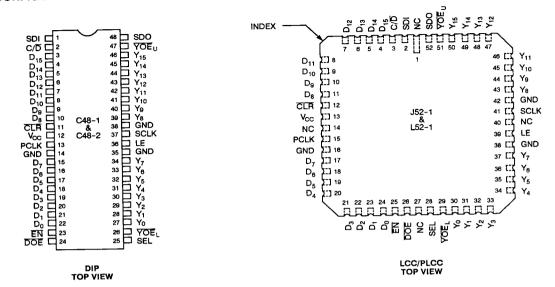

- Available in 48-pin DIP and 52-pin LCC/PLCC

- Product available in Radiation Tolerant and Enhanced versions

- Military product compliant to MIL-STD-883, Class B

### DESCRIPTION:

The IDT49FCT618/A are high-speed, general purpose 16-bit parallel data registers with a Serial Protocol Channel (SPC). The D-to-Y path of the register provides a data path that is designed for normal system operation wherever a high-speed clocked register is required. This device also incorporates a latched read back path from the Y bus to the D bus. The SPC is used to communicate with SPC command and data registers.

The SPC command and data registers are used to observe and control the operation of the 16-bit parallel data register for diagnostic purposes. The SPC command and data registers can be accessed while the system is performing normal system function. Diagnostic operations then can be performed "on the fly", synchronous with the system clock, or can be performed in the "single step" environment. The SPC port utilizes serial data in and out pins (a concept originated at IBM) which can participate in a serial scan loop throughout the system where normal data, address, status and control registers are replaced with the IDT49FCT618/A. The loop can be used to scan in a complete test routine starting point (data, address, etc.). Then, after a specified number of clock cycles, the data can be clocked out and compared with expected results. An "oscilloscope mode" can be achieved by loading data from the SPC data register into the parallel data register synchronous to the system clock (PCLK) using an SPC command which transfers data synchronously. When repeated every Nth clock, the repeating states of the system can be observed on an oscilloscope. When used as a pipeline register, Writable Control Store (WCS) loading can be accomplished by scanning in data through the SPC port and enabling the data onto the D bus pins.

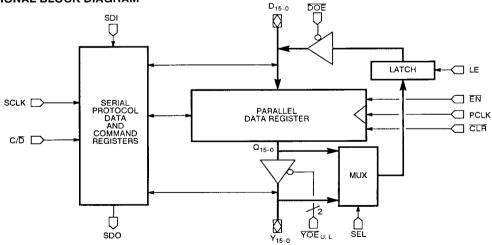

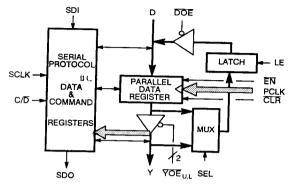

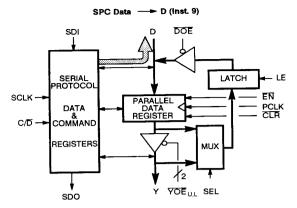

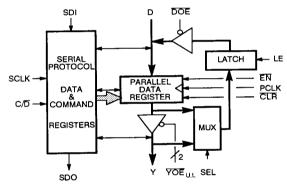

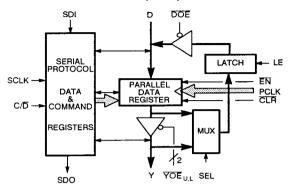

### **FUNCTIONAL BLOCK DIAGRAM**

CEMOS and SPC are trademarks of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

DECEMBER 1987

© 1987 Integrated Device Technology, Inc.

DSC-4027/-

10

## **PIN CONFIGURATIONS**

### PIN DESCRIPTION

| PIN NAME            | 1/0 | DESCRIPTION                                                                      |

|---------------------|-----|----------------------------------------------------------------------------------|

| PCLK                | -   | Parallel Data Register Clock                                                     |

| EN                  | ı   | Clock Enable for PCLK (enabled when low)                                         |

| CLR                 | ı   | Asynchronous 16-Bit Clear (active low)                                           |

| D <sub>15-0</sub>   | 1/0 | Parallel Data Register Input Pins (D <sub>0</sub> = LSB, D <sub>15</sub> = MSB)  |

| Y <sub>15-0</sub>   | 1/0 | Parallel Data Register Output Pins (Y <sub>0</sub> = LSB, Y <sub>15</sub> = MSB) |

| YOE <sub>U, L</sub> | ı   | Output Enables for Y Bus (Overidden by SPC Inst. 8 and 14)                       |

| SEL                 | ı   | Selects Between Parallel Data Register<br>Q or Y Bus for Read Back Data          |

| LE                  | ı   | Controls a Latch in the Read Back<br>Path (transparent when High)                |

| DOE                 | ,   | Output Enable for D Bus (Overidden by SPC Inst. 9)                               |

| SDI                 | 1   | Serial Data In for SPC operation                                                 |

| SDO                 | 0   | Serial Data Out for SPC operation                                                |

| C/D                 | 1   | Mode Control for SPC                                                             |

| SCLK                | 1   | Shift clock for SPC operations                                                   |

TRUTH TABLE (1)

| C/D | SCLK      | PCLK               | EN | CLR | DOE | SEL | LE | YOE <sub>U, L</sub> | ۵     | Υ      | FUNCTION                                              |

|-----|-----------|--------------------|----|-----|-----|-----|----|---------------------|-------|--------|-------------------------------------------------------|

| х   | х         | x                  | х  | х   | х   | Х   | Х  | н                   | х     | High Z | Tri-State Y                                           |

| х   | х         | х                  | х  | L   | х   | х   | х  | Н                   | Х     | L      | Clear Parallel Data Register                          |

| х   | ×         | <u>_</u>           | Н  | Н   | х   | х   | ×  | L                   | Х     | NC     | Hold Parallel Data Register                           |

| Х   | х         |                    | L  | н   | Х   | Х   | х  | L                   | Input | D      | Clock D-to-Y                                          |

| Х   | х         | х                  | х  | Н   | L   | Н   | Н  | Н                   | Ö     | х      | Read Back Parallel Data Register                      |

| х   | х         | х                  | Х  | Н   | L   | L   | Н  | Н                   | Υ     | Input  | Read Back Y Data Bus                                  |

| н   | <b>_</b>  | х                  | х  | ×   | х   | х   | х  | х                   | х     | ×      | Shift Bit into SPC Command<br>Register                |

| L   |           | х                  | х  | Х   | Х   | Х   | Х  | ×                   | Х     | Х      | Shift Bit into SPC Data Register                      |

| J.  | <b>_F</b> | H or L<br>(Static) | х  | х   | х   | х   | х  | ×                   | х     | ×      | Execute SPC Command During Time<br>Between C/D & SCLK |

| Х   | х         | ×                  | ×  | ×   | L   | ×   | L  | х                   | х     | Х      | Read data stored in feedback latch                    |

NOTE:

H = HIGH Voltage Level, L = LOW Voltage Level, X = Don't Care, Z = High Impedance,

## ABSOLUTE MAXIMUM RATINGS (1)

| SYMBOL            | RATING                                     | COMMERCIAL   | MILITARY     | UNIT |

|-------------------|--------------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect to<br>GND | -0.5 to +7.0 | -0.5 to +7.0 | ٧    |

| TA                | Operating<br>Temperature                   | 0 to +70     | -55 to + 125 | °C   |

| T <sub>BIAS</sub> | Temperature<br>Under Bias                  | -55 to +125  | -65 to +135  | °C   |

| T <sub>STG</sub>  | Storage<br>Temperature                     | -55 to + 125 | -65 to +150  | °C   |

| P <sub>T</sub>    | Power Dissipation                          | 0.5          | 0.5          | W    |

| lout              | DC Output Current                          | 120          | 120          | mA   |

### NOTE:

### CAPACITANCE (T<sub>A</sub> = +25°C, f = 1.0MHz)

| SYMBOL           | PARAMETER(1)      | CONDITIONS            | TYP. | MAX. | UNIT |

|------------------|-------------------|-----------------------|------|------|------|

| C <sub>IN</sub>  | Input Capacitance | $V_{IN} = 0V$         | 6    | 10   | pF   |

| C <sub>I/O</sub> | I/O Capacitance   | V <sub>OUT</sub> = 0V | 8    | 12   | рF   |

### NOTE:

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

$V_{LC} = 0.2V; V_{HC} = V_{CC} - 0.2V$ Commercial:  $T_A = 0^{\circ}C \text{ to } +70^{\circ}C; V_{CC} = 5.0V \pm 5\%$ Military:  $T_A = -55^{\circ}C \text{ to } +125^{\circ}C; V_{CC} = 5.0V \pm 10\%$

| SYMBOL           | PARAMETER                               | TEST                                                                           | MIN.                                          | TYP. <sup>(2)</sup> | MAX. | UNI                |              |

|------------------|-----------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------|---------------------|------|--------------------|--------------|

| V <sub>IH</sub>  | Input HIGH Level                        | Guaranteed Logic High                                                          | 2.0                                           | -                   |      | V                  |              |

| V <sub>IL</sub>  | Input LOW Level                         | Guaranteed Logic Low                                                           | Level                                         |                     | -    | 0.8                |              |

| - 115            | to and HIGH Commont                     |                                                                                | $V_1 = V_{CC}$                                |                     | _    | 5                  | ĺ            |

| ŀн               | Input HIGH Current<br>(Except I/O pins) |                                                                                | V <sub>1</sub> = 2.7V                         |                     | -    | 5 (4)              | l            |

|                  |                                         | $V_{CC} = Max.$                                                                | V <sub>1</sub> = 0.5V                         | T                   | _    | -5(4)              | μ,           |

| I <sub>IL</sub>  | Input LOW Current<br>(Except I/O pins)  |                                                                                | V <sub>I</sub> = GND                          |                     | _    | -5                 |              |

| -                |                                         |                                                                                | V <sub>I</sub> = V <sub>CC</sub>              | T -                 |      | 15                 |              |

| I <sub>IH</sub>  | Input HIGH Current<br>(I/O pins only)   |                                                                                | V <sub>1</sub> = 2.7V                         | -                   | _    | 15 <sup>(4)</sup>  |              |

|                  | Input LOW Current                       | $V_{CC} = Max.$                                                                | V <sub>1</sub> = 0.5V                         |                     |      | -15 <sup>(4)</sup> | μA           |

| l <sub>1</sub> L | (I/O pins only)                         | _                                                                              | V <sub>i</sub> = GND                          |                     |      | -15                |              |

| V <sub>IK</sub>  | Clamp Diode Voltage                     | V <sub>CC</sub> = Min., I <sub>N</sub> = -18                                   |                                               | -0.7                | -1.2 |                    |              |

| los              | Short Circuit Current                   | $V_{CC} = Max^{(3)}, V_{C} = 0$                                                | AND                                           | -60                 | -120 |                    | n            |

|                  |                                         | $V_{CC} = 3V, V_{IN} = V_{LC}$                                                 | or V <sub>HC</sub> , l <sub>OH</sub> = -32 μA | V <sub>HC</sub>     | Vcc  |                    |              |

|                  |                                         |                                                                                | I <sub>OH</sub> = -300μA                      | V <sub>HC</sub>     | Voc  |                    |              |

| V <sub>OH</sub>  | Output HIGH Voltage                     | $V_{CC} = Min.$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                        | I <sub>OH</sub> = -12mA MIL.                  | 2.4                 | 4.3  |                    |              |

|                  |                                         | AIN = AIH OL AIT                                                               | I <sub>OH</sub> = -15mA COM'L.                | 2.4                 | 4.3  | <u> </u>           | $oxed{oxed}$ |

|                  |                                         | $V_{CC} = 3V, V_{IN} = V_{LC} \text{ or } V_{HC}, I_{OL} = 300 \mu\text{A}$    |                                               |                     | GND  | V <sub>LC</sub>    |              |

| V <sub>OL</sub>  |                                         |                                                                                | l <sub>OL</sub> = 300μA                       |                     | GND  | V <sub>LC</sub>    |              |

|                  | Output LOW Voltage                      | V <sub>CC</sub> = Min.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | loL = 24mA MIL.                               | T-                  | 0.3  | 0.5                | ]            |

|                  |                                         | TIN - THO TIL                                                                  | loL = 32mA COM'L.                             |                     | 0.3  | 0.5                | <u> </u>     |

| V <sub>H</sub>   | Input Hysteresis on Clocks Only         |                                                                                |                                               | _                   | 200  | T-                 | n            |

### NOTES:

- 1. For conditions shown as max, or min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at  $V_{CC} = 5.0V$ ,  $+25^{\circ}C$  ambient and maximum loading.

- 3. Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed one second.

- 4. This parameter is guaranteed but not tested.

<sup>1.</sup> Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>1.</sup> This parameter is guaranteed by characterization data and not tested.

### POWER SUPPLY CHARACTERISTICS

$V_{LC} = 0.2V; V_{HC} = V_{CC} - 0.2V$

| SYMBOL                  | PARAMETER                                         | TEST CONDIT                                                                                                  | IONS (1)                                                               | MIN. | TYP. <sup>(2)</sup> | MAX.                | UNIT       |

|-------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|---------------------|---------------------|------------|

| Icc                     | Quiescent Power Supply Current                    | $V_{CC} = Max.$<br>$V_{IN} \ge V_{HC}$ ; $V_{IN} \le V_{LC}$<br>$f_{CP} = f_1 = 0$                           |                                                                        | _    | 0.001               | 1.5                 | mA         |

| $\Delta^{ m l}_{ m cc}$ | Quiescent Power Supply Current<br>TTL Inputs HIGH | $V_{CC} = Max.$<br>$V_{IN} = 3.4V^{(3)}$                                                                     |                                                                        | _    | 0.5                 | 2.0                 | mA         |

| I <sub>CCD</sub>        | Dynamic Power Supply Current <sup>(4)</sup>       | V <sub>CC</sub> = Max.<br>Outputs Open<br>YOE <sub>U, L</sub> = GND<br>One Input Toggling<br>50% Duty Cycle  | V <sub>IN</sub> ≥ V <sub>HC</sub><br>V <sub>IN</sub> ≤ V <sub>LC</sub> | _    | 0.15                | 0.25                | mA/<br>MHz |

|                         |                                                   | $V_{CC} = Max.$ Outputs Open $f_{CP} = 10MHz$ 50% Duty Cycle $YOE_{U,L} = GND$                               | $V_{IN} \ge V_{HC}$ $V_{IN} \le V_{LC}$ (FCT)                          | _    | 1.5                 | 4.0                 |            |

| l <sub>c</sub>          | Total Power Supply Current <sup>(8)</sup>         | One Bit Toggling at f <sub>1</sub> = 5MHz 50% Duty Cycle SEL, DOE, CLR, LE, SDI, C/D, SCLK = V <sub>CC</sub> | $V_{IN} = 3.4V \text{ or}$<br>$V_{IN} = GND$                           | -    | 2.0                 | 6.0                 | mA         |

|                         | .'' >                                             | V <sub>CC</sub> = Max.<br>Outputs Open<br>f <sub>CP</sub> = 10MHz<br>50% Duty Cycle<br>∀OE, = GND            | $V_{IN} \ge V_{HC}$ $V_{IN} \le V_{LC}$ (FCT)                          | _    | 6.8                 | 12.8 <sup>(5)</sup> |            |

|                         |                                                   | YOE                                                                                                          | $V_{IN} = 3.4V \text{ or}$<br>$V_{IN} = \text{GND}$                    | _    | 11.0                | 29.8 <sup>(5)</sup> |            |

#### NOTES:

- For conditions shown as max. or min., use appropriate value specified under Electrical Characteristics for the applicable device type.

Typical values are at V<sub>CC</sub> = 5.0V, +25°C ambient and maximum loading.

- Per TTL driven input (V<sub>IN</sub> = 3.4V); all other inputs at V<sub>CC</sub> or GND.

This parameter is not directly testable, but is derived for use in Total Power Supply calculations.

- 5. Values for these conditions are examples of the I<sub>CC</sub> formula. These limits are guaranteed but not tested.

- 6.  $I_{C} = I_{QUIESCENT} + I_{INPUTS} + I_{DYNAMIC}$   $I_{C} = I_{CC} + \Delta I_{CC} D_{H} N_{T} + I_{CCD} (f_{CP}/2 + f_{I} N_{I})$   $I_{CC} = Quiescent Current$

- $\Delta^{I}_{CC}$  = Power Supply Current for a TTL High Input (V<sub>IN</sub> = 3.4V) D<sub>H</sub> = Duty Cycle for TTL Inputs High

- N<sub>T</sub> = Number of TTL Inputs at D<sub>H</sub>

- $f_{CCD} = Dynamic Current Caused by an Input Transition Pair (HLH or LHL) <math>f_{CP} = Clock$  Frequency for Register Devices (Zero for Non-Register Devices)  $f_{\parallel} = Input$  Frequency

- N<sub>i</sub> = Number of Inputs at f<sub>i</sub>

- All currents are in milliamps and all frequencies are in megahertz.

# SWITCHING CHARACTERISTICS OVER OPERATING RANGE

|                                      | Ī          | NG CHARACTI                                               |                       |                     |                  | CT618               |                | L                   | IDT49F       | CT618A                                            |                                                  | ļ        |

|--------------------------------------|------------|-----------------------------------------------------------|-----------------------|---------------------|------------------|---------------------|----------------|---------------------|--------------|---------------------------------------------------|--------------------------------------------------|----------|

|                                      |            |                                                           | CONDITION(1)          | CON                 | l'L              | M                   | L              |                     | M'L          |                                                   | <u> L</u>                                        | UNIT     |

| SYM                                  | BOL        | PARAMETER                                                 | CONDITION             | MIN. <sup>(2)</sup> | MAX.             | MIN. <sup>(2)</sup> | MAX.           | MIN. <sup>(2)</sup> | MAX.         | MIN. <sup>(2)</sup>                               | MAX.                                             |          |

|                                      | Т1         | PCLK † to Y                                               |                       | 3.0                 | 12.5             | 3.0                 | 14.0           |                     |              |                                                   |                                                  |          |

|                                      | T2         | SCLK † to SDO                                             |                       | 3.0                 | 12.5             | 3.0                 | 14.0           |                     |              |                                                   |                                                  |          |

|                                      | Т3         | SDI to SDO<br>(in stub mode)                              |                       | 3.0                 | 12.5             | 3.0                 | 14.0           |                     |              |                                                   |                                                  | ns       |

| t <sub>PLH</sub>                     | T4         | C/D ↓ to Y<br>(YOE <sub>U, L</sub> = Low<br>Inst. 8 & 14) |                       | 3.0                 | 12.5             | 3.0                 | 14.0           |                     |              |                                                   |                                                  | ""       |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | T5         | SCLK † to Y<br>(YOE <sub>U, L</sub> = High,<br>Inst. 8)   |                       | 3.0                 | 12.5             | 3.0                 | 14.0           |                     |              |                                                   |                                                  |          |

|                                      | Т6         | C/D to SDO<br>(Inst. 0,1,2,4)                             |                       | 2.0                 | 12.5             | 3.0                 | 14.0           |                     |              |                                                   |                                                  | -        |

|                                      | T7         | LE to D                                                   |                       | 2.0                 | 12.5             | 3.0                 | 14.0           | <del> </del>        | <del> </del> | <del> </del>                                      |                                                  | 1        |

|                                      | T8         | Y to D                                                    | 1                     | 2.0                 | 12.5             | 3.0                 | 14.0           |                     | <del> </del> | <del> </del>                                      | <del>                                     </del> | 1        |

|                                      | Т9         | SEL or CLR to Y                                           |                       | 2.0                 | 12.5             | 3.0                 | 14.0           |                     |              | <del>                                      </del> |                                                  | ns ns    |

|                                      | T10        | SEL to D                                                  | Į                     | 2.0                 | 12.5             | 3.0                 | 14.0           |                     |              | <del>                                     </del>  |                                                  | 1        |

|                                      | S1         | D to PCLK †                                               |                       | 2.5                 |                  | 3.0                 |                |                     |              | <del> </del>                                      | <del> </del>                                     | ┨        |

|                                      | S2         | C/D to SCLK †                                             |                       | 12.0                |                  | 14.0                |                | <del> </del>        | <u> </u>     | <del>├</del>                                      | -                                                | -        |

|                                      | S3         | SDI to SCLK †                                             |                       | 4.0                 |                  | 5.0                 |                | <del> </del>        |              | <del> </del>                                      | <del> </del>                                     | -        |

|                                      | S4         | Y or D to C/D<br>(Inst. 0, 2 & 4)                         | C <sub>L</sub> = 50pF | 2.0                 |                  | 2.5                 |                |                     |              | <u> </u>                                          |                                                  | -        |

| t <sub>SU</sub>                      | <b>S</b> 5 | C/D (Low) to<br>PCLK †<br>(Inst. 3 & 13)                  | $R_L = 500\Omega$     | 8.0                 |                  | 9.0                 | -              |                     |              |                                                   |                                                  |          |

|                                      | S6         | Y to PCLK †<br>(Inst. 3)                                  |                       | 2.0                 |                  | 2.5                 |                |                     |              |                                                   |                                                  | 4        |

|                                      | S7         | Y to LE                                                   |                       | 3.0                 |                  | 4.0                 |                |                     | <del> </del> | ļ                                                 | ļ .                                              | _ ns     |

|                                      | S8         | SEL to LE                                                 | 1                     | 3.0                 |                  | 4.0                 | _ =            | <del></del>         | <del> </del> |                                                   |                                                  | -        |

|                                      | S9         | EN to PCLK                                                | _                     | 3.0                 | <u> </u>         | 4.0                 |                | <del> </del>        | ┼            | +                                                 | <del></del>                                      | 1        |

|                                      | S10        | PCLK † to LE<br>(Low)                                     |                       | 3.0                 |                  | 4.0                 |                |                     | ļ            |                                                   | <u> </u>                                         | 4        |

|                                      | H1         | D to PCLK †                                               |                       | 2.0                 |                  | 2.5                 | <del>-</del> - | ļ                   | ļ            |                                                   | <del> </del>                                     | _        |

|                                      | H2         | C/D to SCLK ↑                                             |                       | 12.0                |                  | 14.0                |                |                     |              | 1                                                 | 1                                                | +-       |

|                                      | нз         | SDI to SCLK †                                             |                       | 1.0                 |                  | 1.0                 |                |                     |              | <del> </del>                                      | <del> </del>                                     | 4        |

|                                      | H4         | Y or D to C/D ↓<br>(Inst. 0, 2 & 4)                       |                       | 2.0                 |                  | 2.5                 | _              |                     |              |                                                   |                                                  | 4        |

| t <sub>H</sub>                       | Н5         | SCLK (Low) to                                             |                       | 2.0                 | -                | 2.5                 | _              |                     |              |                                                   |                                                  | n        |

|                                      | Н6         | C/D (Low) to<br>PCLK †<br>(Inst. 3 & 13)                  |                       | 2.0                 | _                | 2.5                 | _              |                     |              |                                                   |                                                  |          |

|                                      | Н7         | Y to PCLK †<br>(Inst. 3)                                  |                       | 3.0                 |                  | 3.0                 |                | _                   |              |                                                   | <u> </u>                                         | -        |

|                                      | H8         | Y to LE                                                   |                       | 2.0                 |                  | 2.0                 |                |                     | <del> </del> | <del> </del>                                      | +-                                               | $\dashv$ |

|                                      | Н9         | SEL to LE                                                 |                       | 2.0                 | <del>  -</del> - | 2.0                 | <del>  -</del> |                     |              | <del></del>                                       | +                                                | $\dashv$ |

|                                      | Н          | 0 EN to PCLK †                                            |                       | 2.0                 | l                | 2.0                 |                |                     |              | <u> </u>                                          |                                                  |          |

(Continued)

## SWITCHING CHARACTERISTICS OVER OPERATING RANGE

|                                      |            |                                                                |                   |         | IDT49  | FCT618              |      |                     | IDT49F | CT618A              |      |        |

|--------------------------------------|------------|----------------------------------------------------------------|-------------------|---------|--------|---------------------|------|---------------------|--------|---------------------|------|--------|

| SYM                                  | BOL        | PARAMETER                                                      | ER CONDITION(1)   |         | COM'L. |                     | L.   | COM'L.              |        | MI                  | L.   | ן דואט |

|                                      |            |                                                                |                   | MIN.(2) | MAX.   | MIN. <sup>(2)</sup> | MAX. | MIN. <sup>(2)</sup> | MAX.   | M1N. <sup>(2)</sup> | MAX. |        |

|                                      | 1Z         | YOE <sub>U, L</sub> to Y                                       |                   | 3.0     | 8.0    | 3.0                 | 8.0  |                     |        |                     |      |        |

|                                      | 2Z         | SCLK † to D<br>(Inst. 9)                                       |                   | 3.0     | 9.0    | 3.0                 | 9.0  |                     |        |                     |      |        |

|                                      | 3Z         | C/D ↑ to D or Y<br>(Inst. 9)                                   |                   | 3.0     | 9.0    | 3.0                 | 9.0  |                     |        |                     |      | ns     |

| t <sub>PHZ</sub>                     | 4Z         | SCLK † to Y<br>(YOE <sub>U, L</sub> = High<br>Inst. 8 & 14)    |                   | 3.0     | 9.0    | 3.0                 | 9.0  |                     |        |                     |      | 113    |

|                                      | 5Z         | C/D to ↑ to D or Y<br>(YOE <sub>U, L</sub> = High<br>Inst. 14) |                   | 3.0     | 9.0    | 3.0                 | 9.0  |                     |        |                     |      |        |

|                                      | 6Z         | DOE to D                                                       | $C_L = 50pF$      | 2.0     | 9.0    | 3.0                 | 10.0 |                     |        |                     |      |        |

|                                      | Z1         | YOE <sub>U, L</sub> to Y                                       | $R_L = 500\Omega$ | 3.0     | 10.0   | 3.0                 | 10.0 |                     |        |                     |      |        |

|                                      | <b>Z</b> 2 | C/D ↓ to D<br>(Inst. 9)                                        |                   | 3.0     | 10.0   | 3.0                 | 10.0 |                     |        |                     |      |        |

| t <sub>PZH</sub><br>t <sub>PZL</sub> | <b>Z</b> 3 | C/D 1 to Y<br>(YOE <sub>U L</sub> = High<br>Inst. 14)          |                   | 3.0     | 10.0   | 3.0                 | 10.0 |                     |        |                     |      | ns     |

|                                      | Z4         | DOE to D                                                       |                   | 2.0     | 9.0    | 3.0                 | 10.0 |                     |        |                     |      | 1      |

|                                      | W1         | PCLK (High & Low)                                              |                   | 7.0     | _      | 8.0                 | _    |                     |        |                     |      |        |

| ,                                    | W2         | SCLK (High & Low)                                              |                   | 25.0    | _      | 25.0                | _    |                     |        |                     |      | l l    |

| t <sub>W</sub>                       | W3         | C/D (High)                                                     |                   | 25.0    | _      | 25.0                | _    |                     |        | <u> </u>            |      | i l    |

|                                      | W4         | LE (High-Low)                                                  |                   | 7.0     | _      | 8.0                 | -    |                     |        |                     |      |        |

|                                      | W5         | CLR (Low)                                                      |                   | 7.0     | _      | 8.0                 | -    |                     |        |                     |      |        |

NOTES:

See test circuit and waveforms.

Minimum limits are guaranteed but not tested on Propagation Delays.

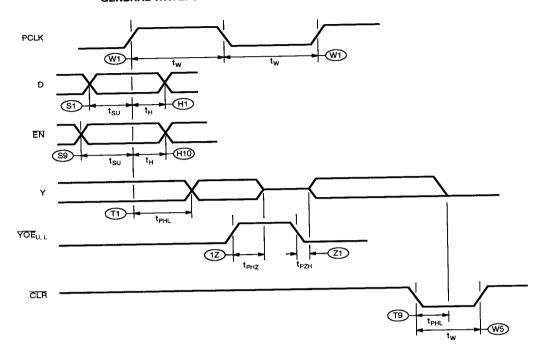

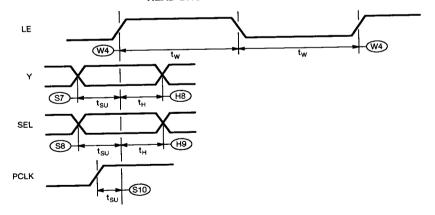

# GENERAL WAVEFORMS FOR PARALLEL INPUTS AND OUTPUTS

# **READ BACK LATCH SETUP & HOLD ITEMS**

### **READ BACK PROPOGATION DELAYS**

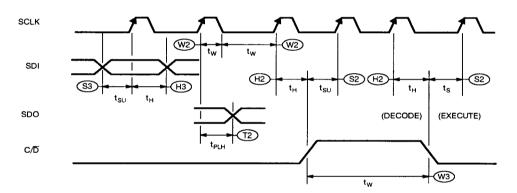

### GENERAL WAVEFORMS FOR SERIAL PROTOCOL INPUTS AND OUTPUTS

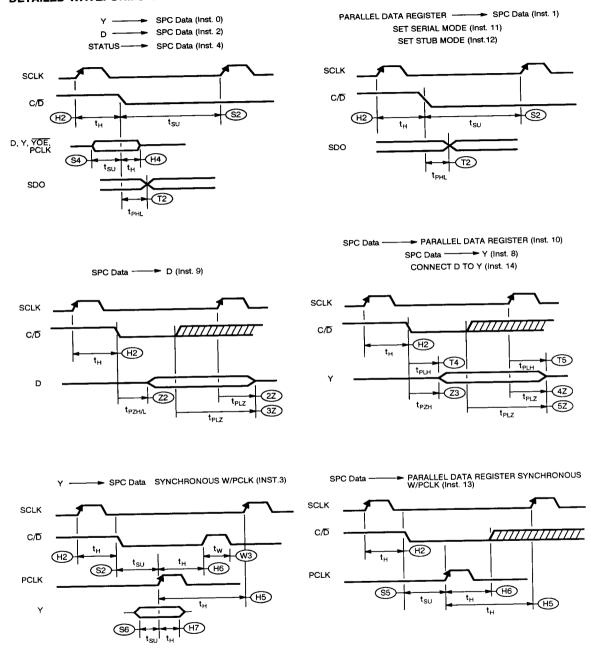

# DETAILED WAVEFORMS OF SERIAL PROTOCOL OPERATIONS

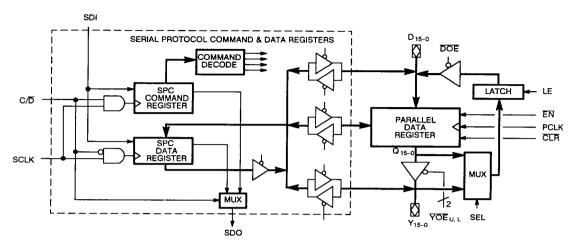

### **DETAILED FUNCTIONAL BLOCK DIAGRAM**

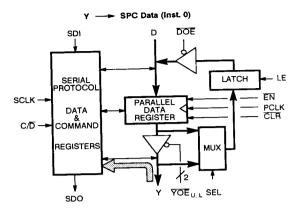

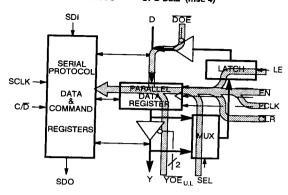

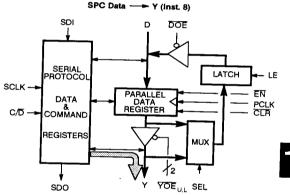

The block diagram consists of three main data paths and two logic blocks. The main data path is from the D inputs down to the parallel data register and through the Y outputs. This is the path that will be used most of the time in normal operation. For serial protocol operations, there are data paths from the Y pins into the SPC data register and control block. Coming out of this block is the data path that allows data to be put back onto the D input pins or into the parallel data register. The PCLK is used to clock the parallel data register. The EIN signal is a clock enable for the 16-bit parallel data path. The CLR line offers an asynchronous 16-bit clear.  $\overline{\text{YOE}}_{\text{U}}$  inputs are used to control the tri-state output of the Y pins.

The other main data path is a read back from the output of the 16-bit parallel data register to the D bus. This path is convenient when using the IDT49FCT618 with a processor because it provides the mechanism to read the contents of the data register. The SEL pin selects data from the internal Q bus or the data output pins Y. The LE signal controls a latch in the read back path. In this way data can be latched "on the fly" and allowed to settle before a processor reads it back on the D pins. The  $\overline{\rm DOE}$  input is a tri-state control which selects whether the D bus is an input or an output.

SPC data and commands are shifted through the SDI pin which is a serial input pin and the SDO pin which is a serial output pin. Data and commands are shifted in Least Significant Bit first, Most Significant Bit last  $(Y_0 = LSB, Y_{15} = MSB)$ . The SCLK is used to shift the data through. The C/D line is used as a control input to determine whether data or command information is being shifted in.

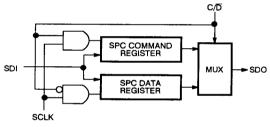

The Serial Protocol Channel (SPC) has been optimized for the minimum number of pins and maximum flexibility. The data is passed in on a serial data input pin (SDI) and out on a serial data output pin (SDO). The transfer of the data is controlled by a serial clock (SCLK) and a command/data mode input (C/ $\overline{D}$ ). These four pins are the basic SPC pins. To the outside, the SPC appears at wo serial shift registers in parallel; one for command and the other data. The serial clock shifts data and the command/data (C/ $\overline{D}$ ) line selects which register is being shifted. The SPC command register is used to control loading of data to and from the parallel data register with other storage elements in the device.

## SPC FUNCTIONAL DESCRIPTION

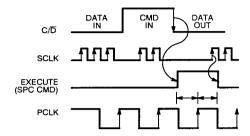

With respect to executing an SPC command, there are four distinct phases: (1) data is shifted in, (2) followed by the SPC command, (3) the SPC command is executed, (4) data is shifted out. During the data mode, data is simultaneously shifted into the SPC data register while the data in the register is shifted out. During the command mode, opcode type information is shifted through the serial ports.

The command is executed when the last bit is shifted in and the  $C/\overline{D}$  line is brought low. The execution phase is ended with the next serial clock edge. Execution of SPC commands is performed by stopping the SPC clock, SCLK, and lowering the C/D line from high-to-low. Later the SCLK may be transitioned from low-to-high. SPC commands and data can be shifted any time without regard for operation. During the execution phase, care must be taken that there is no conflict between the SPC operation and parallel operation. This means that if the SPC operation attempts to load the parallel data register (opcode 10) while PCLK is in transition, the results are undefined. In general, it is required that the PCLK be static during SPC operations. The synchronous commands (opcodes 3 and 13), however, allow the PCLK to run. In these operations the HIGH-to-LOW transition of the C/D line takes on the function of an arm signal in preparation for the next LOW-to-HIGH transition of the PCLK.

10

## **SPC COMMANDS**

There are 16 possible SPC opcodes. Thirteen of these are utilized; the other three are reserved and perform NO-OP functions. The top eight opcodes, 0 through 7, are used for transferring data into the SPC data register for shifting out. The lower eight opcodes, 8 through 15, are used for transferring data from the SPC data register to other parts of the device. Two of the commands are also used for connecting the data in and out pins.

| OPCODE | SPC COMMAND                                        |

|--------|----------------------------------------------------|

| 0      | Y to SPC Data Register                             |

| 1      | Parallel Data Register to SPC Data Register        |

| 2      | D to SPC Data Register                             |

| 3      | Y to SPC Data Register Synchronous w/PCLK          |

| 4      | Status (YOE U. L. PCLK, etc.) to SPC Data Register |

| 5-7    | Reserved (NO-OP)                                   |

| 8      | SPC Data to Y (YOE <sub>U, L</sub> is overidden)   |

| 9      | SPC Data to D (DOE is overidden)                   |

| 10     | SPC Data to Parallel Data Register                 |

| 11     | Select Serial Mode                                 |

| 12     | Select Stub Mode                                   |

| 13     | SPC Data to Y Synchronous w/PCLK                   |

| 14     | Connect D to Y (YOE <sub>U, L</sub> is overidden)  |

| 15     | NO-OP                                              |

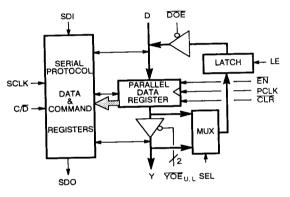

Opcode 0 is used for transferring data from the Y output pins into the SPC data register. Opcode 1 transfers data from the output of the parallel data register into the SPC data register.

PARALLEL DATA REG - SPC Data (Inst. 1)

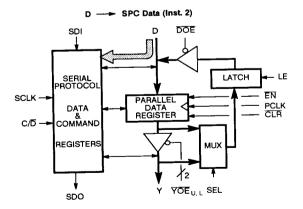

Opcode 2 transfers data which is on data input pin D into the SPC data register.

Opcode 3 transfers data on the Y pins to the SPC data register on the next PCLK, thus achieving a synchronous observation of the parallel data register in real time. This operation can be forced to repeat without shifting in a new command by pulsing C/\overline{D} LOW-HIGH-LOW after each PCLK. As soon as data is shifted out using SCLK, the command is terminated and must be loaded in again.

# Y --- SPC Data SYNCHRONOUS w/PCLK (Inst. 3)

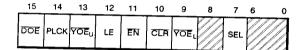

Opcode 4 is used for loading status into the SPC data register. The format of bits is shown below.

### STATUS --- SPC Data (Inst. 4)

Opcodes 5 through 7 are reserved, hence designated NO-OP.

Opcode 8 is used for transferring data directly to the Y pins. When executing opcode 8, the state of  $\overline{YOE}_{U,L}$  is a don't care and data will be output even if  $\overline{YOE}_{U,L}$  = HIGH. Opcode 9 is used for transferring SPC data to the D pins. Operations 8 and 9 can be temporarily suspended by raising the C/D input and resumed by lowering the C/D. As soon as SCLK completes transition, the command is terminated.

10-25

Opcode 10 is used for transferring data from the SPC Data register into the parallel data register, irrespective of the state of PCLK. However, PCLK must be static between C/D going HIGH-to-LOW and SCLK going LOW-to-HIGH.

# SPC Data ----> PARALLEL DATA REGISTER (Inst. 10)

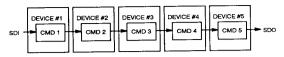

Opcodes 11 and 12 are used to set Serial and Stub mode, respectively. After executing one of these opcodes, the device remains in this mode through other Serial Protocol operations until reprogrammed using either command. The serial mode is the default mode that the IDT49FCT618 powers up in. In Serial mode, commands are shifted through the command register and then to the SDO pin. This is the typical mode used when several varieties of devices that utilize the SPC access method are employed on one serial ring.

#### SERIAL MODE

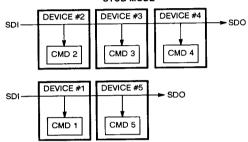

In Stub mode, SDI is connected directly to SDO. The serial input of the command register is connected to SDI. In this way, the same SPC command can be loaded into multiple devices of like type. For example, in four clock cycles the same command could be loaded into 8 IDT49FCT618s (128-bit pipeline register). Dissimilar devices must be segregated into serial scan loops of similar type as shown below (i.e., other devices from IDT that incorporate SPC). During the command phase, the serial shift clock must be slowed down to accommodate the delay from SDI to SDO through all of the devices. The slower clock is typically a small tradeoff compared to the reduced number of clock cycles.

#### STUB MODE

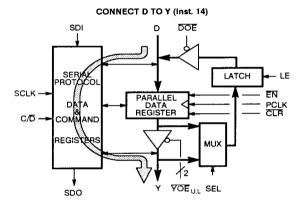

Opcode 13 transfers data from the SPC data register to the pipeline register on the next PCLK. Opcode 14 connects the D bus to the Y bus. Operation 14 can be temporarily suspended by raising the C/D input and resumed by lowering the C/D input again. The operation is terminated by SCLK.

# SPC Data → PARALLEL DATA REGISTER SYNCHRONOUS W/PCLK (Inst. 13)

Opcodes 3 and 13 transfer data synchronous to the PCLK which means that the High-to-Low on the  $C/\overline{D}$  input is an arm signal. The data and command can be shifted in while the PCLK is running. The  $C/\overline{D}$  line is dropped prior to the desired PCLK edge and raised afterwards, before the next edge. Instruction 13 can be repeated many times by leaving the  $C/\overline{D}$  line low during multiple transitions of the PCLK while not clocking SCLK. PCLK cycles can even be skipped by raising the  $C/\overline{D}$  input during the desired clock periods. Instruction 3 can be repeated by pulsing the  $C/\overline{D}$  high after each PCLK.

The ability to repeatedly execute a synchronous command can provide major benefits. For example, the synchronous read (Instruction 3, Y to SPC data) instruction could be clocked into the serial command register. Then, it could be continuously executed by pulsing the  $C/\overline{D}$  line HIGH. When the whole system is stopped (PCLK quiescent), the serial data register will contain the next to the last state of the parallel data register. That value can be shifted out and the current state of the parallel data register can then be observed, allowing for the observation of two states of the parallel data register (the current and the previous).

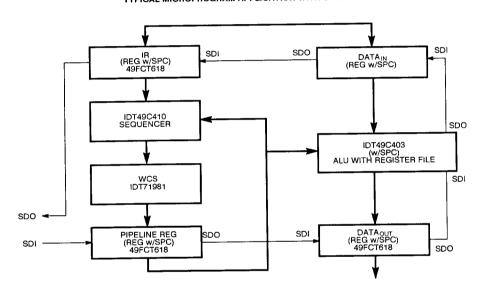

### TYPICAL APPLICATION

In the block diagram of the typical application, the register with SPC register is shown being used with a writable control store in a microprogrammed design. The control store can be initialized through the diagnostics path. The SPC data register with SPC is used for the instruction register going into the IDT49C410, as well as parallel data registers around the IDT49C403. In this way, the designer may use the SPC register to observe and modify the microcode coming out of the writable control store, as well as observing and being able to modify data and instructions in the overall machine. The IDT49C403 is a 16-bit version of the 2903A/203 which includes an SPC port for diagnostic and break point purposes.

The block diagram of the diagnostic ring shows how the devices with SPC Data are hooked together in a serial ring via the SDI and SDO signals. The SPC signals may be generated through registers which are hooked up to a microprocessor. This microprocessor could conceivably be an IBM PC.

As companies like IDT continue to integrate more onto each device and put each device into smaller packages such as surface mount devices, the board level testing becomes more complex for the designer and the manufacturing divisions of companies. To help this situation, SPC was invented. This allows for observation of critical signals deep within the system. During system test when an error is observed, these signals may be modified in order to zero in on the fault in the system.

SPC is primarily a scheme utilizing only a few pins (4) to examine and alter the internal state of a system for the purpose of monitoring and diagnosing system faults. It can be used at many points in the life of a product: design debug and verification, manufacturing test and field service. This document describes a serial diagnostic scheme which was developed at IDT and will be used in future VLSI logic devices designed by IDT.

### TYPICAL MICROPROGRAM APPLICATION WITH SPC™

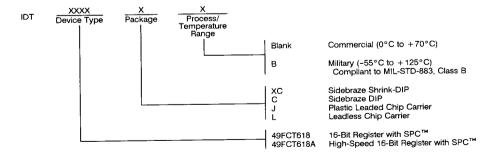

### ORDERING INFORMATION