### 1.0 Features

- 10/100Mbps TX/FX

- Full-duplex or half-duplex

- Supports Auto MDI/MDIX function

- Fully compliant with IEEE 802.3/802.3u

- Supports IEEE 802.3u auto-negotiation

- Supports MII / RMII / SNI interface

- IEEE 802.3 full duplex control specification

- Supports Automatic Power Saving mode

- Supports BaseLine Wander (BLW) compensation

- Supports Interrupt function

- Supports repeater mode

- Single 3.3V power supply with built-in 2.5V regulator

- DSP-based PHY Transceiver technology

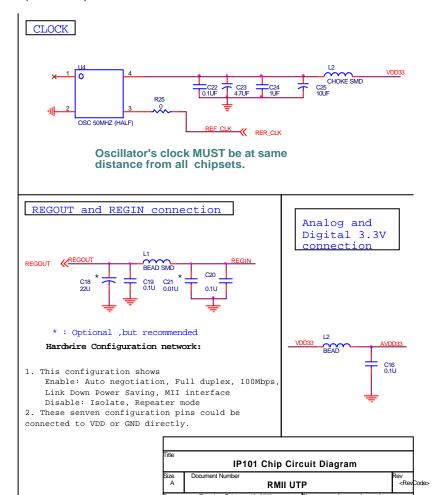

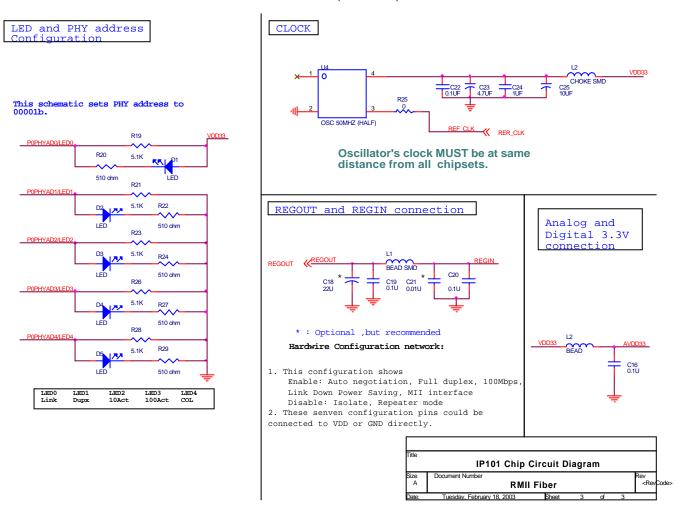

- Using either 25MHz crystal or 50MHz REF\_CLK as clock source

- Flexible LED display for speed, duplex, link, activity and collision

- Supports flow control to communicate with other MAC through MDC and MDIO

- 0.25u, CMOS technology

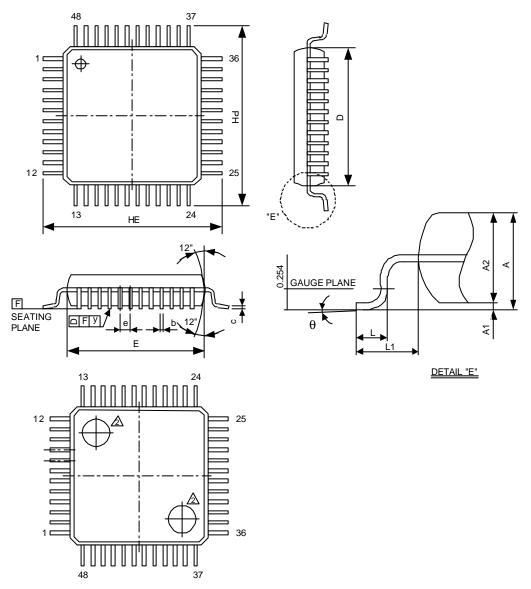

- 48-pin LQFP

## 2.0 General Description

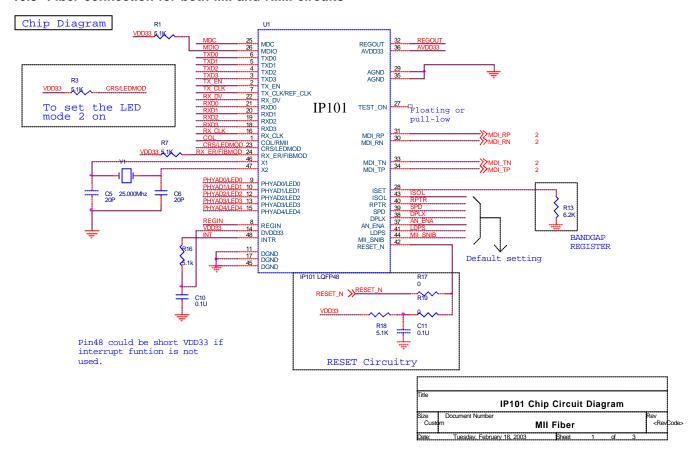

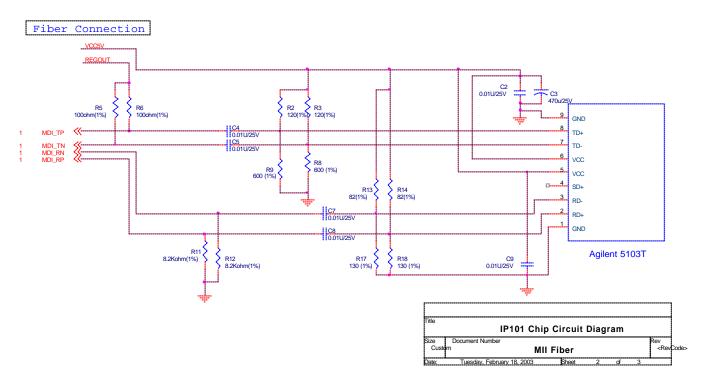

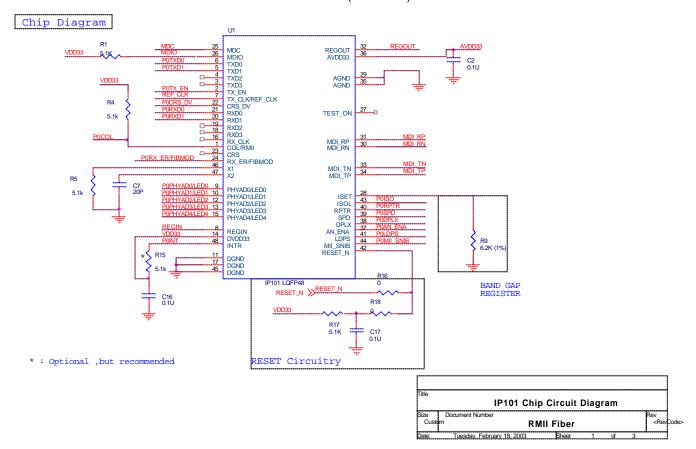

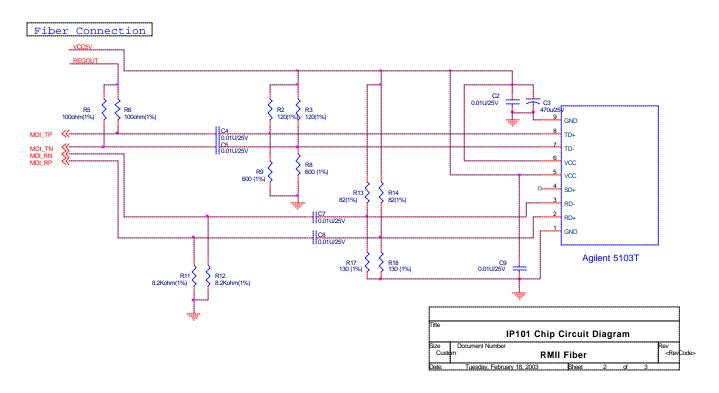

IP101 is an IEEE 802.3/802.3u compliant single-port Fast Ethernet Transceiver for both 100Mbps and 10Mbps operations. It supports Auto MDI/MDIX function to simplify the network installation and reduce the system maintenance cost. To improve the system performance, IP101 provides a hardware interrupt pin to indicate the link, speed and duplex status change. IP101 also provides Media Independent Interface (MII) / Serial Network Interface (SNI) or Reduced Media Independent Interface (RMII) to connect with different types of 10/100Mb Media Access Controller (MAC). IP101 is designed to use category 5 unshielded twisted-pair cable or Fiber-Optic cables connecting to other LAN devices. A PECL interface is supported to connect with an external 100Base-FX fiber optical transceiver.

IP101 Transceiver is fabricated with advanced CMOS technology, which the chip only requires 3.3V as power supply and consumes very low power in the Auto Power Saving mode. IP101 can be implemented as Network Interface Adapter with RJ-45 for twisted-pair connection or MAU for Fiber Connection. It can also be easily implemented into HUB, Switch, Router, Access Point, Advanced Communication Riser (ACR) and Communication and Networking Riser (CNR).

1/33

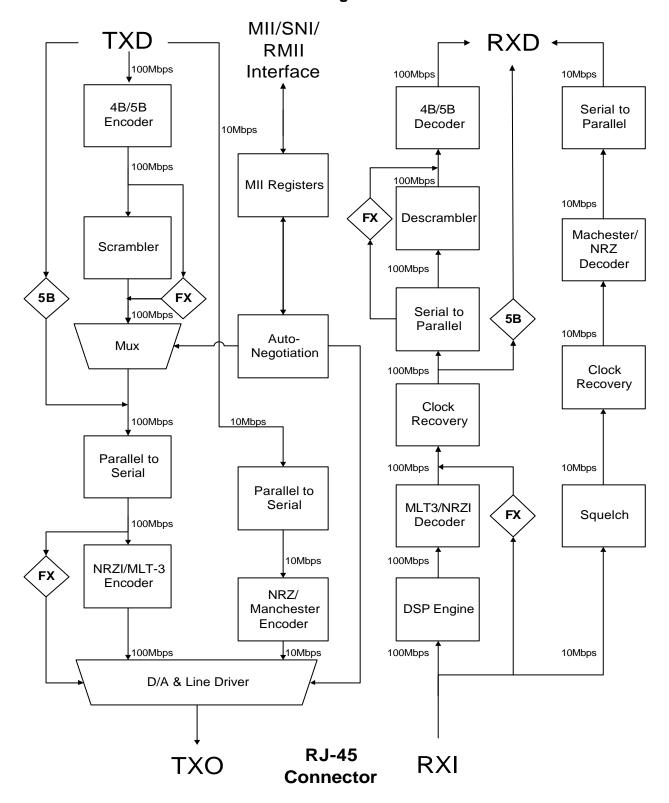

## 3.0 Transmit and Receive Data Path Block Diagram

Figure 1: Flow chart of IP101

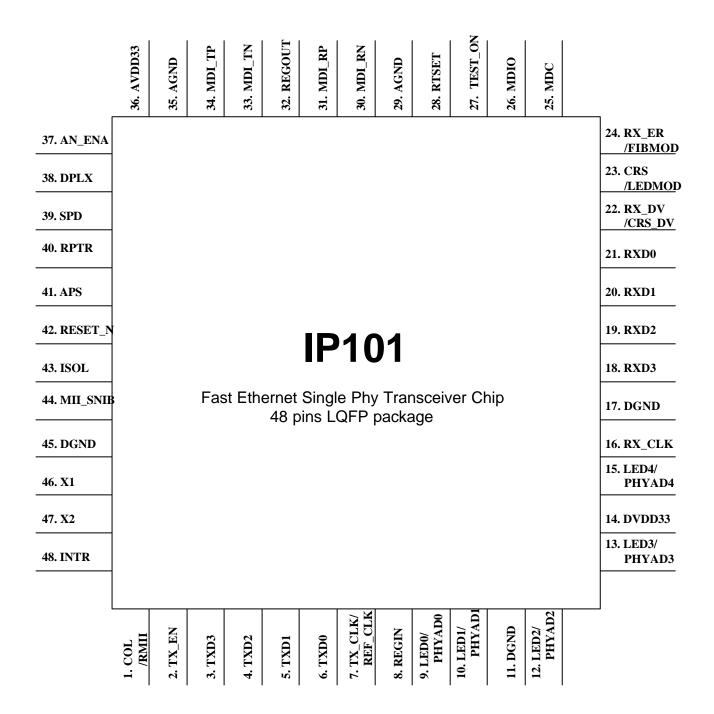

## 4.0 Pin Assignments

Figure 2: IP101 pins assignment

# 5.0 Pin Descriptions

| Type | Description                        |

|------|------------------------------------|

| LI   | Latched Input in power up or reset |

| I/O  | Bi-directional input and output    |

| I    | Input                              |

| 0    | Output                             |

| Туре | Description        |

|------|--------------------|

| PD   | Internal Pull-Down |

| PU   | Internal Pull-Up   |

| Р    | Power              |

| OD   | Open Drain         |

| Pin no.           | Label                                             | Туре      | Description                                                                                                                                                                                                                                                              |  |  |  |

|-------------------|---------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                   | MII and PCS Interface - Management Interface Pins |           |                                                                                                                                                                                                                                                                          |  |  |  |

| 25                | MDC                                               | _         | Management Data Interface Clock: This pin provides a clock reference to MDIO. The clock rate can be up to 10MHz.                                                                                                                                                         |  |  |  |

| 26                | MDIO                                              | I/O       | <b>Management Data interface Input/Output:</b> The function of this pin is to transfer management information between PHY and MAC.                                                                                                                                       |  |  |  |

|                   | MII and PCS                                       | Interface | - Media Independent Interface (MII) Pins                                                                                                                                                                                                                                 |  |  |  |

| 2                 | TX_EN                                             | I<br>(PD) | <b>Transmit Enable:</b> This pin is an active high input. At high status, it indicates the nibble data in TXD[3:0] is valid.                                                                                                                                             |  |  |  |

| 7                 | TX_CLK                                            | 0         | <b>Transmit Clock:</b> This pin provides a continuous 25MHz clock at 100Mbps and 2.5Mbps as timing reference for TXD[3:0] and TX_EN when the chip operates under MII and SNI modes. This pin is an input pin operates as RMII reference clock (REF_CLK) under RMII mode. |  |  |  |

| 3, 4, 5, 6        | TXD[3:0]                                          | I         | <b>Transmit Data:</b> When TX_EN is set low, MAC will transmit data through these 4 lines to PHY which the transmission is synchronizing with TX_CLK.                                                                                                                    |  |  |  |

| 22                | RX_DV                                             | 0         | <b>Receive Data Valid:</b> At high status stands for data flow is present within RXD[0:3] lines and low means no data exchange occurred.                                                                                                                                 |  |  |  |

| 16                | RX_CLK                                            | 0         | <b>Receive Clock:</b> This pin provides 25MHz for 100Mbps transmission or 2.5Mhz for 10Mbps transmission and RX_DV pin uses this pin as its reference under MII or SNI mode. While under RMII mode this pin is driven low.                                               |  |  |  |

| 18, 19,<br>20, 21 | RXD[3:0]                                          | 0         | <b>Receive Data:</b> These 4 data lines are transmission path for PHY to send data to MAC and they are synchronizing with RX_CLK.                                                                                                                                        |  |  |  |

| Pin no. | Label                                                          | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------|----------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         | MII and PCS Interface – Media Independent Interface (MII) Pins |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 24      | RX_ER/<br>FIBMOD                                               | O/LI<br>(PD) | Receive error: This pin outputs a high status when errors occurred in the decoded data in the transmission.  Fiber Mode: During power on reset, this pin status is latched to determine at which media mode to operate:  1: Fiber mode  0: UTP mode  An internal weak pull low resistor sets this to the default of UTP mode. It is possible to use an external 5.1KΩpull high resistor to enable fiber mode.  After power on, the pin operates as the Receive Error pin. |  |  |  |

| 1       | COL/RMII                                                       | O/LI<br>(PD) | Collision Detected: When this pin outputs a high status signal it means collision is detected.  RMII Mode: During power on reset, this pin status is latched and arranged with MII/SNIB (pin44) to determine MAC interface RMII MII/SNIB  1                                                                                                                                                                                                                               |  |  |  |

| 23      | CRS/LEDMOD                                                     | O<br>(PD)    | Carrier Sense: When signal output from this pin is high indicates the transmission is in process and at low status means the line is in idle state.  LEDMOD: During power on reset, this pin status is latched to determine at which LED mode to operate, please refer to the LED pins description.  (Notice: This pin is pulled down internally)                                                                                                                         |  |  |  |

|         |                                                                |              | RMII (Reduced MII)                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 7       | REF_CLK                                                        | I            | <b>Reference Clock:</b> This pin is an input pin operates as RMII reference clock (REF_CLK) under RMII mode. 25MHz Crystal Input and Output, X1 & X2, should be disconnected when REF_CLK is used as the clock source of IP108.                                                                                                                                                                                                                                           |  |  |  |

| 2       | TX_EN                                                          | l<br>(PD)    | Transmit Enable: For MAC to indicate transmit operation                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 5,6     | TXD[1:0]                                                       | I            | Transmit two-bit Data                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 24      | RX_ER                                                          | I/O          | Receive Error                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 22      | CRS_DV                                                         | 0            | Carrier Sense and Receive Data Valid                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 20, 21  | RXD[1:0]                                                       | 0            | Received two-bit Data                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| Pin no.  | Label                                       | Туре         | Description                                                                                                                                                                                                                                                                                             |  |  |  |

|----------|---------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | SNI (Serial Network Interface): 10Mbps only |              |                                                                                                                                                                                                                                                                                                         |  |  |  |

| 2        | TX_EN                                       | I<br>(PD)    | Transmit Enable: Indicate transmit operation to MAC                                                                                                                                                                                                                                                     |  |  |  |

| 7        | TX_CLK                                      | 0            | Transmit Clock: 10MHz, generate either by PHY or by external                                                                                                                                                                                                                                            |  |  |  |

| 6        | TXD0                                        |              | Transmit Serial Data                                                                                                                                                                                                                                                                                    |  |  |  |

| 16       | RX_CLK                                      | 0            | Receive Clock: 10MHz, clock recovery from received data                                                                                                                                                                                                                                                 |  |  |  |

| 21       | RXD0                                        | 0            | Received Serial Data                                                                                                                                                                                                                                                                                    |  |  |  |

| 1        | COL                                         | 0            | Collision Detect                                                                                                                                                                                                                                                                                        |  |  |  |

| 23       | CRS                                         | 0            | Carrier Sense                                                                                                                                                                                                                                                                                           |  |  |  |

|          |                                             | Cabl         | e Transmission Interface                                                                                                                                                                                                                                                                                |  |  |  |

| 34<br>33 | MDI_TP<br>MDI_TN                            | 00           | Transmit Output Pair: Differential pair shared by 100Base-TX, 100Base-FX and 10Base-T modes. When configured as 100Base-TX, output is an MLT-3 encoded waveform. When configured as 100Base-FX, the output is pseudo-ECL level.                                                                         |  |  |  |

| 31<br>30 | MDI_RP<br>MDI_RN                            | <br>         | <b>Receive Input Pair:</b> Differential pair shared by 100Base-TX, 100Base-FX, and 10Base-T modes.                                                                                                                                                                                                      |  |  |  |

|          |                                             | IC           | Configuration Options                                                                                                                                                                                                                                                                                   |  |  |  |

| 43       | ISOL                                        | I<br>(PD)    | Set high to this pin will isolate IP101 from other MAC. This action will also isolate the MDC/MDIO management interface. The power usage is at minimum when this pin is activated. This pin can be directly connected to GND or VCC. (An internal weak pulled-down is used to be inactive as a default) |  |  |  |

| 40       | RPTR                                        | I<br>(PD)    | Enable this pin to high will put the IP101 into repeater mode. This pin can be directly connected to GND or VCC. (An internal weak pulled-down is used to be inactive as a default)                                                                                                                     |  |  |  |

| 39       | SPD                                         | LI/O<br>(PU) | This pin is latched to input during a power on or reset condition. Set high to put the IP101 into 100Mbps operation. This pin can be directly connected to GND or VCC. (An internal weak pulled-up is used to set 100Mbps as a default)                                                                 |  |  |  |

| 38       | DPLX                                        | LI/O<br>(PU) | This pin is latched to input during a power on or reset condition.  Set high to enable full duplex. This pin can be directly connected to GND or VCC. (An internal weak pulled-up is used to set full duplex as a default)                                                                              |  |  |  |

| 37       | AN_ENA                                      | LI/O<br>(PU) | This pin is latched to input during a power on or reset condition. Set high to enable auto-negotiation mode, set low to force mode. This pin can be directly connected to GND or VCC. (An internal weak pulled-up is used to enable N-WAY as a default)                                                 |  |  |  |

| 41       | APS                                         | I<br>(PU)    | Set high to put the IP101 into APS mode. This pin can be directly connected to GND or VCC. Refer to Section 7.7 for more information. (An internal weak pulled-up is used to enable APS mode as a default)                                                                                              |  |  |  |

| 44       | MII_SNIB                                    | LI/O<br>(PU) | This pin is latched to input during a power on or reset condition. Pull high to set the IP101 into MII mode operation. Set low for SNI mode. This pin can be directly connected to GND or VCC. (An internal weak pulled-up is used to set MII mode as a default)                                        |  |  |  |

| 0.01 50                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              | ,                 | ı                                                                                                                                                    |                                                                                                                                                         |                            |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|

| Pin no.                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Label        | Туре              |                                                                                                                                                      | Description                                                                                                                                             |                            |  |

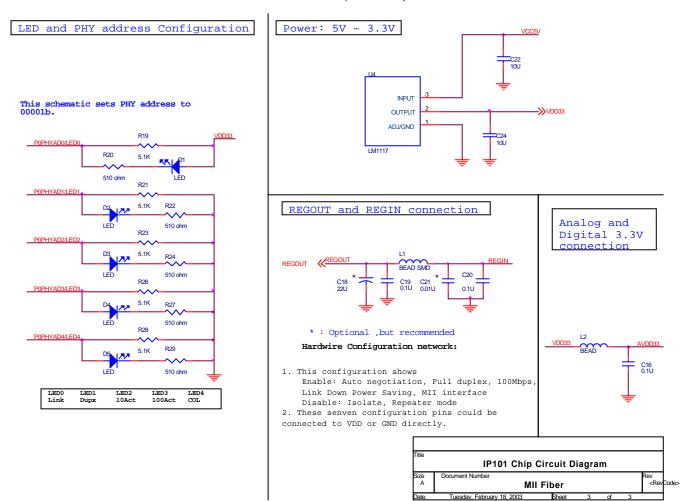

|                                          | LED and PHY Address Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |                   |                                                                                                                                                      |                                                                                                                                                         |                            |  |

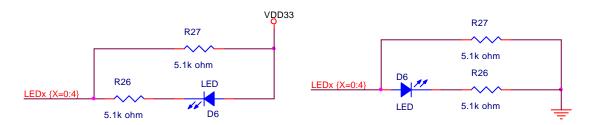

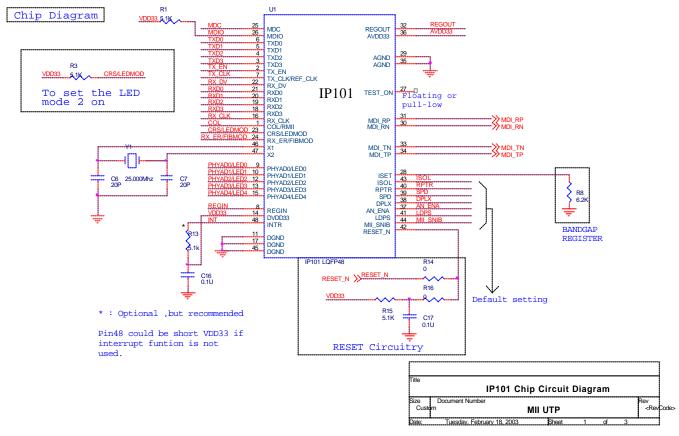

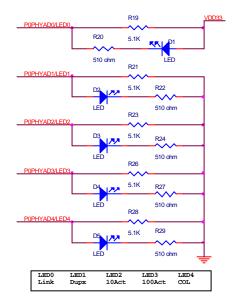

| managemer<br>status indica<br>PHY addres | These five pins are latched into the IP101 during power up reset to configure PHY address [0:4] used for MII management register interface. And then, in normal operation after initial reset, they are used as driving pins for status indication LED. The driving polarity, active low or active high, is determined by each latched status of the PHY address [4:0] during power-up reset. If latched status is high then it will be active low, and if latched status is Low then it will be active high. Moreover, IP101 provides 2 LED modes. If 2 <sup>nd</sup> LED mode is selected by pulling up |              |                   |                                                                                                                                                      |                                                                                                                                                         |                            |  |

| pin CRS, or                              | ıly 3 LE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Os are neede |                   | dication. Default is fir                                                                                                                             |                                                                                                                                                         |                            |  |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                   | D mode 1                                                                                                                                             | LED mode 2                                                                                                                                              |                            |  |

|                                          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LED0<br>LED1 | LINK<br>FULL DUPL | ΓV                                                                                                                                                   | LINK /ACT(blinking)                                                                                                                                     |                            |  |

|                                          | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | LED1         | 10BT /ACT(I       |                                                                                                                                                      | FULL DUPLEX/COL(blinking) 10BT                                                                                                                          |                            |  |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LED3         | 100BT /ACT(I      | 0,                                                                                                                                                   | 100BT                                                                                                                                                   |                            |  |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LED4         | COL               | (Dirriting)                                                                                                                                          | 10021                                                                                                                                                   |                            |  |

| 9                                        | PHYAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | LI/O              | PHY Address [0]                                                                                                                                      |                                                                                                                                                         |                            |  |

| 9                                        | LED0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>5</b> 0/  | Livo              | Status:<br>Mode1: Active whe                                                                                                                         | en linked.<br>en linked and blinking when transn                                                                                                        | nitting or                 |  |

| 10                                       | PHYAD1/<br>LED1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              | LI/O              | PHY Address [1] Status: Mode1: Active when in Full Duplex operation. Mode2: Active when in Full Duplex operation and blinking when collisions occur. |                                                                                                                                                         |                            |  |

| 12                                       | 2 PHYAD2/<br>LED2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              | LI/O              | transmitting or rece                                                                                                                                 | en linked in 10Base-T mode, and<br>eiving data.<br>en linked in 10Base-T mode.                                                                          | blinking when              |  |

| 13                                       | PHYAD3/<br>LED3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              | LI/O              | transmitting or rece                                                                                                                                 | hen linked in 100Base-TX and<br>eiving data.<br>en linked in 100Base-TX mode.                                                                           | blinking when              |  |

| 15                                       | 15 PHYAD4/<br>LED4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | LI/O              | PHY Address [4]<br>Status:<br>Mode1: Active who<br>Mode2: Reserved.                                                                                  | en collisions occur.                                                                                                                                    |                            |  |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Clo          | ck and Misce      | ellaneous - Crystal                                                                                                                                  | Input/Output Pins                                                                                                                                       |                            |  |

| 47                                       | X2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0                 | 25MHz output. It n<br>external 25MHz os                                                                                                              | <b>Itput:</b> Connects to crystal to provinust be left open when X1 is driver scillator. It must be left open when 5MHz oscillator or set to low with a | n with an<br>X1 is driven  |  |

| 46                                       | X1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | I                 | crystal input. If a 2 oscillator's output.                                                                                                           | out: Connects to crystal to provide 5MHz oscillator is used, connect of X1 is set to low with a pull down be applied to pin7 as clock source.           | X1 to the<br>n resistor, a |  |

| Pin no.  | Label                                        | Туре        | Description                                                                                                                                                                                                                              |  |  |  |

|----------|----------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | Clock and Miscellaneous - Miscellaneous Pins |             |                                                                                                                                                                                                                                          |  |  |  |

| 42       | RESET_N                                      | I           | <b>RESET_N:</b> Enable a low status signal will reset the chip. For a complete reset function, this pin must be asserted low for at least 10ms.                                                                                          |  |  |  |

| 48       | INTR                                         | I/O<br>(OD) | Interrupt Pin: When the MII register 17:<15> is set to high, this pin is used as an interrupt pin (Notice: this is an open drain output, so an external pulled-up resistor is needed)                                                    |  |  |  |

| 27       | TEST_ON                                      | (PD)        | <b>Test Enable:</b> Set this pin to high to enable test mode, while for normal operation, this pin does not need to be connected. (An internal weak pulled-down is used to disable test mode as a default)                               |  |  |  |

| 28       | ISET                                         | I           | <b>Transmit Bias Resistor Connection:</b> This pin should be connected to GND via a 6.2KO (1%) resistor to define driving current for transmit DAC. The resistance value may be changed, depending on experimental results of the IP101. |  |  |  |

|          |                                              |             | Power and Ground                                                                                                                                                                                                                         |  |  |  |

| 32       | REGOUT                                       | Р           | Regulator Power Output: This is a regulator power output for IP101 digital circuitry.                                                                                                                                                    |  |  |  |

| 36       | AVDD33                                       | Р           | <b>3.3V Analog power input:</b> This is a 3.3V power supply for analog circuitry, and it should be decoupled carefully.                                                                                                                  |  |  |  |

| 29,35    | AGND                                         | Р           | <b>Analog Ground:</b> These 2 pins should connect to motherboard's GND.                                                                                                                                                                  |  |  |  |

| 8        | REGIN                                        | Р           | Regulator Power Input: This is a regulator power input from Pin32. No external regulator needed.                                                                                                                                         |  |  |  |

| 14       | DVDD33                                       | Р           | <b>3.3V Digital Power input:</b> This is a 3.3V power supply for digital circuitry.                                                                                                                                                      |  |  |  |

| 11,17,45 | DGND                                         | Р           | <b>Digital Ground:</b> These 3 pins should connect to motherboard's GND.                                                                                                                                                                 |  |  |  |

# **6.0 Register Descriptions**

This section will explain the meaning and usage for each of the registers available in the IP101.

The first 7 registers, i.e., Register 0 to Register 6, are defined according to IEEE 802.3 standard, while the rest registers are defined by IC Plus Corp. and they are for internal use or reserved for other usage.

The first 2 registers contain the basic control and status register defined by IEEE standard.

Each register has its own default value, and it is placed in the right block of each register title.

| Register 0 | Register 0 : MII Control Register |                                                                                                                                                                                                                                                                                                                              |                            |  |  |  |

|------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| Address    | Name                              | Description/Usage                                                                                                                                                                                                                                                                                                            | Default value (h):<br>3100 |  |  |  |

| 15         | Reset                             | When set, this action will bring both status and control registers of the PHY to default state. This bit is self-clearing.  1 = Software reset  0 = Normal operation                                                                                                                                                         | 0, RW                      |  |  |  |

| 14         | Loop-back                         | This bit enables loop-back of transmit data to the receive data path, i.e., TXD to RXD.  1 = enable loop-back 0 = normal operation                                                                                                                                                                                           | 0, RW                      |  |  |  |

| 13         | Speed<br>Selection                | This bit sets the speed of transmission.  1 = 100Mbps  0 = 10Mbps  During 100Base-FX mode, and when this bit = 1, it indicates read only.                                                                                                                                                                                    | 1, RW                      |  |  |  |

| 12         | Auto-<br>Negotiation<br>Enable    | This bit determines the auto-negotiation function.  1 = enable auto-negotiation; bits 13 and 8 will be ignored.  0 = disable auto-negotiation; bits 13 and 0:<8> will determine the link speed and the data transfer mode, under this condition. When 100Base-FX mode is enabled, and this bit=0, it indicates read only.    | 1, RW                      |  |  |  |

| 11         | Power Down                        | This bit will turn down the power of the PHY chip and the internal crystal oscillator circuit if this bit is enabled. The MDC and MDIO are still activated for accessing to the MAC.  1 = power down 0 = normal operation                                                                                                    | 0, RW                      |  |  |  |

| 10         | Isolate                           | 1=electrically Isolate PHY from MII but not isolate MDC and MDIO 0=normal operation                                                                                                                                                                                                                                          | 0,RW                       |  |  |  |

| 9          | Restart Auto-<br>Negotiation      | This bit allows the Nway auto-negotiation function to be reset.  1 = restart auto-negotiation  0 = normal operation                                                                                                                                                                                                          | 0, RW                      |  |  |  |

| 8          | Duplex Mode                       | This bit sets the duplex mode if auto-negotiation is disabled (bit 12=0)  1 = full duplex 0 = half duplex After completing auto-negotiation, this bit will reflect the duplex status.(1: Full duplex, 0: Half duplex) When 100Base-FX mode is enabled, this bit can be set through the MDC/MDIO SMI interface or DUPLEX pin. | 1, RW                      |  |  |  |

| 7          | Collision Test                    | 1=enable COL signal test<br>0=disable COL signal test                                                                                                                                                                                                                                                                        | 0,RW                       |  |  |  |

| 6:0        | Reserved                          |                                                                                                                                                                                                                                                                                                                              |                            |  |  |  |

9/33

| Address | Name                             | Description/Usage                                                                                                                                                                                                                                                                                                          | Default value (h):<br>7849 |

|---------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 15      | 100Base-T4                       | 1 = enable 100Base-T4 support<br>0 = suppress 100Base-T4 support                                                                                                                                                                                                                                                           | 0, RO                      |

| 14      | 100Base-TX<br>Full Duplex        | 1 = enable 100Base-TX full duplex support<br>0 = suppress 100Base-TX full duplex support                                                                                                                                                                                                                                   | 1, RO                      |

| 13      | 100BASE-TX<br>Half Duplex        | 1 = enable 100Base-TX half duplex support<br>0 = suppress 100Base-TX half duplex support                                                                                                                                                                                                                                   | 1, RO                      |

| 12      | 10Base-T Full<br>Duplex          | 1 = enable 10Base-T full duplex support<br>0 = suppress 10Base-T full duplex support                                                                                                                                                                                                                                       | 1, RO                      |

| 11      | 10_Base-T<br>Half Duplex         | 1 = enable 10Base-T half duplex support<br>0 = suppress 10Base-T half duplex support                                                                                                                                                                                                                                       | 1, RO                      |

| 10:7    | Reserved                         |                                                                                                                                                                                                                                                                                                                            | 0, RO                      |

| 6       | MF Preamble<br>Suppression       | The IP101 will accept management frames with preamble suppressed. The IP101 accepts management frames without preamble. A Minimum of 32 preamble bits are required for the first SMI read/write transaction after reset. One idle bit is required between any two management transactions as per IEEE802.3u specifications | 1, RO                      |

| 5       | Auto-<br>Negotiation<br>Complete | 1 = auto-negotiation process completed 0 = auto-negotiation process not completed                                                                                                                                                                                                                                          | 0, RO                      |

| 4       | Remote Fault                     | 1 = remote fault condition detected (cleared on read) 0 = no remote fault condition detected When in 100Base-FX mode, this bit means an in-band signal Far-End-Fault is detected.                                                                                                                                          | 0, RO/LH                   |

| 3       | Auto-<br>Negotiation             | 1 = Link had not been experienced fail state<br>0 = Link had been experienced fail state                                                                                                                                                                                                                                   | 1, RO                      |

| 2       | Link Status                      | 1 = valid link established<br>0 = no valid link established                                                                                                                                                                                                                                                                | 0, RO/LL                   |

| 1       | Jabber Detect                    | 1 = jabber condition detected<br>0 = no jabber condition detected                                                                                                                                                                                                                                                          | 0, RO/LH                   |

| 0       | Extended<br>Capability           | 1 = extended register capability 0 = basic register capability only                                                                                                                                                                                                                                                        | 1, RO                      |

| Register 2 | Register 2 : PHY Identifier Register 1 |                                                |                            |  |  |  |

|------------|----------------------------------------|------------------------------------------------|----------------------------|--|--|--|

| Address    | Name                                   | Description/Usage                              | Default value (h):<br>0243 |  |  |  |

| 15:0       | PHYID1                                 | PHY identifier ID for software recognize IP101 | 0X0243, RO                 |  |  |  |

| Register 3 : PHY Identifier Register 2 |        |                                          |                            |  |

|----------------------------------------|--------|------------------------------------------|----------------------------|--|

| Address                                | Name   | Description/Usage                        | Default value (h):<br>0C50 |  |

| 15:0                                   | PHYID2 | PHY identifier ID for software recognize | 0X0C50, RO                 |  |

Note: Register 2 and register 3 identifier registers altogether consist of Vender model, model revision number and Organizationally Unique identifier (OUI) information. Total of 32 bits allocate in these 2 registers and they can return all zeroes in all bits if desired. Register 2 contains OUI's most significant bits and OUI's lest significant bits, Vender model, Model revision number are allocated in register 3.

Register 4 lists the advertised abilities during auto-negotiation for what will be transmitted to IP101's Link Partner.

| Register 4 | : Auto-Negotiat      | ion Advertisement Register                                                                                                     |                            |

|------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Address    | Name                 | Description/Usage                                                                                                              | Default value (h):<br>0001 |

| 15         | NP                   | Next Page bit.  0 = transmitting the primary capability data page  1 = transmitting the protocol specific data page            | 0, RO                      |

| 14         | Reserved             |                                                                                                                                | 0, RO                      |

| 13         | RF                   | 1 = advertise remote fault detection capability     0 = do not advertise remote fault detection capability                     | 0, RW                      |

| 12         | Reserved             |                                                                                                                                | 0, RO                      |

| 11         | Asymmetric.<br>Pause | 1 = asymmetric flow control is supported by local node<br>0 = asymmetric flow control is NOT supported by local node           | 0, RW                      |

| 10         | Pause                | 1 = flow control is supported by local node<br>0 = flow control is NOT supported by local node                                 | 0, RW                      |

| 9          | T4                   | 1 = 100Base-T4 is supported by local node<br>0 = 100Base-T4 not supported by local node                                        | 0, RO                      |

| 8          | TX Full<br>Duplex    | 1 = 100Base-TX full duplex is supported by local node<br>0 = 100Base-TX full duplex not supported by local node                | 1, RW                      |

| 7          | TX                   | 1 = 100Base-TX is supported by local node<br>0 = 100Base-TX not supported by local node                                        | 1, RW                      |

| 6          | 10 Full<br>Duplex    | 1 = 10Base-T full duplex supported by local node<br>0 = 10Base-T full duplex not supported by local node                       | 1, RW                      |

| 5          | 10                   | 1 = 10Base-T is supported by local node<br>0 = 10Base-T not supported by local node                                            | 1, RW                      |

| 4:0        | Selector             | Binary encoded selector supported by this node. Currently only CSMA/CD <00001> is specified. No other protocols are supported. | <00001>, RO                |

Register 5 describes the advertised abilities of the Link Partner's PHY when it is receiving data during the process of auto-negotiation. If next-pages are supported, this register may change after the auto-negotiation has established.

| Register 5 | Register 5 : Auto-Negotiation Link Partner Ability Register |                                                                                                                                                                                             |                            |  |  |  |

|------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|

| Address    | Name                                                        | Description/Usage                                                                                                                                                                           | Default value (h):<br>0080 |  |  |  |

| 15         | Next Page                                                   | Next Page bit. 0 = transmitting the primary capability data page 1 = transmitting the protocol specific data page                                                                           | 0, RO                      |  |  |  |

| 14         | Acknowledge                                                 | 1 = link partner acknowledges reception of local node's capability data word 0 = no acknowledgement                                                                                         | 0, RO                      |  |  |  |

| 13         | Remote Fault                                                | <ul><li>1 = link partner is indicating a remote fault</li><li>0 = link partner does not indicate a remote fault</li></ul>                                                                   | 0, RO                      |  |  |  |

| 12         | Reserved                                                    |                                                                                                                                                                                             | 0, RO                      |  |  |  |

| 11         | Asymmetric.<br>Pause                                        | 1 = asymmetric flow control is supported by local node<br>0 = asymmetric flow control is NOT supported by local node                                                                        | 0, RO                      |  |  |  |

| 10         | Pause                                                       | 1 = flow control is supported by Link partner<br>0 = flow control is NOT supported by Link partner                                                                                          | 0, RO                      |  |  |  |

| 9          | T4                                                          | 1 = 100Base-T4 is supported by link partner<br>0 = 100Base-T4 not supported by link partner                                                                                                 | 0, RO                      |  |  |  |

| 8          | TXFD                                                        | 1 = 100Base-TX full duplex is supported by link partner<br>0 = 100Base-TX full duplex not supported by link partner                                                                         | 0, RO                      |  |  |  |

| 7          | 100BASE-TX                                                  | 1 = 100Base-TX is supported by link partner<br>0 = 100Base-TX not supported by link partner<br>This bit will also be set after the link in 100Base is established<br>by parallel detection. | 1, RO                      |  |  |  |

| 6          | 10FD                                                        | 1 = 10Base-T full duplex is supported by link partner<br>0 = 10Base-T full duplex not supported by link partner                                                                             | 0, RO                      |  |  |  |

| 5          | 10Base-T                                                    | 1 = 10Base-T is supported by link partner<br>0 = 10Base-T not supported by link partner<br>This bit will also be set after the link in 10Base is established<br>by parallel detection.      | 0, RO                      |  |  |  |

| 4:0        | Selector                                                    | Link Partner's binary encoded node selector Currently only CSMA/CD <00001> is specified                                                                                                     | <00000>, RO                |  |  |  |

Register 6 defines more auto-negotiation registers to meet the requirement.

| Register 6 | Register 6 : Auto-Negotiation Expansion Register |                                                                                                                                                                                                     |                            |  |  |

|------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

| Address    | Name                                             | Description/Usage                                                                                                                                                                                   | Default value (h):<br>0000 |  |  |

| 15:5       | Reserved                                         | This bit is always set to 0.                                                                                                                                                                        |                            |  |  |

| 4          | MLF                                              | This status indicates if a multiple link fault has occurred.  1 = fault occurred  0 = no fault occurred                                                                                             | 0, RO                      |  |  |

| 3          | LP_NP_ABLE                                       | This status indicates if the link partner supports Next Page negotiation.  1 = supported 0 = not supported                                                                                          | 0, RO                      |  |  |

| 2          | NP_ABLE                                          | This bit indicates if the device is able to send additional Next Pages.                                                                                                                             | 0, RO                      |  |  |

| 1          | PAGE_RX                                          | This bit will be set if a new link code word page has been received. It is cleared automatically after the auto-negotiation link partner's ability register (register 5) is read by the management. | 0, RO                      |  |  |

| 0          | LP_NW_ABLE                                       | 1 = link partner supports Nway auto-negotiation.                                                                                                                                                    | 0, RO                      |  |  |

Register 16 and register 17 are defined by IC Plus Corp. and it is for internal testing purpose.

| Register 1 | Register 16 : PHY Spec. Control Register |                                                                                                                                                                                                  |                            |  |  |

|------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|

| Address    | Name                                     | Description/Usage                                                                                                                                                                                | Default value (h):<br>0000 |  |  |

| 15         | Debug Mode                               | 0 = IP101 operates at normal mode<br>1 = IP101 operates at debug mode<br>(Notice the functionalities of bit 16:<14>, 16:<13>, 16:<12>,<br>and 16:<4:0> depend on the setting of this bit 16:<15> | 0, R/W                     |  |  |

| 14:12      | Reserved                                 |                                                                                                                                                                                                  |                            |  |  |

| 11         | MDI disable                              | Set high to disable the automatic switch of MDI and MDI-X modes                                                                                                                                  | 0, R/W                     |  |  |

| 10         | Heart Beat<br>Enable                     | Heart beat function enable at 10Base-T                                                                                                                                                           | 0, R/W                     |  |  |

| 9          | Jabber<br>Enable                         | Jabber function enable at 10Base-T                                                                                                                                                               | 0, R/W                     |  |  |

| 8          | Far-End Fault<br>Enable/Disable          | To enable or disable the functionality of Far-End Fault  Mode Enable Disable  100Base-TX 1 0  100Base-FX 0 1                                                                                     | 0, R/W                     |  |  |

| 7          | Analog<br>Power Saving<br>Disable        | Set high to disable the power saving during auto-negotiation                                                                                                                                     | 0, R/W                     |  |  |

| 6          | Reserved                                 |                                                                                                                                                                                                  | 0, R/W                     |  |  |

| 5          | Bypass DSP reset                         | Set high to bypass the reset DSP mechanism in PCS sub-layer                                                                                                                                      | 0, R/W                     |  |  |

| 4:3        | Reserved                                 |                                                                                                                                                                                                  |                            |  |  |

| 2          | Repeater<br>Mode                         | Set high to put IP101 into repeater mode                                                                                                                                                         | 0, R/W                     |  |  |

| 1          | APS Mode                                 | Set high to enable Auto Power Saving mode                                                                                                                                                        | 0, R/W                     |  |  |

| 0          | Analog Off                               | Set high to power down analog transceiver                                                                                                                                                        | 0, R/W                     |  |  |

| Address | Name                    | Description/Usage                                                                         | Default value (h):<br>0E00 |

|---------|-------------------------|-------------------------------------------------------------------------------------------|----------------------------|

| 15      | INTR pin<br>used        | Set high to enable pin48 as an interrupt pin, or high impedance is presented at this pin  | 0, R/W                     |

| 14:12   | Reserved                |                                                                                           |                            |

| 11      | All Mask                | When this bit is set high, changes in all events will not cause an interrupt              | 1, R/W                     |

| 10      | Speed Mask              | When this bit is set high, changes in speed mode will not cause an interrupt              | 1, R/W                     |

| 9       | Duplex Mask             | When this bit is set high, changes in duplex mode will not cause an interrupt             | 1, R/W                     |

| 8       | Link Mask               | When this bit is set high, changes in link status will not cause an interrupt             | 1, R/W                     |

| 7       | Arbiter State<br>Enable | When this bit is set high, changes in N-WAY arbiter state machine will cause an interrupt | 0, R/W                     |

| 6       | Arbiter State<br>Change | Flag to indicate N-WAY arbiter change interrupt                                           | 0, R/W                     |

| 5:3     | Reserved                |                                                                                           | 0, R/W                     |

| 2       | Link Status<br>Change   | Flag to indicate link status change interrupt                                             | 0, R/W                     |

| 1       | Speed<br>Change         | Flag to indicate speed change interrupt                                                   | 0, R/W                     |

| 0       | Duplex<br>Change        | Flag to indicate duplex change interrupt                                                  | 0, R/W                     |

## 7.0 Functional Description

IP101 10/100Mbps Ethernet PHY Transceiver integrates 100 Base-TX, 100 Base-FX and 10 Base-T modules into a single chip. IP101 acts as an interface between physical signaling and Media Access Controller (MAC).

IP101 has several major functions:

- 1. **PCS layer (Physical Coding Sub-Layer)**: This function contains transmit, receive and carrier sense functional circuitries.

- Management interface: Media Independent Interface (MII) or Reduced Management Interface (RMII) registers contains information for communication with other MAC.

- Auto-Negotiation: Communication conditions between 2 PHY transceivers. IP101 advertise its own ability and also detects corresponding operational mode from the other party, eventually both sides will come to an agreement for their optimized transmission mode.

IP101's major features included:

- 1. Flow Control ability

- 2. LED configuration access

- 3. Operation modes for both full and half duplex