### **QLogic Corporation**

# ISP2200 Intelligent Fibre Channel Processors

# **Data Sheet**

### **Features**

- Available in two versions:

- ☐ 66-MHz, 64-bit PCI host bus interface (ISP2200/66)

- □ 33-MHz, 64-bit PCI host bus interface (ISP2200/33)

- Compliance with *PCI Local Bus Specification* revision 2.1

- Supports full-duplex communications in all Fibre Channel topologies

- Compliance with ANSI SCSI standards for class 2 and class 3 service:

- ☐ Fibre Channel Arbitrated Loop (FC-AL-2) working draft, rev 5.7, August 22, 1997

- ☐ Fibre Channel Fabric Loop Attachment (FC-FLA) working draft, rev 2.7, August 12, 1997

- ☐ Fibre Channel Private Loop SCSI Direct Attach (FC-PLDA) working draft, rev 2.0, August 4, 1997

- Supports Fibre Channel protocol SCSI (FCP-SCSI) and Fibre Channel IP protocols

- Compliance with *PCI Bus Power Management Interface Specification* Revision 1.0 (PC97)

- Supports up to 200 Mbytes/sec sustained Fibre Channel data transfer rate

- Initiator, initiator/target, and target modes

- Onboard, enhanced RISC processor to execute operations at the I/O control-block (IOCB) level from the host memory

- Onboard gigabit serial transceivers

- Supports external transceivers with a 10-bit interface

- Supports PCI dual-address cycle (64-bit addressing) and cache commands

- No host intervention required to execute SCSI and IP operations from start to finish

- Simultaneous, multiple logical threads

- Full duplex frame buffer architecture

- Supports JTAG boundary scan

- Supports multi-ID aliasing

### **Product Description**

The ISP2200 is a single-chip, highly integrated, bus master, Fibre Channel processor that targets storage, clustering, and networking applications. This chip connects the PCI bus to a Fibre Channel loop or to a point-to-point Fibre Channel port.

The ISP2200 is pin compatible with the ISP2100A.

The ISP2200 is a fully autonomous device, capable of managing multiple I/O operations and associated data transfers from start to finish without host intervention.

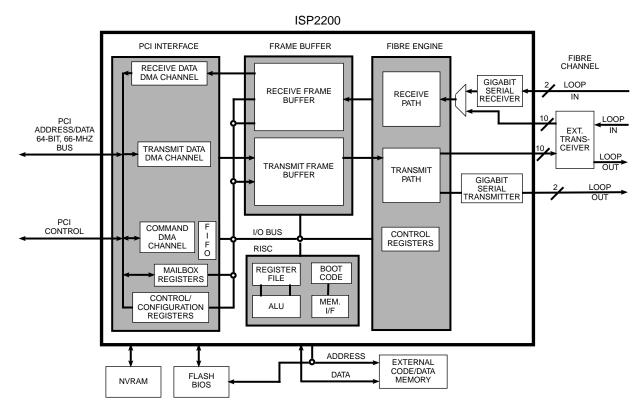

The ISP2200 provides power management support in accordance with the *PCIBus Power Management Interface Specification*. The ISP2200 block diagram is illustrated in figure 1.

Figure 1. ISP2200 Block Diagram

### ISP Initiator/Target SCSI and IP Firmware

The ISP2200 firmware implements a multitasking host adapter that provides the host system with IP communications and complete SCSI command and data transport capabilities, thus freeing the host system from the simultaneous execution of SCSI and IP traffic. The firmware provides two interfaces to the host system: the command interface and the Fibre Channel transport interface. The single-threaded command interface facilitates debugging, configuration, and recovering errors. The multithreaded transport interface maximizes use of the Fibre Channel and host buses.

The ISP2200 can operate simultaneously in initiator and target modes.

### **Software Drivers**

The ISP2200 supports a host software interface similar to the QLogic parallel SCSI and FC-AL processor family, which includes the ISP1020, ISP1040, ISP1080, ISP2100, and ISP2100A chips. Existing ISP2100A software drivers are easily modified to support the ISP2200.

BIOS firmware is available for the ISP2200. FCP-SCSI and IP software drivers are supported for the following operating systems:

- I<sub>2</sub>O

- Novell NetWare

- OS/2

- SCO UNIX

- UnixWare

- Windows 95

- Windows NT

- Solaris; x86 and SPARC systems

# **Subsystem Organization**

To maximize I/O throughput and improve host and Fibre Channel utilization, the ISP2200 incorporates a high-speed, proprietary RISC processor; a Fibre Channel protocol manager (FPM); integrated frame buffer memory; and a host bus, three-channel, bus master DMA controller. The FPM and host bus DMA controller operate independently and concurrently under the control of the onboard RISC processor for maximum system performance.

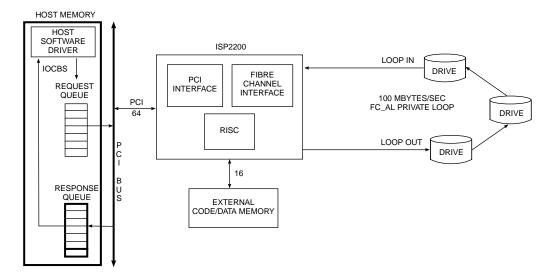

The complete I/O subsystem solution using the ISP2200 and associated supporting memory devices is shown in figure 2.

Figure 2. I/O Subsystem Design Using the ISP2200

## **Interfaces**

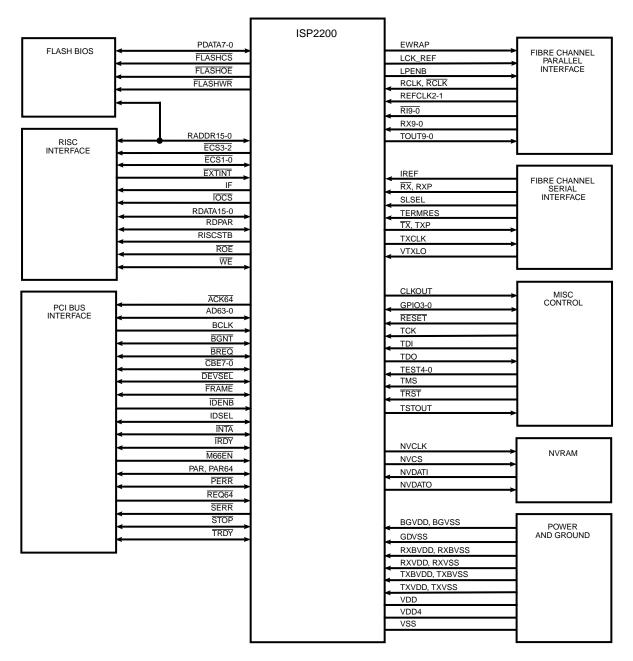

The ISP2200 interfaces consist of the FC-AL interface, PCI bus interface, RISC interface, flash BIOS interface, and NVRAM control. Pins that support these interfaces and other chip operations are shown in figure 3.

Figure 3. ISP2200 Functional Signal Grouping

### **Fibre Channel Interface**

The ISP2200 provides onboard gigabit transceivers for direct connection to the Fibre Channel ports on copper media. A standard 10-bit interface is also provided to connect to external transceivers, if desired.

### **Fibre Channel Protocol Manager**

The ISP2200 FPM supports the following:

- Support for one Fibre Channel port

- 200 Mbytes/sec sustained, full-duplex data transfer rate

- 10-bit interface to external transceivers

- Gigabit serial interface

- Integrated frame buffer that supports up to 2112-byte frame payload

The FPM includes an 8b/10b encoder and decoder, an elasticity buffer for clock skew management, and an FC-AL state machine. The FPM transmits and receives at the full Fibre Channel rate of 106.25 Mbytes/sec. The on-chip frame buffer includes separate areas for received data and transmit data, as well as areas for managing special frames such as command and response. The FPM receive path validates and routes frames received from the Fibre Channel to the appropriate area in the frame buffer. The transmit path transmits frames from the frame buffer to the Fibre Channel. The FPM automatically handles frame delimiters and frame control.

#### **PCI Interface**

The ISP2200 PCI interface supports the following:

- 33-MHz or 66-MHz (ISP2200/66 only), 64-bit, intelligent bus master interface for fetching IOCBs and data transfers

- 64-bit host memory addressing (dual address cycle)

- Backward compatible to 32-bit PCI

- Three-channel DMA controller

- 16-bit slave mode for communication with host

- Pipelined DMA registers for efficient scatter/gather operations

- 32-bit DMA transfer counter for I/O transfer length of up to four gigabytes

- Support for PCI cache commands

- Support for flash BIOS PROM

- Support for subsystem ID

- 3.3V and 5.0V tolerant PCI I/O buffers

The ISP2200 is designed to interface directly to the PCI bus and operate as a 64-bit DMA bus master, which is backward compatible to 32-bit operation. This function is accomplished through a PCI bus interface unit (PBIU) containing an onboard DMA controller. The PBIU generates and samples PCI control signals, generates host memory addresses, and facilitates the transfer of data

between host memory and the onboard frame buffer. It also allows the host to access the ISP2200 internal registers and communicate with the onboard RISC processor.

The ISP2200 supports the minimum power management capabilities specified in revision 1.0 of the *PCI Bus Power Management Interface Specification*, which defines power states D0-D3, where D0 provides maximum power consumption and D3 provides minimal power consumption. The D3 power state is entered by either software (D3 *hot*) or by physically removing power (D3 *cold*). Hot and cold refer to the presence or absence of VCC, respectively.

The ISP2200 supports power states D0, D3 hot, and D3 cold.

The ISP2200 onboard DMA controller consists of three independent DMA channels that initiate transactions on the PCI bus and transfer data between the host memory and frame buffer. The command DMA channel is used mainly by the RISC processor for small transfers, such as fetching commands from and writing status information to the host memory over the PCI bus. The two data DMA channels, one for transmit and one for receive, transfer data between the FC-AL and the PCI bus, allowing for fast context switching.

The PBIU internally arbitrates between the two data DMA channels and the command DMA channel and alternately services them. Each DMA channel has a set of DMA registers that are programmed for transfers by the RISC processor.

#### **RISC Processor**

The ISP2200 RISC processor supports the following:

- Execution of multiple I/O control blocks from the host memory

- Reduced host intervention and interrupt overhead

- One interrupt or less per I/O operation

One of the major features of the ISP2200 is its ability to handle complete I/O transactions from start to finish with no intervention from the host. This high level of integration is accomplished with an onboard RISC processor. The ISP2200 RISC processor controls the chip interfaces; executes simultaneous, multiple IOCBs; and maintains the required thread information for each transfer.

# **Packaging**

The ISP2200 is available in a 256-pin ball grid array (BGA) package and is pin compatible with the ISP2100A.

OS/2, Windows NT, and Windows 95 are trademarks or registered trademarks of Microsoft Corp.

Novell and NetWare are registered trademarks of Novell, Inc.

SCO UNIX is a registered trademark of Santa Cruz Operations.

SPARC is a trademark of SPARC International, Inc.

UNIX is a trademark of AT&T Bell Laboratories.

All other brand and product names are trademarks or registered trademarks of their respective holders.

Specifications are subject to change without notice.

QLogic is a trademark of QLogic Corporation.

©June 2, 1998 QLogic Corporation, 3545 Harbor Blvd., Costa Mesa, CA 92626, (800) ON-CHIP-1 or (714) 438-2200