TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# J T M P 0 4 0 2 0 - X X X S

# CMOS 4 BIT LL MICROCONTROLLER (LL : LOW POWER CONSUMPTION &

### LOW VOLTAGE OPERATION MICROCONTROLLER)

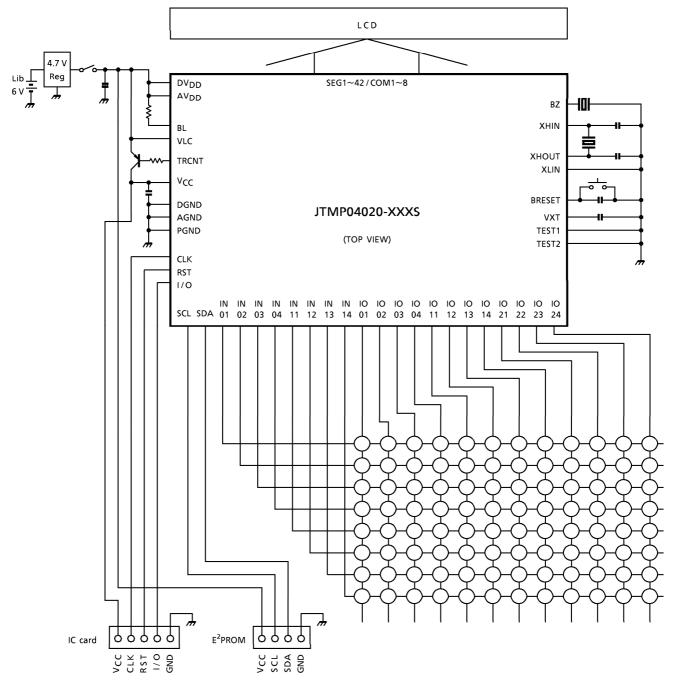

JTMP04020-XXXS is a high-performance LL microcontroller developed for use in contact-type personal reader / writers.

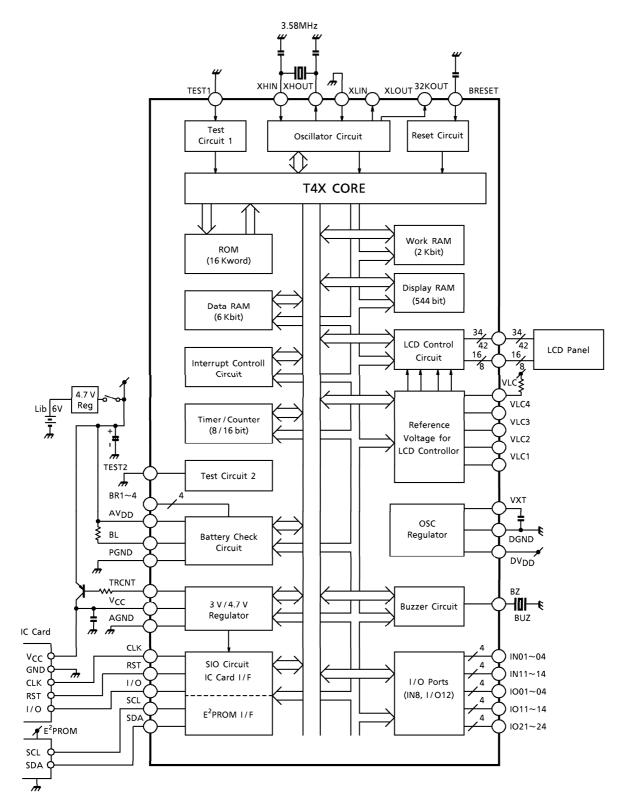

JTMP04020-XXXS combines a 4-bit high-performance CPU, memory (work RAM, data RAM, and program ROM), LCD LL controller driver, multi-function timers, IC card power supply (3 V / 5 V switchable), IC card interface, external memory interface, and battery voltage detector circuit on a single chip.

The basic features are as follows :

#### FEATURES

Number of instructions 56 Minimum instruction execution time : 61 µs (at 32.768 kHz) 57 µs (at 35 kHz)  $1 \mu s$  (at 2 MHz / 3.0 V) 560 ns (at 3.58 MHz / 4.7 V) Oscillator circuit 1 POWER SUPPLY HIGH SPEED LOW SPEED VOLTAGE 3.0 V 2.0 MHz (X'tal) 32.768 kHz (X'tal) 4.7 V 3.58 MHz (X'tal) 35 kHz (Built-in CR) Built-in ROM size 16 K words (1 word = 16 bit) 1 Built-in RAM size : Work RAM 512 x 4 bit 2 Data RAM 6 Kbit **Display RAM** 544 bit (16 com  $\times$  34 seg) 336 bit  $(8 \text{ com} \times 42 \text{ seg})$ 1 Input pin 8 pins (with interrupts) : Input/output pin 12 pins (output pins for key strobe) : Output pin A pin for buzzer output : 4 external interrupts (input pin, IC card I/F, external memory Interrupts I/F) 3 internal interrupts (timer/counter, timing) 8 bit  $\times$  2 ch or 16 bit  $\times$  1 ch Timer (Switchable by software) LCD display driver controller ÷  $34 \text{ seg} \times 16 \text{ com or } 42 \text{ seg} \times 8 \text{ com}$ Watchdog timer Timer/counter can be used as watchdog timer. Operating power supply voltage 3.0 V@f = 2 MHz / 4.7 V@f = 3.58 MHz: 980910EBA1

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

**BLOCK DIAGRAM**

### <u>TOSHIBA</u>

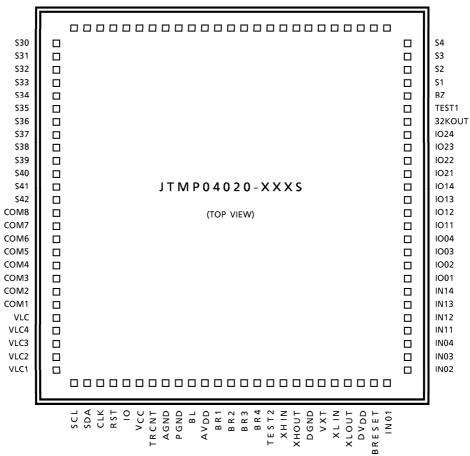

#### PAD / PIN LAYOUT

Pad Assignment

###

Chip size =  $4.92 \text{ mm} \times 5.17 \text{ mm}$ Chip Thickness =  $450 \mu \text{m}$ Substrate voltage = DGND

### **TOSHIBA**

Pad Coordinates

| No. | PAD NAME         | X POINT | Y POINT | No. | PAD NAME  | X POINT | Y POIN |

|-----|------------------|---------|---------|-----|-----------|---------|--------|

| 1   | SCL              | - 1840  | - 2446  | 45  | 32KOUT    | 2324    | 863    |

| 2   | SDA              | - 1690  | - 2446  | 46  | TEST1     | 2324    | 1013   |

| 3   | CLK              | - 1540  | - 2446  | 47  | BZ        | 2324    | 1163   |

| 4   | RST              | - 1390  | - 2446  | 48  | S1        | 2324    | 1313   |

| 5   | 10               | - 1240  | - 2446  | 49  | S2        | 2324    | 1463   |

| 6   | Vcc              | - 1090  | - 2446  | 50  | S3        | 2324    | 1613   |

| 7   | TRCNT            | - 940   | - 2446  | 51  | S4        | 2324    | 1763   |

| 8   | AGND             | - 789   | - 2446  | 52  | S5        | 1708    | 244    |

| 9   | PGND             | - 639   | - 2446  | 53  | S6        | 1558    | 244    |

| 10  | BL               | - 489   | - 2446  | 54  | S7        | 1408    | 244    |

| 11  | AV <sub>DD</sub> | - 339   | - 2446  | 55  | S8        | 1258    | 244    |

| 12  | BR1              | – 189   | - 2446  | 56  | S9        | 1108    | 244    |

| 13  | BR2              | - 39    | - 2446  | 57  | S10       | 958     | 244    |

| 14  | BR3              | 111     | - 2446  | 58  | S11       | 807     | 244    |

| 15  | BR4              | 261     | - 2446  | 59  | S12       | 657     | 244    |

| 16  | TEST2            | 411     | - 2446  | 60  | S13       | 507     | 244    |

| 17  | XHIN             | 561     | - 2446  | 61  | S14       | 357     | 244    |

| 18  | XHOUT            | 712     | - 2446  | 62  | S15       | 207     | 244    |

| 19  | DGND             | 862     | - 2446  | 63  | S16       | 57      | 244    |

| 20  | VXT              | 1012    | - 2446  | 64  | S17       | - 93    | 244    |

| 21  | XLIN             | 1162    | - 2446  | 65  | S18       | - 243   | 244    |

| 22  | XLOUT            | 1312    | - 2446  | 66  | S19       | - 393   | 244    |

| 23  | DV <sub>DD</sub> | 1462    | - 2446  | 67  | S20       | - 543   | 244    |

| 24  | BRESET           | 1612    | - 2446  | 68  | S21       | - 694   | 244    |

| 25  | IN01             | 1762    | - 2446  | 69  | S22       | - 844   | 244    |

| 26  | IN02             | 2324    | – 1989  | 70  | S23       | - 994   | 244    |

| 27  | IN03             | 2324    | – 1839  | 71  | S24       | - 1144  | 244    |

| 28  | IN04             | 2324    | – 1689  | 72  | S25       | - 1294  | 244    |

| 29  | IN11             | 2324    | – 1539  | 73  | S26       | - 1444  | 244    |

| 30  | IN12             | 2324    | – 1389  | 74  | S27       | – 1594  | 244    |

| 31  | IN13             | 2324    | – 1239  | 75  | S28       | - 1744  | 244    |

| 32  | IN14             | 2324    | – 1089  | 76  | S29       | – 1894  | 244    |

| 33  | IO01             | 2324    | - 938   | 77  | S30       | - 2324  | 1778   |

| 34  | 1002             | 2324    | - 788   | 78  | S31       | - 2324  | 162    |

| 35  | IO03             | 2324    | - 638   | 79  | S32       | - 2324  | 147    |

| 36  | 1004             | 2324    | - 488   | 80  | S33       | - 2324  | 132    |

| 37  | IO11             | 2324    | - 338   | 81  | S34       | - 2324  | 117    |

| 38  | IO12             | 2324    | – 188   | 82  | COM16/S31 | - 2324  | 102    |

| 39  | IO13             | 2324    | - 38    | 83  | COM15/S36 | - 2324  | 87     |

| 40  | IO14             | 2324    | 112     | 84  | COM14/S37 | - 2324  | 72     |

| 41  | IO21             | 2324    | 262     | 85  | COM13/S38 | - 2324  | 57     |

| 42  | 1022             | 2324    | 412     | 86  | COM12/S39 | - 2324  | 42     |

| 43  | IO23             | 2324    | 563     | 87  | COM11/S40 | - 2324  | 27     |

| 44  | 1024             | 2324    | 713     | 88  | COM10/S41 | - 2324  | 12     |

2000-04-20 4/67

## **TOSHIBA**

| No. | PAD NAME   | X POINT | Y POINT | No. | PAD NAME | X POINT | Y POINT |

|-----|------------|---------|---------|-----|----------|---------|---------|

| 89  | COM9 / S42 | - 2324  | - 24    | 96  | COM2     | - 2324  | – 1074  |

| 90  | COM8       | - 2324  | - 174   | 97  | COM1     | - 2324  | – 1224  |

| 91  | COM7       | - 2324  | - 324   | 98  | VLC      | - 2324  | – 1375  |

| 92  | COM6       | - 2324  | - 474   | 99  | VLC4     | - 2324  | - 1525  |

| 93  | COM5       | - 2324  | - 624   | 100 | VLC3     | - 2324  | – 1675  |

| 94  | COM4       | - 2324  | - 774   | 101 | VLC2     | - 2324  | – 1825  |

| 95  | COM3       | - 2324  | - 924   | 102 | VLC1     | - 2324  | – 1975  |

### <u>TOSHIBA</u>

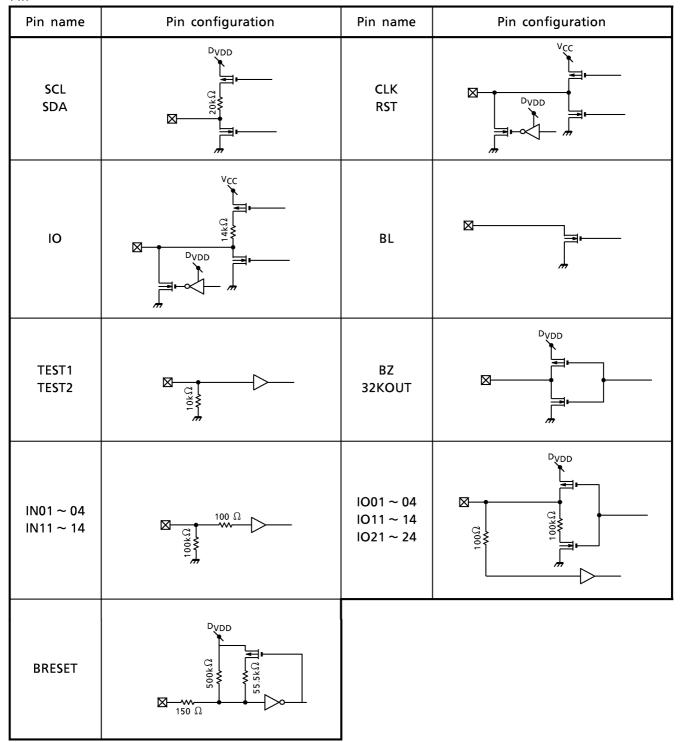

Pin Description

| PIN NAME         | FUNCTION                                                                                   | Remarks                  |

|------------------|--------------------------------------------------------------------------------------------|--------------------------|

| DV <sub>DD</sub> | Power supply voltage for logic signals (+)                                                 |                          |

| AV <sub>DD</sub> | Power supply voltage for analog signals (+)                                                |                          |

| DGND             | GND for logic signals (-)                                                                  |                          |

| AGND             | GND for analog signals (-)                                                                 |                          |

| PGND             | GND for BL pin (-)                                                                         |                          |

| BL               | Pseudo-load control for battery voltage difference detection                               | Cannot be used<br>at 3 V |

| BR1 to 4         | Battery voltage differential detection level setting and external resistor connecting pins | Cannot be used<br>at 3 V |

| TRCNT            | External transistor controller                                                             |                          |

| V <sub>CC</sub>  | Power supply voltage for IC card                                                           |                          |

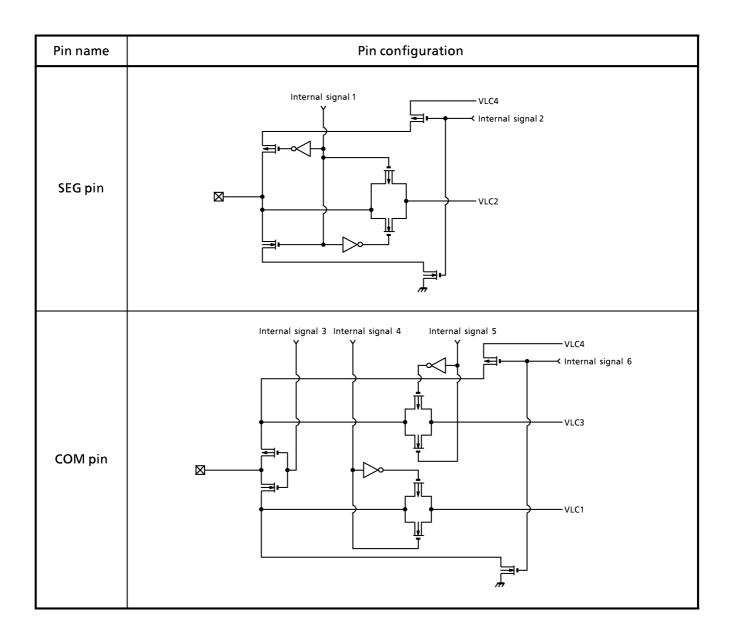

| SEG1~42 (1~34)   | LCD segment outputs                                                                        |                          |

| COM1~8 (1~16)    | LCD common outputs                                                                         |                          |

| VLC1~4           | Reference voltage for LCD                                                                  |                          |

| VLC              | Power supply voltage for LCD (+)                                                           |                          |

| 32KOUT           | Low-speed oscillation frequency output                                                     |                          |

| CLK              | CLK output for IC card                                                                     |                          |

| 1/0              | Data I/O for IC card                                                                       |                          |

| RST              | Reset output for IC card                                                                   |                          |

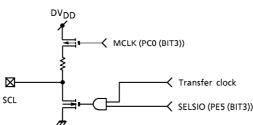

| SCL              | CLK output for external memory                                                             |                          |

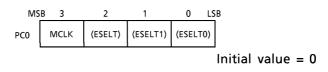

| SDA              | Data I/O for external memory                                                               |                          |

| IN01~04          | Input ports (with interruption)                                                            |                          |

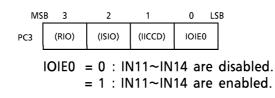

| IN11~14          | Input ports (with interruption)                                                            |                          |

| IO01~04          | I/O ports                                                                                  |                          |

| IO11~14          | I/O ports                                                                                  |                          |

| IO21~24          | I/O ports                                                                                  |                          |

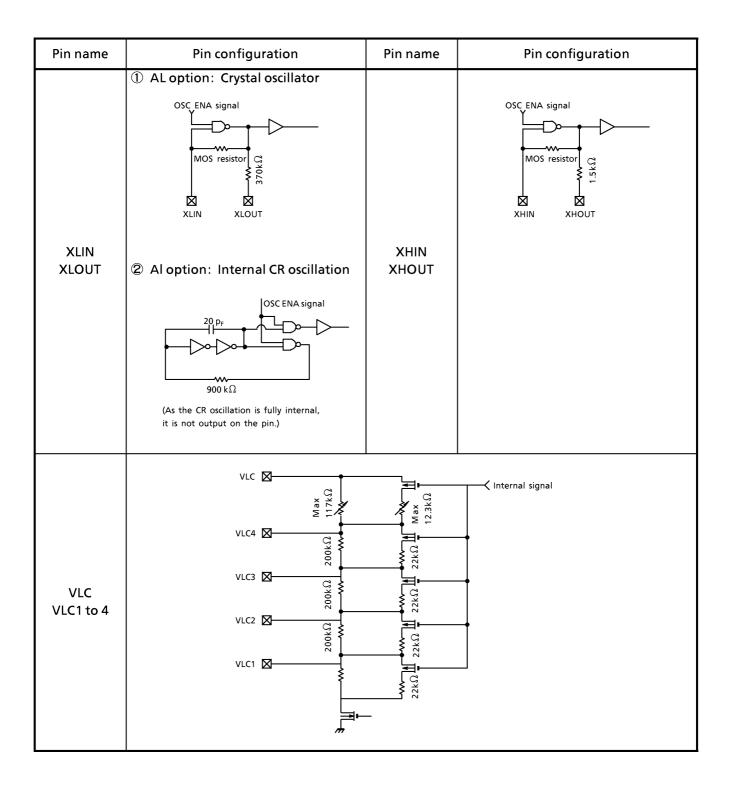

| XHIN~XHOUT       | Crystal connection pin for high-speed oscillator                                           |                          |

| XLIN~XLOUT       | Crystal connection pin for low-speed oscillator                                            |                          |

| BZ               | Buzzer output                                                                              |                          |

| BRESET           | Reset input (low active)                                                                   |                          |

| TEST1            | Test input for logic signal                                                                |                          |

| TEST2            | Test input for analog signal                                                               |                          |

(Note) : Pay attention to the following notes when designing circuit board layout.

(1) Do not locate the high-speed and low-speed clocks line side by side.

(2) Do not locate the clock line and the large current line side by side.

(3) Do not locate lines with analog characteristics and lines with large current line side by side.

(4) Do not locate lines with analog characteristics and clock lines side by side.

Pin

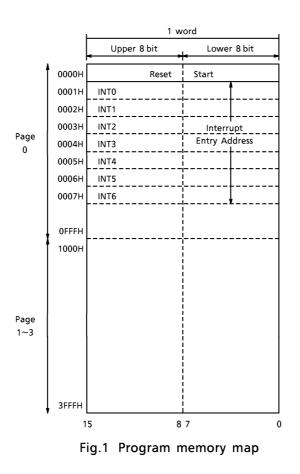

#### **MEMORY MAP**

1. Program ROM

Program ROM consists of 16 bits per 1 word. Op-code and operand are executed in one word units. Program ROM consists of 4 K words per page. The internal program ROM area is 4 pages (16 K words).

This program ROM area can be used for storing constant data. In this case, it can be used in byte units (1 byte = 8 bits).

(Note) : Use the CALL instruction to write the interrupt entry address. Write NOP for unused interrupts.

| : | CALL A | ; INTO |

|---|--------|--------|

|   | NOP    | ; INT1 |

|   | CALL B | ; INT2 |

|   | NOP    | ; INT3 |

|   | NOP    | ; INT4 |

|   | NOP    | ; INT5 |

|   | NOP    | ; INT6 |

|   |        |        |

Example

### **TOSHIBA**

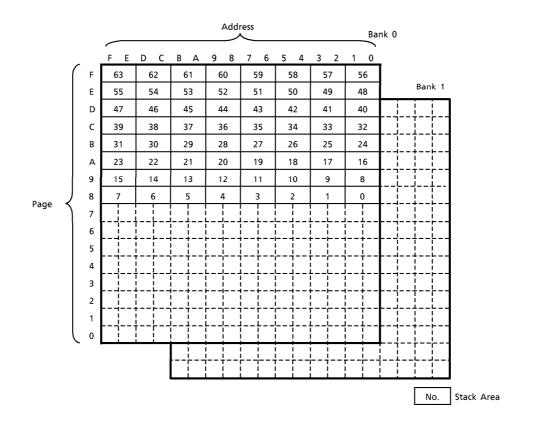

#### 2. Work RAM

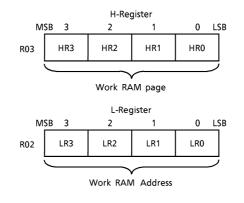

Fig.2 Work RAM

## roshiba

LR

XXXX

XXXX

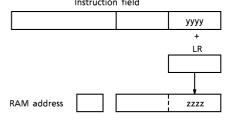

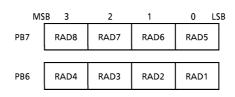

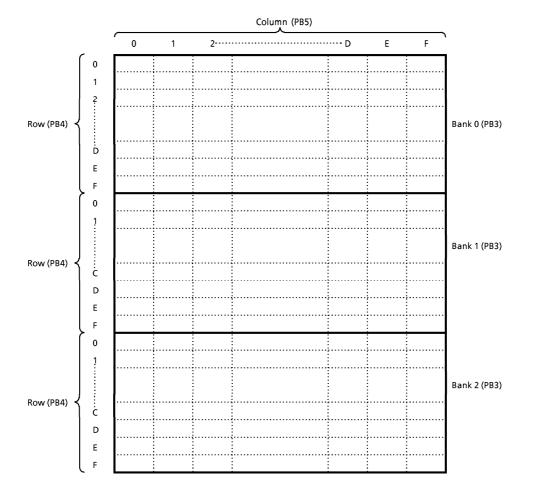

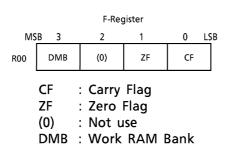

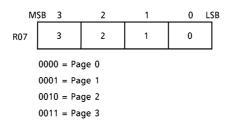

Work RAM consists of  $512 \times 4$  bits. R/W is performed at the address specified by bellows. (1) Indirectly addressing mode (Fig.3 (a)) DMB HR DMB in F-reg, H, L-reg specify the Work RAM address. (DMB : bank, H-reg : page, L-reg : address) RAM address EX. LD A, M :  $A \leftarrow RAM$  (HL) (a) Indirectly addressing (2) Directly addressing mode (Fig.3 (b)) Instruction field Immediate data (8 bits) in instruction specify the Work хххх XXXX ÷. RAM page and address. or хххх Bank is specified by DMB in F-reg. DMB LD 2CH, 0AH : RAM (2CH)  $\leftarrow$  AH EX. RAM address хххх (b) Directly addressing (3) Index addressing mode (Fig.3 (c)) Instruction field Address is specified by adding 4 bits (L-reg) and the immediate data (4 bits) in instruction. LDRI 4H, 3H EX. : RAM (HL + 4H)

$\leftarrow$  RAM (3H, L)  $L \leftarrow L + 1, A \leftarrow A - 1$

(c) Index addressing

Fig.3 Addressing mode

When using the "CALL/CALLS" instruction or start the interruption routine, the data of program counter and Program memory bank are stored in Stack area.

Then, using "RET" instruction, program return according to those data.

BANK 0, PAGE 8~F area can be used as Stack area.

And, using "PUSH" instruction, 8 bits data in a pair register can be stored in Stack area.

Then, using "POP" instruction, those data are returned to the register.

Maximum Stack area is 64 ( $0 \sim 63$ ), and each Stack area consist of 8 bits.

| $ \left( \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Register File | File      |       |          |               |            |          |          |             |               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|-------|----------|---------------|------------|----------|----------|-------------|---------------|

| BBIT         0         2         4           RSM         RAD         UNRIFE         READ         WRITE         READ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               | ADDRESS   | 0     | -        | 2             | æ          | 4        | 5        | 9           | 7             |

| ADDRESS         LOWERABIT         UPPERABIT         L4BIT         H4BIT         L4BIT         H4BIT         L4BIT         H4BIT           MS         BIT3         F         A         L         H         E         D         D           MS         BIT3         REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 8BIT      | 0     |          | 2             |            | 4        |          | 9           |               |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PAGE          | ADDRESS   | шь    | UPPE     | 8             | H4BIT      | 笄        | HH H     |             | H4BIT         |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (RFB)         | R/W       | WRIT  | EAD      |               | READ WRITE | -        |          | READ WRITE  | READ WRITE    |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |               | MSB BIT 3 |       |          |               |            |          |          |             |               |

| L         BIT 1         REGISTER         REGIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | c             | BIT 2     |       | ٩        |               | т          | ш        | ۵        | ۵.          | в             |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | >             |           |       | REGISTER | REGISTER      | REGISTER   | REGISTER | REGISTER | REGISTER    | REGISTER      |

| $ \left( \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | MSB BIT 3 |       | 0        | INT2          | INT6       | <u> </u> |          |             |               |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •             | BIT 2     |       |          | INT1          | INT5       |          |          | LVLC2       |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _             | BIT 1     |       |          | INTO          | INT4       |          |          | I TVLC1     |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |           |       |          | 0             | INT3       |          | +        |             |               |

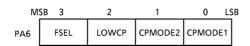

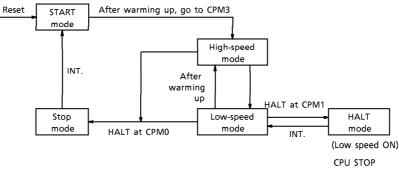

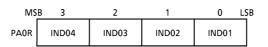

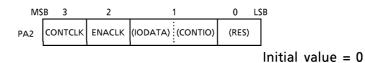

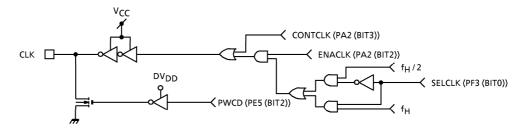

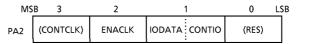

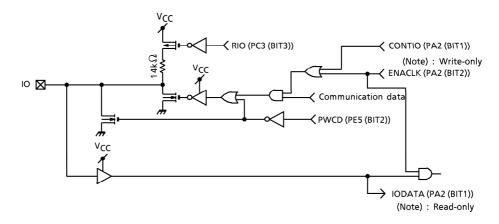

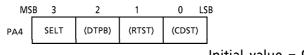

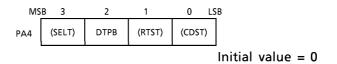

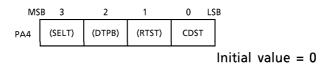

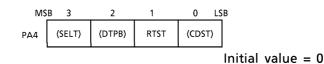

| $ \left  \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | MSB BIT 3 | IND04 | IND14    | CONTCLK       | FCLK3      | SELT     | TREFLG   | FSEL        | RST4          |

| $ \left  \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2             | BIT 2     | IND03 | IND13    | ENACLK        | FCLK2      | DTPB     | RCEFLG   | LOWCP       | RST3          |

| LSB         BIT 0         IND01         IND11         RES         FCLK0         CDST         R           MSB         BIT 2         RAB2         RAR2         RAR3         RAR4         RAR4         RAR4         RAR4         RA8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (PAx)         | BIT 1     | IND02 | IND12    | IODATA CONTIO | FCLK1      | RTST     | PEFLG    | CPMODE2     | RST2          |

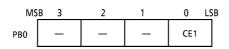

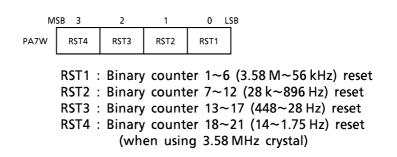

| MSB         BIT 3         RAR4         RAR3           BIT 1         CE1         RAB1         RAB2         RAR3           BIT 1         CE1         RAB1         RAB1         RAR1           MSB         BIT 3         MCLK         IIN04         IIE04         RIO         BCOUT1           MSB         BIT 3         MCLK         IIN04         IIE04         RIO         BCOUT1           MSB         BIT 3         MCLK         IIN02         IIE01         BCOUT1         BCOUT1           MSB         BIT 3         TIA         IIE01         IICCD         BCOUT1         BCOUT1           MSB         BIT 3         TIA         IIR1         IICCD         BCOUT1         BCOUT1           MSB         BIT 3         TIA         IIR3         IIR2         BCSLIO         BCOUT0           MSB         BIT 3         TIA         IIR4         TIE2         DRR4         DRR4           MSB         BIT 3         TIA         IIR3         TIE3         DRR4         DRR4           MSB         BIT 3         TIA         TIR4         TIE4         DRR4         DRR4           MSB         BIT 3         TIR3         TIR3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |           | IND01 | IND11    | RES           | FCLK0      | CDST     | RDEFLG   | CPMODE1     | RST1          |

| $ \left( \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | MSB BIT 3 |       |          |               |            | RAR4     | RAC4     | RAD4        | RAD8          |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | m             | BIT 2     |       |          |               |            | RAR3     | RAC3     | RAD3        | RAD7          |

| LSBBIT 0CE1RAB1RAB1RAR1MSBBIT 3MCLKIIN04IIE04RIOBCOUT1MSBBIT 2ESELTIN03IIE03ISIOBCOUT0BIT 1ESELI0IN01IIE01IIE01IOIE0SELBCLSBBIT 2TI3 $6.8/13.5$ TIR 4TIE4DRR3MSBBIT 2T13 $6.8/13.5$ TIR 3TIE2DRR3MSBBIT 1T12 $27/55$ TIR 3TIE2DRR3MSBBIT 3T14T12 $27/55$ TIR 3TIE2DRR3MSBBIT 3T11T12 $27/55$ TIR 3TIE 3DRR3MSBBIT 3TCH 4SET14TCR18SET13DRR3DRR3MSBBIT 3TCR14SET14TCR18SET13TIR 2TIE 1MSBBIT 3TCR14SET13TCR15CKS13TIE 1DRR1MSBBIT 3TCR14SET13TCR16SET16DRR1MSBBIT 3TCR14SET13TCR16SET12TCR18MSBBIT 3TCR14SET13TCR16SET12TCR18MSBBIT 3TCR14SET13TCR16SET12TCR18MSBBIT 3TCR14SET13TCR16SET22TCR18MSBBIT 3TCR24SET23TCR26SET22TCR26MSBBIT 3TCR24SET23TCR26SET22TCR26 <tr< td=""><td>(PBx)</td><td>BIT 1</td><td></td><td></td><td></td><td>RAB2</td><td>RAR2</td><td>RAC2</td><td>RAD2</td><td>RAD6</td></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (PBx)         | BIT 1     |       |          |               | RAB2       | RAR2     | RAC2     | RAD2        | RAD6          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |           |       |          |               | RAB1       | RAR1     | RAC1     | RAD1        | RAD5          |

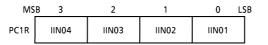

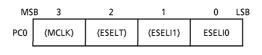

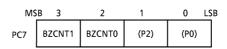

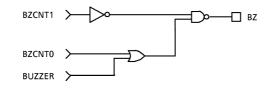

| $ \left  \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |           | 1     | IIN04    | IIE04         | RIO        | BCOUT1   | SELS3    | 32KOUT      | BZCNT1        |

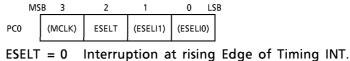

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4             | BIT 2     |       | IIN03    | IIE03         | ISIO       | BCOUTO   | SELS2    | DRCE        | <b>BZCNT0</b> |

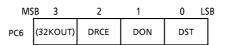

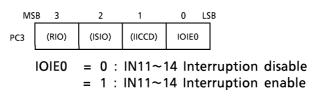

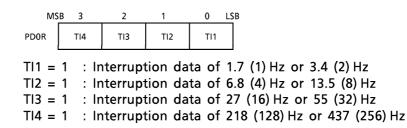

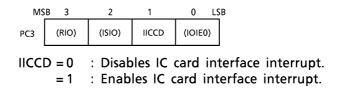

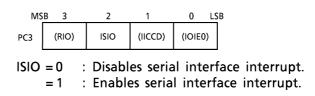

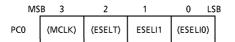

| LSB         BIT 0         ESELIO         IIN01         IIE01         IOIE0         SELBC           MSB         BIT 3         TI4         1.7/3.4         TIR4         TIE4         DRR4           MSB         BIT 1         T12         27/55         TIR3         TIE3         DRR3           LSB         BIT 0         T11         218/437         TIR1         TIE1         DRR1           MSB         BIT 1         T12         27/55         TIR1         TIE1         DRR3           MSB         BIT 0         T11         218/437         TIR1         TIE1         DRR1           MSB         BIT 2         TCR13         SET13         TCR17         SET13         DRR1         TIE1         DRR1           MSB         BIT 2         TCR13         SET13         TCR16         SET13         TCR17         SET13         TCR17         BIR1         TC16         REQT1           MSB         BIT 2         TCR13         SET13         TCR16         SET13         TCR17         SET13         TCR17         BIR2         REQT1         BIR2         REQT0         MSQ10         TC16         BIR1         TC118         BIR3         TC22         TC128         SET23 <td>(PCx)</td> <td>BIT 1</td> <td></td> <td>IIN02</td> <td>IIE02</td> <td>IICCD</td> <td>SELBL</td> <td>SELS1</td> <td>DON</td> <td>P2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (PCx)         | BIT 1     |       | IIN02    | IIE02         | IICCD      | SELBL    | SELS1    | DON         | P2            |

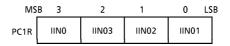

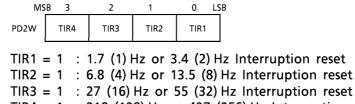

| MSB         BIT 3         TI4         1.7/3.4         TIR4         TIE4         DRR4           BIT 2         T13         6.8/13.5         T1R3         TE3         DRR3         DRR3           BIT 1         T12         27/55         T1R2         TE2         DRR3         DRR3           LSB         BIT 0         T11         218/437         T1R1         TE1         DRR1           MSB         BIT 2         TCR13         SET13         TCR17         SET13         TCR17         BIR1           MSB         BIT 2         TCR13         SET13         TCR16         SET13         TCR17         BIR1         TC16         REQT1           MSB         BIT 2         TCR13         SET13         TCR16         SET13         TCR17         SET13         TC16         REQT1           MSB         BIT 3         TCR14         SET13         TCR16         SET13         TCR16         REQT1         TC16           MSB         BIT 3         TCR12         SET13         TCR16         SET12         TC16         TC16           MSB         BIT 3         TCR24         SET23         TCR25         SET23         TCR26         SET25         TC178         L00 <td></td> <td>1</td> <td></td> <td>IIN01</td> <td>IIE01</td> <td>IOIE0</td> <td>SELBC</td> <td>SELS0</td> <td>DSTA</td> <td>P1</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | 1         |       | IIN01    | IIE01         | IOIE0      | SELBC    | SELS0    | DSTA        | P1            |

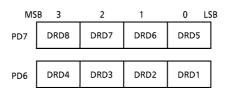

| Image: bit 2         Ti3         EIR3         TIE3         DRR3           LSB         BIT1         T12         27/55         TIR2         TIE2         DRR2           LSB         BIT0         T11         218/437         TIR1         TIE1         DRR1           MSB         BIT2         TCR14         SET14         TCR18         SET13         DRR1         DRR1           MSB         BIT2         TCR13         SET13         TCR17         SET13         TCR17         SET13         TCR17         EG010           MSB         BIT2         TCR13         SET13         TCR16         SET16         CK513         TC1R         REQ70           MSB         BIT2         TCR13         SET13         TCR16         SET16         CK513         TC1R         REQ70           MSB         BIT3         TCR12         SET12         TCR16         SET16         CK513         TC11R         B           MSB         BIT3         TCR24         SET28         TCP5         CMPEN1         TC11R         B           MSB         BIT3         TCR24         SET23         TCR27         SET27         CK523         TC28         TC12R         L00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |           |       | 1.7/3.4  | TIR4          | TIE4       | DRR4     |          | DRD4        | DRD8          |

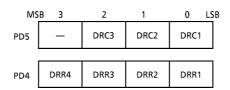

| Image: bit of the second sec | ъ             | BIT 2     |       | 6.8/13.5 | TIR3          | TIE3       | DRR3     | DRC3     | DRD3        | DRD7          |

| LSB         BIT 0         TI1         Z18/437         TIR1         TIE1         DRR1           MSB         BIT 3         TCR14         SET14         TCR18         SET18         MRIO         TC1EN         REQT1           MSB         BIT 3         TCR14         SET13         TCR17         SET17         CKS13         TC1R         REQT0           MSB         BIT 1         TCR12         SET13         TCR17         SET17         CKS13         TC1R         REQT0           MSB         BIT 1         TCR12         SET12         TCR16         SET16         CKS12         CMPEN1         TC11E         B           MSB         BIT 3         TCR11         SET12         TCR16         SET28         TCP5         LC93         TC11R         B         TC11R         B         B         TC11R         B         TC11R         B         TC11R         B         B         TC11R         B         TC12R         TC12R         TC12R         TC12R         TC12R         TC12R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (PDx)         |           | ļ     | 27/55    | TIR2          | TIE2       | DRR2     | DRC2     | DRD2        | DRD6          |

| MSB         BIT 3         TCR14         SET14         TCR18         SET18         MRIO         TC1EN         REQT1           BIT 1         TCR13         SET13         TCR17         SET17         CKS13         TC1R         REQT0           BIT 1         TCR12         SET12         TCR16         SET16         CKS13         TC1R         REQT0           LSB         BIT 0         TCR11         SET11         TCR16         SET12         CKS11         WDT1         TC11E           MSB         BIT 3         TCR24         SET24         TCR28         SET28         TCP5         LC2EN         LD1           MSB         BIT 3         TCR23         SET23         TCR27         SET27         CK523         TC2EN         LD1           BIT 1         TCR23         SET23         TCR26         SET26         CK522         CMPEN2         TC12E           BIT 1         TCR22         SET22         TCR26         SET26         CK522         CMPEN2         TC12E           LSB         BIT 0         TCR21         SET26         SET26         CK522         TC12E         TC12E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | · [       |       | 218/437  | TIR1          | TIE 1      | DRR1     | DRC1     | DRD1        | DRD5          |

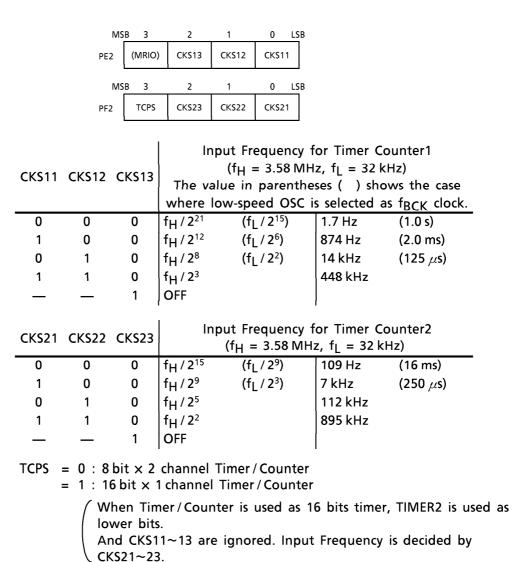

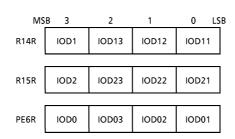

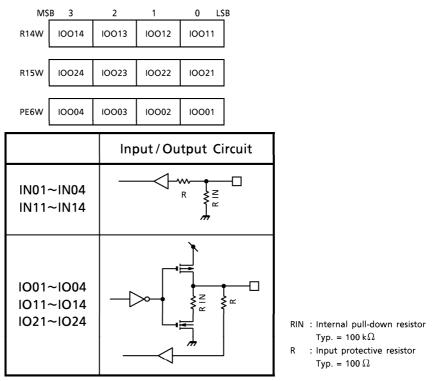

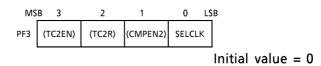

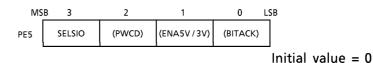

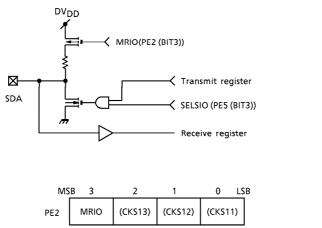

| BIT 2         TCR13         SET13         TCR17         SET17         CKS13         TC1R         REQT0           BIT 1         TCR12         SET12         TCR16         SET16         CKS12         CMPEN1         TC11E         REQT0           LSB         BIT 0         TCR11         SET11         TCR15         SET12         TCR16         BIT         TC11E         BIT         TC11E         BIT         TC111         BIT         TC112         SET11         TCR15         SET12         TC118         B         BIT         TC111         TC118         B         BIT         TC124         SET24         TCR28         SET28         TCP5         LD1         BIT         BIT         TC22N         LD1         BIT         LC228         LD1         BIT         TC222         SET22         TCR26         SET26         CK522         CMPEN2         TC26         LC26         LC27         LC26         LC26         L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | MSB BIT 3 | TCR14 | CR18     | MRIO          | TC1EN      | REQT1    | SELSIO   | IOD04 10004 |               |

| BIT 1         TCR12         SET12         TCR16         SET15         CKS12         CMPEN1         TCI1E           LSB         BIT 0         TCR11         SET13         CKS11         WDT1         TC11E         B           MSB         BIT 3         TCR24         SET13         TCR35         SET28         TCP5         LD1         TC11R         B           MSB         BIT 3         TCR24         SET27         SET28         TCP5         LD1         TC11R         B           MSB         BIT 2         TCR23         SET23         TCR27         SET27         CKS23         LD2         LD1         LD2 <td< td=""><td>9</td><td>BIT 2</td><td>TCR13</td><td>CR17</td><td>CKS13</td><td>TC1R</td><td>REQTO</td><td>PWCD</td><td>IOD03 10003</td><td>BZ3</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9             | BIT 2     | TCR13 | CR17     | CKS13         | TC1R       | REQTO    | PWCD     | IOD03 10003 | BZ3           |

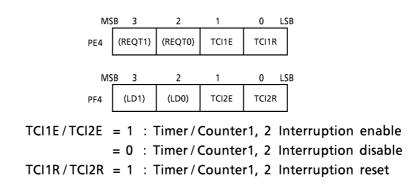

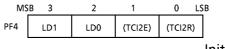

| LSB         BIT 0         TCR11         SET11         TCR15         SET15         CKS11         WDT1         TC11R         B           MSB         BIT 3         TCR24         SET24         TCR28         SET28         TCP5         TC26N         LD1         LD1         LD1           MSB         BIT 2         TCR23         SET23         TCR27         SET27         CK523         LD0         LD1         LD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (PEx)         |           | TCR12 | R16      | CKS12         | CMPEN1     | TCI1E    | ENA5V/3V | IOD02 10002 | BZ2           |

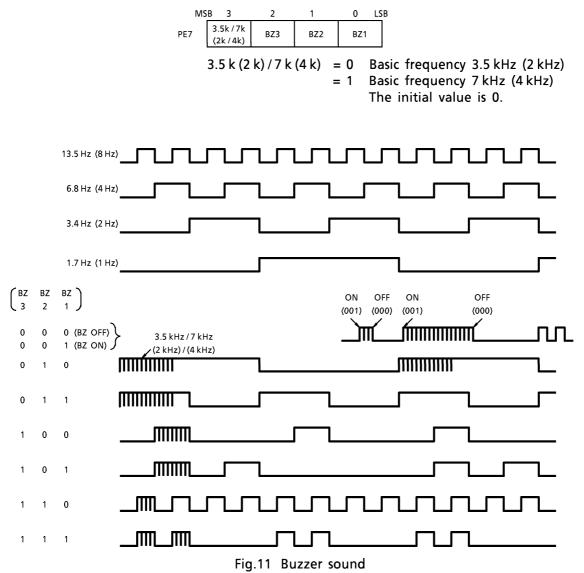

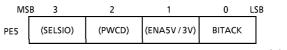

| MSB         BIT 3         TCR24         SET24         TCR28         SET28         TCP5         LD1           BIT 2         TCR23         SET23         TCR27         SET27         SET27         LD0           BIT 1         TCR22         SET22         TCR26         SET26         CK522         CMPEN2         TC26           LSB         BIT 0         TCR21         SET21         TCR25         SET26         SET26         TC126           LSB         BIT 0         TCR21         SET21         TCR25         SET25         TCR27         SET26         TC126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | LSB BIT 0 | TCR11 | .R15     | CKS11         | WDT1       | TCI1R    | BITACK   | IOD01 10001 | BZ1           |