# Hermetically Sealed, Very High Speed, Logic Gate Optocouplers

# Technical Data

## HCPL-540X\* HCPL-643X 5962-89570 5962-89571 HCPL-543X

\*See matrix for available extensions.

#### **Features**

- Dual Marked with Device Part Number and DESC Drawing Number

- Manufactured and Tested on a MIL-PRF-38534 Certified Line

- QML-38534, Class H and K

- Three Hermetically Sealed Package Configurations

- Performance Guaranteed over -55°C to +125°C

- High Speed: 40 M bit/s

- High Common Mode Rejection 500 V/µs Guaranteed

- 1500 Vdc Withstand Test Voltage

- Active (Totem Pole) Outputs

- Three Stage Output Available

- High Radiation Immunity

- HCPL-2400/30 Function Compatibility

- Reliability Data

- Compatible with TTL, STTL, LSTTL, and HCMOS Logic Families

## Applications

- Military and Space

- High Reliability Systems

- Transportation, Medical, and Life Critical Systems

- Isolation of High Speed Logic Systems

- Computer-Peripheral Interfaces

- Switching Power Supplies

- Isolated Bus Driver (Networking Applications)-(5400/1 Only)

- Pulse Transformer Replacement

- Ground Loop Elimination

- Harsh Industrial Environments

- High Speed Disk Drive I/O

- Digital Isolation for A/D, D/A Conversion

## Description

These units are single and dual channel, hermetically sealed optocouplers. The products are capable of operation and storage over the full military temperature range and can be purchased as either standard product or with full MIL-PRF-38534 Class Level H or K testing or from the appropriate DESC Drawing. All devices are manufactured and tested on a MIL-PRF-38534 certified line and are included in the DESC Qualified Manufacturers List QML-38534 for Hybrid Microcircuits.

Each channel contains an AlGaAs light emitting diode which is optically coupled to an integrated high gain photon detector. This combination results in very high

## **Truth Tables**

### (Positive Logic) Multichannel Devices

| Input   | Output |

|---------|--------|

| On (H)  | Н      |

| Off (L) | L      |

#### Single Channel DIP

| Input   | Enable | Output |

|---------|--------|--------|

| On (H)  | L      | L      |

| Off (L) | L      | Н      |

| On (H)  | Н      | Z      |

| Off (L) | Н      | Z      |

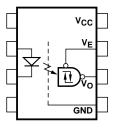

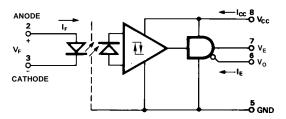

## **Functional Diagram**

Multiple Channel Devices Available

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

data rate capability. The detector has a threshold with hysteresis, which typically provides 0.25 mA of differential mode noise immunity and minimizes the potential for output signal chatter. The detector in the single channel units has a three state output stage which eliminates the need for a pull-up resistor and allows for direct drive of a data bus.

All units are compatible with TTL, STTL, LSTTL, and HCMOS logic families. The 35 ns pulse width distortion specification guarantees a 10 MBd signaling rate at +125 °C with 35% pulse width

distortion. Figures 13 through 16 show recommended circuits for reducing pulse width distortion and optimizing the signal rate of the product. Package styles for these parts are 8 pin DIP through hole (case outlines P), and leadless ceramic chip carrier (case outline 2). Devices may be purchased with a variety of lead bend and plating options. See Selection Guide Table for details. Standard Military Drawing (SMD) parts are available for each package and lead style.

Because the same electrical die (emitters and detectors) are used for each channel of each device listed in this data sheet, absolute maximum ratings, recommended operating conditions, electrical specifications, and performance characteristics shown in the figures are similar for all parts. Occasional exceptions exist due to package variations and limitations and are as noted. Additionally, the same package assembly processes and materials are used in all devices. These similarities give justification for the use of data obtained from one part to represent other part's performance for die related reliability and certain limited radiation test results.

| Package                 | 8 Pin DIP    | 8 Pin DIP             | 20 Pad LCCC   |  |

|-------------------------|--------------|-----------------------|---------------|--|

| Lead Style              | Through Hole | Through Hole          | Surface Mount |  |

| Channels                | 1            | 2                     | 2             |  |

| Common Channel          | None         | V <sub>CC</sub> , GND | None          |  |

| Wiring                  |              |                       |               |  |

| HP Part # & Options     |              |                       |               |  |

| Commercial              | HCPL-5400    | HCPL-5430             | HCPL-6430     |  |

| MIL-PRF-38534, Class H  | HCPL-5401    | HCPL-5431             | HCPL-6431     |  |

| MIL-PRF-38534, Class K  | HCPL-540K    | HCPL-543K             | HCPL-643K     |  |

| Standard Lead Finish    | Gold Plate   | Gold Plate            | Solder Pads   |  |

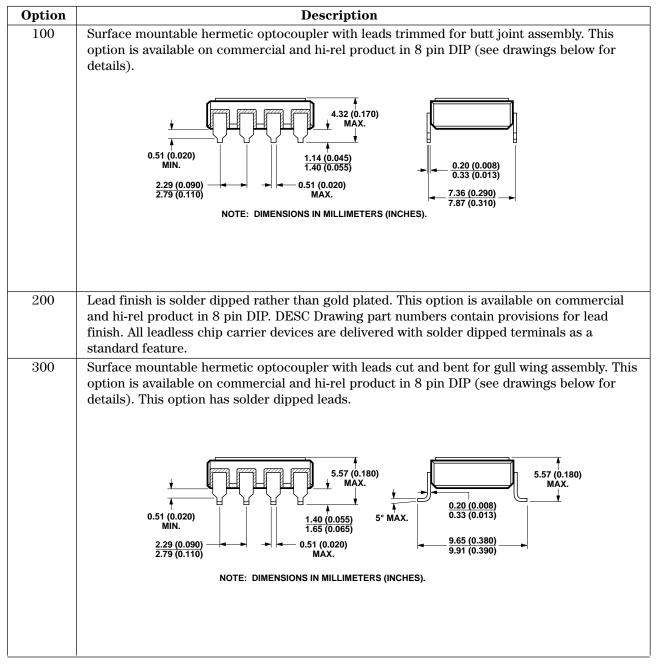

| Solder Dipped           | Option #200  | Option #200           |               |  |

| Butt Cut/Gold Plate     | Option #100  | Option #100           |               |  |

| Gull Wing/Soldered      | Option #300  | Option #300           |               |  |

| SMD Part #              |              |                       |               |  |

| Prescript for all below | 5962-        | 5962-                 | 5962-         |  |

| Either Gold or Solder   | 8957001PX    | 8957101PX             | 89571022X     |  |

| Gold Plate              | 8957001PC    | 8957101PC             |               |  |

| Solder Dipped           | 8957001PA    | 8957101PA             | 89571022A     |  |

| Butt Cut/Gold Plate     | 8957001YC    | 8957101YC             |               |  |

| Butt Cut/Soldered       | 8957001YA    | 8957101YA             |               |  |

| Gull Wing/Soldered      | 8957001XA    | 8957101XA             |               |  |

## Selection Guide-Package Styles and Lead Configuration Options

## **Functional Diagrams**

| 8 Pin DIP                                                                                                       | 8 Pin DIP                                                                                                | 20 Pad LCCC                                                                            |

|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Through Hole                                                                                                    | Through Hole                                                                                             | Surface Mount                                                                          |

| 1 Channel                                                                                                       | 2 Channels                                                                                               | 2 Channels                                                                             |

| $1 \qquad V_{CC} \qquad 8$ $2 \qquad V_{E} \qquad 7$ $3 \qquad I \qquad V_{O} \qquad 6$ $4 \qquad GND \qquad 5$ | $1 \qquad V_{CC} \qquad 8$ $2 \qquad V_{O1} \qquad 7$ $3 \qquad V_{O2} \qquad 6$ $4 \qquad GND \qquad 5$ | $15$ $V_{CC2}$ $19$ $20$ $V_{02}$ $13$ $12$ $2$ $V_{01}$ $V_{01}$ $10$ $GND_1$ $7$ $8$ |

Note: All DIP devices have common  $V_{CC}$  and ground. LCCC (leadless ceramic chip carrier) package has isolated channels with separate  $V_{CC}$  and ground connections.

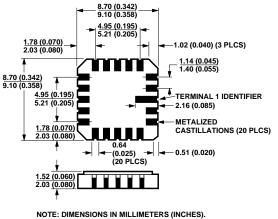

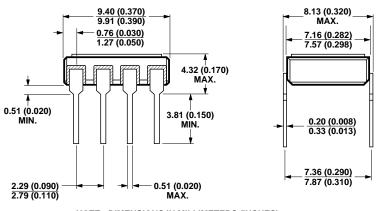

## **Outline Drawings**

20 Terminal LCCC Surface Mount, 2 Channels

NOTE: DIMENSIONS IN MILLIMETERS (INCHES). SOLDER THICKNESS 0.127 (0.005) MAX.

#### 8 Pin DIP Through Hole, 1 and 2 Channel

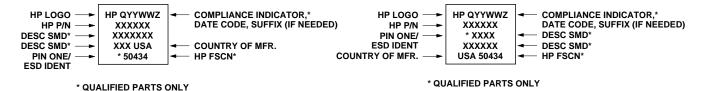

## Leaded Device Marking

## **Leadless Device Marking**

## **Hermetic Optocoupler Options**

## **Absolute Maximum Ratings**

| (No derating required up to $+125^{\circ}$ C)                      |

|--------------------------------------------------------------------|

| Storage Temperature Range, $T_S$                                   |

| Operating Temperature, $T_A$                                       |

| Case Temperature, $T_C$                                            |

| Junction Temperature, $T_J$                                        |

| Lead Solder Temperature                                            |

| Average Forward Current, I <sub>FAVG</sub> (each channel) 10 mA    |

| Peak Input Current, $I_{FPK}$ (each channel)                       |

| Reverse Input Voltage, $V_R$ (each channel)                        |

| Supply Voltage, V <sub>CC</sub>                                    |

| Average Output Current, I <sub>0</sub> 25 mA min., 25 mA max.      |

| (each channel)                                                     |

| Output Voltage, V <sub>0</sub> (each channel)0.5 V min., 10 V max. |

| Output Power Dissipation, P <sub>0</sub> (each channel)130 mW      |

| Package Power Dissipation, P <sub>D</sub> (each channel)           |

## **Single Channel Product Only**

Three State Enable Voltage,  $V_{\!E}$  .....-0.5 V min., 10 V max.

## 8 Pin Ceramic DIP Single Channel Schematic

Note enable pin 7. An external 0.01  $\mu F$  to 0.1  $\mu F$  bypass capacitor must be connected between  $V_{CC}$  and ground for each package type.

## **ESD** Classification

| (MIL-STD-883, Method 3015)    |                             |

|-------------------------------|-----------------------------|

| HCPL-5400/01                  | $(\Delta \Delta)$ , Class 2 |

| HCPL-5430/31 and HCPL-6430/31 | (Dot), Class 3              |

## **Recommended Operating Conditions**

| Parameter                 | Symbol              | Min. | Max.            | Units     |

|---------------------------|---------------------|------|-----------------|-----------|

| Input Current (High)      | I <sub>F(ON)</sub>  | 6    | 10              | mA        |

| Supply Voltage, Output    | V <sub>CC</sub>     | 4.75 | 5.25            | V         |

| Input Voltage (Low)       | V <sub>F(OFF)</sub> | -    | 0.7             | V         |

| Fan Out (Each Channel)    | N                   | I    | 5               | TTL Loads |

| Single Channel Product On | ly                  |      |                 |           |

| High Level Enable Voltage | V <sub>EH</sub>     | 2.0  | V <sub>CC</sub> | V         |

| Low Level Enable Voltage  | V <sub>EL</sub>     | 0    | 0.8             | V         |

## **Electrical Characteristics**

$T_A = -55\,^\circ\!C \text{ to } + 125\,^\circ\!C, \ 4.5 \ V \leq \ V_{CC} \leq \ 5.25 \ V, \ 6 \ mA \leq \ I_{F(ON)} \leq \ 10 \ mA, \ 0 \ V \leq \ V_{F(OFF)} \leq \ 0.7 \ V,$  unless otherwise specified.

|                             |                         |                                                     |                                                                       | Group A <sup>[10]</sup> |      | Limits |      |       |            |              |

|-----------------------------|-------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|-------------------------|------|--------|------|-------|------------|--------------|

| Para                        | ameter                  | Sym.                                                | <b>Test Conditions</b>                                                | Subgroups               | Min. | Typ.*  | Max. | Units | Fig.       | Notes        |

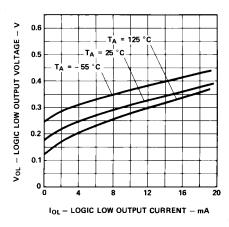

| Low Level C                 | Output Voltage          | V <sub>OL</sub>                                     | $I_{OL} = 8.0 \text{ mA} (5 \text{ TTL Loads})$                       | 1, 2, 3                 |      | 0.3    | 0.5  | V     | 1          | 9            |

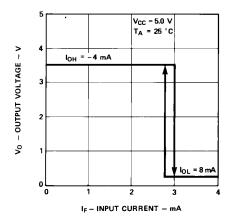

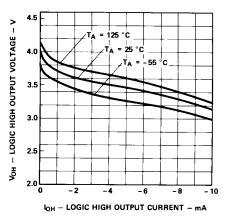

| High Level (                | Output Voltage          | V <sub>OH</sub>                                     | $I_{OH} = -4.0 \text{ mA}$                                            | 1, 2, 3                 | 2.4  |        |      | V     | 2          | 9            |

| Output Leak                 | age Current             | I <sub>OHH</sub>                                    | $V_0 = 5.25 \text{ V}, V_F = 0.7 \text{ V}$                           | 1, 2, 3                 |      |        | 100  | μA    |            | 9            |

| Logic High<br>Supply        | Single<br>Channel       | I <sub>CCH</sub>                                    | $V_{CC} = 5.25 \text{ V}, V_E = 0 \text{ V}$<br>(Single Channel Only) | 1, 2, 3                 |      | 17     | 26   | mA    |            |              |

| Current                     | Dual Channel            |                                                     |                                                                       |                         |      | 34     | 52   |       |            | 13           |

| Logic Low<br>Supply         | Single<br>Channel       | I <sub>CCL</sub>                                    |                                                                       | 1, 2, 3                 |      | 19     | 26   | mA    |            |              |

| Current                     | Dual Channel            |                                                     |                                                                       |                         |      | 38     | 52   |       |            | 13           |

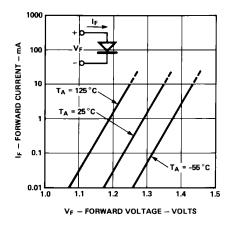

| Input Forwa                 | urd Voltage             | V <sub>F</sub>                                      | $I_F = 10 \text{ mA}$                                                 | 1, 2, 3                 | 1.0  | 1.35   | 1.85 | V     | 4          | 9            |

| Input Revers<br>down Voltag |                         | V <sub>R</sub>                                      | $I_R = 10 \ \mu A$                                                    | 1, 2, 3                 | 3.0  | 4.8    |      | V     |            | 9            |

| Input-Outpu<br>Leakage Cu   |                         | Insulation $I_{I-O}$ $V_{I-O} = 1500$ Vdc, RH = 45% |                                                                       | 1                       |      |        | 1.0  | μA    |            | 2, 3         |

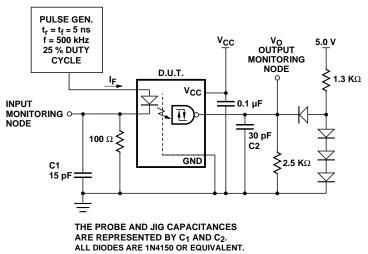

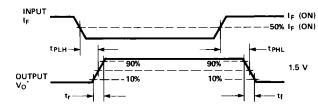

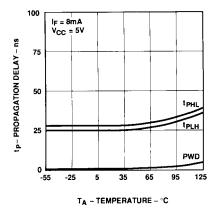

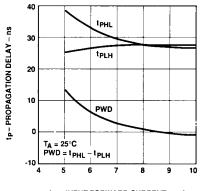

| Propagation<br>Logic Low (  | Delay Time<br>Dutput    | t <sub>PHL</sub>                                    |                                                                       | 9, 10, 11               |      | 33     | 60   | ns    | 5,<br>6, 7 | 4,9          |

| Propagation<br>Logic High   | ı Delay Time<br>Output  | t <sub>PLH</sub>                                    |                                                                       | 9, 10, 11               |      | 30     | 60   | ns    | 5,<br>6, 7 | 4,9          |

| Pulse Width<br>Distortion   |                         | PWD                                                 |                                                                       | 9, 10, 11               |      | 3      | 35   | ns    | 5,<br>6, 7 | 4,9          |

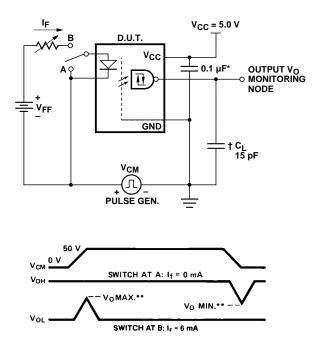

| Logic High<br>Mode Trans    | Common<br>ient Immunity | CM <sub>H</sub>                                     | $V_{CM} = 50 V_{P-P}, I_F = 0 mA$                                     | 9, 10, 11               | 500  | 3000   |      | V/µs  | 11         | 5, 9, 11     |

| Logic Low C<br>Mode Trans   | Common<br>ient Immunity | $ \mathrm{CM}_{\mathrm{L}} $                        | $V_{CM} = 50 V_{P-P}, I_F = 6 mA$                                     | 9, 10, 11               | 500  | 3000   |      | V/µs  | 11         | $5, 9, \\11$ |

#### **Single Channel Product Only**

|                                        |                  | Group A <sup>[1</sup>                                  |           | Limits |       |      |       |      |       |

|----------------------------------------|------------------|--------------------------------------------------------|-----------|--------|-------|------|-------|------|-------|

| Parameter                              | Sym.             | Test Conditions                                        | Subgroups | Min.   | Typ.* | Max. | Units | Fig. | Notes |

| Logic High Enable<br>Voltage           | V <sub>EH</sub>  |                                                        | 1, 2, 3   | 2.0    |       |      | V     |      |       |

| Logic Low Enable<br>Voltage            | V <sub>EL</sub>  |                                                        | 1, 2, 3   |        |       | 0.8  | V     |      |       |

| Logic High Enable                      | I <sub>EH</sub>  | $V_{\rm E} = 2.4  {\rm V}$                             | 1, 2, 3   |        |       | 20   | μA    |      |       |

| Current                                |                  | $V_{\rm E} = 5.25 \text{ V}$                           | 1, 2, 3   |        |       | 100  |       |      |       |

| Logic Low Enable<br>Current            | I <sub>EL</sub>  | $V_{\rm E} = 0.4  \rm V$                               | 1, 2, 3   |        | -0.28 | -0.4 | mA    |      |       |

| High Impedance State<br>Supply Current | I <sub>CCZ</sub> | $V_{CC} = 5.25 \text{ V},$<br>$V_{E} = 5.25 \text{ V}$ | 1, 2, 3   |        | 22    | 28   | mA    |      |       |

| High Impedance State                   | I <sub>OZL</sub> | $V_0 = 0.4 V, V_E = 2 V$                               | 1, 2, 3   |        |       | -20  | μA    |      |       |

| Output Current                         | I <sub>OZH</sub> | $V_0 = 2.4 \text{ V}, V_E = 2 \text{ V}$               |           |        |       | 20   |       |      |       |

|                                        |                  | $V_0 = 5.25 \text{ V}, V_E = 2 \text{ V}$              |           |        |       | 100  |       |      |       |

\*All typical values are at  $V_{CC}$  = 5 V,  $T_{A}$  = 25°C,  $I_{F}$  = 8 mA except where noted.

Typical Characteristics All typical values are at  $T_A$  = 25°C,  $V_{CC}$  = 5 V,  $I_F$  = 8 mA, unless otherwise specified.

| Parameter                                  | Symbol                          | Тур.  | Units            | Test Conditions                                               | Fig. | Notes |

|--------------------------------------------|---------------------------------|-------|------------------|---------------------------------------------------------------|------|-------|

| Input Current Hysteresis                   | I <sub>HYS</sub>                | 0.25  | mA               | $V_{CC} = 5 V$                                                | 3    |       |

| Input Diode Temperature<br>Coefficient     | $\frac{\Delta V_F}{\Delta T_A}$ | -1.11 | mV/°C            | $I_{\rm F} = 10 \ {\rm mA}$                                   | 4    |       |

| Resistance (Input-Output)                  | R <sub>I-O</sub>                | 1012  | Ω                | $V_{I-O} = 500 V$                                             |      | 2     |

| Capacitance (Input-Output)                 | C <sub>I-O</sub>                | 0.6   | pF               | $f = 1 MHz, V_{I-O} = 0 V$                                    |      | 2     |

| Logic Low Short Circuit<br>Output Current  | I <sub>OSL</sub>                | 65    | mA               | $V_{O} = V_{CC} = 5.25 \text{ V},$<br>$I_{F} = 10 \text{ mA}$ |      | 6, 9  |

| Logic High Short Circuit<br>Output Current | I <sub>OSH</sub>                | -50   | mA               |                                                               |      | 6, 9  |

| Output Rise Time (10-90%)                  | t <sub>r</sub>                  | 15    | ns               |                                                               | 5    |       |

| Output Fall Time (90-10%)                  | t <sub>f</sub>                  | 10    | ns               |                                                               | 5    |       |

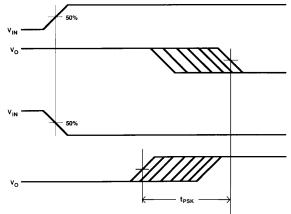

| Propagation Delay Skew                     | t <sub>PSK</sub>                | 30    | ns               |                                                               | 10   | 12    |

| Power Supply Noise Immunity                | PSNI                            | 0.5   | V <sub>P-P</sub> | $48 \text{ Hz} \le f_{ac} \le 50 \text{ MHz}$                 |      | 7     |

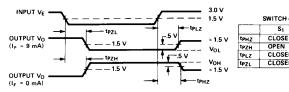

## Single Channel Product Only

| Parameter                           | Symbol           | Тур. | Units | Test Conditions         | Fig. | Notes |

|-------------------------------------|------------------|------|-------|-------------------------|------|-------|

| Input Capacitance                   | C <sub>IN</sub>  | 15   | pF    | $f = 1 MHz, V_F = 0 V,$ |      |       |

|                                     |                  |      |       | Pins 2 and 3            |      |       |

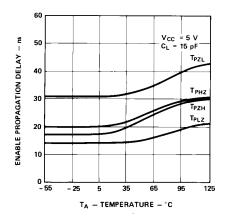

| Output Enable Time to Logic High    | t <sub>PZH</sub> | 15   | ns    |                         | 8,9  |       |

| Output Enable Time to Logic Low     | t <sub>PZL</sub> | 30   | ns    |                         | 8,9  |       |

| Output Disable Time from Logic High | t <sub>PHZ</sub> | 20   | ns    |                         | 8,9  |       |

| Output Disable Time from Logic Low  | t <sub>PLZ</sub> | 15   | ns    |                         | 8,9  |       |

#### **Dual and Quad Channel Product Only**

| Input Capacitance           | C <sub>IN</sub>  | 15   | $\mathrm{pF}$ | $f = 1 MHz, V_0 = 0 V$         |   |

|-----------------------------|------------------|------|---------------|--------------------------------|---|

| Input-Input Leakage Current | I <sub>I-I</sub> | 0.5  | nA            | $RH = 45\%, V_{I-I} = 500 Vdc$ | 8 |

| Input-Input Resistance      | R <sub>I-I</sub> | 1012 | Ω             | $V_{I-I} = 500 V$              | 8 |

| Input-Input Capacitance     | C <sub>I-I</sub> | 1.3  | pF            | $f = 1 MHz, V_F = 0 V$         | 8 |

#### Notes:

- 1. Not to exceed 5% duty factor, not to exceed 50 µsec pulse width.

- 2. All devices are considered two-terminal devices: measured between all input leads or terminals shorted together and all output leads or terminals shorted together.

- 3. This is a momentary withstand test, not an operating condition.

- 4. t<sub>PHL</sub> propagation delay is measured from the 50% point on the rising edge of the input current pulse to the 1.5 V point on the falling edge of the output pulse. The  $t_{pLH}$  propagation delay is measured from the 50% point on the falling edge of the input current pulse to the 1.5 V point on the rising edge of the output pulse. Pulse Width Distortion, PWD =  $|t_{pHL} - t_{pLH}|$ .

- 5.  $CM_{L}$  is the maximum slew rate of the common mode voltage that can be sustained with the output voltage in the logic low state  $(V_{0(MAX)} < 0.8 V)$ . CM<sub>H</sub> is the maximum slow mate of the common mode voltage that can be sustained with the output voltage in the logic high state  $(V_{0(MIX)} > 2.0 V)$ . 6. Duration of output short circuit time not to exceed 10 ms.

- 7. Power Supply Noise Immunity is the peak to peak amplitude of the ac ripple voltage on the  $V_{cc}$  line that the device will withstand and still remain in the desired logic state. For desired logic high state,  $V_{OH(MN)} > 2.0$  V, and for desired logic low state,  $V_{OL(MAX)} < 0.8$  V. 8. Measured between adjacent input pairs shorted together for each multichannel device.

- 9. Each channel.

- 10. Standard parts receive 100% testing at 25°C (Subgroups 1 and 9). SMD and hi-rel parts receive 100% testing at 25, 125, and -55°C (Subgroups 1 and 9, 2 and 10, 3 and 11, respectively).

- 11. Parameters are tested as part of device initial characterization and after design and process changes. Parameters are guaranteed to limits specified for all lots not specifically tested.

- 12. Propagation delay skew is defined as the difference between the minimum and maximum propagation delays for any given group of optocouplers with the same part number that are all switching at the same time under the same operating conditions.

- 13. The HCPL-6430 and HCPL-6431 dual channel parts function as two independent single channel units. Use the single channel parameter limits.

Figure 1. Typical Logic Low Output Voltage vs. Logic Low Output Current.

Figure 3. Typical Output Voltage vs. **Input Forward Current.**

Figure 2. Typical Logic High Output Voltage vs. Logic High Output Current.

Figure 4. Typical Diode Input Forward Current Characteristic.

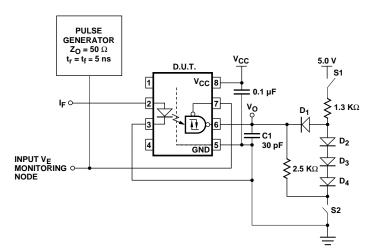

Figure 5. Test Circuit for  $t_{\text{PLH}}, \, t_{\text{PHL}}, \, t_{r}, \, \text{and} \, t_{f}.$

Figure 6. Typical Propagation Delay vs. Ambient Temperature.

IF - INPUT FORWARD CURRENT - mA

Figure 7. Typical Propagation Delay vs. Input Forward Current.

SWITCH MATRIX S<sub>2</sub> CLOSED

tpHZ

CLOSED

tpZH

OPEN

tpLZ

CLOSED

tpZL

CLOSED

CLOSED CLOSED CLOSED OPEN

Figure 8. Test Circuit for  $t_{PHZ}$ ,  $t_{PZH}$ ,  $t_{PLZ}$ , and  $t_{PZL}$ . (Single Channel Product Only).

**Figure 9. Typical Enable Propagation** Delay vs. Ambient Temperature. (Single Channel Product Only).

Figure 10. Propagation Delay Skew, t<sub>PSK</sub>, Waveform.

\*TOTAL LEAD LENGTH < 10 mm FROM DEVICE UNDER TEST. \*\*SEE NOTE 5. †CL IS APPROXIMATELY 15 pF, WHICH INCLUDES PROBE AND STRAY WIRING CAPACITANCE.

Figure 11. Test Diagram for Common Mode Transient Immunity and Typical Waveforms.

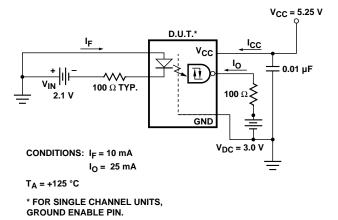

Figure 12. Operating Circuit for Burn-In and Steady State Life Tests.

#### MIL-PRF-38534 Class H, Class K, and DESC SMD Test Program

Hewlett-Packard's Hi-Rel Optocouplers are in compliance with MIL-PRF-38534 Classes H and K. Class H devices are also in compliance with DESC drawings 5962-89570, and 5962-89571.

Testing consists of 100% screening and quality conformance inspection to MIL-PRF-38534.

## Data Rate and Pulse-Width Distortion Definitions

Propagation delay is a figure of merit which describes the finite amount of time required for a system to translate information from input to output when shifting logic levels. Propagation delay from low to high  $(t_{PLH})$ specifies the amount of time required for a system's output to change from a Logic 0 to a Logic 1, when given a stimulus at the input. Propagation delay from high to low  $(t_{PHL})$  specifies the amount of time required for a system's output to change from a Logic 1 to a Logic 0, when given a stimulus at the input (see Figure 5).

When  $t_{PLH}$  and  $t_{PHL}$  differ in value, pulse width distortion results. Pulse width distortion is defined as  $|t_{PHL} - t_{PLH}|$  and determines the maximum data rate capability of a distortion-limited system. Maximum pulse width distortion on the order of 25-35% is typically used when specifying the maximum data rate capabilities of systems. The exact figure depends on the particular application (RS-232, PCM, T-1, etc.).

These high performance optocouplers offer the advantages of specified propagation delay ( $t_{PLH}$ ,  $t_{PHL}$ ), and pulse width distortion ( $|t_{PLH}$ -t  $_{PHL}|$ ) over temperature and power supply voltage ranges.

## Applications

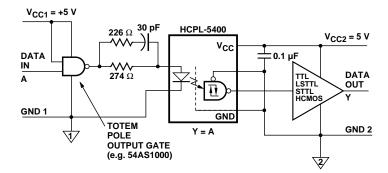

Figure 13. Recommended HCPL-5400 Interface Circuit.

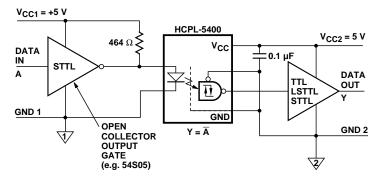

Figure 14. Alternative HCPL-5400 Interface Circuit.

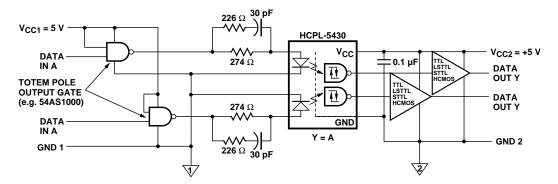

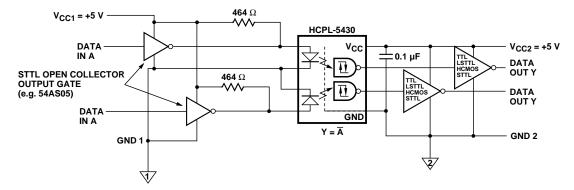

Figure 15. Recommended HCPL-5430 and HCPL-6430 Interface Circuit.

Figure 16. Alternative HCPL-5430 and HCPL-6430 Interface Circuit.

Copyright © Each Manufacturing Company.

All Datasheets cannot be modified without permission.

This datasheet has been download from :

www.AllDataSheet.com

100% Free DataSheet Search Site.

Free Download.

No Register.

Fast Search System.

www.AllDataSheet.com